### Features

- Up to 1.5A Current Output

- 2.7V to 5.5V Input Voltage Range

- 1.5MHz Constant Frequency Operation

- High Efficiency: Up to 96%

- Low Dropout Operation: 100% Duty Cycle

- No Schottky Diode Required

- PFM Mode for High Efficiency in Light Load

- Over Temperature Protected

- Short Circuit Protection

- Low Quiescent Current: 40μA

- Inrush Current Limit and Soft Start

- SOT23-5 Package

# Applications

- Cellular and Smart Phones

- Wireless and DSL Modems

- PDAs

# **General Description**

- Battery-Powered Equipment

- Portable Media Player (PMP)

- PC Cards

The WD2015 is a high-efficiency monolithic synchronous buck regulator using a constant frequency, current mode architecture. The device is available in an adjustable version. Supply current with no load is 40uA and drops to<1uA in shutdown. The 2.7V to 5.5V input voltage range makes the WD2015 ideally suited for single Li-Ion battery powered applications. 100% duty cycle provides low dropout operation, extending battery life in portable systems. PWM/PFM mode operation provides very low output ripple voltage for noise sensitive applications.Switching frequency is internally set at 1.5MHz, allowing the use of small surface mount inductors and capacitors. Low output voltages are easily supported with the 0.6V feedback reference voltage.The WD2015 is offered in a low profile (1mm) 5-pin, thin SOT package, and is available in an adjustable version

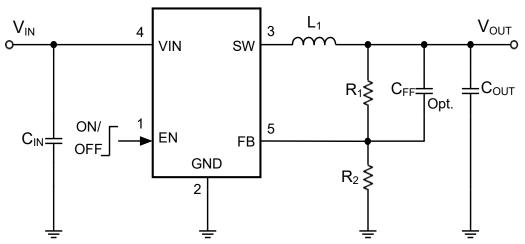

# **Typical Application Circuit**

Typical Application Circuit

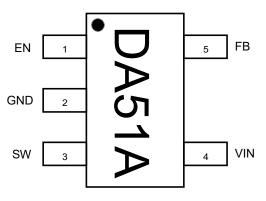

# Package and Pin Description

## **Pin Configuration**

SOT23-5L

### **Pin Description**

| Pin | Name | Function                                                                      |

|-----|------|-------------------------------------------------------------------------------|

| 1   | EN   | Chip Enable Pin. Drive EN above 1.5V to turn on the part.Drive EN below 0.3V  |

|     |      | to turn it off. Do not leave EN floating.                                     |

| 2   | GND  | Ground Pin                                                                    |

| 3   | SW   | Power Switch Output. It is the switch node connection to Inductor. This pin   |

|     |      | connects to the drains of the internal P-ch and N-ch MOSFET switches.         |

| 4   | VIN  | Power Supply Input. Must be closely decoupled to GND with a 10µF or greater   |

|     |      | ceramic capacitor.                                                            |

|     | FB   | Output Voltage Feedback Pin. An internal resistive divider divides the output |

| 5   |      | voltage down for comparison to the internal reference voltage.                |

#### **Order Information**

| Model  | Marking | Description                                               | Package | T/R Qty |

|--------|---------|-----------------------------------------------------------|---------|---------|

| WD2015 | DA51A   | WD2015 Buck, 2.7-5.5V, 1.5A,<br>1.5MHz, VFB 0.6V, SOT23-5 | SOT23-5 | 3000PCS |

All WPM parts are Pb-Free and adhere to the RoHS directive.

# Specifications

## Absolute Maximum Ratings (Note1)

| Item                                        | Min  | Max                   | Unit |

|---------------------------------------------|------|-----------------------|------|

| Input Supply Voltage                        | -0.3 | 6.0                   | V    |

| EN, FB Voltages                             | -0.3 | 6.0                   | V    |

| SW Voltage                                  | -0.3 | V <sub>IN</sub> +0.3V | V    |

| Peak SW Sink and Source Current             | 1.8  |                       | A    |

| Operating Temperature Range                 | -40  | +85                   | °C   |

| Storage Temperature Range                   | -65  | 150                   | °C   |

| Junction Temperature <sub>(Note2)</sub>     | 125  |                       |      |

| Lead Temperature(Soldering,10s)             | 300  |                       | °C   |

| Thermal Resistance( $\theta_{JC}$ ) SOT23-5 | 130  |                       |      |

Note (1): Exceeding these ratings may damage the device.

Note (2): The device is not guaranteed to function outside of its operating conditions.

#### **ESD Ratings**

| Item Description       |                                      | Value      | Unit |

|------------------------|--------------------------------------|------------|------|

|                        | Human Body Model (HBM)               |            |      |

| V <sub>(ESD-HBM)</sub> | ANSI/ESDA/JEDEC JS-001-2014          | $\pm 2000$ | V    |

|                        | Classification, Class: 2             |            |      |

|                        | Charged Device Mode (CDM)            |            |      |

| V <sub>(ESD-CDM)</sub> | ANSI/ESDA/JEDEC JS-002-2014          | ±200       | V    |

|                        | Classification, Class: C0b           |            |      |

| Т                      | JEDEC STANDARD NO.78E APRIL 2016     | 150        |      |

| LATCH-UP               | Temperature Classification, Class: I | ±150       | mA   |

# **Electrical Characteristics**

( $V_{IN}=V_{EN}=3.6V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.)

| Parameter                                              | Conditions                     | Min.  | Тур.  | Max.  | Unit |

|--------------------------------------------------------|--------------------------------|-------|-------|-------|------|

| Input Voltage Range                                    |                                | 2.7   |       | 5.5   | V    |

| UVLO Threshold                                         |                                |       | 2.5   |       | V    |

|                                                        | FB = 90%, Iload=0mA            |       | 150   | 300   | μA   |

| Input DC Supply Current                                | FB=105%, Iload=0mA             |       | 40    | 70    | μΑ   |

|                                                        | $V_{EN} = 0V, V_{IN} = 4.2V$   |       | 0.1   | 1.0   | μA   |

| Regulated Feedback Voltage                             | $T_A = 25^{\circ}C$            | 0.591 | 0.600 | 0.609 | V    |

| Reference Voltage Line Regulation $Vin = 2.7V$ to 5.5V |                                |       | 0.04  | 0.40  | %/V  |

| Output Voltage Line Regulation                         | $V_{IN} = 2.7V$ to 5.5V        |       | 0.04  | 0.4   | %    |

| Output Voltage Load Regulation                         |                                |       | 0.5   |       | %    |

| Oscillation Frequency                                  |                                |       | 1.5   |       | MHz  |

| Peak Current Limit                                     | V <sub>IN</sub> = 3.6V, FB=90% | 1.8   |       |       | A    |

| On Resistance of PMOS                                  | I <sub>SW</sub> =100mA         |       | 150   |       | mΩ   |

| ON Resistance of NMOS                                  | I <sub>SW</sub> =-100mA        |       | 130   |       | mΩ   |

| EN Threshold                                           |                                | 0.30  | 1.0   | 1.50  | V    |

| EN Leakage Current                                     |                                |       | ±0.01 | ±1.0  | μA   |

| SW Leakage Current                                     | $V_{EN}=0V, V_{IN}=V_{SW}=5V$  |       | ±0.01 | ±1.0  | μA   |

| Soft Start                                             |                                |       |       | 1.0   | mS   |

| Thermal Shutdown                                       |                                |       | 160   |       | °C   |

| Thermal Hysteresis                                     |                                |       | 20    |       | °C   |

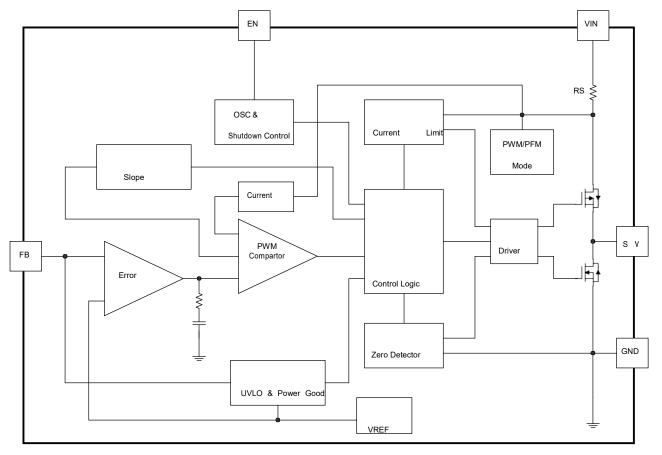

# **Functional Block Diagram**

Figure .Block Diagram

## Operation

The WD2015 uses a constant frequency, current mode step-down architecture. Both the main (P-channel MOSFET) and synchronous (N-channel MOSFET) switches are internal. During normal operation, the internal top power MOSFET is turned on each cycle when the oscillator sets the RS latch, and turned off when the current comparator, ICOMP, resets the RS latch. The peak inductor current at which ICOMP resets the RS latch, is controlled by the output of error amplifier EA. When the load current increases, it causes a slight decrease in the feedback voltage, FB, relative to the 0.6V reference, which in turn, causes the EA amplifier's output voltage to increase until the average inductor current matches the new load current. While the top MOSFET is off, the bottom MOSFET is turned on until either the inductor current starts to reverse, as indicated by the current reversal comparator IRCMP, or the beginning of the next clock cycle

# **Applications Information**

#### Setting the Output Voltage

In the adjustable version, the output voltage is set by a resistive divider according to the following formula:

$$R_2 = \frac{R_1}{V_{OUT} / V_{FB} - 1}$$

The external resistive divider is connected to the output, allowing remote voltage sensing as shown in on page 1

#### **Inductor Selection**

For most designs, the WD2015 operates with inductors of  $1\mu$ H to  $4.7\mu$ H. Low inductance values are physically smaller but require faster switching, which results in some efficiency loss. The inductor value can be derived from the following equation

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_L \times f_{osc}}$$

Where  $\Delta I_L$  is inductor Ripple Current. Large value inductors result in lower ripple current and small value inductors result in high ripple current. For optimum voltage-positioning load transients, choose an inductor with DC series resistance in the 50m $\Omega$  to 150m $\Omega$  range

#### **Input Capacitor Selection**

Higher values, lower cost ceramic capacitors are now becoming available in smaller case sizes. Their high ripple current, high voltage rating and low ESR make them ideal for switching regulator applications. Because the WD2015's control loop does not depend on the output capacitor's ESR for stable operation, ceramic capacitors can be used freely to achieve very low output ripple and small circuit size. However, care must be taken when ceramic capacitors are used at the input and the output. When a ceramic capacitor is used at the input and the power is supplied by a wall adapter through long wires, a load step at the output can induce ringing at the input, VIN. At best, this ringing can couple to the output and be mistaken as loop instability. At worst, a sudden inrush of current through the long wires can potentially cause a voltage spike at VIN, large enough to damage the part. When choosing the input and output ceramic capacitors, choose the X5R or X7R dielectric formulations. These dielectrics have the best temperature and voltage characteristics of all the ceramics for a given value and size.

#### PC Board Layout Checklist

When laying out the printed circuit board, the following checking should be used to ensure proper operation of the WD2015. Check the following in your layout:

- The power traces, consisting of the GND trace, the SW trace and the VIN trace should be kept short, direct and wide.

- Does the (+) plates of Cin connect to Vin as closely as possible? This capacitor provides the AC current to the internal power MOSFETs.

- > Keep the switching node, SW, away from the sensitive VOUT node.

- ➤ Keep the (-) plates of Cin and Cout as close as possible

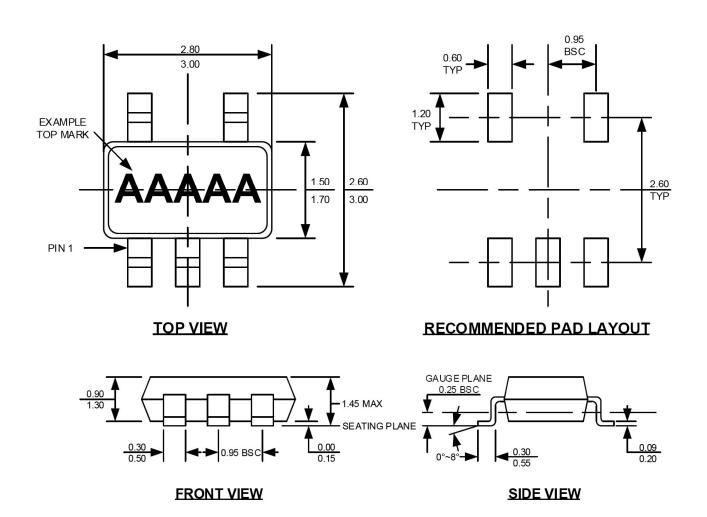

# PACKAGE OUTLINE DRAWING FOR

## SOT23-5

Note:

- 1. All dimensions are in millimeters.

- 2. Package length does not include mold flash, protrusion or gate burr.

- 3. Package width does not include flash or protrusion.

- 4. Lead coplanarity (bottom of leads after forming) shall be 0.10 millimeters max.

- 5. Pin 1 is lower left pin when reading top mark from left to right.