#### WD1305E20

# 18V, 2A, High-Efficiency, Synchronous Step-Down Converter

#### **Descriptions**

The WD1305E20 is a high efficiency, 500kHz switch frequency, synchronous step-down DC-DC converter with delivering 2A current capability. The WD1305E20 operates over a wide input voltage range from 4.5V to 18V and integrates main switch and synchronous switch with very low  $R_{\text{DS(ON)}}$  to minimize the conduction loss.

The WD1305E20 applies Constant-on-time (COT) control mode which provides very fast load transient response and easy loop design. The WD1305E20 integrates full protections features including short-circuit protection, over-current protection, under voltage protection and thermal shutdown to make the part operating safely.

The WD1305E20 is available in SOT-23-6L package. Standard product is Pb-free and Halogen-free.

#### **Features**

- Wide input voltage range of 4.5V to 18V

- Integrate 140mΩ (High Side) / 110mΩ (Low Side)

Low R<sub>DS(ON)</sub> Power MOSFETs

- 70µA Low Quiescent Current

- High-efficiency synchronous-mode Operation

- Power save mode at light load

- Fast load transient response with COT control mode

- Over-current protection and Hiccup

- Output adjustable from 0.6V

## **Applications**

- Set Top Box

- Access Point Router

- DSL Modem \ Security Cameras

- Flat-Panel Televisions and Monitors

#### Http//:www.sh-willsemi.com

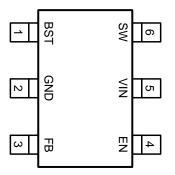

SOT-23-6L

Pin configuration (Top view)

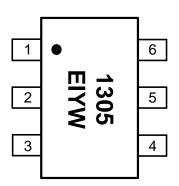

1305 = Device Code

EI = Special code

Y = Year code

W = Week code

Marking

#### **Order information**

| Device         | Package   | Shipping       |

|----------------|-----------|----------------|

| WD1305E20-6/TR | SOT-23-6L | 3000/Reel&Tape |

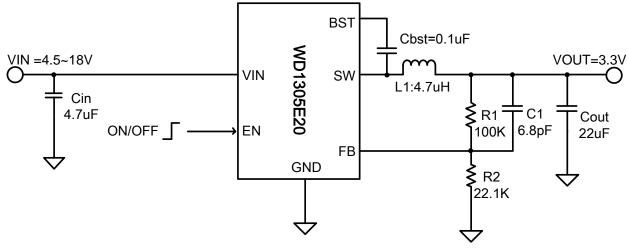

# **Typical Applications**

Fig1 Schematic Diagram

# **Pin Descriptions**

| No. | Symbol | Description                                                                                                                                             |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BST    | Bootstrap pin. Connect a capacitor between SW and BST pins to form a floating supply across the high-side switch driver. Use a 0.1µF BST capacitor.     |

| 2   | GND    | System Ground pin. Reference ground of the regulated output voltage: requires extra care during PCB layout. Connect to GND with copper traces and vias. |

| 3   | FB     | Converter feedback input. Connect to output voltage with feedback resistor divider.                                                                     |

| 4   | EN     | Enable input control pin. To active high for automatic start-up, EN can be connected to VIN directly or through a resistor.                             |

| 5   | VIN    | Supply Voltage pin. Requires a cap to decouple the input rail. Connect using a wide PCB trace.                                                          |

| 6   | SW     | Switch Output pin. Connect using a wide PCB trace.                                                                                                      |

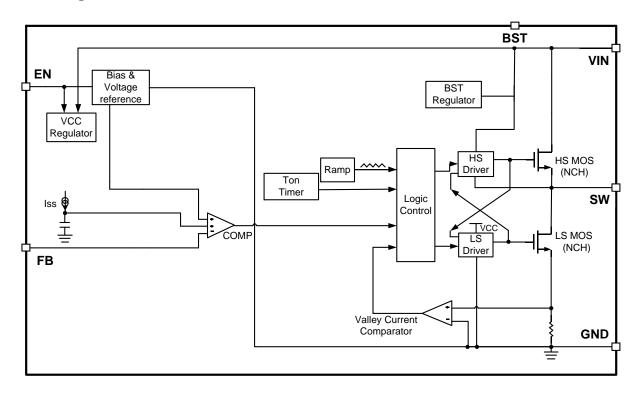

# **Block Diagram**

# Absolute Maximum Ratings(1)

| Parameter                             | Symbol           | Value                              | Unit |

|---------------------------------------|------------------|------------------------------------|------|

| VIN pin voltage range                 | V <sub>IN</sub>  | -0.3∼ <b>+</b> 20                  | V    |

| EN pin voltage range                  | -                | -0.3∼V <sub>IN</sub>               | V    |

| SW pin voltage range (DC)             | Vsw              | -0.3∼(V <sub>IN(Max)</sub> +0.3)   | V    |

| BST pin voltage range(DC)             |                  | $(V_{SW} - 0.3) \sim (V_{SW} + 6)$ | V    |

| All Other Pins Voltage                | -                | -0.3~ 6                            | V    |

| Power Dissipation – SOT23-6L (Note 2) | P <sub>D</sub>   | 0.5                                | W    |

| The armed Characteristics             | Reja             | 250                                | °C/W |

| Thermal Characteristics               | R <sub>θJC</sub> | 110                                | °C/W |

| Maximum Junction Temperature          | TJ               | 150                                | °С   |

| Lead temperature(Soldering, 10s)      | TL               | 260                                | °С   |

| Operating ambient temperature         | Topr             | -40 ~ 85                           | °С   |

| Storage temperature                   | Tstg             | -55 ~ 150                          | °C   |

| TSD Classification                    | HBM              | 5500                               | V    |

| ESD Classification                    | CDM              | 2000                               | V    |

Note (1): Exceeding these ratings may damage the device.

Note (2): The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J(MAX)$ , the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D(MAX) = (T_J(MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.  $\theta_{JA}$  is tested based on EV5303-1.0 board.

# Recommended Operation Conditions (3)

| Symbol                                     | Characteristics       | Min             | Тур | Max | Unit          |

|--------------------------------------------|-----------------------|-----------------|-----|-----|---------------|

| V <sub>IN</sub>                            | Supply Voltage        | 4.5             | 12  | 18  | V             |

| Vouт                                       | Output Voltage        | V <sub>FB</sub> |     | 8   | V             |

| Operating Junction Temp. (T <sub>J</sub> ) | Operating temperature | -40             | •   | 125 | ${\mathbb C}$ |

Note (3): The device is not guaranteed to function outside of its operating conditions.

# Electronics Characteristics (Ta=25°C, V<sub>IN</sub>=12V, unless otherwise noted)

| Parameter                             | Symbol            | Conditions                                        | Min. | Тур. | Max. | Units |  |

|---------------------------------------|-------------------|---------------------------------------------------|------|------|------|-------|--|

| Input Voltage Range                   | $V_{IN}$          |                                                   | 4.5  |      | 18   | V     |  |

| V <sub>IN</sub> Under Voltage Lockout |                   | Rising                                            |      | 4.15 | 4.45 |       |  |

| Threshold                             | Vuvlo             | Falling                                           |      | 3.85 |      | V     |  |

| Standby Supply Current                | ΙQ                | V <sub>FB</sub> = 105%, I <sub>OUT</sub> = 0A     |      | 70   | 100  | uA    |  |

| Shutdown Supply Current               | I <sub>SHDN</sub> | V <sub>EN</sub> = 0V, Vin=12V                     |      | 2    | 5    | uA    |  |

| Feedback reference Voltage            | V <sub>FB</sub>   |                                                   | -2%  | 0.6  | 2%   | V     |  |

| Inductor valley Current Limit         | I <sub>LIM</sub>  | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 5V      |      | 2.4  |      | Α     |  |

| Oscillator Frequency                  | fosc              | V <sub>FB</sub> or V <sub>OUT</sub> in regulation |      | 500  |      | kHz   |  |

| R <sub>DS(ON)</sub> of HS FET         | R <sub>PFET</sub> | Isw = 100mA                                       |      | 0.14 |      | Ω     |  |

| R <sub>DS(ON)</sub> of LS FET         | R <sub>NFET</sub> | Isw = −100mA                                      |      | 0.11 |      | Ω     |  |

| Feedback Leakage Current              | I <sub>FB</sub>   | VFB=0.85V                                         |      |      | ±30  | nA    |  |

| SW Leakage Current                    | ILSW              | $V_{IN} = 12V, V_{SW} = 0V \text{ or } 12V$       |      |      | ±5   | uA    |  |

| EN Rising Threshold                   | V <sub>ENH</sub>  |                                                   | 1.4  |      |      | V     |  |

| EN falling Threshold                  | VENL              |                                                   |      |      | 0.4  | V     |  |

| EN Lookago Current                    | le                | $V_{IN} = 12V, V_{EN} = 0V$                       |      |      | 1    |       |  |

| EN Leakage Current                    | I <sub>EN</sub>   | V <sub>IN</sub> = 12V, V <sub>EN</sub> = VIN      |      | 1    | 2    | uA    |  |

| Min On Time                           |                   |                                                   |      | 50   |      | nS    |  |

| Min Off Time                          |                   |                                                   |      | 100  |      | nS    |  |

| Soft Start Time                       |                   |                                                   |      | 800  |      | uS    |  |

| land OVB Chatdows                     | Vovp              | Rising                                            |      | 19   |      | V     |  |

| Input OVP Shutdown                    |                   | Falling                                           | 18   | 18.5 |      | V     |  |

| Over Voltage Protection               |                   |                                                   |      | 15   |      | uS    |  |

| Blanking Time                         |                   |                                                   |      | 10   |      | uS    |  |

| Over Temperature Protection           | Тотр              |                                                   |      | 155  |      | °C    |  |

| OTP Hysteresis                        |                   |                                                   |      | 25   |      | °C    |  |

Note (4): Guaranteed by design and engineering sample characterization.

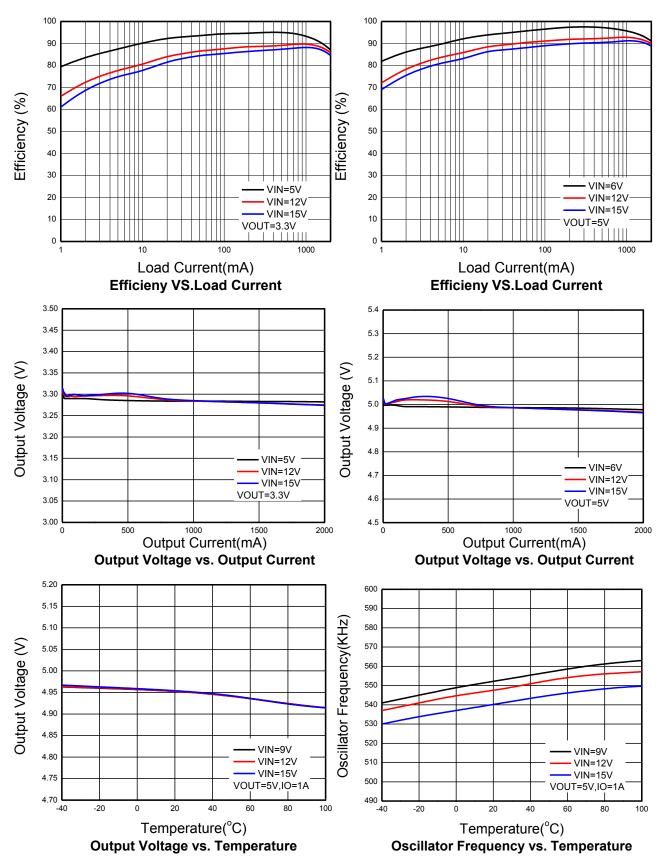

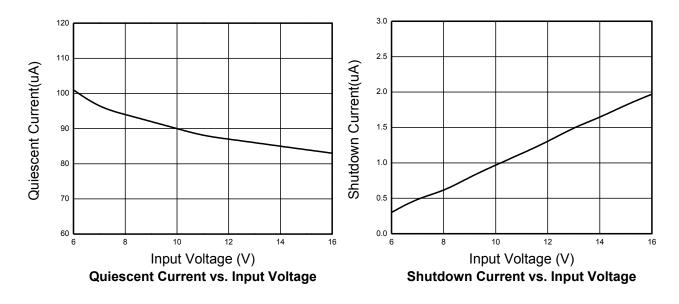

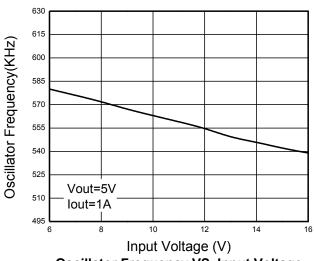

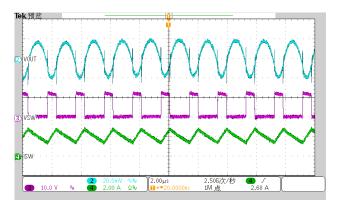

## **Typical Characteristics**

(Ta=25℃, VIN=12V, VEN=3V, VOUT =5V, L1=4.7uH, CIN=4.7uF, COUT=22μF, C1=6.8pF, unless otherwise noted)

Oscillator Frequency VS. Input Voltage

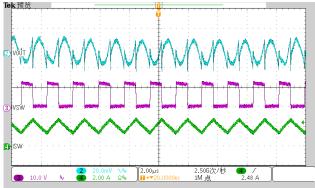

Ripple, VIN=12V, VO=3.3V,VEN=3.0V,IO=2A

Ripple, VIN=12V, VO=5V, VEN=3.0V, IO=2A

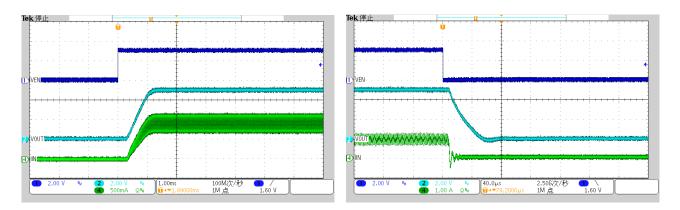

$V_{\text{IN}}$ =12V,  $V_{\text{O}}$ =5V, $V_{\text{EN}}$ =3.0V, $I_{\text{O}}$ =2A, EN On

VIN=12V, VO=5V,VEN=3.0V,IO=2A, EN OFF

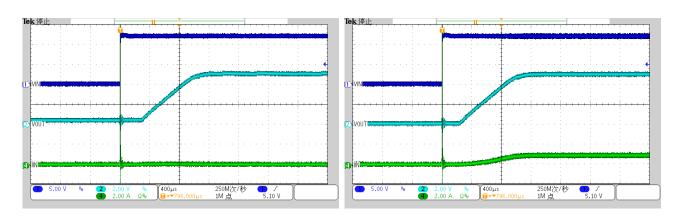

VIN= VEN=12V,VO=5V,IO=1mA,VIN ON

VIN= VEN=12V, VO=5V, IO=2A, VIN ON

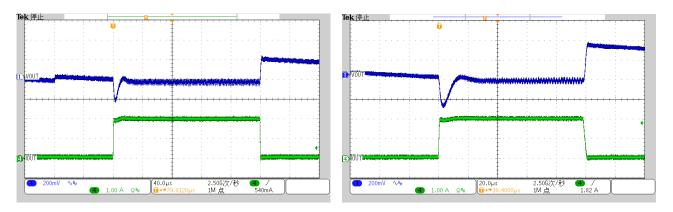

VIN=12V,VO=3.3V,VEN=3.0V,IO=1mA-2A

VIN=12V,VO=5V,VEN=3.0V,IO=1mA-2A

#### **Operation Informations**

#### **Control Mode**

The WD1305E20 step-down converter operates with typically 500KHz constant on time at moderate to heavy load currents. Both the upper and lower synchronous N-channel MOSFET switches are internal. The converter uses a proprietary fast constant on time control (FCOT) scheme to achieve good line and load transient response. The FCOT™ mode control combines adaptive on-time control with internal compensation circuit an pseudo-fixed frequency and low external component count configuration with both low ESR and ceramic output capacitors. It is stable even with virtually no ripple at the output.

At the beginning of each cycle, the high-side MOSFET is turned on. This MOSFET is turned off after internal one shot timer expires. This one shot duration is set proportional to the converter input voltage- $V_{\text{IN}}$  and inversely proportional to the output voltage- $V_{\text{O}}$  to maintain a pseudo-fixed frequency over the input voltage range. The one-shot timer is reset and the high-side MOSFET is turned on again when a internal pseudo ramp is fallen below the output of internal error amplifier.

#### **Short-Circuit Protection**

WD1305E20 provides cycle by cycle current limit, the inductor valley current need to drop below the current limit before the next pulse can be fired.

#### **Dropout Operation**

Once the input voltage comes close to the nominal output voltage, the upper switch is turned on for one or more cycles. Every 20-30us, low side FET is turned on briefly to refresh Cboot. Thus the voltage difference between BST and SW can be kept high enough to fully turn on the upper FET.

The output voltage will then be determined by the input voltage minus the voltage drop across the upper N-channel MOSFET and the inductor.

#### **Shutdown Mode**

Drive EN to GND to place the WD1305E20 in shutdown mode. In shutdown mode, the reference, control circuit, main switch, and synchronous switch turn off and the output becomes high impedance. Input current falls to  $1.8\mu A$  (Typ.) during shutdown mode.

#### **Over Temperature Protection (OTP)**

As soon as the junction temperature (T<sub>J</sub>) exceeds 155°C (Typ.), the device goes into thermal shutdown. In this mode, the high-side and low-side MOSFET are turned off.

# **Application Informations**

External component selection for the application circuit depends on the load current requirements. Certain tradeoffs between different performance parameters can also be made.

#### **Output Voltage Setting**

The output voltage can be calculated as:

$$V_{OUT} = 0.6 \times \left(1 + \frac{R1}{R2}\right)$$

The external resistive divider is connected to the output. The sum of R1 and R2 should be between  $10k\Omega$  to 1  $M\Omega$ , to keep the network robust against noise. An external feed forward capacitor C1 is required for optimum load transient response. The value of C1 should be in the range between 6.8pF and 22pF. If Vout is 3.3V, R1=100k is chosen, then using the equation, R2 can be calculated to be 22.1k.

Route the FB line away from noise sources, such as the inductor or the SW line.

#### Inductor Selection

The WD1305E20 high switching frequency allows the use of a physically small inductor. The inductor ripple current is determined by

$$\Delta I_L = \frac{V_{OUT}}{(f)(L)} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

Where  $\Delta I_L$  is the peak-to-peak inductor ripple current and f is the switching frequency. The inductor peak-to-peak current ripple is typically set to be 40% of the maximum dc load current. Using this guideline and solving for L,

$$L = \frac{V_{OUT}}{f(40\% I_{LOAD(MAX)})} \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

It is important to ensure that the inductor is capable of handling the maximum peak inductor current,  $I_{\text{LPK}}$ , determined by

$$I_{LPK} = I_{LOAD(MAX)} + \frac{\Delta I_L}{2}$$

#### Inductor Core Selection

Different core materials and shapes will change the size/current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don't radiate much energy, but generally cost more than powdered iron core inductors with similar electrical characteristics. The choice of which style inductor to use often depends more on the price vs. size requirements and any radiated **EMI** requirements than on what the WD1305E20 requires to operate.

#### **Input Capacitor Selection**

Capacitor ESR is a major contributor to input ripple in high-frequency DC-DC converters. Ordinary aluminum electrolytic capacitors have high ESR and should be avoided. Low-ESR tantalum or polymer capacitors are better and provide a compact solution for space constrained surface mount designs. Ceramic capacitors have the lowest overall ESR. The input filter capacitor reduces peak currents and noise at the input voltage source. Connect a low ESR bulk capacitor (4.7µF to 10µF) to the input. Select this bulk capacitor to meet the input ripple requirements and voltage rating rather than capacitance value. Use the following equation to calculate the maximum RMS input current:

$$I_{RMS} = \frac{I_{OUT}}{V_{IN}} \sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}$$

#### **Output Capacitor Selection**

Ceramic capacitors with low-ESR values have the lowest output voltage ripple and are recommended. At nominal load current, the device operates in PWM mode, and the RMS ripple current is calculated as:

$$I_{RMSCout} = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f} \times \frac{1}{2 \times \sqrt{3}}$$

At nominal load current, the device operates in

PWM mode, and the overall output voltage ripple is the sum of the voltage spike caused by the output capacitor ESR plus the voltage ripple caused by charging and discharging the output capacitor:

$$\Delta V = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f} \times \left(\frac{1}{8 \times C_{OUT} \times f} + ESR\right)$$

At light load currents, the converter operates in pulse skipping mode, and the output voltage ripple is dependent on the capacitor and inductor values. Larger output capacitor and inductor values minimize the voltage ripple in PSM operation and tighten dc output accuracy in PSM operation.

#### **PC Board Layout Considerations**

A good circuit board layout aids in extracting the most performance from the WD1305E20. Poor circuit layout degrades the output ripple and the electromagnetic interference (EMI) or electromagnetic compatibility (EMC) performance. The evaluation board layout is optimized for the WD1305E20. Use this layout for best performance. If this layout needs changing, use the following guidelines:

- 1. Use separate analog and power ground planes. Connect the sensitive analog circuitry (such as voltage divider components) to analog ground; connect the power components (such as input and output bypass capacitors) to power ground. Connect the two ground planes together near the load to reduce the effects of voltage dropped on circuit board traces. Locate C<sub>IN</sub> as close to the V<sub>IN</sub> pin as possible, and use separate input bypass capacitors for the analog.

- 2. Route the high current path from  $C_{\text{IN}}$ , through L, to the SW and PGND pins as short as possible.

- 3. Keep high current traces as short and as wide as possible.

- 4. Place the feedback resistors as close as possible to the FB pin to prevent noise pickup.

- Avoid routing high impedance traces, such as FB, near the high current traces and

components or near the switch node (SW).

If high impedance traces are routed near high current and/or the SW node, place a ground plane shield between the traces.

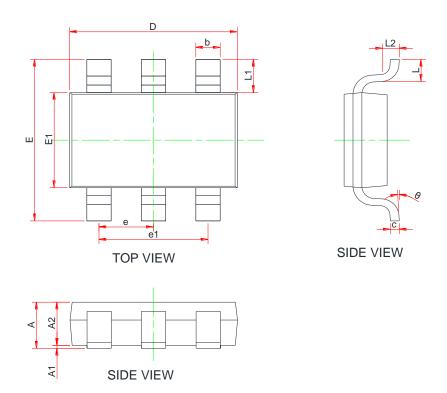

# **PACKAGE OUTLINE DIMENSIONS**

# SOT-23-6L

| Comple of | Dimensions in Millimeters |      |      |  |  |

|-----------|---------------------------|------|------|--|--|

| Symbol    | Min.                      | Тур. | Max. |  |  |

| A         | -                         | -    | 1.45 |  |  |

| A1        | 0                         | -    | 0.15 |  |  |

| A2        | 0.90                      | 1.10 | 1.30 |  |  |

| b         | 0.30                      | 0.40 | 0.50 |  |  |

| С         | 0.10                      | -    | 0.21 |  |  |

| D         | 2.72                      | 2.92 | 3.12 |  |  |

| E         | 2.60                      | 2.80 | 3.00 |  |  |

| E1        | 1.40                      | 1.60 | 1.80 |  |  |

| е         | 0.85                      | 0.95 | 1.05 |  |  |

| e1        | 1.80                      | 1.90 | 2.00 |  |  |

| L         | 0.30                      | -    | 0.60 |  |  |

| L1        | 0.59Ref                   |      |      |  |  |

| L2        | 0.25Ref                   |      |      |  |  |

| θ         | 0 °                       | -    | 8 °  |  |  |

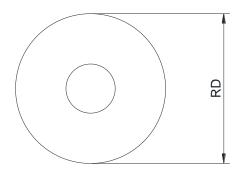

# TAPE AND REEL INFORMATION

## **Reel Dimensions**

#

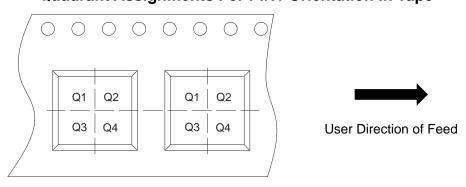

# **Quadrant Assignments For PIN1 Orientation In Tape**

| RD   | Reel Dimension                          | <b>☑</b> 7inch | ☐ 13inch |             |      |

|------|-----------------------------------------|----------------|----------|-------------|------|

| W    | Overall width of the carrier tape       | <b>▼</b> 8mm   | ☐ 12mm   | ☐ 16mm      |      |

| P1   | Pitch between successive cavity centers | ☐ 2mm          | ✓ 4mm    | ☐ 8mm       |      |

| Pin1 | Pin1 Quadrant                           | □ Q1           | □ Q2     | <b>✓</b> Q3 | □ Q4 |