# 额定2A双路 H 桥电机驱动器(完美替换DRV8833& MP6507)

- 1 特性

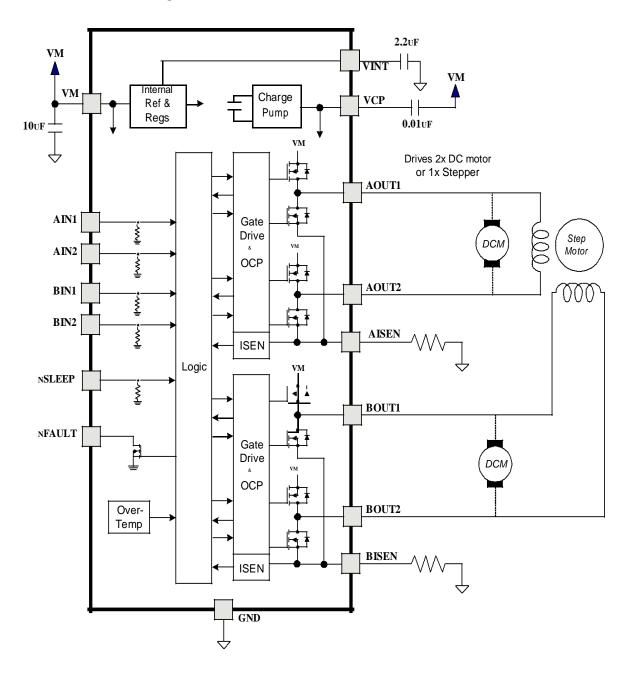

- 双路 H 桥电流控制电机驱动器

- 可以驱动两部直流电机或一部步进电机

- 低金属氧化物半导体场效应晶体管 (MOSFET)

导通电阻: 高侧 (HS) + 低侧 (LS) 360mΩ

- 输出电流(V<sub>M</sub> = 5V, 25°C 时)

- 采用 HTSSOP16 封装:每条 H 桥的 RMS 电流为 1A,峰值电流为 1.3A

- 采用QFN16 封装:每条 H 桥的 RMS 电流为 0.9A,峰值电流为 1.2A

- 可以将输出并联,以实现

2A RMS 电流、2.6A 峰值流(HTSSOP16封装)

1.8A RMS 电流、2.2A 峰值流(QFN16封装)

- T.OA KWS 电流、2.2A 峰值流、GFI

宽电源电压范围:

- 2.7V 至 10.8V

- PWM 绕组电流调节/电流限制

- 耐热增强型表面贴装封装

## 2 应用

- 电池供电式玩具

- 服务点 (POS) 打印机

- 视频安保摄像机

- 办公自动化设备

- 游戏机

- 机器人

# 3 说明

HT8833 器件为玩具、打印机及其他机电一体化应用 提供了一款双桥电机驱动器解决方案。

该器件具有两个 H 桥驱动器,能够驱动两部直流刷式 电机、一部双极步进电机、多个螺线管或其他感性负 载。

每个 H 桥的输出驱动器模块由配置为 H 桥的 N 沟道功 率 MOSFET 组成,用于驱动电机绕组。每个 H 桥均 具备调节或限制绕组电流的电路。

该器件利用故障输出引脚实现内部关断功能,提供过流 保护、短路保护、欠压锁定和过热保护。另外,还提供 了一种低功耗休眠模式。

HT8833B采用带有带有散热器的超薄型密脚封装,且 支持特殊封装外形的订制。(环保型:符合 RoHS 标 准且 不含锑/溴)。

# 4 订购信息

| PART NUMBER | PACKAGE     | BODY SIZE         |

|-------------|-------------|-------------------|

| HT8833BRSZ  | HTSSOP (16) | 5.00 mm × 6.40 mm |

| HT8833BRQZ  | QFN (16)    | 3.00 mm × 3.00 mm |

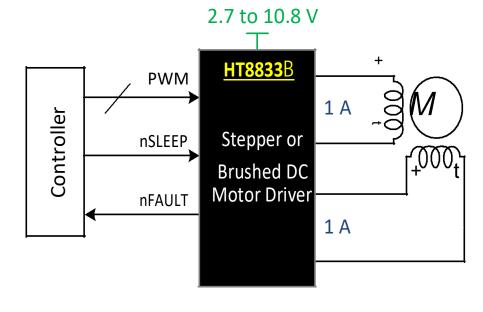

简化电路原理图

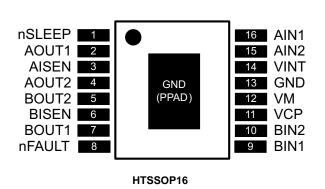

# **5** Pin Configuration and Functions

### **Pin Functions**

|           | PIN        |                  |       |                                                |                                                                                                                             |

|-----------|------------|------------------|-------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| NAME      | WQFN       | HTSSOP,<br>TSSOP | 1/0.7 | DESCRIPTION                                    | EXTERNAL COMPONENTS<br>OR CONNECTIONS                                                                                       |

| POWER AND | O GROUND   |                  |       |                                                |                                                                                                                             |

| GND       | 11<br>PPAD | 13               | _     | Device ground. HTSSOP package<br>has PowerPAD. | Both the GND pin and device PowerPAD must be connected to ground.                                                           |

| VINT      | 12         | 14               | _     | Internal supply bypass                         | Bypass to GND with 2.2-μF, 6.3-V capacitor.                                                                                 |

| VM        | 10         | 12               | _     | Device power supply                            | Connect to motor supply. A 10-µF<br>(minimum) ceramic bypass capacitor to<br>GND is recommended.                            |

| VCP       | 9          | 11               | IO    | High-side gate drive voltage                   | Connect a 0.01-µF, 16-V (minimum) X7R ceramic capacitor to VM.                                                              |

| CONTROL   |            |                  |       |                                                |                                                                                                                             |

| AIN1      | 14         | 16               | I     | Bridge A input 1                               | Logic input controls state of AOUT1.<br>Internal pulldown.                                                                  |

| AIN2      | 13         | 15               | I     | Bridge A input 2                               | Logic input controls state of AOUT2.<br>Internal pulldown.                                                                  |

| BIN1      | 7          | 9                | I     | Bridge B input 1                               | Logic input controls state of BOUT1.<br>Internal pulldown.                                                                  |

| BIN2      | 8          | 10               | I     | Bridge B input 2                               | Logic input controls state of BOUT2.<br>Internal pulldown.                                                                  |

| nSLEEP    | 15         | 1                | I     | Sleep mode input                               | Logic high to enable device, logic low to<br>enter low-power sleep mode and reset all<br>internal logic. Internal pulldown. |

(1) I = Input, O = Output, OZ = Tri-state output, OD = Open-drain output, IO = Input/output

# Pin Functions (continued)

| DIN  | - | un (1) |            |  |

|------|---|--------|------------|--|

| WOFN |   |        | DECODIDION |  |

|      |   |        |            |  |

|      |   |        |            |  |

|      |   |        |            |  |

|      |   |        |            |  |

|      |   |        |            |  |

|      |   |        |            |  |

|      |   |        |            |  |

|      |   |        |            |  |

|      |   |        |            |  |

# 6 Specifications

\_\_\_\_

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|     |                            | MIN                                          | MAX             | VIT |

|-----|----------------------------|----------------------------------------------|-----------------|-----|

| \/M | Power subdu voltage        | _0 3                                         | 11 R            | V   |

|     | Digital input his valtage  | <u> ۲</u>                                    | 7               |     |

|     |                            | <u>^                                    </u> | 0 F             |     |

|     | Bard and the second second | L                                            | . 0. 1977 977 1 | ۸   |

| -   | • · · · · ·                |                                              |                 | ^   |

| i   | -                          |                                              |                 | -   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

| <br> | - |  |

|------|---|--|

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

$T_A = 25^{\circ}C$  (unless otherwise noted)

(1) RDS(ON) increases and maximum output current is reduced at VM supply voltages below 5 V.

(2)  $V_{M} = 5 V$ , power dissipation and thermal limits must be observed.

### 6.4 Thermal Information

# 6.5 Electrical Characteristics

$T_A = 25^{\circ}C$  (unless otherwise noted)

|                | PARAMETER                                                 | TEST CONDITIONS                                                                                 | MIN | TYP        | MAX      | UNIT     |

|----------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|------------|----------|----------|

| POWER S        | UPPLY                                                     |                                                                                                 |     |            |          |          |

| VM             | VM operating supply current                               | V <sub>M</sub> = 5 V, xIN1 = 0 V, xIN2 = 0 V                                                    |     | 1.7        | 3        | mA       |

| VMQ            | VM sleep mode supply current                              | $V_{M} = 5 V$                                                                                   |     | 1.6        | 2.5      | μA       |

| UVLO           | VM undervoltage lockout voltage                           | V <sub>M</sub> falling                                                                          |     |            | 2.6      | V        |

| V              | VM undervoltage lockout                                   |                                                                                                 |     |            |          |          |

| HYS            | hysteresis                                                |                                                                                                 |     | 90         |          | mV       |

|                | EVEL INPUTS                                               | т <u>г</u>                                                                                      |     |            |          |          |

| /              | the state of the state of                                 | nSLEEP                                                                                          |     |            | 0.5      |          |

| L              | Input low voltage                                         | All other pins                                                                                  |     |            | 0.7      | V        |

| V              |                                                           | nSLEEP                                                                                          | 2.5 |            |          |          |

| IH             | Input high voltage                                        | All other pins                                                                                  | 2   |            |          | V        |

| HYS            | Input hysteresis                                          |                                                                                                 |     | 0.4        |          | V        |

| R              |                                                           | nSLEEP                                                                                          |     | 500        |          |          |

| PD             | Input pulldown resistance                                 | All except nSLEEP                                                                               |     | 150        |          | kΩ       |

| L              | Input low current                                         | VIN = 0                                                                                         |     |            | 1        | μA       |

|                |                                                           | VIN = 3.3 V, nSLEEP                                                                             |     | 6.6        | 13       |          |

| IH             | Input high current                                        | VIN = 3.3 V, all except nSLEEP                                                                  |     | 16.5       | 33       | μΑ       |

| DEG            | Input deglitch time                                       |                                                                                                 |     | 450        |          | ns       |

| nFAULT (       | OUTPUT (OPEN-DRAIN OUTPUT)                                | · · · · ·                                                                                       |     |            | •        |          |

| V<br>OL        | Output low voltage                                        | IO = 5 mA                                                                                       |     |            | 0.5      | V        |

| ОН             | Output high leakage current                               | V <sub>O</sub> = 3.3 V                                                                          |     |            | 1        | μA       |

| H-BRIDGI       |                                                           |                                                                                                 |     |            |          | •        |

|                |                                                           | V <sub>M</sub> = 5 V, I <sub>O</sub> = 500 mA, T <sub>J</sub> = 25°C                            |     | 200        |          |          |

|                |                                                           | V <sub>M</sub> = 5 V, I <sub>O</sub> = 500 mA, T <sub>J</sub> = 85°C                            |     |            | 325      |          |

|                | HS FET on resistance                                      | V <sub>M</sub> = 2.7 V, I <sub>O</sub> = 500 mA, T <sub>J</sub> = 25°C                          |     | 250        |          |          |

| R              |                                                           | V <sub>M</sub> = 2.7 V, I <sub>O</sub> = 500 mA, T <sub>J</sub> = 85°C                          |     |            | 350      |          |

| DS(ON)         |                                                           | $V_{\rm M} = 5 \text{ V}, 1 \text{ O} = 500 \text{ mA}, \text{ T}_{\rm J} = 25^{\circ}\text{C}$ |     | 160        |          | mΩ       |

|                |                                                           | $V_{M} = 5 V, I_{Q} = 500 mA, T_{J} = 85^{\circ}C$                                              |     | 100        | 275      |          |

|                | LS FET on resistance                                      | $V_{M} = 2.7 \text{ V}, I_{O} = 500 \text{ mA}, T_{J} = 25^{\circ}\text{C}$                     |     | 200        | 210      |          |

|                |                                                           | $V_{M} = 2.7 \text{ V}, I_{Q} = 500 \text{ mA}, T_{J} = 85^{\circ}\text{C}$                     |     | 200        | 300      |          |

| OFF            | Off-state leakage current                                 | $V_{M} = 5 V, T_{J} = 25^{\circ}C, V_{OUT} = 0 V$                                               | -1  |            | 1        | μA       |

|                | 0                                                         | ·M - • •, •, •, = 20 •, •001 - • •                                                              | I   |            | 1        | μπ       |

| J<br>PWM       | Current control PWM frequency                             | Internal PWM frequency                                                                          |     | 50         |          | kHz      |

| <sup>t</sup> R | Rise time                                                 | $V_{\rm M}$ = 5 V, 16 $\Omega$ to GND, 10% to 90% V <sub>M</sub>                                |     | 180        |          |          |

| tF             | Fall time                                                 | $V_{\rm M} = 5 \text{ V}, 16 \Omega \text{ to GND}, 10\% \text{ to 90\% V}_{\rm M}$             |     | 160        |          | ns       |

| PROP           |                                                           |                                                                                                 |     |            |          | ns       |

| PROP           | Propagation delay INx to OUTx<br>Dead time <sup>(1)</sup> | V <sub>M</sub> = 5 V<br>V = 5 V                                                                 |     | 1.1<br>450 |          | µs<br>ns |

| DEAD           | TION CIRCUITS                                             | м                                                                                               |     |            |          |          |

|                |                                                           | 1                                                                                               | 0   | 0.0        | <u> </u> |          |

| OCP            | Overcurrent protection trip level                         | ł                                                                                               | 2   | 3.3        |          | A        |

| DEG            | OCP Deglitch time                                         | <u> </u>                                                                                        | 4   |            |          | μs       |

| OCP<br>L       | Overcurrent protection period                             |                                                                                                 |     | 1.35       |          | ms       |

| TSD            | Thermal shutdown temperature                              | Die temperature                                                                                 | 150 | 160        | 180      | °C       |

(1) Internal dead time. External implementation is not necessary.

# **Electrical Characteristics**

$T_A = 25^{\circ}C$  (unless otherwise noted)

| PARAMETER   | TEST CONDITIONS | MIN | ТҮР              | ЛДХ | JIT |

|-------------|-----------------|-----|------------------|-----|-----|

|             |                 |     |                  |     |     |

|             |                 | 400 | 200              | 040 | .17 |

| ····· ····· |                 |     | ^ <del>-</del> - |     |     |

|             |                 |     |                  |     |     |

| 1           |                 |     |                  |     |     |

# 6.6 Typical Characteristics

# 7 Detailed Description

# 7.1 Overview

The HT8833 device is an integrated motor driver solution for brushed DC or bipolar stepper motors. The device integrates two NMOS H-bridges and current regulation circuitry. The HT8833 can be powered with a supply voltage from 2.7 to 10.8 V and can provide an output current up to 1.5-A RMS.

A simple PWM interface allows easy interfacing to the controller circuit.

The current regulation is a fixed frequency PWM slow decay.

The device includes a low-power sleep mode, which lets the system save power when not driving the motor.

## 7.2 Functional Block Diagram

### 7.3 Feature Description

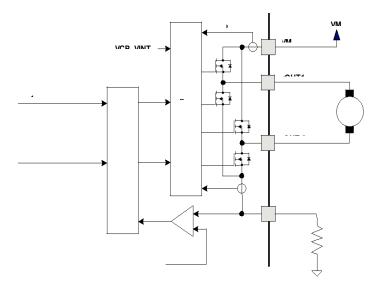

#### 7.3.1 Fixed-Frequency PWM Motor Drivers

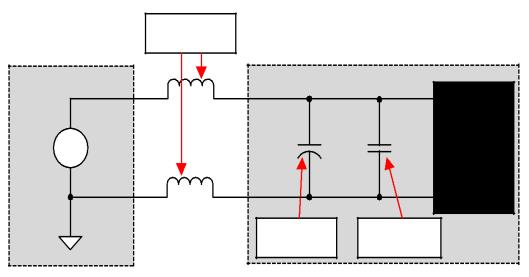

HT8833 contains two identical H-bridge motor drivers with current-control PWM circuitry. 🛽 5 shows a block diagram of the circuitry.

#### 图 5. Motor Control Circuitry

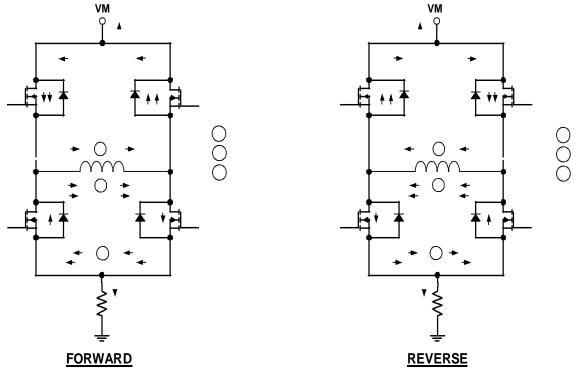

#### 7.3.2 Bridge Control and Decay Modes

The AIN1 and AIN2 input pins control the state of the AOUT1 and AOUT2 outputs; similarly, the BIN1 and BIN2 input pins control the state of the BOUT1 and BOUT2 outputs. 表 1 shows the logic.

#### 表 1. H-Bridge Logic

The inputs can also be used for PWM control of the motor speed. When controlling a winding with PWM, when the drive current is interrupted, the inductive nature of the motor requires that the current must continue to flow. This is called recirculation current. To handle this recirculation current, the H-bridge can operate in two different states: fast decay or slow decay. In fast decay mode, the H-bridge is disabled and recirculation current flows through the body diodes; in slow decay, the motor winding is shorted.

To PWM using fast decay, the PWM signal is applied to one xIN pin while the other is held low; to use slow decay, one xIN pin is held high.

| 表 2. | PWM | Control | of | Motor | Speed |

|------|-----|---------|----|-------|-------|

|------|-----|---------|----|-------|-------|

|  | • |

|--|---|

|  |   |

|  |   |

|  |   |

|  |   |

|  |   |

6 shows the current paths in different drive and decay modes.

图 6. Drive and Decay Modes

### 7.3.3 Current Control

The current through the motor windings may be limited, or controlled, by a fixed-frequency PWM current regulation, or current chopping. For DC motors, current control is used to limit the start-up and stall current of the motor. For stepper motors, current control is often used at all times.

When an H-bridge is enabled, current rises through the winding at a rate dependent on the DC voltage and inductance of the winding. If the current reaches the current chopping threshold, the bridge disables the current until the beginning of the next PWM cycle. Immediately after the current is enabled, the voltage on the xISEN pin is ignored for a fixed period of time before enabling the current sense circuitry. This blanking time is fixed at 3.75  $\mu$ s. This blanking time also sets the minimum on time of the PWM when operating in current chopping mode.

The PWM chopping current is set by a comparator which compares the voltage across a current sense resistor connected to the xISEN pins with a reference voltage. The reference voltage is fixed at 200 mV.

The chopping current is calculated in 公式 1.

Example: If a 1- $\Omega$  sense resistor is used, the chopping current will be 200 mV/1  $\Omega$  = 200 mA.

Once the chopping current threshold is reached, the H-bridge switches to slow decay mode. Winding current is recirculated by enabling both of the low-side FETs in the bridge. This state is held until the beginning of the next fixed-frequency PWM cycle.

If current control is not needed, the xISEN pins should be connected directly to ground.

#### 7.3.4 nSLEEP Operation

Driving nSLEEP low will put the device into a low power sleep state. In this state, the H-bridges are disabled, the gate drive charge pump is stopped, all internal logic is reset, and all internal clocks are stopped. All inputs are ignored until nSLEEP returns inactive high. When returning from sleep mode, some time (up to 1 ms) needs to pass before the motor driver becomes fully operational. To make the board design simple, the nSLEEP can be pulled up to the supply (VM). TI recommends using a pullup resistor when this is done. This resistor limits the current to the input in case VM is higher than 6.5 V. Internally, the nSLEEP pin has a 500-k $\Omega$  resistor to GND. It also has a clamping Zener diode that clamps the voltage at the pin at 6.5 V. Currents greater than 250  $\mu$ A can cause damage to the input structure. Hence the recommended pullup resistor would be between 20 k $\Omega$  and 75 k $\Omega$ .

#### 7.3.5 Protection Circuits

The HT8833 is fully protected against undervoltage, overcurrent and overtemperature events.

#### 7.3.5.1 Overcurrent Protection (OCP)

An analog current limit circuit on each FET limits the current through the FET by limiting the gate drive. If this analog current limit persists for longer than the OCP deglitch time, all FETs in the H-bridge will be disabled

and the nFAULT pin will be driven low. The driver will be re-enabled after the OCP retry period (t<sub>OCP</sub>) has passed. nFAULT becomes high again at this time. If the fault condition is still present, the cycle repeats. If the fault is no longer present, normal operation resumes and nFAULT remains deasserted. Please note that only the H-bridge in which the OCP is detected will be disabled while the other bridge will function normally.

Overcurrent conditions are detected independently on both high- and low-side devices; that is, a short to ground, supply, or across the motor winding will all result in an overcurrent shutdown. Overcurrent protection does not use the current sense circuitry used for PWM current control, so it functions even without presence of the xISEN resistors.

#### 7.3.5.2 Thermal Shutdown (TSD)

If the die temperature exceeds safe limits, all FETs in the H-bridge will be disabled and the nFAULT pin will be driven low. Once the die temperature has fallen to a safe level, operation will automatically resume.

#### 7.3.5.3 Undervoltage Lockout (UVLO)

If at any time the voltage on the VM pin falls below the undervoltage lockout threshold voltage, all circuitry in the device will be disabled, and all internal logic will be reset. Operation will resume when VM rises above the UVLO threshold. nFAULT is driven low in the event of an undervoltage condition.

| FAULT                     | CONDITION              | ERROR REPORT | H-BRIDGE | INTERNAL<br>CIRCUITS | RECOVERY               |

|---------------------------|------------------------|--------------|----------|----------------------|------------------------|

| VM undervoltage<br>(UVLO) | V <sub>M</sub> < 2.5 V | None         | Disabled | Disabled             | V <sub>M</sub> > 2.7 V |

| Overcurrent (OCP)         | OUT OCP                | FAULTn       | Disabled | Operating            | OCP                    |

| Thermal Shutdown<br>(TSD) | T > T<br>J TSD         | FAULTn       | Disabled | Operating            | T < T - T<br>J TSD HYS |

#### 表 3. Device Protection

#### 7.4 Device Functional Modes

The HT8833 is active unless the nSLEEP pin is brought logic low. In sleep mode, the H-bridge FETs are disabled (Hi-Z). The HT8833 is brought out of sleep mode automatically if nSLEEP is brought logic high. tWAKE must elapse before the outputs change state after wakeup.

| 表 4. Modes of Opera | ation |

|---------------------|-------|

|---------------------|-------|

| FAULT             | CONDITION               | H-BRIDGE  | INTERNAL CIRCUITS |

|-------------------|-------------------------|-----------|-------------------|

| Operating         | nSLEEP pin high         | Operating | Operating         |

| Sleep mode        | nSLEEP pin low          | Disabled  | Disabled          |

| Fault encountered | Any fault condition met | Disabled  | See 表 3           |

#### 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

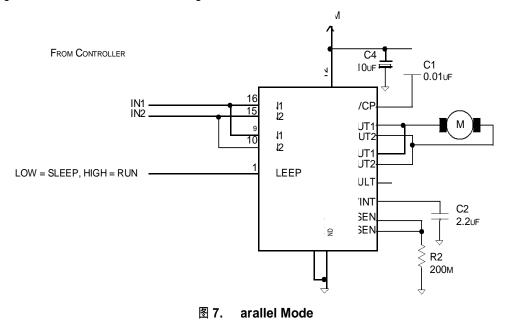

The HT8833 is used in brushed DC or stepper motor control. The following design procedure can be used to configure the HT8833 in a brushed DC motor application. The inputs and outputs are connected in parallel to achieve higher current.

#### 8.2 Typical Application

The two H-bridges in the HT8833 can be connected in parallel for double the current of a single H-bridge. The internal dead time in the HT8833 prevents any risk of cross-conduction (shoot-through) between the two bridges due to timing differences between the two bridges. 🛛 7 shows the connections.

#### 8.2.1 Design Requirements

| <b>5. Design Parameters</b> | 長 5. | Design | Parameters |

|-----------------------------|------|--------|------------|

|-----------------------------|------|--------|------------|

| DESIGN PARAMETER         | FERENCE   | EXAMPLE VALUE |

|--------------------------|-----------|---------------|

| Motor voltage            | VM        | 10 V          |

| Motor RMS current        | RMS       | 0.8 A         |

| Motor start-up current   | START     | 2 A           |

| Motor current trip point | I<br>TRIP | 2.5 A         |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Motor Voltage

The motor voltage to use will depend on the ratings of the motor selected and the desired RPM. A higher voltage spins a brushed DC motor faster with the same PWM duty cycle applied to the power FETs. A higher voltage also increases the rate of current change through the inductive motor windings.

### 8.2.2.2 Motor Current Trip Point

When the voltage on pin xISEN exceeds  $V_{TRIP}$  (0.2 V), current regulation is activated. The R<sub>ISENSE</sub> resistor should be sized to set the desired I<sub>CHOP</sub> level.

$R_{ISENSE} = 0.2 V / I_{CHOP}$

To set  $I_{CHOP}$  to 1 A,  $R_{SENSE}$  = 0.2 V / 1 A = 0.2  $\Omega$ .

#### 8.2.2.3 Sense Resistor

For optimal performance, it is important for the sense resistor to be:

- Surface-mount

- Low inductance

- Rated for high enough power

- · Placed closely to the motor driver

The power dissipated by the sense resistor equals  $I_{RMS}^2 \times R$ . For example, if peak motor current is 3 A, RMS motor current is 2 A, and a 0.05- $\Omega$  sense resistor is used, the resistor will dissipate 2 A<sup>2</sup> × 0.05  $\Omega$  = 0.2 W. The power quickly increases with higher current levels.

Resistors typically have a rated power within some ambient temperature range, along with a derated power curve for high ambient temperatures. When a PCB is shared with other components generating heat, margin should be added. For best practice, measure the actual sense resistor temperature in a final system, along with the power MOSFETs, as those are often the hottest components.

Because power resistors are larger and more expensive than standard resistors, the common practice is to use multiple standard resistors in parallel, between the sense node and ground. This distributes the current and heat dissipation.

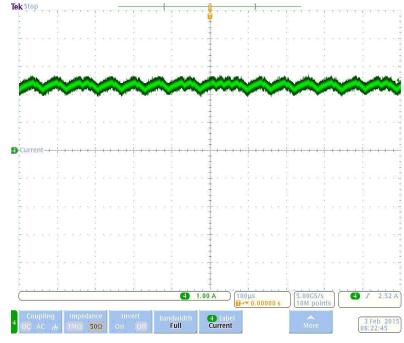

# 8.2.3 Application Curve

图 8. Current Regulation

(2)

# 9 Power Supply Recommendations

### 9.1 Bulk Capacitance

Having an appropriate local bulk capacitance is an important factor in motor drive system design. It is generally beneficial to have more bulk capacitance, while the disadvantages are increased cost and physical size.

The amount of local capacitance needed depends on a variety of factors, including:

- The highest current required by the motor system

- The capacitance and ability to source current

- · The amount of parasitic inductance between the power supply and motor system

- The acceptable voltage ripple

- The type of motor used (brushed DC, brushless DC, stepper)

- The motor braking method

The inductance between the power supply and the motor drive system limits the rate current can change from the power supply. If the local bulk capacitance is too small, the system responds to excessive current demands or dumps from the motor with a change in voltage. When adequate bulk capacitance is used, the motor voltage remains stable and high current can be quickly supplied.

The data sheet generally provides a recommended value, but system-level testing is required to determine the appropriate sized bulk capacitor.

图 9. Example Setup of Motor Drive System With External Power Supply

The voltage rating for bulk capacitors should be higher than the operating voltage, to provide margin for cases when the motor transfers energy to the supply.

## 9.2 Power Supply and Logic Sequencing

There is no specific sequence for powering up the HT8833. The presence of digital input signals is acceptable before VM is applied. After VM is applied to the HT8833, the device begins operation based on the status of the control pins.

## 10 Layout

### 10.1 Layout Guidelines

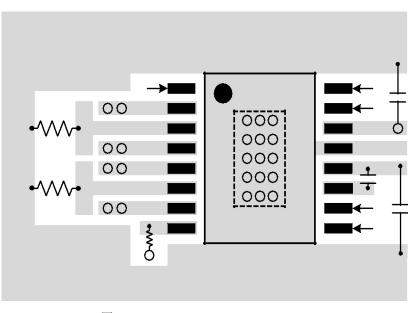

The VM pin should be bypassed to GND using low-ESR ceramic bypass capacitors with a recommended value of  $10-\mu$ F rated for VM. This capacitor should be placed as close to the VM pin as possible with a thick trace or ground plane connection to the device GND pin.

A low-ESR ceramic capacitor must be placed in between the VM and VCP pins. TI recommends a value of 0.01  $\mu$ F rated for 16 V. Place this component as close to the pins as possible.

Bypass VINT to ground with a 2.2-µF ceramic capacitor rated 6.3 V. Place this bypass capacitor as close to the pin as possible.

#### 10.1.1 Heatsinking

The PowerPAD package uses an exposed pad to remove heat from the device. For proper operation, this pad must be thermally connected to copper on the PCB to dissipate heat. On a multilayer PCB with a ground plane, this can be accomplished by adding a number of vias to connect the thermal pad to the ground plane. On PCBs without internal planes, copper area can be added on either side of the PCB to dissipate heat. If the copper area is on the opposite side of the PCB from the device, thermal vias are used to transfer the heat between top and bottom layers.

In general, the more copper area that can be provided, the more power can be dissipated.

注 The PW package option is not thermally enhanced and TI recommends adhering to the power dissipation limits.

### 10.2 Layout Example

图 10. Recommended Layout Example

# **10.3 Thermal Considerations**

## 10.3.1 Maximum Output Current

In actual operation, the maximum output current achievable with a motor driver is a function of die temperature. This, in turn, is greatly affected by ambient temperature and PCB design. Basically, the maximum motor current will be the amount of current that results in a power dissipation level that, along with the thermal resistance of the package and PCB, keeps the die at a low enough temperature to stay out of thermal shutdown.

The dissipation ratings given in the data sheet can be used as a guide to calculate the approximate maximum power dissipation that can be expected to be possible without entering thermal shutdown for several different PCB constructions. However, for accurate data, the actual PCB design must be analyzed through measurement or thermal simulation.

### 10.3.2 Thermal Protection

The HT8833 has thermal shutdown (TSD) as described above. If the die temperature exceeds approximately 150°C, the device will be disabled until the temperature drops by 45°C.

Any tendency of the device to enter TSD is an indication of either excessive power dissipation, insufficient heatsinking, or too high an ambient temperature.

# **10.4 Power Dissipation**

Power dissipation in the HT8833 is dominated by the DC power dissipated in the output FET resistance, or

R<sub>DS(ON)</sub>. There is additional power dissipated due to PWM switching losses, which are dependent on PWM frequency, rise and fall times, and VM supply voltages. These switching losses are typically on the order of 10% to 30% of the DC power dissipation.

The DC power dissipation of one H-bridge can be roughly estimated by  $\Delta \pm 3$ .

$3_{\text{TOT}} + 6 \pm 5_{\text{DS(ON)}} u$ ,  $2/6 \pm 5_{\text{DS(ON)}} u$ , 2

where

- PTOT is the total power dissipation

- · HS RDS(ON) is the resistance of the high-side FET

- LS R<sub>DS(ON)</sub> is the resistance of the low-side FET

- · IOUT(RMS) is the RMS output current being applied to the motor

(3)

R<sub>DS(ON)</sub> increases with temperature, so as the device heats, the power dissipation increases. This must be taken into consideration when sizing the heatsink.

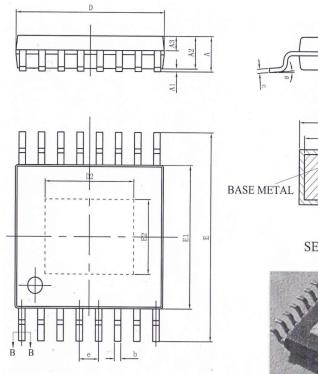

# HT8833B

# HTSSOP16

| E C       |    |    |  |

|-----------|----|----|--|

|           |    |    |  |

|           | b  |    |  |

| 1         | b1 |    |  |

|           | 4  | 10 |  |

| ASE METAL |    |    |  |

WITH PLATING

SECTION B-B

| SYMBOL | MILLIMETER |      |             |  |

|--------|------------|------|-------------|--|

| SIMBOL | MIN        | NOM  | MAX         |  |

| А      | _          |      | 1.20        |  |

| A1     | 0.05       |      | 0.15        |  |

| A2     | 0.90       | 1.00 | 1.05        |  |

| A3     | 0.39       | 0.44 | 0.49        |  |

| b      | 0.20       | _    | 0.28        |  |

| b1     | 0.19       | 0.22 | 0.25        |  |

| с      | 0.13       |      | 0.17        |  |

| c1     | 0.12       | 0.13 | 0.14        |  |

| D      | 4.90       | 5.00 | 5.10        |  |

| Е      | 6.20       | 6.40 | 6.60        |  |

| E1 -   | 4.30       | 4.40 | 4.50        |  |

| e      | 0.65BSC    |      |             |  |

| L      | 0.45       | -    | 0.75        |  |

| L1     | 1.00BSC    |      |             |  |

| θ      | 0          | _    | $8^{\circ}$ |  |

| Size(mm)<br>L/F Size<br>(mil) | D2      | E2       |

|-------------------------------|---------|----------|

| 91*118                        | 2.80REF | 2. 10REF |

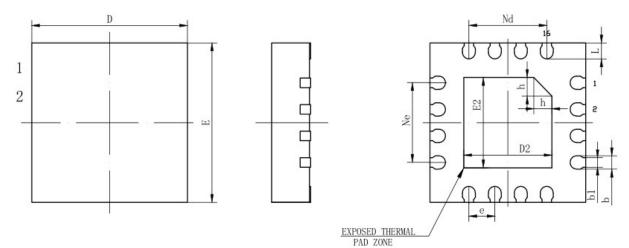

# HT8833B

# QFNP16-3\*3

TOP VIEW

BOTTOM VIEW

| SYMBOL     | MILLIMETER |      |      |  |

|------------|------------|------|------|--|

|            | MIN        | NOM  | MAX  |  |

| А          | 0.70       | 0.75 | 0.80 |  |

| A1         | 0          | 0.02 | 0.05 |  |

| b          | 0.18       | 0.25 | 0.30 |  |

| b1         | 0.18REF    |      |      |  |

| с          | 0.203REF   |      |      |  |

| D          | 2.90       | 3.00 | 3.10 |  |

| <b>D</b> 2 | 1.60       | 1.70 | 1.80 |  |

| e          | 0. 50BSC   |      |      |  |

| Ne         | 1. 50BSC   |      |      |  |

| Nd         | 1.50BSC    |      |      |  |

| Е          | 2.90       | 3.00 | 3.10 |  |

| E2         | 1.60       | 1.70 | 1.80 |  |

| L          | 0.25       | 0.30 | 0.35 |  |

| h          | 0.30       | 0.35 | 0.40 |  |