# 4Gb DDR3 SDRAM

Lead-Free&Halogen-Free (RoHS Compliant) H5TQ4G83EFR-xxC H5TQ4G83EFR-xxI H5TQ4G83EFR-xxL H5TQ4G63EFR-xxC H5TQ4G63EFR-xxI H5TQ4G63EFR-xxL H5TQ4G63EFR-xxJ

\* SK Hynix reserves the right to change products or specifications without notice.

# **Revision History**

| Revision No. | History         | Draft Date | Remark |

|--------------|-----------------|------------|--------|

| 0.1          | Initial Version | Mar. 2016  |        |

### Description

The H5TQ4G83EFR-xxC,H5TQ4G63EFR-xxC, H5TQ4G83EFR-xxI, H5TQ4G63EFR-xxI, H5TQ4G63EFR-xxI, H5TQ4G63EFR-xxL, H5TQ4G63EFR-xxJ and H5TQ4G63EFR-xxJ are a 4,294,967,296-bit CMOS Double Data Rate III (DDR3) Synchronous DRAM, ideally suited for the main memory applications which requires large memory density and high bandwidth. SK Hynix 4Gb DDR3 SDRAMs offer fully synchronous operations referenced to both rising and falling edges of the clock. While all addresses and control inputs are latched on the rising edges of the CK (falling edges of the CK), Data, Data strobes and Write data masks inputs are sampled on both rising and falling edges of it. The data paths are internally pipelined and 8-bit prefetched to achieve very high bandwidth.

#### **Device Features and Ordering Information**

#### **FEATURES**

- VDD=VDDQ=1.5V +/- 0.075V

- Fully differential clock inputs (CK, CK) operation

- Differential Data Strobe (DQS, DQS)

- On chip DLL align DQ, DQS and DQS transition with CK transition

- DM masks write data-in at the both rising and falling edges of the data strobe

- All addresses and control inputs except data, data strobes and data masks latched on the rising edges of the clock

- Programmable CAS latency 5, 6, 7, 8, 9, 10, 11, 13 and 14 supported

- Programmable additive latency 0, CL-1, and CL-2 supported

- Programmable CAS Write latency (CWL) = 5, 6, 7, 8

9 and 10

- Programmable burst length 4/8 with both nibble sequential and interleave mode

- · BL switch on the fly

- 8banks

- Average Refresh Cycle (Tcase of 0 °C~95 °C)

- 7.8 μs at 0°C ~ 85 °C - 3.9 μs at 85°C ~ 95 °C Commercial Temperature( 0°C ~ 95 °C) Industrial Temperature( -40°C ~ 95 °C)

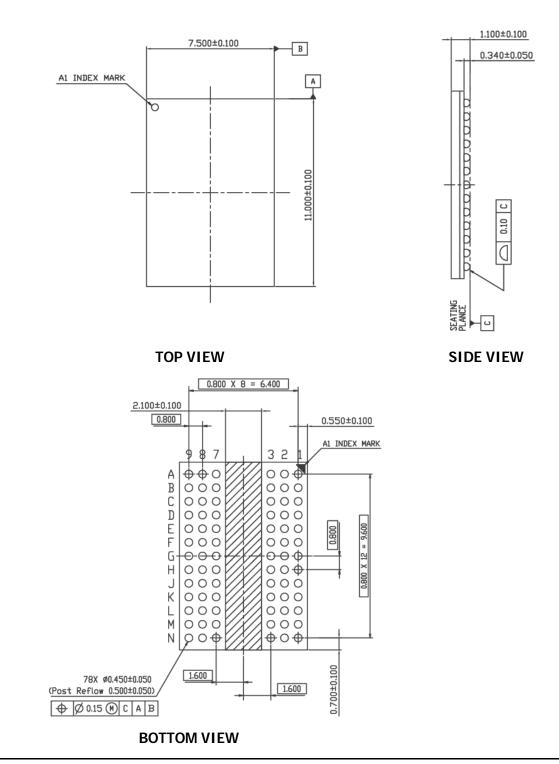

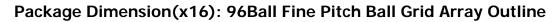

- JEDEC standard 78ball FBGA(x8), 96ball FBGA (x16)

- Driver strength selected by EMRS

- Dynamic On Die Termination supported

- Asynchronous RESET pin supported

- ZQ calibration supported

- TDQS (Termination Data Strobe) supported (x8 only)

- Write Levelization supported

- 8 bit pre-fetch

#### \* This product in compliance with the RoHS directive.

#### ORDERING INFORMATION

| Part No.                             | Configuration | Power Consumption     | Temperature | Package      |

|--------------------------------------|---------------|-----------------------|-------------|--------------|

| H5TQ4G83EFR-*xxC                     |               | Normal Consumption    | Commercial  |              |

| H5TQ4G83EFR-*xxI                     | 512M x 8      | Normal consumption    | Industrial  | 78ball FBGA  |

| H5TQ4G83EFR-*xxL                     |               | Low Power Consumption | Commercial  | 700all 1 DGA |

| H5TQ4G83EFR-*xxJ                     |               | (IDD6 Only)           | Industrial  |              |

| H5TQ4G63EFR-*xxC                     |               | Normal Consumption    | Commercial  |              |

| H5TQ4G63EFR-*xxI                     | 256M x 16     | Normal consumption    | Industrial  | 96ball FBGA  |

| H5TQ4G63EFR-*xxL<br>H5TQ4G63EFR-*xxJ | 250IVI X 10   | Low Power Consumption | Commercial  | 900ali FDGA  |

|                                      |               | (IDD6 Only)           | Industrial  |              |

\* xx means Speed Bin Grade

#### **OPERATING FREQUENCY**

| Speed<br>Grade | Frequency [Mbps] |     |      |      |      |      |      |      |      |      | Remark             |  |  |  |

|----------------|------------------|-----|------|------|------|------|------|------|------|------|--------------------|--|--|--|

| (Marking)      | CL5              | CL6 | CL7  | CL8  | CL9  | CL10 | CL11 | CL12 | CL13 | CL14 | (CL-tRCD-tRP)      |  |  |  |

| -H9            | 667              | 800 | 1066 | 1066 | 1333 | 1333 |      |      |      |      | DDR3-1333 9-9-9    |  |  |  |

| -PB            | 667              | 800 | 1066 | 1066 | 1333 | 1333 | 1600 |      |      |      | DDR3-1600 11-11-11 |  |  |  |

| -RD*           |                  | 800 | 1066 | 1066 | 1333 | 1333 | 1600 |      | 1866 |      | DDR3-1866 13-13-13 |  |  |  |

| -TE            |                  | 800 | 1066 | 1066 | 1333 | 1333 | 1600 |      | 1866 | 2133 | DDR3-2133 14-14-14 |  |  |  |

\*Note1: In case of 1.5V P/N (H5TQ4G8(6)3EFR), -RDC covers Lower speed of -PBC and -H9C

п

|   | 1      | 2     | 3   | 4 | 5 | 6 | 7       | 8      | 9    |   |   |

|---|--------|-------|-----|---|---|---|---------|--------|------|---|---|

|   |        |       | 1   | 1 |   |   |         |        |      |   |   |

| Α | VSS    | VDD   | NC  |   |   |   | NF/TDQS | VSS    | VDD  |   | Α |

| В | VSS    | VSSQ  | DQ0 |   |   |   | DM/TDQS | VSSQ   | VDDQ |   | В |

| С | VDDQ   | DQ2   | DQS |   |   |   | DQ1     | DQ3    | VSSQ |   | С |

| D | VSSQ   | DQ6   | DQS |   |   |   | VDD     | VSS    | VSSQ |   | D |

| Е | VREFDQ | VDDQ  | DQ4 |   |   |   | DQ7     | DQ5    | VDDQ |   | Е |

| F | NC     | VSS   | RAS |   |   |   | СК      | VSS    | NC   |   | F |

| G | ODT    | VDD   | CAS |   |   |   | СК      | VDD    | CKE  |   | G |

| н | NC     | CS    | WE  |   |   |   | A10/AP  | ZQ     | NC   |   | Н |

| J | VSS    | BA0   | BA2 |   |   |   | A15     | VREFCA | VSS  |   | J |

| к | VDD    | A3    | A0  |   |   |   | A12/BC  | BA1    | VDD  |   | к |

| L | VSS    | A5    | A2  |   |   |   | A1      | A4     | VSS  |   | L |

| м | VDD    | A7    | A9  |   |   |   | A11     | A6     | VDD  |   | М |

| Ν | VSS    | RESET | A13 |   |   |   | A14     | A8     | VSS  |   | Ν |

|   |        |       |     |   |   |   |         |        |      |   |   |

|   | 1      | 2     | 3   | 4 | 5 | 6 | 7       | 8      | 9    | l |   |

#### x8 Package Ball out (Top view): 78ball FBGA Package

| A 0000<br>B 0000<br>C 0000<br>E 0000<br>F 0000<br>H 0000<br>K 0000<br>K<br>K 0000<br>K<br>K<br>K<br>K |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N 000 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

(Top View: See the balls through the Package)

O Populated ball+ Ball not populated

Г

|   | 1      | 2     | 3    | 4 | 5 | 6 | 7      | 8      | 9    |  |   |

|---|--------|-------|------|---|---|---|--------|--------|------|--|---|

|   |        |       |      | 1 |   |   |        |        |      |  |   |

| Α | VDDQ   | DQU5  | DQU7 |   |   |   | DQU4   | VDDQ   | VSS  |  | Α |

| В | VSSQ   | VDD   | VSS  |   |   |   | DQSU   | DQU6   | VSSQ |  | В |

| С | VDDQ   | DQU3  | DQU1 |   |   |   | DQSU   | DQU2   | VDDQ |  | С |

| D | VSSQ   | VDDQ  | DMU  |   |   |   | DQU0   | VSSQ   | VDD  |  | D |

| Е | VSS    | VSSQ  | DQL0 |   |   |   | DML    | VSSQ   | VDDQ |  | Е |

| F | VDDQ   | DQL2  | DQSL |   |   |   | DQL1   | DQL3   | VSSQ |  | F |

| G | VSSQ   | DQL6  | DQSL |   |   |   | VDD    | VSS    | VSSQ |  | G |

| н | VREFDQ | VDDQ  | DQL4 |   |   |   | DQL7   | DQL5   | VDDQ |  | н |

| J | NC     | VSS   | RAS  |   |   |   | СК     | VSS    | NC   |  | J |

| к | ODT    | VDD   | CAS  |   |   |   | СК     | VDD    | CKE  |  | к |

| L | NC     | CS    | WE   |   |   |   | A10/AP | ZQ     | NC   |  | L |

| м | VSS    | BA0   | BA2  |   |   |   | NC     | VREFCA | VSS  |  | М |

| Ν | VDD    | A3    | A0   |   |   |   | A12/BC | BA1    | VDD  |  | Ν |

| Р | VSS    | A5    | A2   |   |   |   | A1     | A4     | VSS  |  | Р |

| R | VDD    | A7    | A9   |   |   |   | A11    | A6     | VDD  |  | R |

| т | VSS    | RESET | A13  |   |   |   | A14    | A8     | VSS  |  | Т |

|   |        |       |      |   |   |   |        |        |      |  |   |

|   | 1      | 2     | 3    | 4 | 5 | 6 | 7      | 8      | 9    |  |   |

### x16 Package Ball out (Top view): 96ball FBGA Package

(Top View: See the balls through the Package)

O Populated ball

+ Ball not populated

# **Pin Functional Description**

| Symbol                                                                  | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СК, СК                                                                  | Input | Clock: CK and $\overline{CK}$ are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of $\overline{CK}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CKE, (CKE0),<br>(CKE1)                                                  | Input | Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and output drivers. Taking CKE Low provides Precharge Power-Down and Self-Refresh operation (all banks idle), or Active Power-Down (row Active in any bank).<br>CKE is asynchronous for Self-Refresh exit. After VREFCA and VREFDQ have become stable during the power on and initialization sequence, they must be maintained during all operations (including Self-Refresh). CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, CK, ODT and CKE, are disabled during power-down. Input buffers, excluding CKE, are disabled during Self-Refresh. |

| <u>CS</u> , ( <u>CS</u> 0),<br>( <u>CS1), (CS2</u> ),<br>( <u>CS3</u> ) | Input | Chip Select: All commands are masked when $\overline{CS}$ is registered HIGH.<br>$\overline{CS}$ provides for external Rank selection on systems with multiple Ranks.<br>$\overline{CS}$ is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ODT, (ODT0),<br>(ODT1)                                                  | Input | On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR3 SDRAM. When enabled, ODT is only applied to each DQ, DQS, $\overline{\text{DQS}}$ and DM/TDQS, NU/TDQS (When TDQS is enabled via Mode Register A11=1 in MR1) signal for x4/x8 configurations. For x16 configuration, ODT is applied to each DQ, DQSU, $\overline{\text{DQSU}}$ , DQSL, $\overline{\text{DQSL}}$ , DMU, and DML signal. The ODT pin will be ignored if MR1 is programmed to disable ODT.                                                                                                                                                                                                   |

| $\frac{\overline{RAS}}{CAS}, \overline{WE}$                             | Input | Command Inputs: $\overline{RAS}$ , $\overline{CAS}$ and $\overline{WE}$ (along with $\overline{CS}$ ) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DM, (DMU),<br>(DML)                                                     | Input | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS. For x8 device, the function of DM or TDQS/TDQS is enabled by Mode Register A11 setting in MR1.                                                                                                                                                                                                                                                                                                                                                                                                      |

| BA0 - BA2                                                               | Input | Bank Address Inputs: BA0 - BA2 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines if the mode register or extended mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A0 - A15                                                                | Input | Address Inputs: Provide the row address for Active commands and the column address for Read/Write commands to select one location out of the memory array in the respective bank. (A10/AP and A12/BC have additional functions, see below). The address inputs also provide the op-code during Mode Register Set commands.                                                                                                                                                                                                                                                                                                                                                                              |

| A10 / AP                                                                | Input | Auto-precharge: A10 is sampled during Read/Write commands to determine whether<br>Autoprecharge should be performed to the accessed bank after the Read/Write operation.<br>(HIGH: Autoprecharge; LOW: no Autoprecharge).A10 is sampled during a Precharge<br>command to determine whether the Precharge applies to one bank (A10 LOW) or all<br>banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by bank<br>addresses.                                                                                                                                                                                                                                                     |

| A12 / BC                                                                | Input | Burst Chop: A12 / BC is sampled during Read and Write commands to determine if burst chop (on-the-fly) will be performed.<br>(HIGH, no burst chop; LOW: burst chopped). See command truth table for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Symbol                                                                             | Туре              | Function                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                                                                              | Input             | Active Low Asynchronous Reset: Reset is active when RESET is LOW, and inactive when RESET is HIGH. RESET must be HIGH during normal operation.<br>RESET is a CMOS rail-to-rail signal with DC high and low at 80% and 20% of V <sub>DD</sub> , i.e. 1.20V for DC high and 0.30V for DC low.                                                                                                                               |

| DQ                                                                                 | Input /<br>Output | Data Input/ Output: Bi-directional data bus.                                                                                                                                                                                                                                                                                                                                                                              |

| DQU, <u>DQL</u> ,<br>DQS, <u>DQS</u> ,<br>DQSU, <u>DQSU</u> ,<br>DQSL, <u>DQSL</u> | Input /<br>Output | Data Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. The data strobe DQS, DQSL, and DQSU are paired with differential signals DQS, DQSL, and DQSU, respectively, to provide differential pair signaling to the system during reads and writes. DDR3 SDRAM supports differential data strobe only and does not support single-ended.                            |

| TDQS, TDQS                                                                         | Output            | Termination Data Strobe: TDQS/TDQS is applicable for x8 DRAMs only. When enabled via Mode Register A11 = 1 in MR1, the DRAM will enable the same termination resistance function on TDQS/TDQS that is applied to DQS/DQS. When disabled via mode register A11 = 0 in MR1, DM/TDQS will provide the data mask function and TDQS is not used. x4/x16 DRAMs must disable the TDQS function via mode register A11 = 0 in MR1. |

| NC                                                                                 |                   | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                 |

| NF                                                                                 |                   | No Function                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>DDQ</sub>                                                                   | Supply            | DQ Power Supply: 1.5 V +/- 0.075 V                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>SSQ</sub>                                                                   | Supply            | DQ Ground                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>DD</sub>                                                                    | Supply            | Power Supply: 1.5 V +/- 0.075 V                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS</sub>                                                                    | Supply            | Ground                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>REFDQ</sub>                                                                 | Supply            | Reference voltage for DQ                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>REFCA</sub>                                                                 | Supply            | Reference voltage for CA                                                                                                                                                                                                                                                                                                                                                                                                  |

| ZQ                                                                                 | Supply            | Reference Pin for ZQ calibration                                                                                                                                                                                                                                                                                                                                                                                          |

#### Note:

Input only pins (BA0-BA2, A0-A15, RAS, CAS, WE, CS, CKE, ODT, DM, and RESET) do not supply termination.

#### ROW AND COLUMN ADDRESS TABLE

#### 4Gb

| Configuration          | 512Mb x 8 | 256Mb x 16 |

|------------------------|-----------|------------|

| # of Banks             | 8         | 8          |

| Bank Address           | BA0 - BA2 | BA0 - BA2  |

| Auto precharge         | A10/AP    | A10/AP     |

| BL switch on the fly   | A12/BC    | A12/BC     |

| Row Address            | A0 - A15  | A0 - A14   |

| Column Address         | A0 - A9   | A0 - A9    |

| Page size <sup>1</sup> | 1 KB      | 2 KB       |

**Note1:** Page size is the number of bytes of data delivered from the array to the internal sense amplifiers when an ACTIVE command is registered. Page size is per bank, calculated as follows:

page size = 2  $^{\text{COLBITS}}$  \* ORG  $\div$  8

where COLBITS = the number of column address bits, ORG = the number of I/O (DQ) bits

### **Absolute Maximum Ratings**

#### **Absolute Maximum DC Ratings**

#### **Absolute Maximum DC Ratings**

| Symbol                             | Parameter                           | Rating           | Units | Notes |

|------------------------------------|-------------------------------------|------------------|-------|-------|

| VDD                                | Voltage on VDD pin relative to Vss  | - 0.4 V ~ 1.80 V | V     | 1,3   |

| VDDQ                               | Voltage on VDDQ pin relative to Vss | - 0.4 V ~ 1.80 V | V     | 1,3   |

| V <sub>IN</sub> , V <sub>OUT</sub> | Voltage on any pin relative to Vss  | - 0.4 V ~ 1.80 V | V     | 1     |

| T <sub>STG</sub>                   | Storage Temperature                 | -55 to +100      | °C    | 1, 2  |

Notes:

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

- 3. VDD and VDDQ must be within 300mV of each other at all times; and VREF must not be greater than 0.6XVDDQ,When VDD and VDDQ are less than 500mV; VREF may be equal to or less than 300mV.

### DRAM Component Operating Temperature Range

#### **Temperature Range**

| Symbol            | Parameter                          | Rating     | Units | Notes |

|-------------------|------------------------------------|------------|-------|-------|

|                   | Normal Operating Temperature Range | 0 to 85    | °C    | 1,2   |

| T <sub>OPER</sub> | Extended Temperature Range         | 85 to 95   | °C    | 1,4   |

|                   | Industrial Temperature Range       | 0 to 85 °C | °C    | 1,3,4 |

#### Notes:

- 1. Operating Temperature TOPER is the case surface temperature on the center / top side of the DRAM. For measurement conditions, please refer to the JEDEC document JESD51-2.

- 2. The Normal Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be maintained between 0 - 85oC under all operating conditions.

- 3. The Industrial Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be maintained between -40 - 85oC under all operating conditions.

- 4. Some applications require operation of the DRAM in the Extended Temperature Range between 85oC and 95oC case temperature. Full specifications are guaranteed in this range, but the following additional conditions apply:

- a. Refresh commands must be doubled in frequency, therefore reducing the Refresh interval tREFI to 3.9 µs.

- b. If Self-Refresh operation is required in the Extended Temperature Range, then it is mandatory to use the Manual Self-Refresh mode with Extended Temperature Range capability (MR2 A6 = 0b and MR2 A7 = 1b).

# AC & DC Operating Conditions

### **Recommended DC Operating Conditions**

### **Recommended DC Operating Conditions**

|        | _                         |       | Rating |       |       |       |

|--------|---------------------------|-------|--------|-------|-------|-------|

| Symbol | Parameter                 | Min.  | Тур.   | Max.  | Units | Notes |

| VDD    | Supply Voltage            | 1.425 | 1.500  | 1.575 | V     | 1,2   |

| VDDQ   | Supply Voltage for Output | 1.425 | 1.500  | 1.575 | V     | 1,2   |

Notes:

1. Under all conditions, VDDQ must be less than or equal to VDD.

2. VDDQ tracks with VDD. AC parameters are measured with VDD and VDDQ tied together.

### IDD and IDDQ Specification Parameters and Test Conditions

#### IDD and IDDQ Measurement Conditions

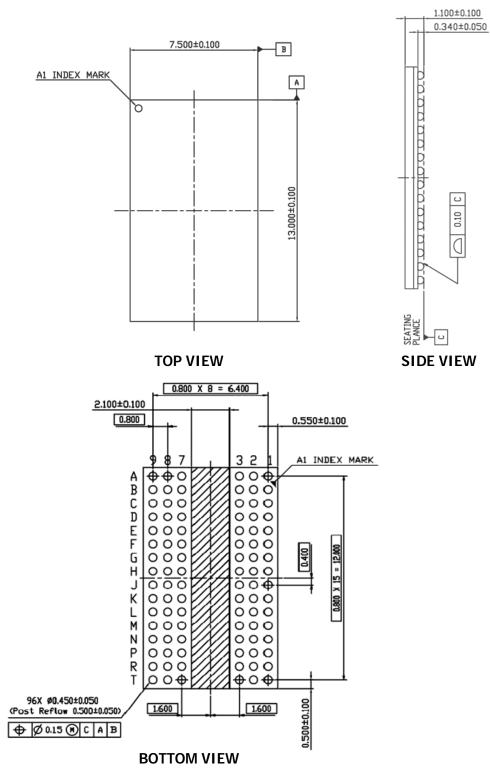

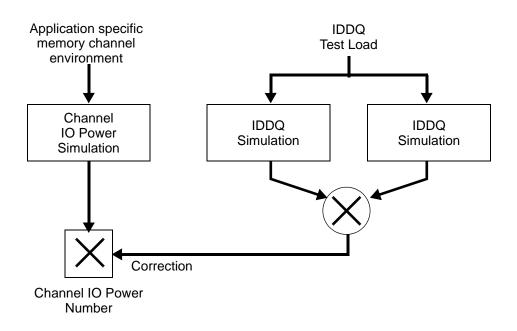

In this chapter, IDD and IDDQ measurement conditions such as test load and patterns are defined. Figure 1. shows the setup and test load for IDD and IDDQ measurements.

- IDD currents (such as IDD0, IDD1, IDD2N, IDD2NT, IDD2P0, IDD2P1, IDD2Q, IDD3N, IDD3P, IDD4R, IDD4W, IDD5B, IDD6, IDD6ET, and IDD7) are measured as time-averaged currents with all VDD balls of the DDR3 SDRAM under test tied together. Any IDDQ current is not included in IDD currents.

- IDDQ currents (such as IDDQ2NT and IDDQ4R) are measured as time-averaged currents with all VDDQ balls of the DDR3 SDRAM under test tied together. Any IDD current is not included in IDDQ currents.

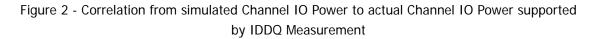

Attention: IDDQ values cannot be directly used to calculate IO power of the DDR3 SDRAM. They can be used to support correlation of simulated IO power to actual IO power as outlined in Figure 2. In DRAM module application, IDDQ cannot be measured separately since VDD and VDDQ are using one merged-power layer in Module PCB.

For IDD and IDDQ measurements, the following definitions apply:

- "0" and "LOW" is defined as VIN  $\leq V_{ILAC(max)}$ .

- "1" and "HIGH" is defined as VIN  $>= V_{IHAC(max)}$ .

- "MID\_LEVEL" is defined as inputs are VREF = VDD/2.

- Timing used for IDD and IDDQ Measurement-Loop Patterns are provided in Table 1.

- Basic IDD and IDDQ Measurement Conditions are described in Table 2.

- Detailed IDD and IDDQ Measurement-Loop Patterns are described in Table 3 through Table 10.

- IDD Measurements are done after properly initializing the DDR3 SDRAM. This includes but is not limited to setting RON = RZQ/7 (34 Ohm in MR1);

- $\begin{array}{l} \mbox{Qoff} = \mbox{0}_B \mbox{ (Output Buffer enabled in MR1);} \\ \mbox{RTT_Nom} = \mbox{RZQ/6} \mbox{ (40 Ohm in MR1);} \\ \mbox{RTT_Wr} = \mbox{RZQ/2} \mbox{ (120 Ohm in MR2);} \\ \end{array}$

- TDQS Feature disabled in MR1

- Attention: The IDD and IDDQ Measurement-Loop Patterns need to be executed at least one time before actual IDD or IDDQ measurement is started.

- Define D = { $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$ }:= {HIGH, LOW, LOW, LOW}

- Define  $\overline{D} = \{\overline{CS}, \overline{RAS}, \overline{CAS}, \overline{WE}\} := \{HIGH, HIGH, HIGH, HIGH\}$

Figure 1 - Measurement Setup and Test Load for IDD and IDDQ (optional) Measurements [Note: DIMM level Output test load condition may be different from above]

Rev. 0.1/ Mar 2016

|                         | Sumbol           | DDR3-1066 | DDR3-1333 | DDR3-1600 | DDR3-1866 | DDR3-2133 | Unit |

|-------------------------|------------------|-----------|-----------|-----------|-----------|-----------|------|

|                         | Symbol           | 7-7-7     | 9-9-9     | 11-11-11  | 13-13-13  | 14-14-14  | Unit |

| t <sub>CK</sub>         |                  | 1.875     | 1.5       | 1.25      | 1.07      | 0.935     | ns   |

| CL                      |                  | 7         | 9         | 11        | 13        | 14        | nCK  |

| <i>n</i> <sub>RCD</sub> |                  | 7         | 9         | 11        | 13        | 14        | nCK  |

| n <sub>RC</sub>         |                  | 27        | 33        | 39        | 45        | 50        | nCK  |

| n <sub>RAS</sub>        |                  | 20        | 24        | 28        | 32        | 36        | nCK  |

| n <sub>RP</sub>         |                  | 7         | 9         | 11        | 13        | 14        | nCK  |

|                         | 1KB page<br>size | 20        | 20        | 24        | 26        | 27        | nCK  |

| n <sub>FAW</sub>        | 2KB page<br>size | 27        | 30        | 32        | 33        | 38        | nCK  |

|                         | 1KB page<br>size | 4         | 4         | 5         | 5         | 6         | nCK  |

| n <sub>RRD</sub>        | 2KB page<br>size | 6         | 5         | 6         | 6         | 7         | nCK  |

| n <sub>RFC</sub> -      | 512Mb            | 48        | 60        | 72        | 85        | 97        | nCK  |

| n <sub>RFC</sub> -1     | 1 Gb             | 59        | 74        | 88        | 103       | 118       | nCK  |

| n <sub>RFC</sub> -      | 2 Gb             | 86        | 107       | 128       | 150       | 172       | nCK  |

| n <sub>RFC</sub> -      | 4 Gb             | 139       | 174       | 208       | 243       | 279       | nCK  |

| n <sub>RFC</sub> - 8 Gb |                  | 187       | 234       | 280       | 328       | 375       | nCK  |

### Table 1 -Timings used for IDD and IDDQ Measurement-Loop Patterns

#### Table 2 - Basic IDD and IDDQ Measurement Conditions

| Symbol                  | Description                                                                                                          |

|-------------------------|----------------------------------------------------------------------------------------------------------------------|

|                         | Operating One Bank Active-Precharge Current                                                                          |

|                         | CKE: High; External clock: On; tCK, nRC, nRAS, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: High between ACT    |

| 1                       | and PRE; Command, Address, Bank Address Inputs: partially toggling according to Table 3; Data IO:                    |

| <b>I</b> <sub>DD0</sub> | MID-LEVEL; DM: stable at 0; Bank Activity: Cycling with one bank active at a time: 0,0,1,1,2,2, (see                 |

|                         | Table 3); Output Buffer and RTT: Enabled in Mode Registers <sup>b)</sup> ; ODT Signal: stable at 0; Pattern Details: |

|                         | see Table 3.                                                                                                         |

| Symbol                     | Description                                                                                                          |  |  |  |  |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| (                          | Operating One Bank Active-Precharge Current                                                                          |  |  |  |  |  |  |  |

| C                          | CKE: High; External clock: On; tCK, nRC, nRAS, nRCD, CL: see Table 1; BL: 8 <sup>a)</sup> ; AL: 0; CS: High between  |  |  |  |  |  |  |  |

| <b>/</b>                   | ACT, RD and PRE; Command, Address; Bank Address Inputs, Data IO: partially toggling according to                     |  |  |  |  |  |  |  |

| <b>/</b> <sub>DD1</sub>    | Table 4; DM: stable at 0; Bank Activity: Cycling with on bank active at a time: 0,0,1,1,2,2, (see Table              |  |  |  |  |  |  |  |

| 4                          | 4); Output Buffer and RTT: Enabled in Mode Registers <sup>b)</sup> ; ODT Signal: stable at 0; Pattern Details: see   |  |  |  |  |  |  |  |

| L                          | Table 4.                                                                                                             |  |  |  |  |  |  |  |

| F                          | Precharge Standby Current                                                                                            |  |  |  |  |  |  |  |

| (                          | CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a)</sup> ; AL: 0; CS: stable at 1; Command, Address, |  |  |  |  |  |  |  |

| I <sub>dd2n</sub> E        | Bank Address Inputs: partially toggling according to Table 5; Data IO: MID_LEVEL; DM: stable at 0;                   |  |  |  |  |  |  |  |

| E                          | Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode Registers <sup>b)</sup> ; ODT Signal: stable |  |  |  |  |  |  |  |

| а                          | at 0; Pattern Details: see Table 5.                                                                                  |  |  |  |  |  |  |  |

| F                          | Precharge Standby ODT Current                                                                                        |  |  |  |  |  |  |  |

| C                          | CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a)</sup> ; AL: 0; CS: stable at 1; Command, Address, |  |  |  |  |  |  |  |

| I <sub>dd2nt</sub> E       | Bank Address Inputs: partially toggling according to Table 6; Data IO: MID_LEVEL; DM: stable at 0;                   |  |  |  |  |  |  |  |

| E                          | Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode Registers <sup>b)</sup> ; ODT Signal: tog-   |  |  |  |  |  |  |  |

| ç                          | gling according to Table 6; Pattern Details: see Table 6.                                                            |  |  |  |  |  |  |  |

| F                          | Precharge Power-Down Current Slow Exit                                                                               |  |  |  |  |  |  |  |

| C                          | CKE: Low; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a)</sup> ; AL: 0; CS: stable at 1; Command, Address,  |  |  |  |  |  |  |  |

| I <sub>DD2P0</sub> E       | Bank Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks closed;              |  |  |  |  |  |  |  |

| C                          | Output Buffer and RTT: Enabled in Mode Registers <sup>b)</sup> ; ODT Signal: stable at 0; Precharge Power Down       |  |  |  |  |  |  |  |

| Ν                          | Mode: Slow Exit <sup>c)</sup>                                                                                        |  |  |  |  |  |  |  |

| F                          | Precharge Power-Down Current Fast Exit                                                                               |  |  |  |  |  |  |  |

| C                          | CKE: Low; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a)</sup> ; AL: 0; CS: stable at 1; Command, Address,  |  |  |  |  |  |  |  |

| <b>/<sub>DD2P1</sub></b> Е | Bank Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks closed;              |  |  |  |  |  |  |  |

| C                          | Output Buffer and RTT: Enabled in Mode Registers <sup>b)</sup> ; ODT Signal: stable at 0; Precharge Power Down       |  |  |  |  |  |  |  |

| Ν                          | Mode: Fast Exit <sup>c)</sup>                                                                                        |  |  |  |  |  |  |  |

| F                          | Precharge Quiet Standby Current                                                                                      |  |  |  |  |  |  |  |

|                            | CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a)</sup> ; AL: 0; CS: stable at 1; Command, Address, |  |  |  |  |  |  |  |

| <b>J</b> DD2Q              | Bank Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks closed;              |  |  |  |  |  |  |  |

| C                          | Output Buffer and RTT: Enabled in Mode Registers <sup>b)</sup> ; ODT Signal: stable at 0                             |  |  |  |  |  |  |  |

| Active Standby Current         Active Standby Current         CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a)</sup> ; AL: 0; CS: stable at 1; Command, Addr         Bank Address Inputs: partially toggling according to Table 5; Data IO: MID_LEVEL; DM: stable at 0;         Bank Activity: all banks open; Output Buffer and RTT: Enabled in Mode Registers <sup>b)</sup> ; ODT Signal: sta         at 0; Pattern Details: see Table 5.         Active Power-Down Current         CKE: Low; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a)</sup> ; AL: 0; CS: stable at 1; Command, Addr         Bank Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks op         Output Buffer and RTT: Enabled in Mode Registers <sup>b)</sup> ; ODT Signal: stable at 0         Operating Burst Read Current         CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: High between RD; Command         Address, Bank Address Inputs: partially toggling according to Table 7; Data IO: seamless read data b         with different data between one burst and the next one according to Table 7; DM: stable at 0; Bank         Activity: all banks open, RD commands cycling through banks: 0,0,1,1,2,2,(see Table 7); Output Buf |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JDD3N       Bank Address Inputs: partially toggling according to Table 5; Data IO: MID_LEVEL; DM: stable at 0;         Bank Activity: all banks open; Output Buffer and RTT: Enabled in Mode Registers <sup>b</sup> ); ODT Signal: state at 0; Pattern Details: see Table 5.         Active Power-Down Current         CKE: Low; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: stable at 1; Command, Addr         Bank Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks op         Output Buffer and RTT: Enabled in Mode Registers <sup>b</sup> ; ODT Signal: stable at 0         Operating Burst Read Current         CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: High between RD; Comman         Address, Bank Address Inputs: partially toggling according to Table 7; DAta IO: seamless read data b         with different data between one burst and the next one according to Table 7; DM: stable at 0; Bank                                                                                                                                                                                                                                                                                               |

| At 0; Pattern Details: see Table 5.         Active Power-Down Current         CKE: Low; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: stable at 1; Command, Addr         Bank Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks op         Output Buffer and RTT: Enabled in Mode Registers <sup>b</sup> ); ODT Signal: stable at 0         Operating Burst Read Current         CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: High between RD; Comman         Address, Bank Address Inputs: partially toggling according to Table 7; Data IO: seamless read data b         with different data between one burst and the next one according to Table 7; DM: stable at 0; Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IDD3P       CKE: Low; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: stable at 1; Command, Addr         Bank Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks op         Output Buffer and RTT: Enabled in Mode Registers <sup>b</sup> ); ODT Signal: stable at 0         Operating Burst Read Current         CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: High between RD; Comman         Address, Bank Address Inputs: partially toggling according to Table 7; Data IO: seamless read data b         with different data between one burst and the next one according to Table 7; DM: stable at 0; Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| JDD3P       Bank Address Inputs: stable at 0; Data IO: MID_LEVEL; DM: stable at 0; Bank Activity: all banks op<br>Output Buffer and RTT: Enabled in Mode Registers <sup>b</sup> ; ODT Signal: stable at 0         Operating Burst Read Current       Operating Burst Read Current         CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: High between RD; Comman<br>Address, Bank Address Inputs: partially toggling according to Table 7; Data IO: seamless read data b<br>with different data between one burst and the next one according to Table 7; DM: stable at 0; Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Joda       Operating Burst Read Current         CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: High between RD; Comman         Address, Bank Address Inputs: partially toggling according to Table 7; Data IO: seamless read data b         with different data between one burst and the next one according to Table 7; DM: stable at 0; Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Joda       Operating Burst Read Current         CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: High between RD; Comman         Address, Bank Address Inputs: partially toggling according to Table 7; Data IO: seamless read data b         with different data between one burst and the next one according to Table 7; DM: stable at 0; Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>J</b> <sub>DD4R</sub> Address, Bank Address Inputs: partially toggling according to Table 7; Data IO: seamless read data b with different data between one burst and the next one according to Table 7; DM: stable at 0; Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>7</b> DD4R with different data between one burst and the next one according to Table 7; DM: stable at 0; Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| and RTT: Enabled in Mode Registers <sup>b)</sup> ; ODT Signal: stable at 0; Pattern Details: see Table 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Operating Burst Write Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CKE: High; External clock: On; tCK, CL: see Table 1; BL: 8 <sup>a</sup> ); AL: 0; CS: High between WR; Commar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Address, Bank Address Inputs: partially toggling according to Table 8; Data IO: seamless read data b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>V</b> <sub>DD4W</sub> with different data between one burst and the next one according to Table 8; DM: stable at 0; Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Activity: all banks open, WR commands cycling through banks: 0,0,1,1,2,2,(see Table 8); Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| fer and RTT: Enabled in Mode Registers <sup>b)</sup> ; ODT Signal: stable at HIGH; Pattern Details: see Table 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Burst Refresh Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CKE: High; External clock: On; tCK, CL, nRFC: see Table 1; BL: 8 <sup>a)</sup> ; AL: 0; CS: High between REF; C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Ирото mand, Address, Bank Address Inputs: partially toggling according to Table 9; Data IO: MID_LEVEL;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| stable at 0; Bank Activity: REF command every nREF (see Table 9); Output Buffer and RTT: Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Mode Registers <sup>b)</sup> ; ODT Signal: stable at 0; Pattern Details: see Table 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |