## FlexInput IC for automotive applications

#### **Features**

- AEC-Q100 qualified

- 12 V and 24 V systems compatible (operating battery supply voltage 5.5 V-36 V)

- Programmable interface with 15 total inputs:

- 12 for connection to external analog loads (with connection to VVAR, VDD5 and clamped battery VPRE, with resistance measurement)

- 4 with also λ sensor functionality

- 4 with also SENT functionality

- 3 for connection to external digital switches (with connection to VPRE)

- Programmable pull-up/down current sources

- Integrated precise resistance measurements

- · 12 bit ADC for voltage measurements

- 15 bit ADC for resistance measurements

- Variable reluctance sensor / Hall sensor Interface

- 1 analog output channel + 4 digital output channels

- SPI interface for device configuration and data communication

- · Overtemperature protection

- Thermal resistance R<sub>th(j-c)</sub> = 3 K/W

# Product status link L9966 Product summary Order code L9966CB-TR

**Package**

**Packing**

TQFP48

Tape and reel

### **Description**

The L9966 is an automotive grade IC designed to be used as sensors interface. Up to 15 channels are available for analog sensing, resistance measurement and digital sensing (e.g. temperature, lambda, pressure, position sensors).

The L9966 allows replacing a number of discrete components and it gives the possibility to change the sensors across different applications without modifying the PCB hardware.

Target applications are Engine Control Units and Body/Chassis Modules.

GADG0401180943PS

## 1 Block diagram

VT5V VDD5 VDD5REF VDDREF VOLTAGE REFERENCE GENERATOR IO[12:1] 5V REF VADC 1 REF Vref=2.8V CMP th3

CMP th2

CMP th1 MUX IO\_5 : IO\_8 IO[12:1] **₽** ANALOG IO[15:1] CMP th3 Vref=1.25V ∑Delta ADC 1 12 bit IO\_1 : IO\_4 ANALOG / SENT 500κΩ 🕽 SENT1 / GTM1 CMP th3 IO\_9: IO\_12 3<u>.3</u>V ANALOG / LAMBDA from ADC 1 INT CTRL\_CFG from SENT cs from ADC 1 SEQUENCER from ADC 2 EU 1 EU 2 CLK MOSI SCLK SPI CMP th3 MISO MISO THRESHOLD adaption IO\_13:IO\_15 VRSP ADC1 voltage dividers -> Full Scale R\_GND 🖁 🖁 GND

Figure 1. Block diagram

DB3718 - Rev 1 page 2/11

# 2 Pin description

10\_1 10\_12 12 90 8 0 6<u>0</u> 7\_0 S S 48 46 45 44 43 42 41 40 39 38 37 RR3 36 **RST** RR2 2 35 SS\_CLK RR1 3 34 SS\_CS R\_GND 4 33 MOSI VRSP 5 MISO **VRSN** 6 31 SYNC GND 7 VDD5V 30 VDD5REF 8 29 INT AOX 9 SENT1\_GTM1 28 VT5V 10 27 SENT2\_GTM2 VRS\_OUT 11 26 SENT3\_GTM3 VI5V 25 SENT4\_GTM4 17 18 19 20 21 22 23 24 CTRL\_CFG 0 GADG0401181015PS

Figure 2. Pin connection diagram

**Table 1. Pin description**

| Pin-Nr. | Pin-name  | Description                                   | Pin-class (1) |

|---------|-----------|-----------------------------------------------|---------------|

| 1       | RR3       | Reference Pullup Resistor 3 for R-Measurement | I             |

| 2       | RR2       | Reference Pullup Resistor 2 for R-Measurement | I             |

| 3       | RR1       | Reference Pullup Resistor 1 for R-Measurement | I             |

| 4       | R_GND (2) | Reference Ground for high accuracy signals    | I             |

| 5       | VRSP      | Positive variable reluctance sensor input     | Α             |

| 6       | VRSN      | Negative variable reluctance sensor input     | А             |

DB3718 - Rev 1 page 3/11

| Pin-Nr. | Pin-name   | Description                                                                                  | Pin-class (1) |  |

|---------|------------|----------------------------------------------------------------------------------------------|---------------|--|

| 7       | GND        | Ground for supply voltage                                                                    |               |  |

| 8       | VDD5REF    | Positive reference to both ADC                                                               |               |  |

| 9       | AOX        | Analog output for input channel x                                                            |               |  |

| 10      | VT5V       | Ratiometric Voltage output VI5V                                                              |               |  |

| 11      | VRS_Out    | Digital Output of Variable reluctance sensor                                                 |               |  |

| 12      | VI5V       | nput Voltage                                                                                 |               |  |

| 13      | nc         | Not connected                                                                                | -             |  |

| 14      | VTX        | Ratiometric Voltage output VIX                                                               |               |  |

| 15      | VIX        | Input Voltage output VIX                                                                     |               |  |

| 16      | CTRL_CFG   | Input to control current source / Configuration input to select SPI Address-Mux during Reset | I             |  |

| 17      | IO_13      | Flexible Input and current output 13                                                         | D             |  |

| 18      | IO_14      | Flexible Input and current output 14                                                         | D             |  |

| 19      | IO_15      | Flexible Input and current output 15                                                         | D             |  |

| 20      | IO_1       | Flexible Input and current output 1 / SENT1                                                  | Α             |  |

| 21      | IO_2       | Flexible Input and current output 2 / SENT2                                                  | Α             |  |

| 22      | IO_3       | Flexible Input and current output 3 / SENT3                                                  | Α             |  |

| 23      | IO_4       | Flexible Input and current output 4 / SENT4                                                  | Α             |  |

| 24      | nc         | Not connected                                                                                | -             |  |

| 25      | SENT4_GTM4 | Digital Output for SENT 4 channel / GTM_TO_SENT_4                                            | I             |  |

| 26      | SENT3_GTM3 | Digital Output for SENT 3 channel r/ GTM_TO_SENT_3                                           | I             |  |

| 27      | SENT2_GTM2 | Digital Output for SENT 2 channel / GTM_TO_SENT_2                                            | I             |  |

| 28      | SENT1_GTM1 | Digital Output for SENT 1 channel / GTM_TO_SENT_1                                            | I             |  |

| 29      | INT        | Interrupt (result status for controller)                                                     | I             |  |

| 30      | VDD5V      | 5 V Power supply                                                                             | 1             |  |

| 31      | SYNC       | Digital input to synchronize sequencer start                                                 | I             |  |

| 32      | MISO       | Communication interface clock for Master-IN/ Slave-OUT                                       | 1             |  |

| 33      | MOSI       | Communication interface for Master-OUT/ Slave-IN                                             | I             |  |

| 34      | CS         | Communication interface chip select                                                          | I             |  |

| 35      | SCLK       | Communication interface clock                                                                | I             |  |

| 36      | RST        | Reset                                                                                        | I             |  |

| 37      | nc         | Not connected                                                                                | -             |  |

| 38      | nc         | Not connected                                                                                | -             |  |

| 39      | IO_12      | Flexible Input and current output 12 / LAMBDA                                                | Α             |  |

| 40      | IO_11      | Flexible Input and current output 11 / LAMBDA                                                | Α             |  |

| 41      | IO_10      | Flexible Input and current output 10 / LAMBDA                                                | Α             |  |

| 42      | IO_9       | Flexible Input and current output 9 / LAMBDA                                                 | Α             |  |

| 43      | IO_8       | Flexible Input and current output 8                                                          |               |  |

| 44      | IO_7       | Flexible Input and current output 7                                                          | Α             |  |

| 45      | IO_6       | Flexible Input and current output 6                                                          | Α             |  |

| 46      | IO_5       | Flexible Input and current output 5                                                          | Α             |  |

DB3718 - Rev 1 page 4/11

| F | in-Nr. | Pin-name | Description        | Pin-class (1) |

|---|--------|----------|--------------------|---------------|

|   | 47     | WAKE     | Output for wake-up | I             |

|   | 48     | UBSW     | Battery supply     | S             |

#### 1. see Pin-class legend:

2. R\_GND is the ground reference for ADC1, ADC2, VDD5REF voltage divider, input channel voltage dividers. In case R\_GND connection to ground on the PCB is lost, R\_GND is referenced one diode voltage drop above GND.

#### Pin-class legend:

- I: ECU Internal Pins: connection to other electrical components on the ECU (Local pins).

- Supply Pins: connection to supply sources with protected battery supply (Local pins except UBSW that is a global pin).

- A: Analog Inputs: connection to external ECU pins (Global pin).

- **D:** Digital Inputs: connection to external ECU pins (Global pin).

DB3718 - Rev 1 page 5/11

# 3 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

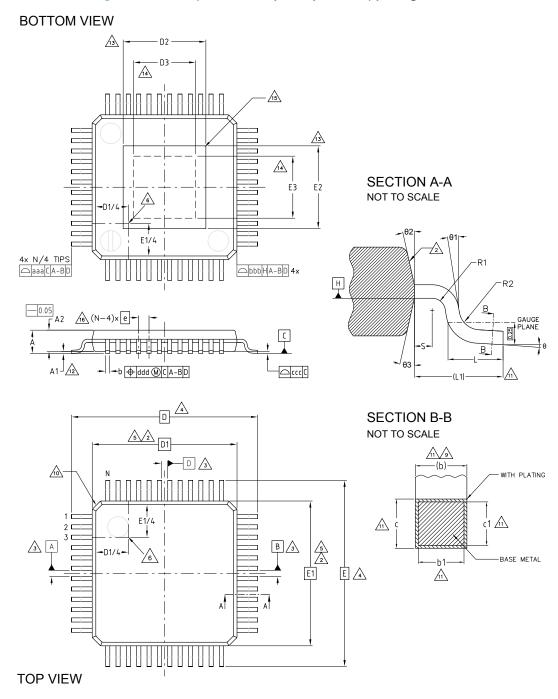

## 3.1 TQFP48 (7x7x1 mm exposed pad down) package information

Figure 3. TQFP48 (7x7x1 mm exposed pad down) package outline

DB3718 - Rev 1 page 6/11

Table 2. TQFP48 (7x7x1 mm exp. pad down) package mechanical data

|        | Dimensions |                        |      |        |

|--------|------------|------------------------|------|--------|

| Symbol | Min.       | Тур.                   | Max. | - Note |

| Θ      | 0°         | 3.5°                   | 7°   |        |

| Θ1     | 0°         | -                      | -    |        |

| Θ2     | 11°        | 12°                    | 13°  |        |

| Θ3     | 11°        | 12°                    | 13°  |        |

| A      | -          | -                      | 1.20 | 15     |

| A1     | 0.05       | -                      | 0.15 | 12     |

| A2     | 0.95       | 1.00                   | 1.05 | 15     |

| b      | 0.17       | 0.22                   | 0.27 | 9, 11  |

| b1     | 0.17       | 0.20                   | 0.23 | 11     |

| С      | 0.09       | -                      | 0.20 | 11     |

| c1     | 0.09       | -                      | 0.16 | 11     |

| D      | 9.00 BSC   |                        |      | 4      |

| D1     |            | 7.00 BSC               |      | 2, 5   |

| D2     | -          | -                      | 4.15 | 13     |

| D3     | 3.89       | -                      | -    | 14     |

| е      |            | 0.50 BSC               |      |        |

| E      |            | 9.00 BSC               |      | 4      |

| E1     |            | 7.00 BSC               |      | 2, 5   |

| E2     | -          | -                      | 4.15 | 13     |

| E3     | 3.89       | -                      | -    | 14     |

| L      | 0.45       | 0.60                   | 0.75 |        |

| L1     |            | 1.00 REF               |      |        |

| N      |            | 48                     |      | 16     |

| R1     | 0.08       | -                      | -    |        |

| R2     | 0.08       | -                      | 0.20 |        |

| S      | 0.20       | -                      | -    |        |

|        | Toleranc   | e of form and position |      |        |

| aaa    | aaa 0.20   |                        |      |        |

| bbb    | 0.20       |                        |      | 1, 7   |

| ccc    | 0.08       |                        |      | 1, 1   |

| ddd    | 0.08       |                        |      |        |

#### Notes:

- Dimensioning and tolerancing schemes conform to ASME Y14.5M-1994.

- 2. The top package body size may be smaller than the bottom package size up to 0.15 mm.

- 3. Datum A-B and D to be determined at datum plane H.

- 4. To be determined at seating datum plane C.

- 5. Dimensions D1 and E1 do not include mold flash or protrusions. Allowable mold flash or protrusions is "0.25 mm" per side. D1 and E1 are maximum plastic body size dimensions including mold mismatch.

DB3718 - Rev 1 page 7/11

- 6. Details of pin 1 identifier are optional but must be located within the zone indicated.

- All dimensions are in millimeters.

- 8. No intrusion allowed inwards the leads.

- 9. Dimension "b" does not include dambar protrusion. Allowable dambar protrusion shall not cause the lead width to exceed the maximum "b" dimension by more than 0.08 mm. Dambar cannot be located on the lower radius or the foot. Minimum space between protrusion and an adjacent lead is 0.07 mm for 0.4 mm and 0.5 mm pitch packages.

- 10. Exact shape of each corner is optional.

- 11. These dimensions apply to the flat section of the lead between 0.10 mm and 0.25 mm from the lead tip.

- 12. A1 is defined as the distance from the seating plane to the lowest point on the package body.

- 13. Dimensions D2 and E2 show the maximum exposed metal area on the package surface where the exposed pad is located (if present). It includes all metal protrusions from exposed pad itself.

- 14. Dimensions D3 and E3 show the minimum solderable area, defined as the portion of exposed pad which is guaranteed to be free from resin flashes/bleeds, bordered by internal edge of inner groove.

- 15. The optional exposed pad is generally coincident with the top or bottom side of the package and not allowed to protrude beyond that surface.

- 16. "N" is the number of terminal positions for the specified body size.

DB3718 - Rev 1 page 8/11

# **Revision history**

Table 3. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 22-Nov-2018 | 1       | Initial release. |

DB3718 - Rev 1 page 9/11

# **Contents**

| 1  | Bloc   | ck diagram                                             | 2 |  |

|----|--------|--------------------------------------------------------|---|--|

| 2  | Pin    | description                                            | 3 |  |

| 3  | Pac    | Package information                                    |   |  |

|    | 3.1    | TQFP48 (7x7x1 mm exposed pad down) package information | 6 |  |

| Re | vision | history                                                | 9 |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

DB3718 - Rev 1 page 11/11