## LTC4015

Multichemistry Buck Battery Charger Controller with Digital Telemetry System

### FEATURES

- Multichemistry Li-Ion/Polymer, LiFePO<sub>4</sub>, or Lead-Acid Battery Charger with Termination

- High Efficiency Synchronous Buck Battery Charger

- Digital Telemetry System Monitors V<sub>BAT</sub>, I<sub>BAT</sub>, R<sub>BAT</sub>,NTC Ratio (Battery Temperature), V<sub>IN</sub>, I<sub>IN</sub>, V<sub>SYSTEM</sub>, Die Temperature

- Coulomb Counter and Integrated 14-Bit ADC

- Wide Charging Input Voltage Range: 4.5V to 35V

- Wide Battery Voltage Range: Up to 35V

- Input Undervoltage Charge Current Limit Loop

- Maximum Power Point Tracking

- Optional I<sup>2</sup>C Serial Port Control

- Input Current Limit Prioritizes System Load Output

- Input and Output Ideal Diodes Provide Low Loss PowerPath<sup>™</sup> Operation

- Instant-On Operation with Discharged Battery

### **APPLICATIONS**

- Portable Medical Instruments/Military Equipment

- Industrial Handhelds/Lighting

- Ruggedized Notebook/Tablet Computers

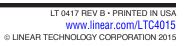

### TYPICAL APPLICATION

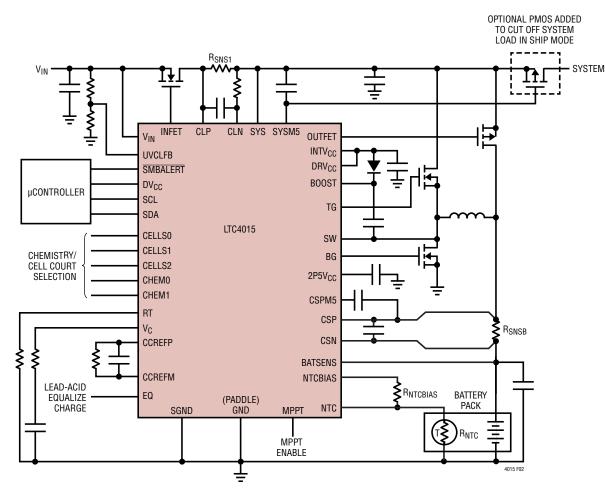

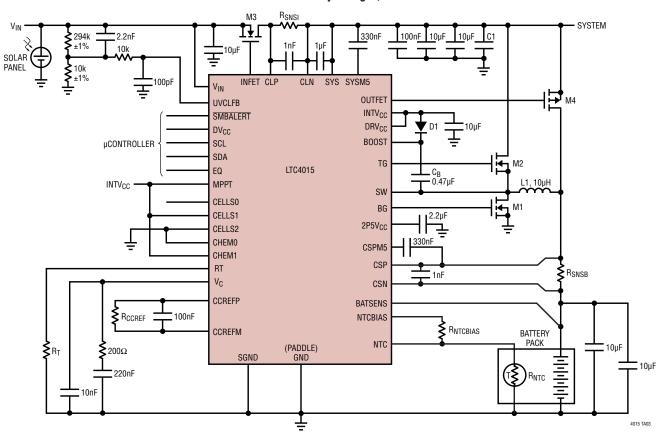

$12V_{\text{IN}}$  2-Cell Li-Ion 8A Step-Down Battery Charger Controller

### DESCRIPTION

The LTC<sup>®</sup>4015 is a complete synchronous buck controller/ charger with pin-selectable, chemistry specific charging and termination algorithms.

The LTC4015 can charge Li-Ion/Polymer, LiFePO<sub>4</sub>, or leadacid batteries. Battery charge voltage is pin selectable and I<sup>2</sup>C adjustable. Input current limit and charge current can be accurately programmed with sense resistors and can be individually adjusted via the I<sup>2</sup>C serial port. A digital telemetry system monitors all system power parameters.

Safety timer and current termination algorithms are supported for lithium chemistry batteries. The LTC4015 also includes automatic recharge, precharge (Li-Ion) and NTC thermistor protection. The LTC4015's I<sup>2</sup>C port allows user customization of charger algorithms, reading of charger status information, configuration of the maskable and programmable alerts, plus use and configuration of the Coulomb counter.

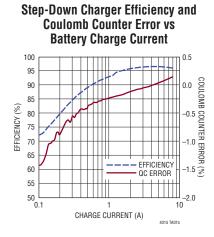

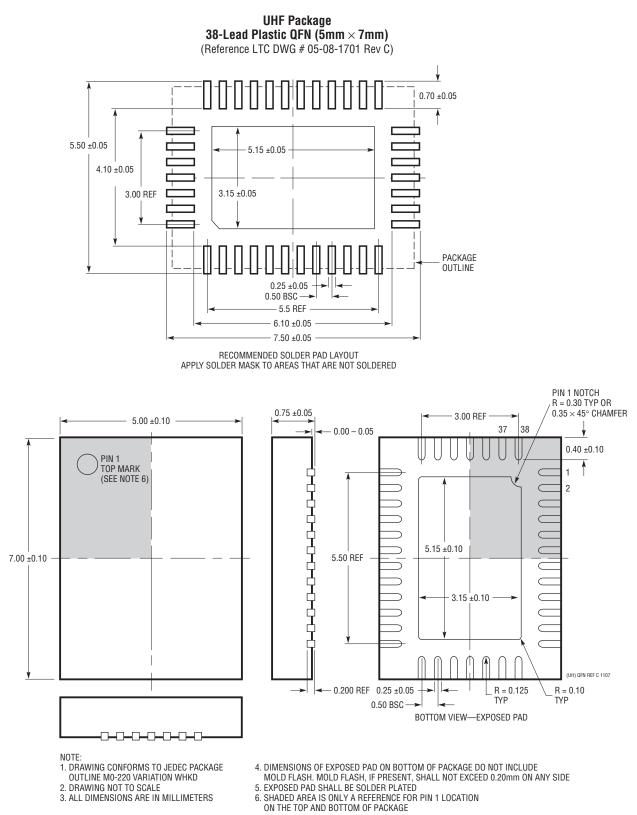

#### Available in a 38-Lead 5mm × 7mm QFN package.

∠

T, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and PowerPath is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features                             | 1  |

|--------------------------------------|----|

| Applications                         | 1  |

| Typical Application                  | 1  |

| Description                          | 1  |

| Absolute Maximum Ratings             | 3  |

| Order Information                    | 3  |

| Data Sheet Conventions               | 3  |

| Pin Configuration                    | 3  |

| Electrical Characteristics           | 4  |

| Typical Performance Characteristics1 | 10 |

| Pin Functions1                       | 13 |

| Block Diagram1                       | 15 |

| I <sup>2</sup> C Timing Diagram1     |    |

| Operation1                           | 17 |

| Applications Information             | 12 |

| Register Description                 | 19 |

| DETAILED Register Descriptions       |    |

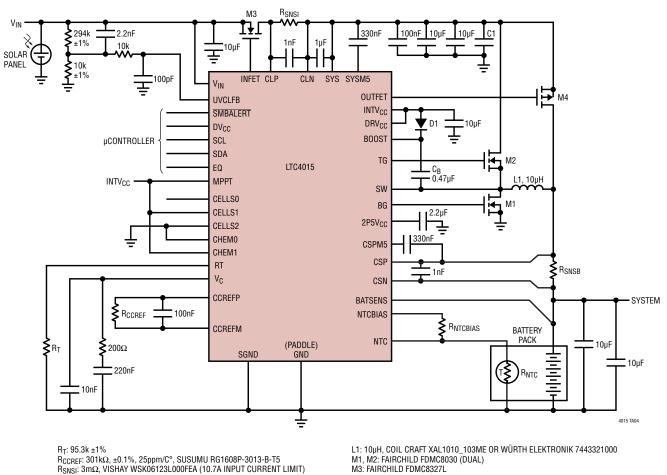

| Typical Applications                 | 72 |

| Package Description                  | 74 |

| Revision History                     | 75 |

| Typical Application                  | 76 |

| Related Parts                        | 76 |

### **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 5)

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ |

|------------------------------------------------------|

| DV <sub>CC</sub> , DRV <sub>CC</sub> –0.3V to 5.5V   |

| CELLSO, CELLS1, CELLS2, CHEM0, CHEM1,                |

| MPPT, EQ0.3V to INTV <sub>CC</sub>                   |

| SDA, SCL, SMBALERT0.3V to DV <sub>CC</sub>           |

| I <sub>UVCLFB</sub> (Note 4)±200μA                   |

| INTV <sub>CC</sub> Peak Output Current100mA          |

| Operating Junction Temperature Range                 |

| (Notes 2,3)–40 to 125°C                              |

| Storage Temperature Range65 to 150°C                 |

### PIN CONFIGURATION

### ORDER INFORMATION http://www.linear.com/product/LTC4015#orderinfo

| LEAD FREE FINISH | TAPE AND REEL     | E AND REEL PART MARKING* PACKAGE DESCRIPTION |                                        | TEMPERATURE RANGE |

|------------------|-------------------|----------------------------------------------|----------------------------------------|-------------------|

| LTC4015EUHF#PBF  | LTC4015EUHF#TRPBF | 4015                                         | 38-Lead (5mm $\times$ 7mm) Plastic QFN | -40°C to 125°C    |

| LTC4015IUHF#PBF  | LTC4015IUHF#TRPBF | 4015                                         | 38-Lead (5mm $\times$ 7mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

### DATA SHEET CONVENTIONS

- $V_{PINNAME}$  and  $I_{PINNAME}$  represents the voltage on a pin or the pin current;  $V_{EQ} = EQ$  Pin Voltage.

- Hexadecimal numbers are prefixed with 0x; 0x10 is a hexadecimal 10

- Register symbol names will be capitalized. Symbols within a register will be lower case;

en\_meas\_sys\_valid\_alert is bit 15 in register EN\_LIMIT\_ALERTS (0x0D)

- LiFePO<sub>4</sub> is lithium iron phosphate, Li-Ion is used for both lithium-ion and lithium-ion polymer

- Lithium chemistries refers to LiFePO<sub>4</sub>, lithium-ion, and lithium-ion polymer as a group.

- When a register name is used in square brackets, this means the 16 bit value associated with that register; For example [VBAT] is the 16 bit ADC measurement value of the per cell battery voltage.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25$ °C. (Note 2),  $DV_{CC} = 3.3V$ , UVCLFB = 1.5; CELLS1 =  $INTV_{CC}$ ; EQ, MPPT, CELLS0, CELLS2, CHEM0, CHEM1 = 0; RT = 95.3k;  $R_{CCREF} = 301k$ ,  $R_{NTCBIAS} = R_{NTC} = 10k$ ; BATSENS = CSN = CSP;  $DRV_{CC} = INTV_{CC}$ ; SYS = CLP = CLN. Conditions: Charging;  $V_{IN} = 12V$ , SYS = 12V, BATSENS = 7.4V .....Battery Only;  $V_{IN} = 0V$ , SYS = 8.4V, BATSENS = 8.4V

| SYMBOL                   | PARAMETER                                                                                          | CONDITIONS                                                                           |   | MIN   | ТҮР            | MAX  | UNITS                |

|--------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---|-------|----------------|------|----------------------|

| V <sub>IN</sub>          | Input Supply Voltage Range                                                                         | Note 8                                                                               |   | 3.1   |                | 35   | V                    |

| V <sub>BAT</sub>         | Battery Voltage Range                                                                              | Note 8                                                                               | • |       |                | 35   | V                    |

| V <sub>CHARGE(TOL)</sub> | Charge Voltage, Regulated Battery per Cell<br>Tolerance, All Chemistries                           | Li-Ion ,4.2V per Cell; LiFePO <sub>4</sub> 3.6V per<br>Cell; Lead-Acid 2.2V per Cell | • | -1.25 |                | 1.25 | %                    |

|                          | Regulated Battery Charge Current<br>Tolerance                                                      | Full-Scale V <sub>CSP-CSN</sub> /R <sub>SNSB</sub>                                   | • | -2.0  |                | 2.0  | %                    |

| V <sub>SYS</sub>         | SYS Pin Voltage                                                                                    | Note 8                                                                               |   | 3.05  |                | 35   | V                    |

| Quiescent Curr           | ent $I_Q = I_{VIN} + I_{CLP} + I_{CLN} + I_{SYS} + I_{SW} + I_{CSP} +$                             | Icsn + Ibatsens                                                                      |   |       |                |      |                      |

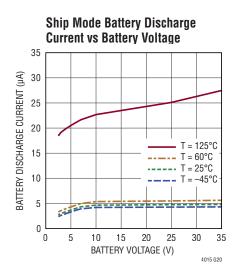

|                          | Battery Discharge Current (No Input                                                                | Battery Only, Telemetry Inactive                                                     |   |       | 112            | 325  | μA                   |

|                          | Supply, Coulomb Counter Disabled)                                                                  | Battery Only, Telemetry Active 1% Duty Cycle                                         | • |       | 140            | 364  | μA                   |

|                          |                                                                                                    | Battery Only, Telemetry Active<br>Continuously                                       |   |       | 2.84           |      | mA                   |

|                          | I <sub>Q</sub> , Charging                                                                          | Charging, Switcher Suspended                                                         |   |       | 3.00           |      | mA                   |

|                          |                                                                                                    | Charging, $V_{BAT} > V_{CHARGE}$ (Note 7)                                            |   |       | 4.10           |      | mA                   |

|                          | I <sub>Q</sub> , Ship Mode                                                                         | Ship Mode (V <sub>IN</sub> = 0)                                                      |   |       | 5              | 40   | μA                   |

| l <sub>Vin</sub>         | V <sub>IN</sub> Pin Current                                                                        | Battery Only (No Input Supply)                                                       |   | -200  |                | 200  | nA                   |

|                          |                                                                                                    | Charging                                                                             |   |       | <140           |      | μA                   |

| I <sub>SYS</sub>         | SYS Pin Current                                                                                    | Battery Only, Telemetry Off                                                          |   |       | 100            |      | μA                   |

|                          |                                                                                                    | Battery Only, Telemetry On                                                           |   |       | 2.75           |      | mA                   |

|                          |                                                                                                    | Charging, $V_{BAT} > V_{CHARGE}$ (Note 7)                                            |   |       | 3.65           |      | mA                   |

| V <sub>IN_DUVLO</sub>    | V <sub>IN</sub> to V <sub>BATSENS</sub> Differential Undervoltage (Must Be Satisfied for Charging) | Rising Threshold<br>Hysteresis                                                       | • | 140   | 200<br>100     | 250  | mV<br>mV             |

| V <sub>IN_OVLO</sub>     | Input Overvoltage Lockout<br>(Inhibits Charger)                                                    | Rising Threshold<br>Hysteresis                                                       | • | 37.7  | 38.6<br>1.4    | 39.5 | V<br>V               |

| Input Undervol           | tage Current Limit                                                                                 |                                                                                      |   |       |                |      |                      |

| VUVCLFB                  | UVCLFB Pin Regulation Range (8-Bit DAC)                                                            | V <sub>UVCLFB</sub> Maximum Code 0xFF<br>V <sub>UVCLFB</sub> Minimum Code 0x00       | • | 1188  | 1200<br>4.6875 | 1212 | mV<br>mV             |

|                          | UVCLFB Pin Regulation DAC LSB                                                                      |                                                                                      |   |       | 4.6875         |      | mV                   |

|                          | UVCLFB Pin Leakage Current                                                                         | V <sub>UVCLFB</sub> = 1.2V                                                           |   | -100  |                | 100  | nA                   |

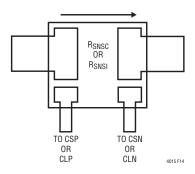

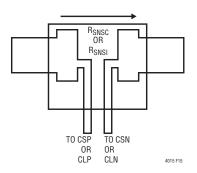

| Input Current L          | imit                                                                                               |                                                                                      |   |       |                |      |                      |

|                          | Regulated Input Current Limit Tolerance                                                            | Full-Scale V <sub>CLP-CLN</sub> /R <sub>SNSI</sub>                                   |   | -2.0  |                | 2.0  | %                    |

| I <sub>CL</sub>          | Input Current Limit Range                                                                          | $I_{CL} = (V_{CLP - CLN})/R_{SNSI}$                                                  |   |       | 0.5 – 32       |      | mV/R <sub>SNSI</sub> |

|                          | Input Current Limit LSB Step Size                                                                  |                                                                                      |   |       | 0.5            |      | mV/R <sub>SNSI</sub> |

|                          | CLP Input Current                                                                                  | $V_{CLP} = 12V, V_{CLP-CLN} = 32mV$                                                  |   |       | 45             |      | μA                   |

|                          | CLN Input Current                                                                                  | $V_{CLP} = 12V, V_{CLP-CLN} = 32mV$                                                  |   | -100  |                | 100  | nA                   |

|                          | CLP, CLN Common Mode Range                                                                         | Note 8                                                                               |   | 4     |                | 35   | V                    |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25$ °C. (Note 2),  $DV_{CC} = 3.3V$ , UVCLFB = 1.5; CELLS1 = INTV<sub>CC</sub>; EQ, MPPT, CELLS0, CELLS2, CHEM0, CHEM1 = 0; RT = 95.3k;  $R_{CCREF} = 301k$ ,  $R_{NTCBIAS} = R_{NTC} = 10k$ ; BATSENS = CSN = CSP;  $DRV_{CC} = INTV_{CC}$ ; SYS = CLP = CLN. Conditions: Charging;  $V_{IN} = 12V$ , SYS = 12V, BATSENS = 7.4V .....Battery Only;  $V_{IN} = 0V$ , SYS = 8.4V, BATSENS = 8.4V

| SYMBOL                              | PARAMETER                                                          | CONDITIONS                                                                                                                                                                                 |   | MIN  | ТҮР          | MAX  | UNITS                                        |

|-------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|--------------|------|----------------------------------------------|

| INTV <sub>CC</sub> Regulate         | or (SYS is Supply Pin for This Regulator)                          |                                                                                                                                                                                            |   |      |              |      |                                              |

| VINTVCC                             | Internal Regulator Output Voltage                                  | No Load                                                                                                                                                                                    |   |      | 5            |      | V                                            |

|                                     | Load Regulation                                                    | I <sub>INTVCC</sub> = 50 mA                                                                                                                                                                |   |      | 1.5          | 2.5  | %                                            |

| VINTVCC_CUVLO                       | INTV <sub>CC</sub> Undervoltage Charger Lockout                    | Rising Threshold<br>Hysteresis                                                                                                                                                             | • | 4.2  | 4.3<br>0.3   | 4.4  | V<br>V                                       |

| VINTVCC_TUVLO                       | INTV <sub>CC</sub> Undervoltage Telemetry System<br>Lockout        | Rising Threshold<br>Hysteresis                                                                                                                                                             | • | 2.75 | 2.85<br>0.12 | 2.95 | V<br>V                                       |

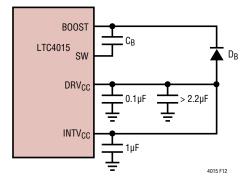

| DRV <sub>CC</sub> INPUT (E          | xternal Supply or Supplied by INTV <sub>CC</sub> )                 |                                                                                                                                                                                            |   |      |              |      |                                              |

| V <sub>DRVCC</sub>                  | DRV <sub>CC</sub> Supply Voltage                                   |                                                                                                                                                                                            |   | 4.3  |              | 5.5  | V                                            |

|                                     | DRV <sub>CC</sub> Undervoltage Lockout                             | Rising Threshold<br>Hysteresis                                                                                                                                                             | • | 4.1  | 4.2<br>0.3   | 4.3  | V<br>V                                       |

| Battery Charger<br>(All Chemistries |                                                                    |                                                                                                                                                                                            |   |      |              |      |                                              |

| ICHARGE                             | Battery Charge Current Range,<br>Battery Charge Current Resolution | V <sub>CSP</sub> > 2.6V (Note 10)                                                                                                                                                          |   |      | 1 – 32<br>1  |      | mV/R <sub>SNSB</sub><br>mV/R <sub>SNSB</sub> |

|                                     | Peak Low V <sub>CSP</sub> Charge Current                           | V <sub>CSP</sub> < 2.4V                                                                                                                                                                    |   |      | 7.0          |      | mV/R <sub>SNSB</sub>                         |

|                                     | I <sub>BATSENS</sub> + I <sub>CSP</sub> + I <sub>CSN</sub>         | $ \begin{array}{l} Charger \ Suspended \ (Telemetry \ Active) \\ V_{IN}, \ V_{SYS} = 12V, \ V_{BATSENS} = 7.4V \\ V_{IN}, \ V_{SYS} = 35V, \ V_{BATSENS} = 34V \ (9 \ Cells) \end{array} $ |   |      | 110<br>200   |      | μA<br>μA                                     |

| Lithium-lon/Lith                    | ium Polymer Battery Charger                                        |                                                                                                                                                                                            |   |      |              |      |                                              |

| Lithium-lon/Lith                    | ium Polymer Programmable, CHEM1, CHEI                              | MO = [LL] (Note 9)                                                                                                                                                                         |   |      |              |      |                                              |

|                                     | Li-Ion Charge Voltage Max DAC Setting                              | Code 11111 (Note 11)                                                                                                                                                                       |   |      | 4.2          |      | V/Cell                                       |

|                                     | Li-Ion Charge Voltage Min DAC Setting                              | Code 00000 (Note 11)                                                                                                                                                                       |   |      | 3.8125       |      | V/Cell                                       |

|                                     | Li-Ion Charge Voltage DAC LSB                                      |                                                                                                                                                                                            |   |      | 12.5         |      | mV                                           |

|                                     | Li-Ion Recharge Voltage                                            | Percent of Charge Voltage                                                                                                                                                                  |   |      | 97.5         |      | %                                            |

|                                     | Charge C/x Termination Setting                                     | V <sub>CSP-CSN</sub> (I <sup>2</sup> C Termination Option)                                                                                                                                 |   |      | 3.2          |      | mV                                           |

| Lithium-lon/Lith                    | nium Polymer Fixed 4.2, 4.1, 4.0 Charge Vo                         | ltage, CHEM1, CHEM0 = [HH,LZ,ZL] (Note 9                                                                                                                                                   | ) |      |              |      |                                              |

|                                     | 4.2V Fixed Li-Ion Charge Voltage                                   | CHEM1,0 = [H,H] (Note 11)                                                                                                                                                                  |   |      | 4.200        |      | V/Cell                                       |

|                                     | 4.2V Fixed Li-Ion Recharge Voltage                                 | CHEM1,0 = [H,H]                                                                                                                                                                            |   |      | 4.095        |      | V/Cell                                       |

|                                     | 4.1V Fixed Li-Ion Charge Voltage                                   | CHEM1,0 = [L,Z] (Note 11)                                                                                                                                                                  |   |      | 4.100        |      | V/Cell                                       |

|                                     | 4.1V Fixed Li-Ion Recharge Voltage                                 | CHEM1,0 = [L,Z]                                                                                                                                                                            |   |      | 4.000        |      | V/Cell                                       |

|                                     | 4.0V Fixed Li-Ion Charge Voltage                                   | CHEM1,0 = [Z,L] (Note 11)                                                                                                                                                                  |   |      | 4.000        |      | V/Cell                                       |

|                                     | 4.0V Fixed Li-Ion Recharge Voltage                                 | CHEM1,0 = [Z,L]                                                                                                                                                                            |   |      | 3.900        |      | V/Cell                                       |

| Lithium-lon/Lith                    | nium Polymer, CHEM1, CHEM0 = [LL, HH, L                            | Z, ZL] (Note 9)                                                                                                                                                                            |   |      |              |      |                                              |

|                                     | Low Battery Precharge Threshold                                    | Charge Voltage = 4.2V                                                                                                                                                                      |   |      | 2.85         |      | V/Cell                                       |

|                                     | Low Battery Precharge Hysteresis                                   | Charge Voltage = 4.2V                                                                                                                                                                      |   |      | 50           |      | mV/Cell                                      |

|                                     | Low Battery Precharge Current                                      | I <sub>CHARGE</sub> Set to 32 mV/R <sub>SNSB</sub>                                                                                                                                         |   |      | 3            |      | mV/R <sub>SNSB</sub>                         |

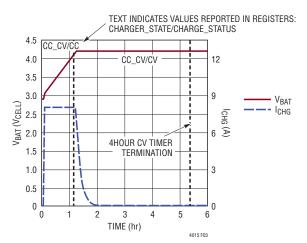

|                                     | Max Charge Time                                                    |                                                                                                                                                                                            |   |      | 18.2         |      | hrs                                          |

|                                     | Charge Termination Timer                                           | (Default Termination)                                                                                                                                                                      |   |      | 4            |      | hrs                                          |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25$ °C. (Note 2),  $DV_{CC} = 3.3V$ , UVCLFB = 1.5; CELLS1 = INTV<sub>CC</sub>; EQ, MPPT, CELLS0, CELLS2, CHEM0, CHEM1 = 0; RT = 95.3k;  $R_{CCREF} = 301k$ ,  $R_{NTCBIAS} = R_{NTC} = 10k$ ; BATSENS = CSN = CSP;  $DRV_{CC} = INTV_{CC}$ ; SYS = CLP = CLN. Conditions: Charging;  $V_{IN} = 12V$ , SYS = 12V, BATSENS = 7.4V .....Battery Only;  $V_{IN} = 0V$ , SYS = 8.4V, BATSENS = 8.4V

| SYMBOL                          | PARAMETER                                                                                                                                                              | CONDITIONS                                                                 | MIN   | ТҮР                        | MAX | UNITS                                    |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------|----------------------------|-----|------------------------------------------|

| LiFePO <sub>4</sub> Battery C   | Charger                                                                                                                                                                |                                                                            | I     |                            |     | <u> </u>                                 |

| LiFePO <sub>4</sub> , Program   | nmable, CHEM1,CHEM0 = [LH] (Note 9)                                                                                                                                    |                                                                            |       |                            |     |                                          |

|                                 | LiFePO <sub>4</sub> Charge Voltage Max DAC setting                                                                                                                     | Code 11111 (Note 11)                                                       |       | 3.8                        |     | V/Cell                                   |

|                                 | LiFePO <sub>4</sub> Charge Voltage Min DAC setting                                                                                                                     | Code 00000 (Note 11)                                                       |       | 3.4125                     |     | V/Cell                                   |

|                                 | LiFePO <sub>4</sub> Charge Voltage DAC LSB                                                                                                                             |                                                                            |       | 12.5                       |     | mV                                       |

|                                 | LiFePO <sub>4</sub> Recharge Voltage                                                                                                                                   | POR Value I <sup>2</sup> C Programmable                                    |       | 3.35                       |     | V/Cell                                   |

| V <sub>LiFePO4</sub> -C/x       | Charge Termination C/x Threshold                                                                                                                                       | V <sub>CSP-CSN</sub> (I <sup>2</sup> C Programmable)                       |       | 3.2                        |     | mV                                       |

| LiFePO <sub>4</sub> Fixed Sta   | andard Charge, Fixed Fast Charge, CHEM1                                                                                                                                | , CHEMO = [ZH,HZ] (Note 9)                                                 |       |                            |     |                                          |

|                                 | LiFePO <sub>4</sub> Fixed Fast Charge Absorb Voltage                                                                                                                   | CHEM1, CHEM0 = [HZ] Only (Note 11)                                         |       | 3.8                        |     | V/Cell                                   |

|                                 | LiFePO <sub>4</sub> Charge Voltage                                                                                                                                     | CHEM1, CHEM0 = [ZH,HZ] (Note 11)                                           |       | 3.6                        |     | V/Cell                                   |

|                                 | LiFePO <sub>4</sub> Recharge Voltage                                                                                                                                   | CHEM1, CHEM0 = [ZH,HZ] (Note 11)                                           |       | 3.35                       |     | V/Cell                                   |

| LiFePO <sub>4</sub> , CHEM1,    | , CHEMO = [LH,HZ,ZH] (Note 9)                                                                                                                                          |                                                                            | ·     |                            |     | <u> </u>                                 |

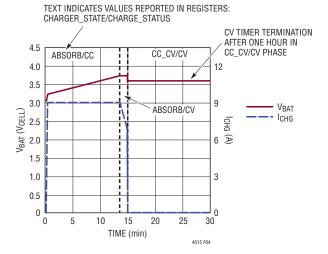

|                                 | Max Charge Time                                                                                                                                                        |                                                                            |       | 18.2                       |     | hrs                                      |

| V <sub>LiFePO4</sub> -T(CV)     | Charge Termination Time                                                                                                                                                |                                                                            |       | 1                          |     | hrs                                      |

| Lead-Acid Battery               | / Charger                                                                                                                                                              |                                                                            | - ·   |                            |     |                                          |

| Lead-Acid Fixed,                | CHEM1, CHEM0 = [ZZ] (Note 9)                                                                                                                                           |                                                                            |       |                            |     |                                          |

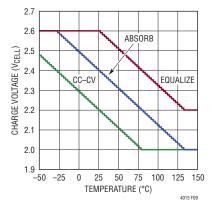

| V <sub>Lead_</sub> Acid_Vcharge | Lead-Acid V <sub>CHARGE</sub> , Equalization<br>Lead-Acid V <sub>CHARGE</sub> , Absorption<br>Lead-Acid V <sub>CHARGE</sub> , CV<br>Lead-Acid Temperature Compensation | (Note 11)<br>(Note 11)<br>(Note 11)                                        |       | 2.6<br>2.4<br>2.2<br>-3.65 |     | V/Cell<br>V/Cell<br>V/Cell<br>mV/Cell/°C |

| Lead-Acid Progra                | mmable, CHEM1, CHEM0 = [HL] (Note 9)                                                                                                                                   |                                                                            | ·     |                            |     |                                          |

| V <sub>Lead_</sub> Acid_Vcharge | Lead-Acid V <sub>CHARGE</sub> DAC Maximum<br>Lead-Acid V <sub>CHARGE</sub> DAC Minimum<br>Lead-Acid V <sub>CHARGE</sub> DAC Resolution<br>Lead-Acid Temperature Comp   | Code 111111 (Note 11)<br>Code 000000 (Note 11)<br>Temperature Comp Enabled |       | 2.6<br>2.0<br>9.5<br>-3.65 |     | V/Cell<br>V/Cell<br>mV<br>mV/Cell/°C     |

| Thermistor (NTC)                | BIAS                                                                                                                                                                   |                                                                            |       |                            |     | I                                        |

| V <sub>NTCBIAS</sub>            | Applied NTC Bias Voltage                                                                                                                                               | Internally Switched to 1.2V                                                |       | 1.2                        |     | V                                        |

| INTC                            | NTC Leakage Current                                                                                                                                                    |                                                                            | -50   |                            | 50  | nA                                       |

| SYSM5, CSPM5 F                  | Regulators                                                                                                                                                             |                                                                            |       |                            |     |                                          |

| -5V <sub>VINM5</sub>            | V <sub>SYS</sub> – V <sub>SYSM5</sub> , V <sub>CSP</sub> – V <sub>CSPM5</sub>                                                                                          | No Load                                                                    |       | 4.8                        |     | V                                        |

| Power Path/Ideal                | Diode Controllers                                                                                                                                                      |                                                                            | ·     |                            |     |                                          |

| V <sub>FT0</sub>                | Forward Turn-On Voltage                                                                                                                                                |                                                                            |       | 50                         |     | mV                                       |

| V <sub>FR</sub>                 | Forward Regulation                                                                                                                                                     |                                                                            |       | 15                         |     | mV                                       |

| V <sub>RTO</sub>                | Reverse Turn-Off                                                                                                                                                       |                                                                            |       | -30                        |     | mV                                       |

| t <sub>IF(ON)</sub>             | INFET Turn-On Time                                                                                                                                                     | $INFET - V_{IN} > 3V, C_{INFET} = 3.3nF$                                   |       | 550                        |     | μs                                       |

| t <sub>IF(OFF)</sub>            | INFET Turn-Off Time                                                                                                                                                    | $INFET - V_{IN} < 1V, C_{INFET} = 3.3nF$                                   |       | 2                          |     | μs                                       |

| t <sub>OF(ON)</sub>             | OUTFET Turn-On Time                                                                                                                                                    | VBAT – OUTFET > 3V, C <sub>OUTFET</sub> = 3.3nF                            |       | 2.3                        |     | μs                                       |

| t <sub>OF(OFF)</sub>            | OUTFET Turn-Off Time                                                                                                                                                   | VBAT – OUTFET < 1V, C <sub>OUTFET</sub> = 3.3nF                            |       | 1.9                        |     | μs                                       |

| Inductor Current F              | Regulation                                                                                                                                                             |                                                                            |       |                            |     |                                          |

| ILIM                            | Cycle by Cycle Max Charge Current                                                                                                                                      | Note 5                                                                     | • 47  | 52                         | 57  | mV/R <sub>SNSB</sub>                     |

| I <sub>REV</sub>                | Reverse Inductor Current                                                                                                                                               |                                                                            | • 3.8 | 7.0                        | 10  | mV/R <sub>SNSB</sub>                     |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25$ °C. (Note 2),  $DV_{CC} = 3.3V$ , UVCLFB = 1.5; CELLS1 = INTV<sub>CC</sub>; EQ, MPPT, CELLS0, CELLS2, CHEM0, CHEM1 = 0; RT = 95.3k;  $R_{CCREF} = 301k$ ,  $R_{NTCBIAS} = R_{NTC} = 10k$ ; BATSENS = CSN = CSP;  $DRV_{CC} = INTV_{CC}$ ; SYS = CLP = CLN. Conditions: Charging;  $V_{IN} = 12V$ , SYS = 12V, BATSENS = 7.4V .....Battery Only;  $V_{IN} = 0V$ , SYS = 8.4V, BATSENS = 8.4V

| SYMBOL               | PARAMETER                                                                                                                                                                                                                                                                                                                                                              | CONDITIONS                                                                                                     |   | MIN | ТҮР                                  | MAX          | UNITS                                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---|-----|--------------------------------------|--------------|--------------------------------------|

| Oscillator           |                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                | 1 |     |                                      |              |                                      |

| f <sub>OSC</sub>     | Switching Frequency                                                                                                                                                                                                                                                                                                                                                    | R <sub>T</sub> = 95.3k                                                                                         |   | 475 | 500                                  | 525          | kHz                                  |

| f <sub>MAX</sub>     | Maximum Programmable Frequency                                                                                                                                                                                                                                                                                                                                         | R <sub>T</sub> = 47.5k                                                                                         |   |     | 1                                    |              | MHz                                  |

| f <sub>MIN</sub>     | Minimum Programmable Frequency                                                                                                                                                                                                                                                                                                                                         | R <sub>T</sub> = 237k                                                                                          |   |     | 200                                  |              | kHz                                  |

| Gate Drivers         |                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |   |     |                                      |              |                                      |

| R <sub>UP-TG</sub>   | TG Pull-Up On-Resistance                                                                                                                                                                                                                                                                                                                                               |                                                                                                                |   |     | 2.0                                  |              | Ω                                    |

| R <sub>DOWN-TG</sub> | TG Pull-Down On-Resistance                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |   |     | 0.5                                  |              | Ω                                    |

| R <sub>UP-BG</sub>   | BG Pull-Up On-Resistance                                                                                                                                                                                                                                                                                                                                               |                                                                                                                |   |     | 2.0                                  |              | Ω                                    |

| R <sub>DOWN-BG</sub> | TG Pull-Down On-Resistance                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |   |     | 0.5                                  |              | Ω                                    |

| t <sub>R-TG</sub>    | TG 10% to 90% Rise Time                                                                                                                                                                                                                                                                                                                                                | C <sub>LOAD</sub> = 3.3nF                                                                                      |   |     | 20                                   |              | ns                                   |

| t <sub>F-TG</sub>    | TG 90% to 10% Fall Time                                                                                                                                                                                                                                                                                                                                                | C <sub>LOAD</sub> = 3.3nF                                                                                      |   |     | 10                                   |              | ns                                   |

| t <sub>R-BG</sub>    | BG 10% to 90% Rise Time                                                                                                                                                                                                                                                                                                                                                | C <sub>LOAD</sub> = 3.3nF                                                                                      |   |     | 20                                   |              | ns                                   |

| t <sub>F-BG</sub>    | BG 90% to 10% Fall Time                                                                                                                                                                                                                                                                                                                                                | C <sub>LOAD</sub> = 3.3nF                                                                                      |   |     | 10                                   |              | ns                                   |

| t <sub>NO</sub>      | Non-Overlap Time                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                |   |     | 60                                   |              | ns                                   |

| t <sub>ON(MIN)</sub> | Minimum On-Time                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |   |     | 140                                  |              | ns                                   |

| DC <sub>MAX</sub>    | Maximum Duty Cycle                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |   |     | 98.4                                 |              | %                                    |

| VC Error Amp         | lifier                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |   |     |                                      |              |                                      |

| 9m                   | $\begin{array}{l} \label{eq:gm} Transconductance to V_{C} pin\\ g_{m} \left(V_{CSP-CSM}\right) (Constant-Current)\\ g_{m} \left(V_{BATSENS}\right) (Constant-Voltage Lithium)\\ g_{m} \left(V_{BATSENS}\right) (Constant-Voltage LA)\\ g_{m} \left(V_{UVCLFB}\right) (Input Voltage Regulation)\\ g_{m} \left(V_{CLP-CLM}\right) (Input Current Limiting) \end{array}$ | 2 Cell; (gm = 1.06 <sup>-3</sup> • 2/(7 • Cell Count)<br>6 Cell; (gm = 1.06 <sup>-3</sup> • 3/(7 • Cell Count) |   |     | 4.10<br>0.15<br>0.08<br>1.06<br>4.10 |              | mmho<br>mmho<br>mmho<br>mmho<br>mmho |

| Telemetry A/D        | ) Measurement Subsystem, Battery Only Mode                                                                                                                                                                                                                                                                                                                             |                                                                                                                |   |     |                                      |              |                                      |

| V <sub>ERR</sub>     | Measurement Error (Note 6)                                                                                                                                                                                                                                                                                                                                             | $V_{IN} = 1V$<br>$V_{IN} = 35V$                                                                                |   |     |                                      | ±100<br>±1.5 | mV<br>%                              |

|                      |                                                                                                                                                                                                                                                                                                                                                                        | V <sub>SYS</sub> = 2.5V<br>V <sub>SYS</sub> = 35V                                                              |   |     |                                      | ±100<br>±1.5 | mV<br>%                              |

|                      |                                                                                                                                                                                                                                                                                                                                                                        | V <sub>BAT</sub> = 1.75V, 1 Cell Li-Ion<br>V <sub>BAT</sub> = 35V, 9 Cell Li-Ion                               |   |     |                                      | ±50<br>±1.5  | mV<br>%                              |

|                      |                                                                                                                                                                                                                                                                                                                                                                        | $V_{CLP-CLN} = 0mV$<br>$V_{CLP-CLN} = 32mV$                                                                    |   |     |                                      | ±200<br>±2.5 | μV<br>%                              |

|                      |                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CSP-CSN</sub> = 0mV<br>V <sub>CSP-CSN</sub> = 32mV                                                      |   |     |                                      | ±200<br>±2.5 | μV<br>%                              |

|                      |                                                                                                                                                                                                                                                                                                                                                                        | NTC/NTCBIAS = 50%, 75%<br>NTC/NTCBIAS = 5%                                                                     |   |     |                                      | ±2<br>±3.5   | %                                    |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C. (Note 2),  $DV_{CC} = 3.3V$ , UVCLFB = 1.5; CELLS1 = INTV<sub>CC</sub>; EQ, MPPT, CELLS0, CELLS2, CHEM0, CHEM1 = 0; RT = 95.3k;  $R_{CCREF} = 301k$ ,  $R_{NTCBIAS} = R_{NTC} = 10k$ ; BATSENS = CSN = CSP;  $DRV_{CC} = INTV_{CC}$ ; SYS = CLP = CLN. Conditions: Charging;  $V_{IN} = 12V$ , SYS = 12V, BATSENS = 7.4V .....Battery Only;  $V_{IN} = 0V$ , SYS = 8.4V, BATSENS = 8.4V

| SYMBOL                     | PARAMETER                                       | CONDITIONS                                                                     |   | MIN | ТҮР        | MAX  | UNITS                       |

|----------------------------|-------------------------------------------------|--------------------------------------------------------------------------------|---|-----|------------|------|-----------------------------|

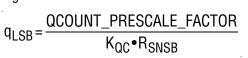

| Coulomb Cou                | nter                                            |                                                                                | l |     |            | I    |                             |

| V <sub>SENSE</sub>         | Sense Voltage Differential Input Range          | V <sub>CSP-CSN</sub>                                                           |   |     |            | ±50  | mV                          |

| q <sub>LSB</sub>           | Charge Measurement Resolution                   | Prescaler M = 512 (Default)                                                    |   |     | 0.017      |      | mVhr                        |

| TCE                        | Total Charge Error                              | $10mV \le  V_{SENSE}  \le 50mV$                                                |   |     |            | ±1.5 | %                           |

|                            |                                                 | $10mV \le  V_{SENSE}  \le 50mV$                                                |   |     |            | ±2.5 | %                           |

|                            |                                                 | V <sub>SENSE</sub> = 1mV                                                       |   |     | <1.0       |      | %                           |

| I <sub>QC_CSP</sub>        | I <sub>Q</sub> <sup>-</sup> Coulomb Counter     | V <sub>SENSE</sub> = 30mV, Battery Only                                        |   |     | 78         |      | μA                          |

| CELLSO, CELI               | S1, CELLS2, CHEMO, CHEM1 Programming I          | nput Pins (Note 9)                                                             |   |     |            | •    |                             |

| VIHPP                      | Input High Threshold                            | INT <sub>VCC</sub> – V <sub>PIN</sub>                                          |   |     |            | 0.3  | V                           |

| V <sub>ILPP</sub>          | Input Low Threshold                             | V <sub>PIN</sub>                                                               |   |     |            | 0.3  | V                           |

| R <sub>IZPP</sub>          | Input High-Z Test Resistance                    | Internal 50k/50k Resistor Divider Applied to Inputs During Chemistry/Cell Read |   |     | 25         |      | kΩ                          |

| MPPT, EQ Inp               | ut Pins                                         |                                                                                |   |     |            |      |                             |

|                            | MPPT, EQ Input High Threshold                   |                                                                                |   | 1.1 |            |      | V                           |

|                            | MPPT, EQ Input Low Threshold                    |                                                                                |   |     |            | 0.2  | V                           |

|                            | MPPT, EQ Pin Leakage Current                    | V <sub>EQ</sub> , V <sub>MPPT</sub> = 5V                                       |   |     | 0          | 1    | μA                          |

| SMBALERT Pi                | n Characteristics                               |                                                                                |   |     |            | •    |                             |

| SMBALERT                   | SMBALERT Pin Leakage Current                    | V <sub>SMBALERT</sub> = 5V                                                     |   |     | 0          | 1    | μA                          |

| V <sub>SMBALERT</sub>      | SMBALERT Pin Output Low Voltage                 | I <sub>SMBALERT</sub> = 1mA                                                    |   |     | 65         | 100  | mV                          |

| I <sup>2</sup> C Port, SDA | , SCL                                           |                                                                                |   |     |            |      |                             |

| DV <sub>CC</sub>           | I <sup>2</sup> C Logic Reference Level          |                                                                                |   | 1.6 |            | 5.5  | V                           |

| IDVCCQ                     | DV <sub>CC</sub> Current                        | SCL/SDA = 0kHz                                                                 |   |     | 0          |      | μA                          |

| ADDRESS                    | I <sup>2</sup> C Address                        |                                                                                |   | 11( | 01_000[R/V | V]b  |                             |

| V <sub>IHI2C</sub>         | Input High Threshold                            |                                                                                |   |     |            | 70   | $\% \text{ DV}_{\text{CC}}$ |

| V <sub>ILI2C</sub>         | Input Low Threshold                             |                                                                                |   | 30  |            |      | % DV <sub>CC</sub>          |

| I <sub>IHI2C</sub>         | Input Leakage High                              |                                                                                |   | -1  |            | 1    | μA                          |

| I <sub>ILI2C</sub>         | Input Leakage Low                               |                                                                                |   | -1  |            | 1    | μA                          |

| V <sub>OLI2C</sub>         | Digital Output Low (SDA)                        | I <sub>SDA</sub> = 3mA                                                         |   |     |            | 0.4  | V                           |

| F <sub>SCL</sub>           | SCL Clock Frequency                             |                                                                                |   |     |            | 400  | kHz                         |

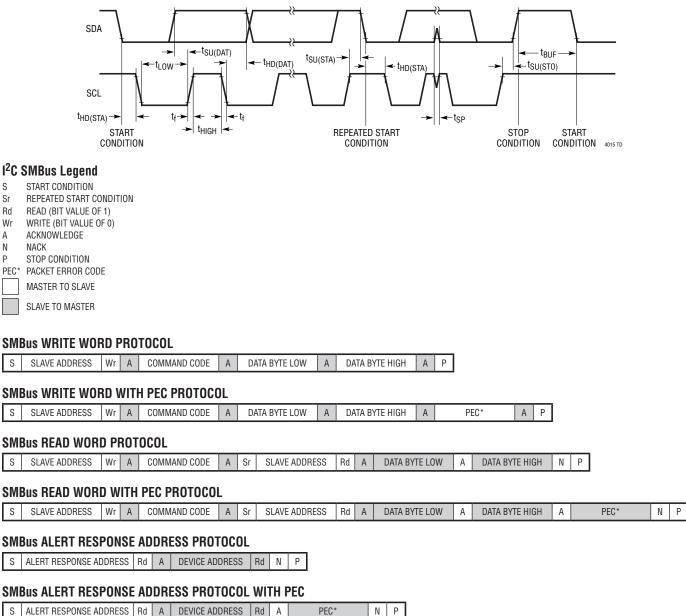

| t <sub>LOW</sub>           | LOW Period of SCL Clock                         |                                                                                |   | 1.3 |            |      | μS                          |

| t <sub>HIGH</sub>          | HIGH Period of SCL Clock                        |                                                                                |   | 0.6 |            |      | μS                          |

| t <sub>BUF</sub>           | Bus Free Time Between Start and Stop Conditions |                                                                                |   | 1.3 |            |      | μs                          |

| t <sub>HD(STA)</sub>       | Hold Time, After (Repeated) Start<br>Condition  |                                                                                |   | 0.6 |            |      | μs                          |

| t <sub>SU(STA)</sub>       | Setup Time After a Repeated Start Condition     |                                                                                |   | 0.6 |            |      | μs                          |

| t <sub>SU(STO)</sub>       | Stop Condition Set-Up Time                      |                                                                                |   | 0.6 |            |      | μs                          |

### **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating

junction temperature range, otherwise specifications are at  $T_A = 25$ °C. (Note 2),  $DV_{CC} = 3.3V$ , UVCLFB = 1.5;  $CELLS1 = INTV_{CC}$ ; EQ, MPPT, CELLS0, CELLS2, CHEM0, CHEM1 = 0; RT = 95.3k;  $R_{CCREF} = 301k$ ,  $R_{NTCBIAS} = R_{NTC} = 10k$ ; BATSENS = CSN = CSP;  $DRV_{CC} = INTV_{CC}$ ; SYS = CLP = CLN. Conditions: Charging;  $V_{IN} = 12V$ , SYS = 12V, BATSENS = 7.4V .....Battery Only;  $V_{IN} = 0V$ , SYS = 8.4V, BATSENS = 8.4V

| SYMBOL                    | PARAMETER                           | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|---------------------------|-------------------------------------|------------|-----|-----|-----|-------|

| t <sub>HD(DAT(OUT))</sub> | Output Data Hold Time               |            | 0   |     | 900 | ns    |

| t <sub>HD)DAT(IN))</sub>  | Input Data Hold Time                |            | 0   |     |     | ns    |

| t <sub>SU(DAT)</sub>      | Data Set-Up Time                    |            | 100 |     |     | ns    |

| t <sub>SP</sub>           | Input Spike Suppression Pulse Width |            |     |     | 50  | ns    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC4015 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC4015E is guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC4015I is guaranteed over the -40°C to 125°C operating junction temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors. The junction temperature (T<sub>J</sub>, in °C) is calculated from the ambient temperature (T<sub>A</sub>, in °C) and power dissipation (PD, in Watts) according to the formula:

$T_J = T_A + (PD \bullet \theta_{JA})$ where  $\theta_{JA} = 34^{\circ}C/W$  for the UHF package.

**Note 3:** The LTC4015 includes overtemperature protection that is intended to protect the device during momentary overload conditions. The maximum rated junction temperature will be exceeded when this protection is active. Continuous operation above the specified absolute maximum operating junction temperature may impair device reliability or permanently damage the device.

**Note 4:** UVCLFB is internally clamped above the maximum UVCLFB regulation point (2.5V at 200µA nominally). Maximum input current must be limited to 200µA when this clamp is reached.

**Note 5:** The current limit features of this part are intended to protect the IC from short term or intermittent fault conditions. Continuous operation above the maximum specified pin current may result in device degradation or failure.

**Note 6:** Measurement error is the magnitude of the difference between the actual measured value and the ideal value. Error for V<sub>CLP-CLN</sub> and V<sub>CSP-CSN</sub> is expressed in  $\mu$ V, a conversion to an equivalent current may be made by dividing by the sense resistors, R<sub>SNSI</sub> and R<sub>SNSB</sub>, respectively.

**Note 7:**  $V_{CHARGE}$  is the battery charge voltage (or CV, constant-voltage) target.  $V_{BAT}$  is the battery voltage. Dynamic supply current is higher due to the gate charge being delivered at the switching frequency. See the Applications Information section.

**Note 8:**  $V_{IN}$ , or  $V_{BAT}$  for battery only operation, may be connected to any suitable DC power source from 2.8V to 35V such that the voltage at  $V_{SYS}$  is high enough to allow  $INTV_{CC}$  to support the desired mode of operation. In order for the telemetry system to operate,  $INTV_{CC}$  must exceed the telemetry undervoltage lockout ( $V_{INTVCC\_TUVLO}$ ). In order for the battery charger to operate,  $INTV_{CC}$  must exceed the charger undervoltage lockout ( $V_{INTVCC\_TUVLO}$ ). Allowing for 0.3V of drop from  $V_{IN}$  to  $INTV_{CC}$ , these modes require a minimum input voltage of 3.1V and 4.35V, respectively. Additionally the  $V_{IN}$  to  $V_{BATSENS}$  ( $V_{IN\_DULVO}$ ) differential must also be satisfied for charging.

**Note 9:** Chemistry selection is made using the CHEM1 and CHEM0 pins. These are three-state pins used by the LTC4015 to select of one of nine chemistry specific charging algorithms. These pins should be hard wired to GND(L),  $INTV_{CC}(H)$ , or left open (Z > 1000k $\Omega$ ).

**Note 10:**  $I_{CHARGE}$  is the battery charge current (or CC, constant-current) target.  $I_{CHG}$  is the charge current when charging.

**Note 11:** Charge voltage tolerance is  $V_{CHARGE(TOL)}$  which is specified at the beginning of the electrical table. The LTC4015 is not a substitute for pack protection! The 4015 does not monitor or balance individual cells – the full stack voltage is divided by number of cells for simplicity only.

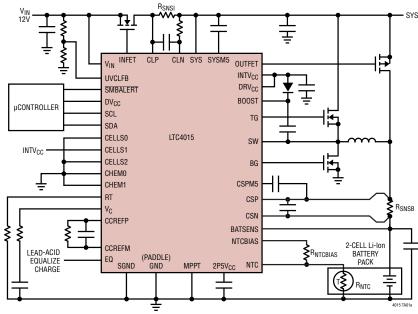

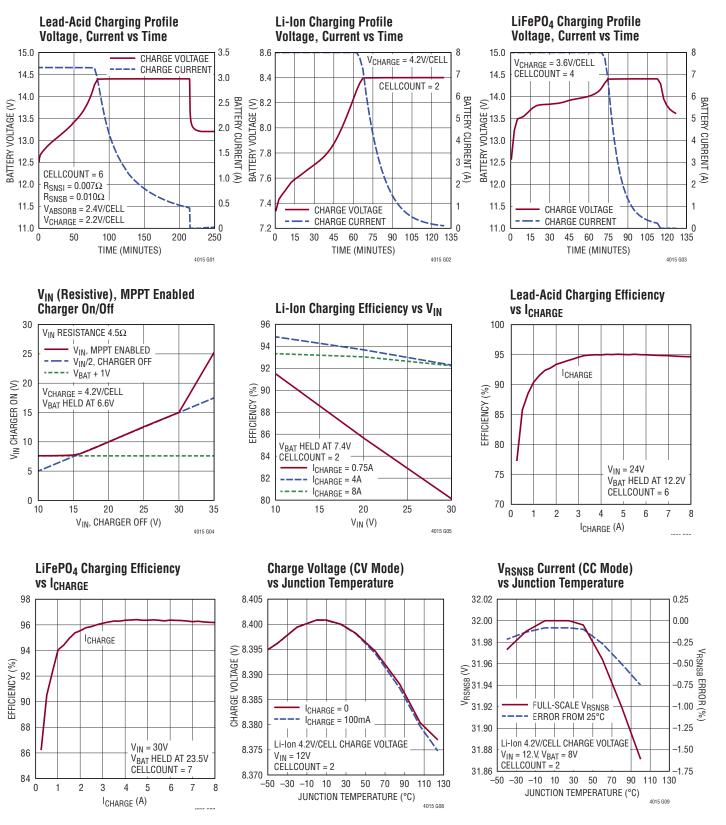

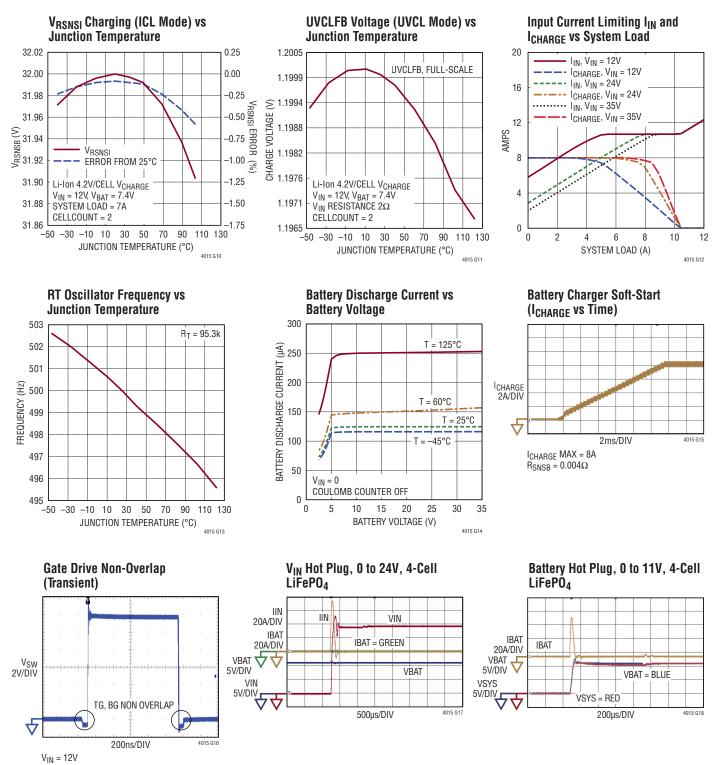

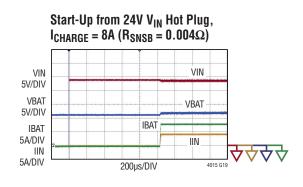

### TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25^{\circ}C$ , application circuit 1 unless

otherwise noted.

### TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25^{\circ}C$ , application circuit 1 unless

otherwise noted.

$V_{BAT} = 7.4V$

### **TYPICAL PERFORMANCE CHARACTERISTICS**

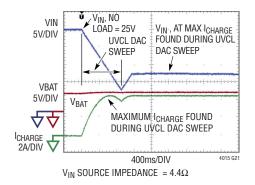

MPPT Algorithm Using UVCL DAC Sweep to Find MPP

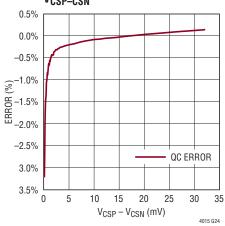

Coulomb Counter Accuracy vs V<sub>CSP-CSN</sub>

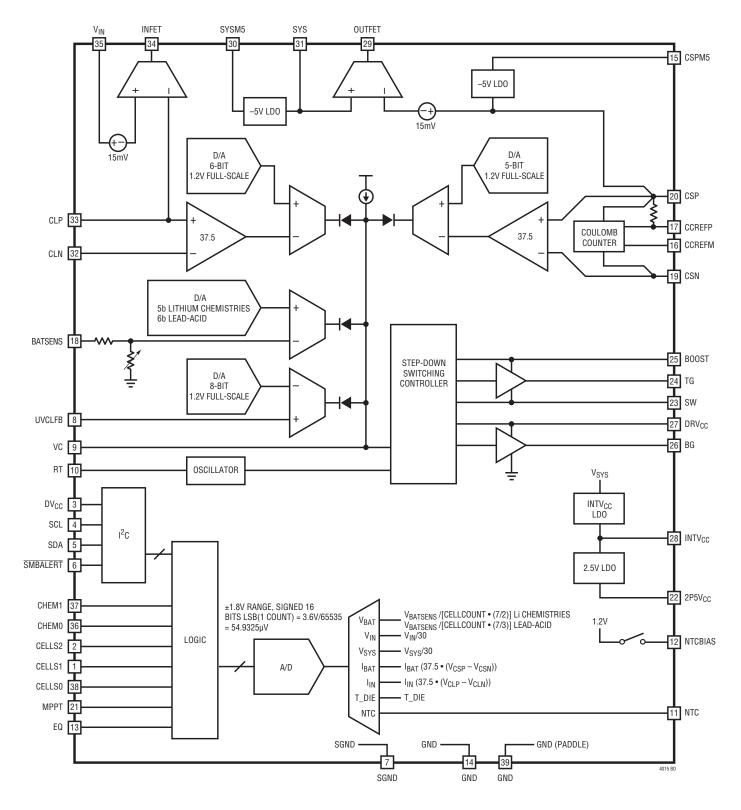

### PIN FUNCTIONS

**CELLS1 (Pin 1):** Number of Cells Select Pin. Three-state pin used in combination with CELLS0 and CELLS2 to set the total number of battery cells.

**CELLS2 (Pin 2):** Number of Cells Select Pin. Three-state pin used in combination with CELLS0 and CELLS1 to set the total number of battery cells.

**DV<sub>CC</sub> (Pin 3):** Logic Supply for the I<sup>2</sup>C Serial Port. DV<sub>CC</sub> sets the reference level of the SDA and SCL pins for I<sup>2</sup>C compliance. It must be connected to the same power supply used to power the I<sup>2</sup>C pull up resistors. If the I<sup>2</sup>C port is unused connect this pin to INTV<sub>CC</sub>, do not float.

**SCL (Pin 4):** Clock Input for the I<sup>2</sup>C Serial Port. The I<sup>2</sup>C input levels are scaled with respect to  $DV_{CC}$  for I<sup>2</sup>C compliance. If the I<sup>2</sup>C port is unused connect this pin to INTV<sub>CC</sub>, do not float.

**SDA (Pin 5):** Data Input/Output for the I<sup>2</sup>C serial port. The I<sup>2</sup>C input levels are scaled with respect to  $DV_{CC}$  for I<sup>2</sup>C compliance. If the I<sup>2</sup>C port is unused connect this pin to INTV<sub>CC</sub>, do not float.

**SMBALERT** (Pin 6): Open-Drain Interrupt Request. Pulls low when something important needs to be reported back to the system.

**SGND (Pin 7):** Signal Ground. All small signal components and compensation should connect to this ground, which should be connected to PGND at a single point.

**UVCLFB (Pin 8):** Undervoltage Current Limit Feedback Pin. UVCLFB can be used to reduce charge current when the V<sub>IN</sub> pin reaches a level programmed by the user supplied resistor divider. This feature can be used for power sources with higher source impedance such as a solar panel. Maximum charge current is tapered off when this pin is below 1.2V, at 1.15V the charge current is zero. UVCLFB is internally clamped to about 2.5V with 200µA in this pin. Limit the current into this pin to 200µA at maximum V<sub>IN</sub> using the thevenin resistance of the input divider. If the input undervoltage current limit feature is not desired, connect UVCLFB to 2P5V<sub>CC</sub> through a 10k resistor or to V<sub>IN</sub> through an appropriately sized resistor. **VC (Pin 9):** Current Control Threshold and Error Amplifier Compensation Point. The current comparator threshold increases with this control voltage. The voltage normally ranges from 900mV to 2.4V.

**RT (Pin 10):** Connect a resistor from RT to GND to set frequency of the switching power supply.

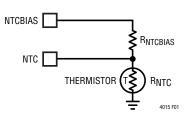

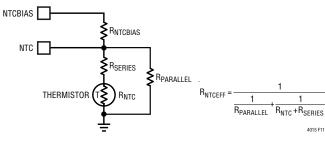

**NTC (Pin 11):** Thermistor Input. The NTC pin connects to a negative temperature coefficient thermistor (Type\_2) to monitor the temperature of the battery. The voltage on this pin is digitized by the analog to digital converter and is available via the I<sup>2</sup>C port. The thermistor value is also used to qualify battery charging. Connect a low drift bias resistor from NTCBIAS to NTC and a thermistor from NTC to ground. If NTC functions are unwanted, use a resistor equal in value to R<sub>NTCBIAS</sub> instead of a thermistor.

**NTCBIAS (Pin 12):** NTC Thermistor Bias Output. Connect a bias resistor between NTCBIAS and NTC, and a thermistor between NTC and GND. The bias resistor should be equal in value to the nominal value of the thermistor. The LTC4015 applies 1.2V to this pin during NTC measurement.

**EQ (Pin 13):** Equalize. Apply a logic signal between 1.5V and INTV<sub>CC</sub> (5V) to this pin to allow the 4015 to trigger lead-acid equalize mode. GND this pin if unused, do not float.

**GND (Pin 14, Exposed Pad Pin 39):** Ground. The exposed pad should be connected by multiple vias directly under the LTC4015 to a continuous ground plane on the second layer of the printed circuit board.

**CSPM5 (Pin 15):** Internal Supply Pin. The V<sub>CSPM5</sub> pin regulates at the higher of ground or approximately  $V_{CSP} - 5V$ . A low impedance multilayer ceramic capacitor should be connected from V<sub>CSP</sub> to V<sub>CSPM5</sub>.

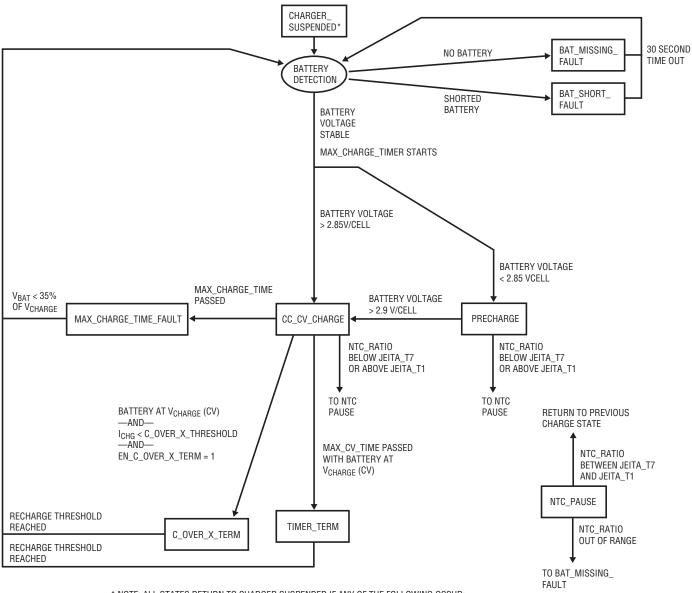

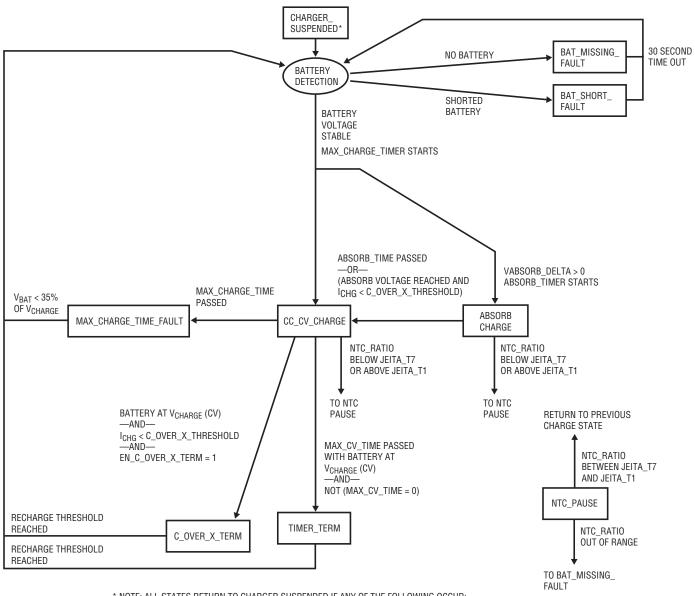

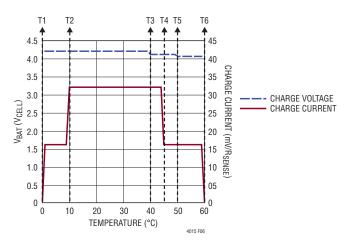

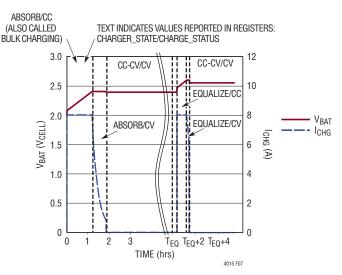

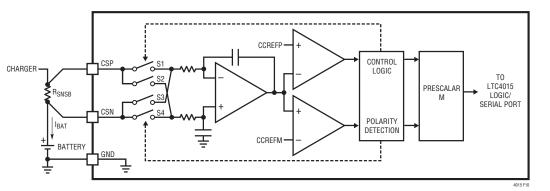

**CCREFM (Pin 16):** Coulomb Counter Reference Resistor Pin. Leakage on this pin will affect Coulomb counter accuracy. Connect a 301k, 0.1%, 25ppm resistor from CCREFM to CCREP.