# Integrated 3-Port 10/100 Managed Switch with PHYs

#### **Features**

- · Advanced Switch Features

- IEEE 802.1q VLAN Support for Up to 16 Groups (Full Range of VLAN IDs)

- VLAN ID Tag/Untag Options, Per Port Basis

- IEEE 802.1p/q Tag Insertion or Removal on a Per Port Basis (Egress)

- Programmable Rate Limiting at the Ingress and Egress on a Per Port Basis

- Broadcast Storm Protection with Percent Control (Global and Per Port Basis)

- IEEE 802.1d Rapid Spanning Tree Protocol Support

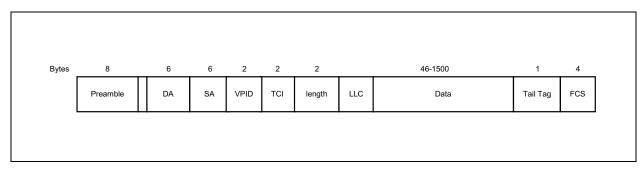

- Tail Tag Mode (1 byte Added before FCS) Support at Port 3 to Inform the Processor which Ingress Port Receives the Packet and its Priority

- Bypass Feature that Automatically Sustains the Switch Function between Port 1 and Port 2 when CPU (Port 3 Interface) Goes to the Sleep Mode

- Self-Address Filtering

- Individual MAC Address for Port 1 and Port 2

- Supports RMII Interface and 50 MHz Reference Clock Output

- IGMP Snooping (IPv4) Support for Multicast Packet Filtering

- IPv4/IPv6 QoS Support

- MAC Filtering Function to Forward Unknown Unicast Packets to Specified Port

- · Comprehensive Configuration Register Access

- Serial Management Interface (SMI) to All Internal Registers

- MII Management (MIIM) Interface to PHY Registers

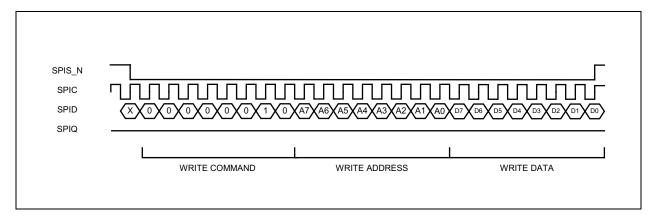

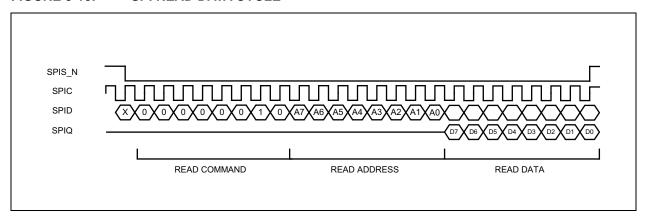

- High Speed SPI and I<sup>2</sup>C Interface to All Internal Registers

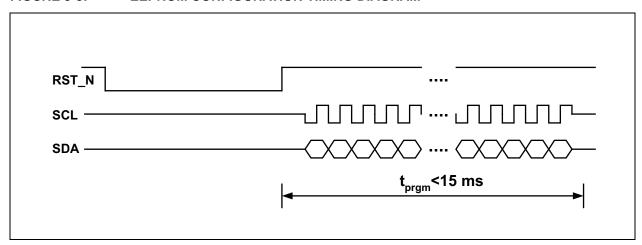

- I/O Pins Strapping and EEPROM to Program Selective Registers in Unmanaged Switch Mode

- Control Registers Configurable on the Fly (Port-Priority, 802.1p/d/q, AN…)

- QoS/CoS Packet Prioritization Support

- Per Port, 802.1p and DiffServ-Based

- Re-Mapping of 802.1p Priority Field Per Port basis, Four Priority Levels

- Proven Integrated 3-Port 10/100 Ethernet Switch

- 3rd Generation Switch with Three MACs and Two PHYs Fully Compliant with IEEE 802.3u Standard

- Non-Blocking Switch Fabric Ensures Fast Packet Delivery by Utilizing a 1k MAC Address Lookup Table and a Store-and-Forward Architecture

- Full-Duplex IEEE 802.3x Flow Control (PAUSE) with Force Mode Option

- Half-Duplex Back Pressure Flow Control

- HP Auto MDI-X for Reliable Detection of and Correction for Straight-Through and Crossover Cables with Disable and Enable Option

- LinkMD<sup>®</sup> TDR-Based Cable Diagnostics Permit Identification of Faulty Copper Cabling

- MII Interface Supports Both MAC Mode and PHY Mode

- Comprehensive LED Indicator Support for Link, Activity, Full-/Half-Duplex and 10/100 Speed

- HBM ESD Rating 4 kV

- · Switch Monitoring Features

- Port Mirroring/Monitoring/Sniffing: Ingress and/ or Egress Traffic to Any Port or MII

- MIB Counters for Fully Compliant Statistics Gathering 34 MIB Counters Per Port

- Loopback Modes for Remote Diagnostic of Fail-

- · Low Power Dissipation

- Full-Chip Software Power-Down (Register Configuration Not Saved)

- Energy-Detect Mode Support

- Dynamic Clock Tree Shutdown Feature

- Per Port Based Software Power-Save on PHY (Idle Link Detection, Register Configuration Preserved)

- Voltages: Single 3.3V Supply with Internal 1.8V LDO for 3.3V VDDIO

- Optional 3.3V, 2.5V, and 1.8V for VDDIO

- Transceiver Power 3.3V for VDDA\_3.3

- Industrial Temperature Range: –40°C to +85°C

- · Available in a 48-Pin LQFP, Lead-Free Package

#### **Applications**

- VolP Phone

- · Set-Top/Game Box

- Automotive

- · Industrial Control

- IPTV POF

- · SOHO Residential Gateway

- Broadband Gateway/Firewall/VPN

- · Integrated DSL/Cable Modem

- Wireless LAN Access Point + Gateway

- Standalone 10/100 Switch

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### **Table of Contents**

| 1.0 Introduction                                                |    |

|-----------------------------------------------------------------|----|

| 2.0 Pin Description and Configuration                           | 5  |

| 3.0 Functional Description                                      | 11 |

| 4.0 Register Descriptions                                       | 36 |

| 5.0 Operational Characteristics                                 | 71 |

| 6.0 Electrical Characteristics                                  | 72 |

| 7.0 Timing Specifications                                       | 74 |

| 8.0 Reset Circuit                                               | 84 |

| 9.0 Selection of Isolation Transformers                         | 85 |

| 10.0 Package Outline                                            | 86 |

| Appendix A. Data Sheet Revision History  The Microchip Web Site | 87 |

| The Microchip Web Site                                          | 88 |

| Customer Change Notification Service                            | 88 |

| Customer Support                                                | 88 |

| Product Identification System                                   |    |

#### 1.0 INTRODUCTION

#### 1.1 General Description

KSZ8863MLL, KSZ8863FLL, and KSZ8863RLL are highly integrated 3-port switch-on-a-chip ICs in the industry's smallest footprint. They are designed to enable a new generation of low port count, cost-sensitive, and power-efficient 10/100 Mbps switch systems. Low power consumption, advanced power management, and sophisticated QoS features (for example, IPv6 priority classification support) make these devices ideal for IPTV, IP-STB, VoIP, automotive, and industrial applications.

The KSZ8863 family is designed to support the GREEN requirement in today's switch systems. Advanced power management schemes include software power down, per port power down, and energy detect mode that shuts down the transceiver when a port is idle.

KSZ8863MLL/FLL/RLL also offers a bypass mode that enables system-level power saving. In this mode, the processor connected to the switch through the MII interface can be shut down without impacting the normal switch operation.

The configurations provided by the KSZ8863 family enable the flexibility to meet the requirements of different applications:

- KSZ8863MLL: Two 10/100BASE-T/TX transceivers and one MII interface

- KSZ8863RLL: Two 10/100BASE-T/TX transceivers and one RMII interface

- KSZ8863FLL: One 100BASE-FX, one 10/100BASE-T/TX transceivers, and one MII interface

The devices are available in RoHS-compliant 48-pin LQFP packages. Industrial-grade and automotive-grade are also available.

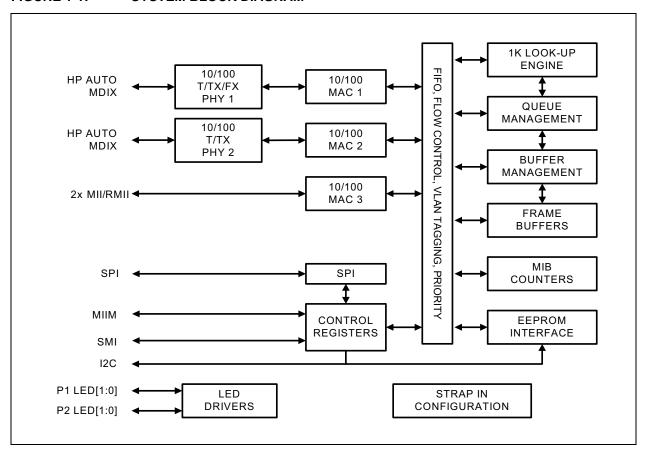

FIGURE 1-1: SYSTEM BLOCK DIAGRAM

#### 2.0 PIN DESCRIPTION AND CONFIGURATION

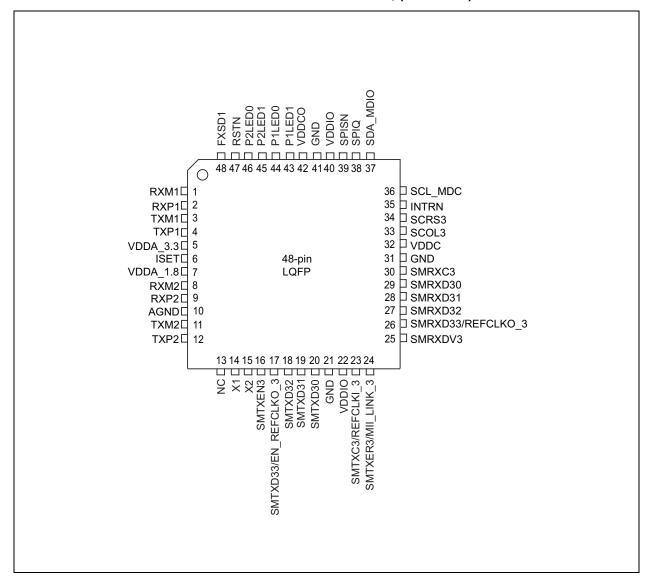

FIGURE 2-1: 48-PIN 7 MM X 7 MM LQFP ASSIGNMENT, (TOP VIEW)

TABLE 2-1: SIGNALS

| Pin<br>Number | Pin<br>Name              | Type<br>Note 2-1 | Description                                                                                                                                                                                                                                                           |

|---------------|--------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | RXM1                     | I/O              | Physical receive or transmit signal (– differential)                                                                                                                                                                                                                  |

| 2             | RXP1                     | I/O              | Physical receive or transmit signal (+ differential)                                                                                                                                                                                                                  |

| 3             | TXM1                     | I/O              | Physical transmit or receive signal (– differential)                                                                                                                                                                                                                  |

| 4             | TXP1                     | I/O              | Physical transmit or receive signal (+ differential)                                                                                                                                                                                                                  |

| 5             | VDDA_3.3                 | Р                | 3.3V analog V <sub>DD</sub>                                                                                                                                                                                                                                           |

| 6             | ISET                     | 0                | Set physical transmit output current. Pull down this pin with an 11.8 k $\Omega$ 1% resistor to ground.                                                                                                                                                               |

| 7             | VDDA_1.8                 | Р                | 1.8V analog core power input from VDDCO (pin 42).                                                                                                                                                                                                                     |

| 8             | RXM2                     | I/O              | Physical receive or transmit signal (– differential)                                                                                                                                                                                                                  |

| 9             | RXP2                     | I/O              | Physical receive or transmit signal (+ differential)                                                                                                                                                                                                                  |

| 10            | AGND                     | GND              | Analog ground                                                                                                                                                                                                                                                         |

| 11            | TXM2                     | I/O              | Physical transmit or receive signal (– differential)                                                                                                                                                                                                                  |

| 12            | TXP2                     | I/O              | Physical transmit or receive signal (+ differential)                                                                                                                                                                                                                  |

| 13            | NC                       | NC               | No connection                                                                                                                                                                                                                                                         |

| 14            | X1                       | I                | 25 MHz or 50 MHz crystal or oscillator clock connections. Pins (X1 and X2) connect to a crystal. If an oscillator is used, X1 connects to a 3.3V tolerant oscillator, and X2 is a NC.                                                                                 |

| 15            | X2                       | 0                | Note: The clock is ±50 ppm for both crystal and oscillator. The clock should be applied to X1 pin before the reset voltage goes high.                                                                                                                                 |

| 16            | SMTXEN3                  | lpu              | Switch MII transmit enable                                                                                                                                                                                                                                            |

| 17            | SMTXD33/<br>EN_REFCLKO_3 | lpu              | MLL/FLL: Switch MII transmit data bit 3 RLL: Strap option: RMII mode Clock selection PU = Enable REFCLKO_3 output PD = Disable REFCLKO_3 output                                                                                                                       |

| 18            | SMTXD32                  | lpu              | Switch MII transmit data bit 2 RLL: <b>Strap option:</b> X1 pin Clock selection (for Rev A3 and behind A3) PU = 25 MHz to X1 pin as clock source (default) PD = 50 MHz to X1 pin as clock source to provide or receive 50 MHz RMII reference clock for RLL part       |

| 19            | SMTXD31                  | lpu              | Switch MII/RMII transmit data bit 1                                                                                                                                                                                                                                   |

| 20            | SMTXD30                  | lpu              | Switch MII/RMII transmit data bit 0                                                                                                                                                                                                                                   |

| 21            | GND                      | GND              | Digital ground                                                                                                                                                                                                                                                        |

| 22            | VDDIO                    | Р                | 3.3V, 2.5V, or 1.8V digital $\ensuremath{V_{DD}}$ input power supply for IO with well decoupling capacitors                                                                                                                                                           |

| 23            | SMTXC3/<br>REFCLKI_3     | I/O              | MLL/FLL: Switch MII transmit clock (MII and SNI modes only) Output in PHY MII mode and SNI mode Input in MAC MII and RMII mode RLL: Reference clock input Note: Pull-down by resistor is needed if the internal reference clock is used in RLL by register 198 bit 3. |

| 24            | SMTXER3/<br>MII_LINK_3   | lpd              | Switch port 3 MII transmit error in MII mode  0 = MII link indicator from host in MII PHY mode  1 = No link on port 3 MII PHY mode and enable bypass mode                                                                                                             |

TABLE 2-1: SIGNALS (CONTINUED)

| IADLL 2-      | 0.0.0, (20            | CONTINO          | -29                                                                                                                                                                                                                                                                                                                                               |

|---------------|-----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Number | Pin<br>Name           | Type<br>Note 2-1 | Description                                                                                                                                                                                                                                                                                                                                       |

| 25            | SMRXDV3               | lpu/O            | Switch MII/RMII receive data valid  Strap option: Force duplex mode (P1DPX)  PU = Port 1 default to full-duplex mode if P1ANEN = 1 and auto-negotiation fails. Force port 1 in full-duplex mode if P1ANEN = 0.  PD = Port 1 default to half-duplex mode if P1ANEN = 1 and auto-negotiation fails. Force port 1 in half-duplex mode if P1ANEN = 0. |

| 26            | SMRXD33/<br>REFCLKO_3 | lpu/O            | MLL/FLL: Switch MII receive data bit 3 RLL: Output reference clock in RMII mode.  Strap option: enable auto-negotiation on port 2 (P2ANEN) PU = Enable PD = Disable                                                                                                                                                                               |

| 27            | SMRXD32               | lpu/O            | Switch MII receive data bit 2  Strap option: Force the speed on port 2 (P2SPD)  PU = Force port 2 to 100BT if P2ANEN = 0  PD = Force port 2 to 10BT if P2ANEN = 0                                                                                                                                                                                 |

| 28            | SMRXD31               | lpu/O            | Switch MII/RMII receive data bit 1  Strap option: Force duplex mode (P2DPX)  PU = Port 2 default to full-duplex mode if P2ANEN = 1 and auto-negotiation fails. Force port 2 in full-duplex mode if P2ANEN = 0.  PD = Port 2 set to half-duplex mode if P2ANEN = 1 and auto-negotiation fails. Force port 2 in half-duplex mode if P2ANEN = 0.     |

| 29            | SMRXD30               | lpu/O            | Switch MII/RMII receive data bit 0  Strap option: Force flow control on port 2 (P2FFC)  PU = Always enable (force) port 2 flow control feature.  PD = Port 2 flow control feature enable is determined by auto-negotiation result.                                                                                                                |

| 30            | SMRXC3                | I/O              | Switch MII receive clock. Output in PHY MII mode Input in MAC MII mode                                                                                                                                                                                                                                                                            |

| 31            | GND                   | GND              | Digital ground                                                                                                                                                                                                                                                                                                                                    |

| 32            | VDDC                  | Р                | 1.8V digital core power input from VDDCO (pin 42)                                                                                                                                                                                                                                                                                                 |

| 33            | SCOL3                 | lpu/O            | Switch MII collision detect                                                                                                                                                                                                                                                                                                                       |

| 34            | SCRS3                 | lpu/O            | Switch MII carrier sense                                                                                                                                                                                                                                                                                                                          |

| 35            | INTRN                 | Opu              | Interrupt Active-low signal to host CPU to indicate an interrupt status bit is set when lost link. Refer to register 187 and 188.                                                                                                                                                                                                                 |

| 36            | SCL_MDC               | I/O              | SPI Slave mode/I <sup>2</sup> C Slave mode: clock input I <sup>2</sup> C Master mode: clock output MIIM clock input                                                                                                                                                                                                                               |

| 37            | SDA_MDIO              | lpu/O            | SPI Slave mode: serial data input I <sup>2</sup> C Master/Slave mode: serial data input/output MIIM: Data input/output Note: An external pull-up is needed on this pin when it is in use.                                                                                                                                                         |

| 38            | SPIQ                  | lpd/O            | SPI Slave mode: serial data output Note: An external pull-up is needed on this pin when it is in use.  Strap option: Force flow control on port 1 (P1FFC) PU = Always enable (force) port 1 flow control feature PD = Port 1 flow control feature enable is determined by auto-negotiation result.                                                |

#### TABLE 2-1: SIGNALS (CONTINUED)

| TABLE 2-1. GIGNALO (GGNTINGLE) |             |                  |                                                                                                                                                                                                                                                                                                                                            |  |

|--------------------------------|-------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin<br>Number                  | Pin<br>Name | Type<br>Note 2-1 | Description                                                                                                                                                                                                                                                                                                                                |  |

| 39                             | SPISN       | lpd              | SPI Slave mode: chip select (active-low) When SPISN is high, KSZ8863MLL/FLL/RLL is deselected and SPIQ is held in a high impedance state. A high-to-low transition is used to initiate SPI data transfer. Note: An external pull-up is needed on this pin when using SPI or MDC MDIO-MIIM/SMI mode.                                        |  |

| 40                             | VDDIO       | Р                | 3.3V, 2.5V, or 1.8V digital $V_{\text{DD}}$ input power supply for IO with well decoupling capacitors                                                                                                                                                                                                                                      |  |

| 41                             | GND         | GND              | Digital ground                                                                                                                                                                                                                                                                                                                             |  |

| 42                             | VDDCO       | Р                | 1.8V core power voltage output (internal 1.8V LDO regulator output) This 1.8V output pin provides power to both VDDA_1.8 and VDDC input pins. Note: Internally, 1.8V LDO regulator input comes from VDDIO. Do not connect an external power supply to VDDCO pin. The ferrite bead is requested between analog and digital 1.8V core power. |  |

| 43                             | P1LED1      | lpu/O            | Port 1 LED Indicators: Default: Speed (refer to register 195 bit [5:4]) Strap option: Force the speed on port 1 (P1SPD) PU = Force port 1 to 100BT if P1ANEN = 0 PD = Force port 1 to 10BT if P1ANEN = 0                                                                                                                                   |  |

| 44                             | P1LED0      | lpd/O            | Port 1 LED Indicators:  Default: Link/Act. (refer to register 195 bit [5:4])  Strap option: Enable auto-negotiation on port 1 (P1ANEN)  PU = Enable (better to pull up in design)  PD = Disable (default)                                                                                                                                  |  |

TABLE 2-1: SIGNALS (CONTINUED)

| Pin    | Pin    | Туре     | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description                                        | on                                                                                       |        |                                                            |

|--------|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------|--------|------------------------------------------------------------|

| Number | Name   | Note 2-1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |                                                                                          |        |                                                            |

| 45     | P2LED1 | lpu/O    | Port 2 LED Indicators: Default: Speed (refer to register 195 bit [5:4]) Strap option: Serial bus configuration  Port 2 LED Indicators: Default: Link/Act. (refer to register 195 bit [5:4]) Strap option: Serial bus configuration Serial bus configuration pins to select mode of access to KSZ8863MLL/ FLL/RLL internal registers.  [P2LED1, P2LED0] = [0, 0] — I <sup>2</sup> C Master (EEPROM) mode (If EEPROM is not detected, the KSZ8863MLL/FLL/RLL is configured with the default values of its internal registers and the values of its strap-in pins.) |                                                    |                                                                                          |        |                                                            |

|        |        |          | Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Туре                                               | Description                                                                              |        |                                                            |

|        |        |          | SPIQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                  | Not used (tri-stated)                                                                    |        |                                                            |

|        |        |          | SCL_MDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                  | I <sup>2</sup> C clock                                                                   |        |                                                            |

|        |        |          | SDA_MDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I/O                                                | I <sup>2</sup> C data I/O                                                                |        |                                                            |

|        |        |          | SPISN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I                                                  | Not used                                                                                 |        |                                                            |

|        |        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    | 1011_1111 <read> 1011_1110 <write>  Interface Signals SPIQ SCL_MDC</write></read>        | Type O | Description  Not used (tri-stated)  I <sup>2</sup> C clock |

|        |        |          | SDA_MDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I/O                                                | I <sup>2</sup> C data I/O                                                                |        |                                                            |

| 46     | P2LED0 | lpu/O    | SPISN     [P2LED1, P2LED0] = [1,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | │I<br>0] — SPI Slave                               | Not used mode                                                                            |        |                                                            |

|        |        | J        | Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Туре                                               | Description                                                                              |        |                                                            |

|        |        |          | SPIQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                  | SPI data out                                                                             |        |                                                            |

|        |        |          | SCL_MDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                  | SPI clock                                                                                |        |                                                            |

|        |        |          | SDA_MDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I                                                  | SPI data in                                                                              |        |                                                            |

|        |        |          | SPISN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I                                                  | SPI chip select                                                                          |        |                                                            |

|        |        |          | bit registers through its SO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LL/FLL/RLL pro<br>CL_MDC and SI<br>ILL/FLL/RLL pro | vides access to all its internal 8-<br>DA_MDIO pins.<br>ovides access to its 16-bit MIIM |        |                                                            |

| 47     | RSTN   | lpu      | Hardware reset pin (active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | e-low)                                             |                                                                                          |        |                                                            |

| 48     | FXSD1  | I        | MLL/RLL: No connection or connect to analog ground by 1 k $\Omega$ pull-down resistor. FLL: Fiber signal detect                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |                                                                                          |        |                                                            |

#### Note 2-1 P = power supply

GND = Ground

I = Input

O = Output

I/O = Bi-directional

Ipu/O = Input with internal pull-up during reset; output pin otherwise.

Ipu = Input with internal pull-up. Ipd = Input with internal pull-down. Opu = Output with internal pull-up. Opd = Output with internal pull-down.

Speed: Low (100BASE-TX), High (10BASE-T) Full-Duplex: Low (full-duplex), High (half-duplex)

Activity: Toggle (transmit/receive activity)

Link: Low (link), High (no link)

#### 3.0 FUNCTIONAL DESCRIPTION

KSZ8863MLL/FLL/RLL contains two 10/100 physical layer transceivers and three MAC units with an integrated layer 2 managed switch.

KSZ8863MLL/FLL/RLL has the flexibility to reside in either a managed or unmanaged design. In a managed design, the host processor has complete control of KSZ8863MLL/FLL/RLL via the SMI interface, MIIM interface, SPI bus, or I<sup>2</sup>C bus. An unmanaged design is achieved through I/O strapping and/or EEPROM programming at system reset time.

On the media side, KSZ8863MLL/FLL/RLL supports IEEE 802.3 10BASE-T and 100BASE-TX on both PHY ports. Physical signal transmission and reception are enhanced through the use of patented analog circuitries that make the design more efficient and allow for lower power consumption and smaller chip die size.

#### 3.1 Physical Layer Transceiver

#### 3.1.1 100BASE-TX TRANSMIT

The 100BASE-TX transmit function performs parallel-to-serial conversion, 4B/5B coding, scrambling, NRZ-to-NRZI conversion, and MLT3 encoding and transmission.

The circuitry starts with a parallel-to-serial conversion, which converts the MII data from the MAC into a 125 MHz serial bit stream. The data and control stream is then converted into 4B/5B coding, followed by a scrambler. The serialized data is further converted from NRZ-to-NRZI format, and then transmitted in MLT3 current output. The output current is set by an external 1% 11.8 k $\Omega$  resistor for the 1:1 transformer ratio.

The output signal has a typical rise/fall time of 4 ns and complies with the ANSI TP-PMD standard regarding amplitude balance, overshoot, and timing jitter. The wave-shaped 10BASE-T output is also incorporated into the 100BASE-TX transmitter.

#### 3.1.2 100BASE-TX RECEIVE

The 100BASE-TX receiver function performs adaptive equalization, DC restoration, MLT3-to-NRZI conversion, data and clock recovery, NRZI-to-NRZ conversion, de-scrambling, 4B/5B decoding, and serial-to-parallel conversion.

The receiving side starts with the equalization filter to compensate for inter-symbol interference (ISI) over the twisted pair cable. Since the amplitude loss and phase distortion is a function of the cable length, the equalizer must adjust its characteristics to optimize performance. In this design, the variable equalizer makes an initial estimation based on comparisons of incoming signal strength against some known cable characteristics, and then tunes itself for optimization. This is an ongoing process and self-adjusts against environmental changes such as temperature variations.

Next, the equalized signal goes through a DC restoration and data conversion block. The DC restoration circuit is used to compensate for the effect of baseline wander and to improve the dynamic range. The differential data conversion circuit converts the MLT3 format back to NRZI. The slicing threshold is also adaptive.

The clock recovery circuit extracts the 125 MHz clock from the edges of the NRZI signal. This recovered clock is then used to convert the NRZI signal into the NRZ format. This signal is sent through the de-scrambler followed by the 4B/5B decoder. Finally, the NRZ serial data is converted to the MII format and provided as the input data to the MAC.

#### 3.1.3 PLL CLOCK SYNTHESIZER

KSZ8863MLL/FLL/RLL generates 125 MHz, 62.5 MHz, and 31.25 MHz clocks for system timing. Internal clocks are generated from an external 25 MHz or 50 MHz crystal or oscillator. KSZ8863RLL can generate a 50 MHz reference clock for the RMII interface.

#### 3.1.4 SCRAMBLER/DE-SCRAMBLER (100BASE-TX ONLY)

The purpose of the scrambler is to spread the power spectrum of the signal to reduce electromagnetic interference (EMI) and baseline wander. Transmitted data is scrambled through the use of an 11-bit wide linear feedback shift register (LFSR). The scrambler generates a 2047-bit non-repetitive sequence, and the receiver then de-scrambles the incoming data stream using the same sequence as at the transmitter.

#### 3.1.5 100BASE-FX OPERATION

The 100BASE-FX operation is similar to the 100BASE-TX operation with the differences being that the scrambler/descrambler and MLT3 encoder/decoder are bypassed on transmission and reception. In addition, auto-negotiation is bypassed and auto MDI/MDI-X is disabled.

#### 3.1.6 100BASE-FX SIGNAL DETECTION

In 100BASE-FX operation, FXSD (fiber signal detect), input pin 48, is usually connected to the fiber transceiver SD (signal detect) output pin. The fiber signal threshold can be selected by register 192 bit 6 for port 1. When FXSD is less than the threshold, no fiber signal is detected and a far-end fault (FEF) is generated. When FXSD is over the threshold, the fiber signal is detected.

Alternatively, the designer may choose not to implement the FEF feature. In this case, the FXSD input pin is tied high to force 100BASE-FX mode.

100BASE-FX signal detection is summarized in Table 3-1:

TABLE 3-1: FX SIGNAL THRESHOLD

| Register 192 Bit 7, Bit 6 (Port 1) | Fiber Signal Threshold at FXSD |

|------------------------------------|--------------------------------|

| 1                                  | 2.0V                           |

| 0                                  | 1.2V                           |

To ensure proper operation, a resistive voltage divider is recommended to adjust the fiber transceiver SD output voltage swing to match the FXSD pin's input voltage threshold.

#### 3.1.7 100BASE-FX FAR-END FAULT

A far-end fault (FEF) occurs when the signal detection is logically false on the receive side of the fiber transceiver. The KSZ8863FLL detects a FEF when its FXSD input is below the Fiber Signal Threshold. When a FEF is detected, KSZ8863FLL signals its fiber link partner that a FEF has occurred by sending 84 1's followed by a zero in the idle period between frames. By default, FEF is enabled.

#### 3.1.8 10BASE-T TRANSMIT

The 10BASE-T driver is incorporated with the 100BASE-TX driver to allow for transmission using the same magnetics. They are internally wave-shaped and pre-emphasized into outputs with a typical 2.3V amplitude. The harmonic contents are at least 27 dB below the fundamental frequency when driven by an all-ones Manchester-encoded signal.

#### 3.1.9 10BASE-T RECEIVE

On the receive side, input buffers and level detecting squelch circuits are employed. A differential input receiver circuit and a phase-locked loop (PLL) perform the decoding function. The Manchester-encoded data stream is separated into clock signal and NRZ data. A squelch circuit rejects signals with levels less than 400 mV or with short pulse widths to prevent noise at the RXP-or-RXM input from falsely triggering the decoder. When the input exceeds the squelch limit, the PLL locks onto the incoming signal and KSZ8863MLL/FLL/RLL decodes a data frame. The receiver clock is maintained active during idle periods in between data reception.

#### 3.1.10 MDI/MDI-X AUTO CROSSOVER

To eliminate the need for crossover cables between similar devices, KSZ8863MLL/FLL/RLL supports HP Auto MDI/MDI-X and IEEE 802.3u standard MDI/MDI-X auto crossover. HP Auto MDI/MDI-X is the default.

The auto-sense function detects remote transmit and receive pairs and correctly assigns transmit and receive pairs for the KSZ8863MLL/FLL/RLL device. This feature is extremely useful when end users are unaware of cable types, and also, saves on an additional uplink configuration connection. The auto-crossover feature can be disabled through the port control registers, or MIIM PHY registers.

The IEEE 802.3u standard MDI and MDI-X definitions are illustrated in Table 3-2.

TABLE 3-2: MDI/MDI-X PIN DEFINITIONS

|                    | MDI | МС         | DI-X    |

|--------------------|-----|------------|---------|

| RJ-45 Pins Signals |     | RJ-45 Pins | Signals |

| 1                  | TD+ | 1          | RD+     |

| 2                  | TD- | 2          | RD-     |

| 3                  | RD+ | 3          | TD+     |

| 6                  | RD- | 6          | TD-     |

#### 3.1.10.1 Straight Cable

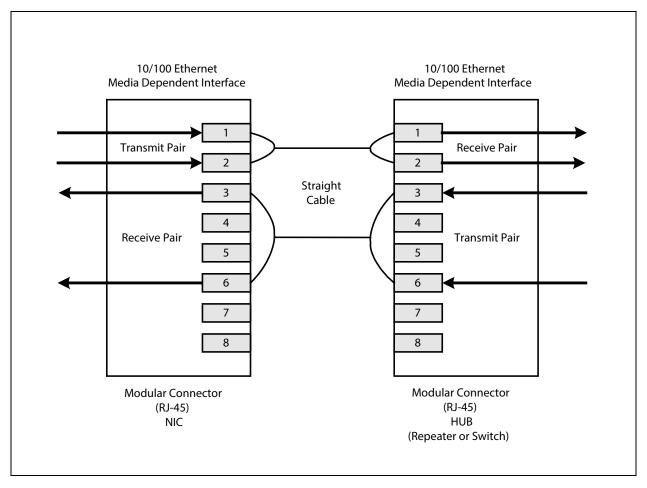

A straight cable connects an MDI device to an MDI-X device, or an MDI-X device to an MDI device. Figure 3-1 depicts a typical straight cable connection between a NIC card (MDI) and a switch, or hub (MDI-X).

FIGURE 3-1: TYPICAL STRAIGHT CABLE CONNECTION

#### 3.1.10.2 Crossover Cable

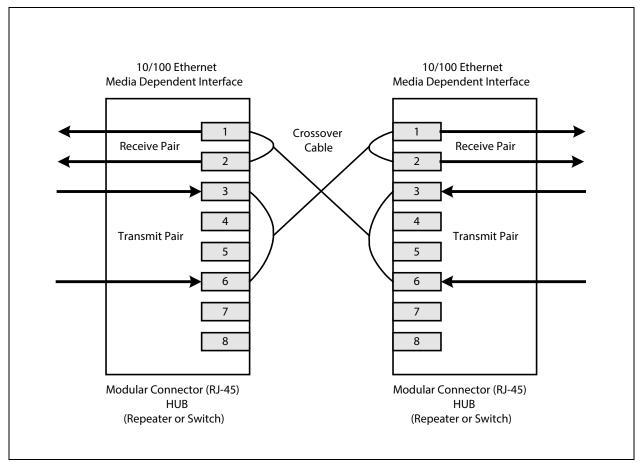

A crossover cable connects an MDI device to another MDI device, or an MDI-X device to another MDI-X device. Figure 3-2 shows a typical crossover cable connection between two switches or hubs (two MDI-X devices).

FIGURE 3-2: TYPICAL CROSSOVER CABLE CONNECTION

#### 3.1.11 AUTO-NEGOTIATION

KSZ8863MLL/FLL/RLL conforms to the auto-negotiation protocol defined in Clause 28 of the IEEE 802.3u specification.

Auto-negotiation allows unshielded twisted pair (UTP) link partners to select the best common mode of operation. In auto-negotiation, link partners advertise their capabilities across the link to each other. If auto-negotiation is not supported or the KSZ8863MLL/FLL/RLL link partner is forced to bypass auto-negotiation, KSZ8863MLL/FLL/RLL sets its operating mode by observing the signal at its receiver. This is known as parallel detection, and allows KSZ8863MLL/FLL/RLL to establish a link by listening for a fixed signal protocol in the absence of auto-negotiation advertisement protocol.

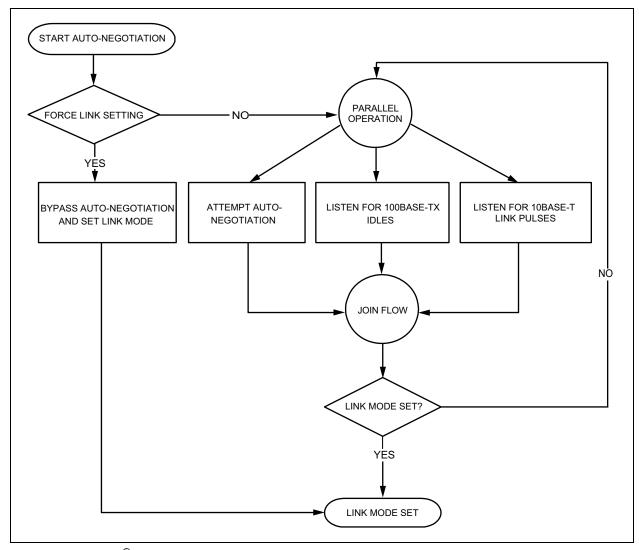

The link up process is shown in Figure 3-3.

#### FIGURE 3-3: AUTO-NEGOTIATION AND PARALLEL OPERATION

#### 3.1.12 LINKMD® CABLE DIAGNOSTICS

KSZ8863MLL/FLL/RLL supports LinkMD. The LinkMD feature utilizes time domain reflectometry (TDR) to analyze the cabling plant for common cabling problems such as open circuits, short circuits, and impedance mismatches.

LinkMD works by sending a pulse of known amplitude and duration down the MDI and MDI-X pairs and then analyzes the shape of the reflected signal. Timing the pulse duration gives an indication of the distance to the cabling fault. Internal circuitry displays the TDR information in a user-readable digital format.

Cable diagnostics are only valid for copper connections and do not support fiber optic operation.

#### 3.1.12.1 Access

LinkMD is initiated through accessing the PHY special control/status registers {26, 42} and the LinkMD result registers {27, 43} for ports 1 and 2 respectively; and in conjunction with the port registers control 13 for ports 1 and 2 respectively to disable Auto MDI/MDIX.

Alternatively, the MIIM PHY registers 0 and 29 can be used for LinkMD access.

#### 3.1.12.2 Usage

The following is a sample procedure for using LinkMD with registers {42, 43, 45} on port 2:

Disable auto MDI/MDI-X by writing a '1' to register 45, bit [2] to enable manual control over the differential pair used to transmit the LinkMD pulse.

- 2. Start cable diagnostic test by writing a '1' to register 42, bit [4]. This enable bit is self-clearing.

- 3. Wait (poll) for register 42, bit [4] to return a '0', indicating cable diagnostic test is complete.

- 4. Read cable diagnostic test results in register 42, bits [6:5]. The results are as follows:

- 00 = normal condition (valid test)

- 01 = open condition detected in cable (valid test)

- 10 = short condition detected in cable (valid test)

- 11 = cable diagnostic test failed (invalid test)

The '11' case, invalid test, occurs when KSZ8863MLL/FLL/RLL is unable to shut down the link partner. In this instance, the test is not run because it is impossible for KSZ8863MLL/FLL/RLL to determine if the detected signal is a reflection of the signal generated or a signal from another source.

5. Get the distance to fault by concatenating register 42, bit [0] and register 43, bits [7:0]; and multiplying the result by a constant of 0.4. The distance to the cable fault can be determined by the following formula:

#### **EQUATION 3-1:**

$D(Distance \text{ to cable fault in meters}) = 0.4 \times (Register 26 \text{ bit } [0] \times Register 27 \text{ bits } [7:0])$

Concatenated values of registers 42 and 43 are converted to decimal before multiplying by 0.4.

The constant (0.4) may be calibrated for different cabling conditions, including cables with a velocity of propagation that varies significantly from the norm.

#### 3.2 Power Management

KSZ8863MLL/FLL/RLL supports enhanced power management feature in low power state with energy detection to ensure low-power dissipation during device idle periods. There are five operation modes under the power management function, which is controlled by two bits in register 195 (0xC3) and one bit in register 29 (0x1D), 45(0x2D) as shown below:

- Register 195 bit [1:0] = 00 Normal Operation Mode

- Register 195 bit [1:0] = 01 Energy Detect Mode

- Register 195 bit [1:0] = 10 Soft Power Down Mode

- Register 195 bit [1:0] = 11 Power Saving Mode

- Register 29, 45 bit 3 = 1 Port Based Power Down Mode

Table 3-3 indicates all internal function blocks status under four different power management operation modes.

#### TABLE 3-3: INTERNAL FUNCTION BLOCK STATUS

| KSZ8863MLL/FLL/RLL | Power Management Operation Modes |                          |                       |                         |  |  |

|--------------------|----------------------------------|--------------------------|-----------------------|-------------------------|--|--|

| Function Blocks    | Normal Mode                      | Power Saving<br>Mode     | Energy Detect<br>Mode | Soft Power Down<br>Mode |  |  |

| Internal PLL Clock | Enabled                          | Enabled                  | Disabled              | Disabled                |  |  |

| Tx/Rx PHY          | Enabled                          | Rx unused block disabled | Energy detect at Rx   | Disabled                |  |  |

| MAC                | Enabled                          | Enabled                  | Disabled              | Disabled                |  |  |

| Host Interface     | Enabled                          | Enabled                  | Disabled              | Disabled                |  |  |

#### 3.2.1 NORMAL OPERATION MODE

This is the default setting bit [1:0] = 00 in register 195 after the chip power-up or hardware reset. When KSZ8863MLL/FLL/RLL is in this normal operation mode, all PLL clocks are running, PHY and MAC are on, and the host interface is ready for CPU read or write.

During the normal operation mode, the host CPU can set the bit [1:0] in register 195 to transit the current normal operation mode to any one of the other three power management operation modes.

#### 3.2.2 POWER SAVING MODE

The power saving mode is entered when auto-negotiation mode is enabled, cable is disconnected, and bit [1:0] = 11 in register 195 is set. When KSZ8863MLL/FLL/RLL is in this mode, all PLL clocks are enabled, MAC is on, all internal register values are not changed, and the host interface is ready for CPU read or write. In this mode, it mainly controls the PHY transceiver on or off based on line status to achieve power saving. The PHY remains transmitting and only turns off the unused receiver block. Once the activity resumes due to plugging a cable or attempting by the far end to establish a link, KSZ8863MLL/FLL/RLL can automatically enable the PHY power-up to normal power state from power saving mode.

During the power saving mode, the host CPU can set bit [1:0] = 0 in register 195 to transit the current power saving mode to any one of the other three power management operation modes.

#### 3.2.3 ENERGY DETECT MODE

The energy detect mode provides a mechanism to save more power than in the normal operation mode when KSZ8863MLL/FLL/RLL is not connected to an active link partner. In this mode, the device saves up to 87% of the power. If the cable is not plugged, KSZ8863MLL/FLL/RLL can automatically enter a low-power state, that is, the energy detect mode. In this mode, KSZ8863MLL/FLL/RLL keeps transmitting 120 ns width pulses at a rate of 1 pulse/second. Once the activity resumes due to plugging a cable or attempting by the far end to establish a link, KSZ8863MLL/FLL/RLL can automatically power up to normal power state in energy detect mode.

Energy detect mode consists of two states: normal power state and low power state. In low power state, KSZ8863MLL/FLL/RLL reduces the power consumption by disabling all circuitries except the energy detect circuitry of the receiver. The energy detect mode is entered by setting bit [1:0] = 01 in register 195. When KSZ8863MLL/FLL/RLL is in this mode, it monitors the cable energy. If there is no energy on the cable for a time longer than the pre-configured value at bit [7:0] Go-Sleep time in register 196, KSZ8863MLL/FLL/RLL goes into a low power state. When KSZ8863MLL/FLL/RLL is in low power state, it keeps monitoring the cable energy. Once the energy is detected from the cable, KSZ8863MLL/FLL/RLL enters the normal power state. When KSZ8863MLL/FLL/RLL is in the normal power state, it can transmit or receive packet from the cable.

It saves about 87% of the power when the MII interface is in PHY mode (register 53 bit 7 = 0), pin SMTXER3/MII\_LINK\_3 is connected to High, register 195 bit [1:0] = 01, bit 2 = 1(Disable PLL), and no cables are connected.

#### 3.2.4 SOFT POWER DOWN MODE

The soft power down mode is entered by setting bit [1:0] = 10 in register 195. When KSZ8863MLL/FLL/RLL is in this mode, all PLL clocks are disabled, PHY and MAC are off, and all internal register values are not changed. When the host set bit [1:0] = 00 in register 195, this device reverts from current soft power down mode to normal operation mode.

#### 3.2.5 PORT-BASED POWER DOWN MODE

In addition, KSZ8863MLL/FLL/RLL features a per-port power down mode. To save power, a PHY port that is not in use can be powered down via the port control register 29 or 45 bit 3, or the MIIM PHY register. It saves about 15 mA per port.

#### 3.3 MAC and Switch

#### 3.3.1 ADDRESS LOOKUP

The internal lookup table stores MAC addresses and their associated information. It contains a 1K unicast address table plus switching information.

KSZ8863MLL/FLL/RLL is guaranteed to learn 1K addresses and distinguishes itself from hash-based lookup tables, which depending on the operating environment and probabilities, may not guarantee the absolute number of addresses it can learn.

#### 3.3.2 LEARNING

The internal lookup engine updates its table with a new entry if the following conditions are met:

- · The received packet's Source Address (SA) does not exist in the lookup table.

- The received packet is good; the packet has no receiving errors and is of legal length.

The lookup engine inserts the qualified SA into the table, along with the port number and time stamp. If the table is full, the last entry of the table is deleted to make room for the new entry.

#### 3.3.3 MIGRATION

The internal lookup engine also monitors whether a station has moved. If a station has moved, it updates the table accordingly. Migration happens when the following conditions are met:

- The received packet's SA is in the table, but the associated source port information is different.

- · The received packet is good; the packet has no receiving errors and is of legal length.

The lookup engine updates the existing record in the table with the new source port information.

#### 3.3.4 AGING

The lookup engine updates the time stamp information of a record whenever the corresponding SA appears. The time stamp is used in the aging process. If a record is not updated for a period of time, the lookup engine removes the record from the table. The lookup engine constantly performs the aging process and continuously removes aging records. The aging period is about 200 seconds. This feature can be enabled or disabled through register 3 (0x03) bit [2].

#### 3.3.5 FORWARDING

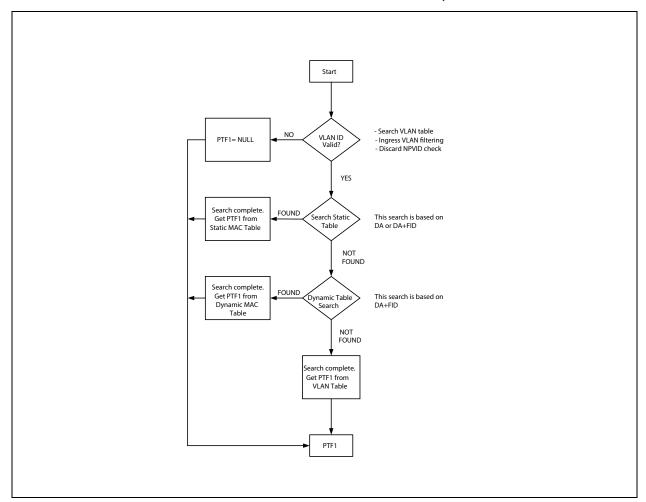

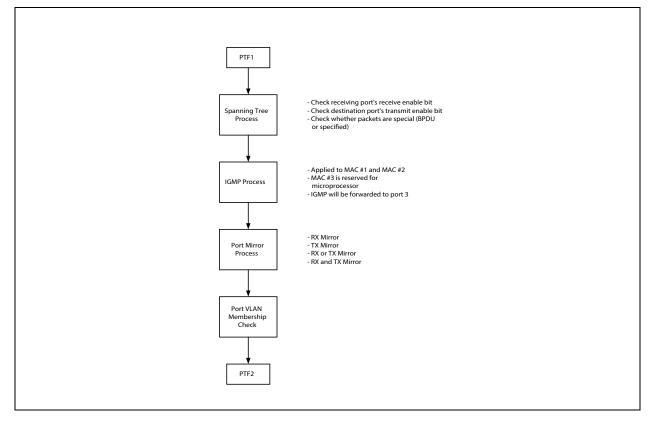

KSZ8863MLL/FLL/RLL forwards packets using the algorithm that is depicted in the following flowcharts. Figure 3-4 shows stage one of the forwarding algorithm, where the search engine looks up the VLAN ID, static table, and dynamic table for the destination address, and comes up with "port to forward 1" (PTF1). PTF1 is then further modified by spanning tree, IGMP snooping, port mirroring, and port VLAN processes to come up with "port to forward 2" (PTF2), as shown in Figure 3-5. The packet is sent to PTF2.

FIGURE 3-4: DESTINATION ADDRESS LOOKUP FLOW CHART, STAGE 1

FIGURE 3-5: DESTINATION ADDRESS RESOLUTION FLOW CHART, STAGE 2

KSZ8863MLL/FLL/RLL does not forward the following packets:

- Error packets: These include framing errors, Frame Check Sequence (FCS) errors, alignment errors, and illegal size packet errors.

- 2. IEEE802.3x PAUSE frames: KSZ8863MLL/FLL/RLL intercepts these packets and performs full duplex flow control accordingly.

- 3. "Local" packets: Based on destination address (DA) lookup. If the destination port from the lookup table matches the port from which the packet originated, the packet is defined as local.

#### 3.3.6 SWITCHING ENGINE

KSZ8863MLL/FLL/RLL features a high-performance switching engine to move data to and from the MAC's packet buffers. It operates in store and forward mode, while the efficient switching mechanism reduces overall latency.

The switching engine has a 32-kb internal frame buffer. This buffer pool is shared among all three ports. There are a total of 256 buffers available. Each buffer is sized at 128 bytes.

#### 3.3.7 MAC OPERATION

KSZ8863MLL/FLL/RLL strictly abides by IEEE 802.3 standards to maximize compatibility.

#### 3.3.7.1 Inter Packet Gap (IPG)

If a frame is successfully transmitted, the 96 bits time IPG is measured between the two consecutive MTXEN. If the current packet is experiencing collision, the 96 bits time IPG is measured from MCRS and the next MTXEN.

#### 3.3.7.2 Back-Off Algorithm

KSZ8863MLL/FLL/RLL implements the IEEE 802.3 standard for the binary exponential back-off algorithm and the optional "aggressive mode" back-off. After 16 collisions, the packet is optionally dropped depending on the switch configuration for register 4 (0x04) bit [3].

#### 3.3.7.3 Late Collision

If a transmit packet experiences collisions after 512 bit times of the transmission, the packet is dropped.

#### 3.3.7.4 Illegal Frames

KSZ8863MLL/FLL/RLL discards frames less than 64 bytes and can be programmed to accept frames up to 1518 bytes, 1536 bytes, or 1916 bytes. These maximum frame size settings are programmed in register 4 (0x04). Since KSZ8863MLL/FLL/RLL supports VLAN tags, the maximum sizing is adjusted when these tags are present.

#### 3.3.7.5 Full-Duplex Flow Control

KSZ8863MLL/FLL/RLL supports the standard IEEE 802.3x flow control frames on both transmit and receive sides.

On the receive side, if KSZ8863MLL/FLL/RLL receives a pause control frame, KSZ8863MLL/FLL/RLL does not transmit the next normal frame until the timer, specified in the pause control frame, expires. If another pause frame is received before the current timer expires, the timer is updated with the new value in the second pause frame. During this period (while it is flow controlled), only flow control packets from KSZ8863MLL/FLL/RLL are transmitted.

On the transmit side, KSZ8863MLL/FLL/RLL has intelligent and efficient ways to determine when to invoke flow control. The flow control is based on availability of the system resources, including available buffers, available transmit queues and available receive queues.

KSZ8863MLL/FLL/RLL will flow control a port that has just received a packet if the destination port resource is busy. KSZ8863MLL/FLL/RLL issues a flow control frame (XOFF) containing the maximum pause time defined by the IEEE 802.3x standard. Once the resource is freed up, KSZ8863MLL/FLL/RLL sends out the other flow control frame (XON) with zero pause time to turn off the flow control (turn on transmission to the port). A hysteresis feature is provided to prevent the flow control mechanism from being constantly activated and deactivated.

KSZ8863MLL/FLL/RLL flow controls all ports if the receive gueue becomes full.

#### 3.3.7.6 Half-Duplex Backpressure

A half-duplex backpressure option (not in IEEE 802.3 standards) is also provided. The activation and deactivation conditions are the same as a full-duplex flow control. If backpressure is required, KSZ8863MLL/FLL/RLL sends preambles to defer the other stations' transmission (carrier sense deference).

To avoid jabber and excessive deference (as defined in the IEEE 802.3 standard), after a certain time, KSZ8863MLL/FLL/RLL discontinues the carrier sense and then raises it again quickly. This short silent time (no carrier sense) prevents other stations from sending out packets, thus keeping other stations in a carrier sense deferred state. If the port has packets to send during a backpressure situation, the carrier sense type backpressure is interrupted and those packets are transmitted instead. If there are no additional packets to send, carrier sense type backpressure is activated again until switch resources free up. If a collision occurs, the binary exponential back-off algorithm is skipped and carrier sense is generated immediately, thus reducing the chance of further collisions and maintaining carrier sense to prevent packet reception.

To ensure that no packet is lost in 10BASE-T or 100BASE-TX half-duplex modes, the user must enable the following:

- Aggressive back-off (register 3 (0x03), bit [0])

- No excessive collision drop (register 4 (0x04), bit [3])

Note that these bits are not set as defaults because it is not the IEEE standard.

#### 3.3.7.7 Broadcast Storm Protection

KSZ8863MLL/FLL/RLL has an intelligent option to protect the switch system from receiving too many broadcast packets. As the broadcast packets are forwarded to all ports except the source port, an excessive number of switch resources (bandwidth and available space in transmit queues) may be utilized. KSZ8863MLL/FLL/RLL can opt to include "multicast packets" for storm control. The broadcast storm rate parameters are programmed globally and can be enabled or disabled on a per-port basis. The rate is based on a 67 ms interval for 100BT and a 500 ms interval for 10BT. At the beginning of each interval, the counter is cleared to zero, and the rate limit mechanism starts to count the number of bytes during the interval. The rate definition is described in register 6 (0x06) and 7 (0x07). The default setting is 0x63 (99 decimal). This is equal to a rate of 1%, calculated as follows:

148,800 frames/sec × 67 ms/interval × 1% = 99 frames/interval (approx.) = 0x63

Note: The 148,800 frames/sec is based on 64-byte block of packets in 100BASE-TX with 12 bytes of IPG and 8 bytes of preamble between two packets.

#### 3.3.7.8 Port Individual MAC Address and Source Port Filtering

KSZ8863MLL/FLL/RLL provides individual MAC address for port 1 and port 2. They can be set at registers 142-147 and 148-153. The packet is filtered if its source address matches the MAC address of port 1 or port 2 when register 21 and 37 bit 6 is set to 1, respectively. For example, the packet is dropped after it completes the loop of a ring network.

#### 3.3.8 MII INTERFACE OPERATION

The Media Independent Interface (MII) is specified in Clause 22 of the IEEE 802.3u standard. It provides a common interface between physical layer and MAC layer devices. The MII provided by KSZ8863MLL/FLL is connected to the device's third MAC; the MII default is PHY mode and can be set to MAC mode with the register 53 bit 7. The interface contains two distinct groups of signals: one for transmission and the other for reception. Table 3-4 describes the signals used by the MII bus.

TABLE 3-4: MII SIGNALS

| PHY Mode Connections               |                               |                     | MAC Mode                | de Connections                |  |

|------------------------------------|-------------------------------|---------------------|-------------------------|-------------------------------|--|

| External MAC<br>Controller Signals | KSZ8863MLL/FLL<br>PHY Signals | Pin Description     | External PHY<br>Signals | KSZ8863MLL/FLL<br>MAC Signals |  |

| MTXEN                              | SMTXEN3                       | Transmit Enable     | MTXEN                   | SMRXDV3                       |  |

| MTXER                              | SMTXER3                       | Transmit Error      | MTXER                   | (NOT USED)                    |  |

| MTXD3                              | SMTXD33                       | Transmit Data Bit 3 | MTXD3                   | SMRXD33                       |  |

| MTXD2                              | SMTXD32                       | Transmit Data Bit 2 | MTXD2                   | SMRXD32                       |  |

| MTXD1                              | SMTXD31                       | Transmit Data Bit 1 | MTXD1                   | SMRXD31                       |  |

| MTXD0                              | SMTXD30                       | Transmit Data Bit 0 | MTXD0                   | SMRXD30                       |  |

| MTXC                               | SMTXC3                        | Transmit Clock      | MTXC                    | SMRXC3                        |  |

| MCOL                               | SCOL3                         | Collision Detection | MCOL                    | SCOL3                         |  |

| MCRS                               | SCRS3                         | Carrier Sense       | MCRS                    | SCRS3                         |  |

| MRXDV                              | SMRXDV3                       | Receive Data Valid  | MRXDV                   | SMTXEN3                       |  |

| MRXER                              | (NOT USED)                    | Receive Error       | MRXER                   | SMTXER3                       |  |

| MRXD3                              | SMRXD33                       | Receive Data Bit 3  | MRXD3                   | SMTXD33                       |  |

| MRXD2                              | SMRXD32                       | Receive Data Bit 2  | MRXD2                   | SMTXD32                       |  |

| MRXD1                              | SMRXD31                       | Receive Data Bit 1  | MRXD1                   | SMTXD31                       |  |

| MRXD0                              | SMRXD30                       | Receive Data Bit 0  | MRXD0                   | SMTXD30                       |  |

| MRXC                               | SMRXC3                        | Receive Clock       | MRXC                    | SMTXC3                        |  |

The MII operates in either PHY mode or MAC mode. The data interface is nibble-wide and runs at ¼ the network bit rate (not encoded). Additional signals on the transmit side indicate when data is valid or when an error occurs during transmission. Similarly, the receive side has signals that convey when the data is valid and without physical layer errors. For half-duplex operation, the SCOL signal indicates if a collision has occurred during transmission.

KSZ8863MLL/FLL does not provide the MRXER signal for PHY mode operation, and the MTXER signal for MAC mode operation. Normally, MRXER indicates a receive error coming from the physical layer device and MTXER indicates a transmit error from the MAC device. Because the switch filters error frames, these MII error signals are not used by KSZ8863MLL/FLL. So, for PHY mode operation, if the device interfacing with KSZ8863MLL/FLL has an MRXER input pin, it needs to be tied low. And, for MAC mode operation, if the device interfacing with KSZ8863MLL/FLL has an MTXER input pin, it also needs to be tied low.

KSZ8863MLL/FLL provides a bypass feature in the MII PHY mode. Pin SMTXER3/MII\_LINK is used for MII link status. If the host is powered down, pin MII\_LINK goes to high. In this case, no new ingress frames from port 1 or port 2 are sent out through port 3, and the frames for port 3 already in packet memory are flushed out.

#### 3.3.9 RMII INTERFACE OPERATION

The Reduced Media Independent Interface (RMII) specifies a low pin count Media Independent Interface (MII). RMII provides a common interface between physical layer and MAC layer devices, and has the following key characteristics:

- Ports 10 Mbps and 100 Mbps data rates

- · Uses a single 50 MHz clock reference (provided internally or externally)

- · Provides independent 2-bit wide (di-bit) transmit and receive data paths

- · Contains two distinct groups of signals: one for transmission and the other for reception

When EN\_REFCLKO\_3 is high, KSZ8863RLL outputs a 50 MHz in REFCLKO\_3. Register 198 bit [3] is used to select the internal or external reference clock. Internal reference clock means that the clock for the RMII of KSZ8863RLL is provided by KSZ8863RLL internally and the REFCLKI\_3 pin is unconnected. For the external reference clock, the clock provides to KSZ8863RLL via REFCLKI\_3.

If KSZ8863RLL does not provide the reference clock, this 50 MHz reference clock with divide-by-2 (25 MHz) has to be used in X1 pin instead of the 25 MHz crystal, since the clock skew of these two clock sources impacts the RMII timing before Rev A3 part. The Rev A3 part can connect the external 50 MHz reference clock to X1 pin and SMTXC3/REF-CLKI\_3 pins directly with strap pins of pin 17 SMTXD33/EN\_REFCLKO\_3 and pin 18 SMTXD32 to be pulled down.

TABLE 3-5: RMII CLOCK SETTING

| Reg. 198<br>Bit [3] | Pin 17 SMTXD33/<br>EN_REFCLKO_3<br>Internal pull-up | Pin 18 SMTXD32<br>Internal pull-up<br>(For Rev A3) | Clock Source                                                                                                                      | Note                                                                    |

|---------------------|-----------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

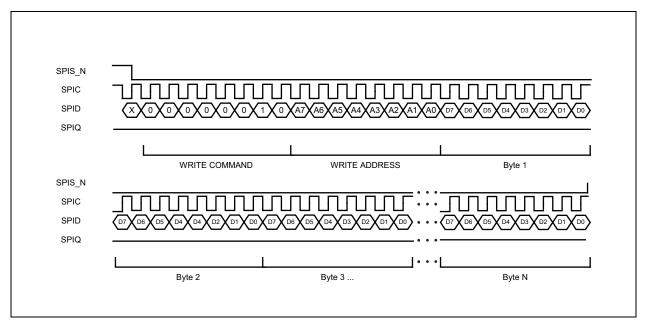

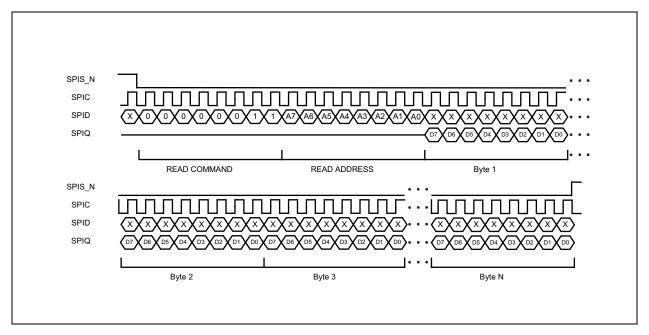

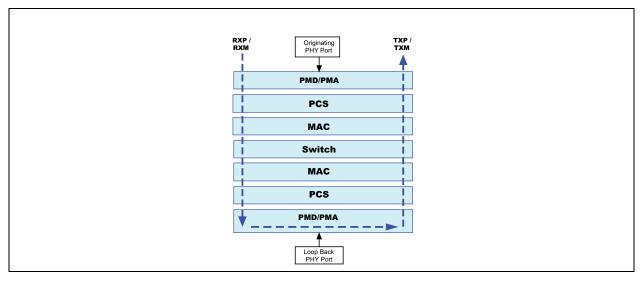

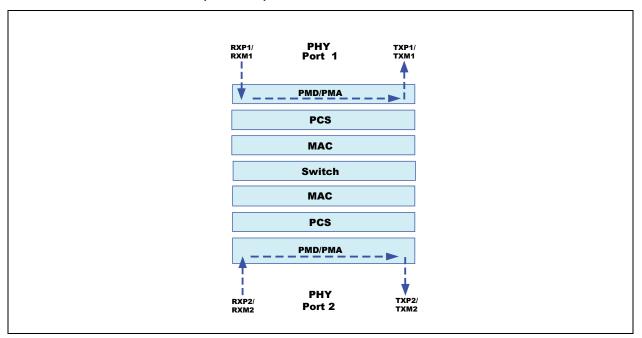

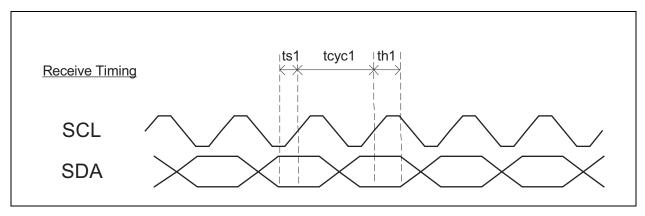

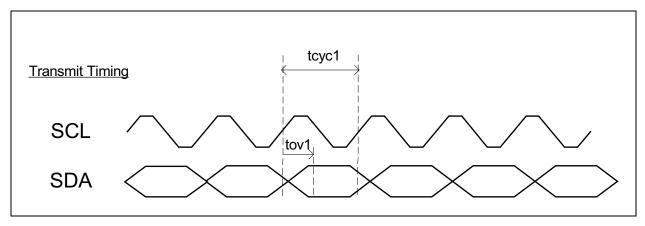

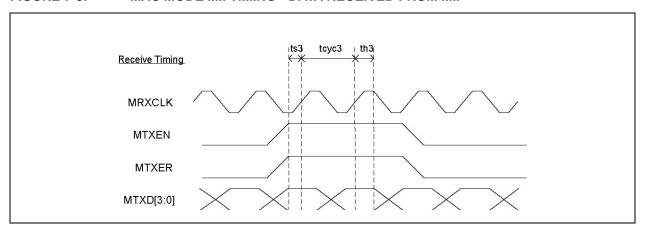

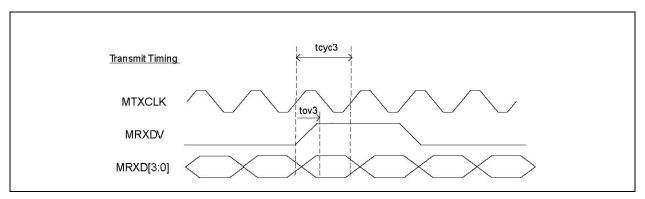

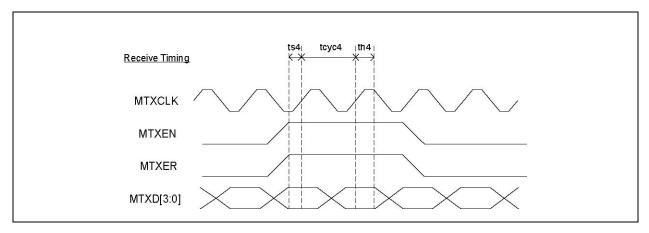

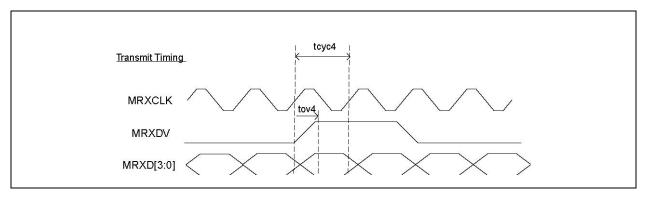

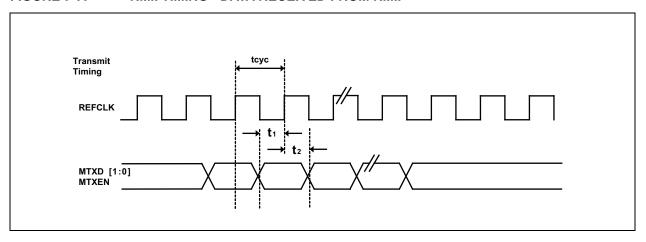

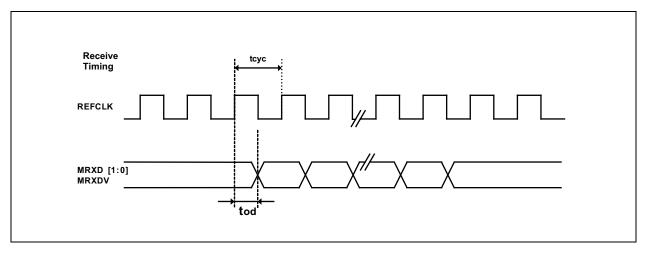

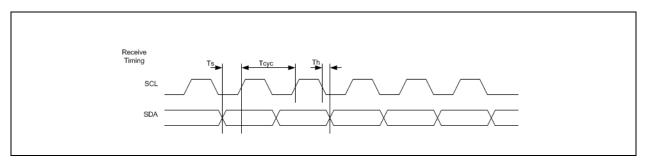

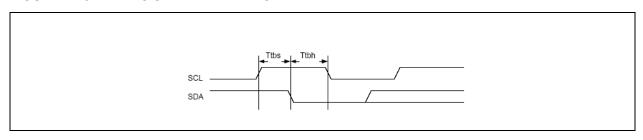

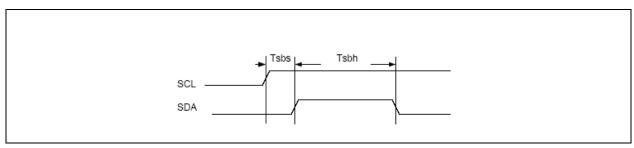

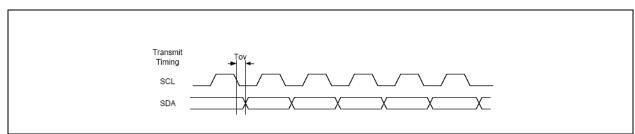

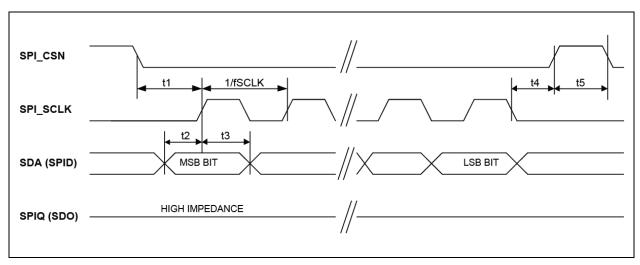

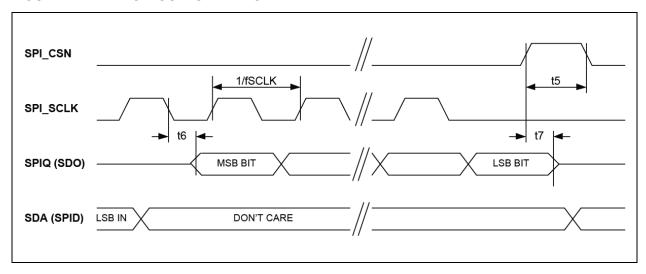

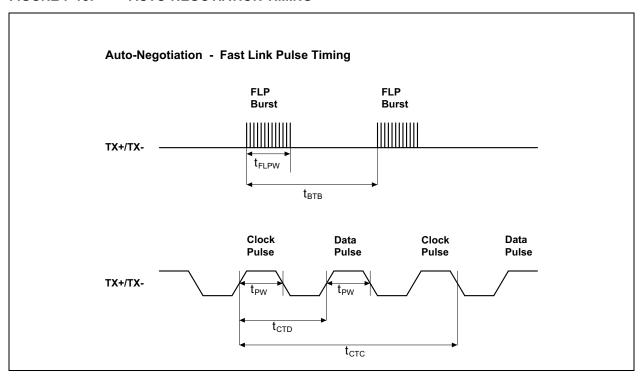

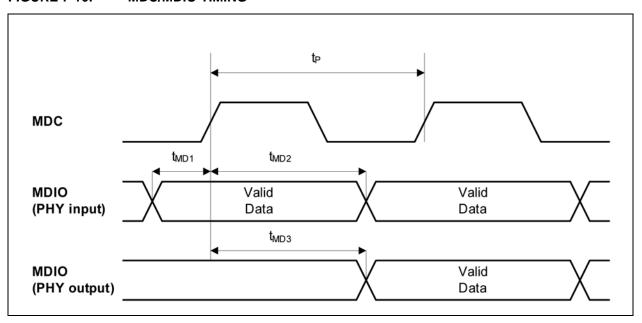

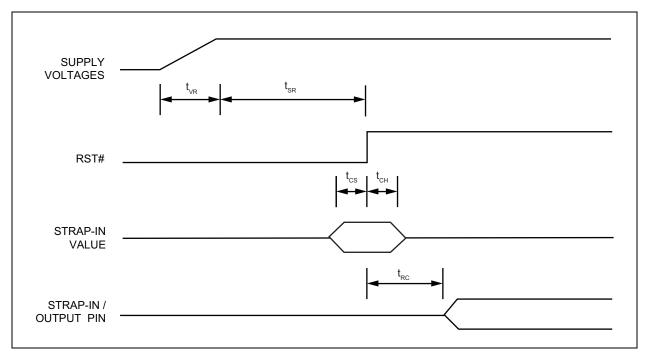

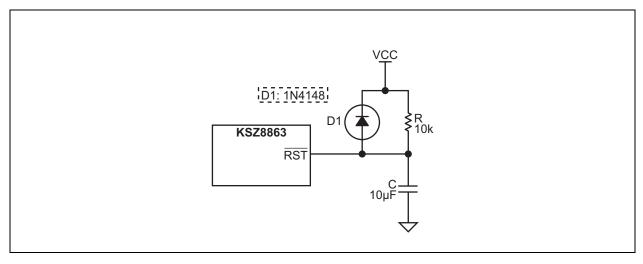

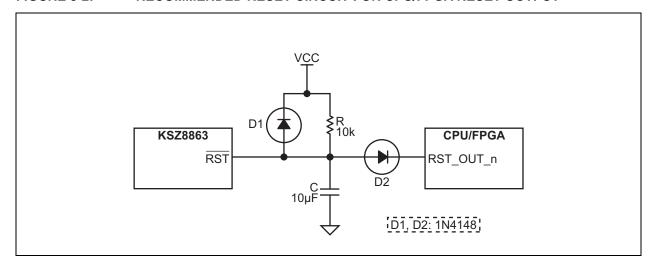

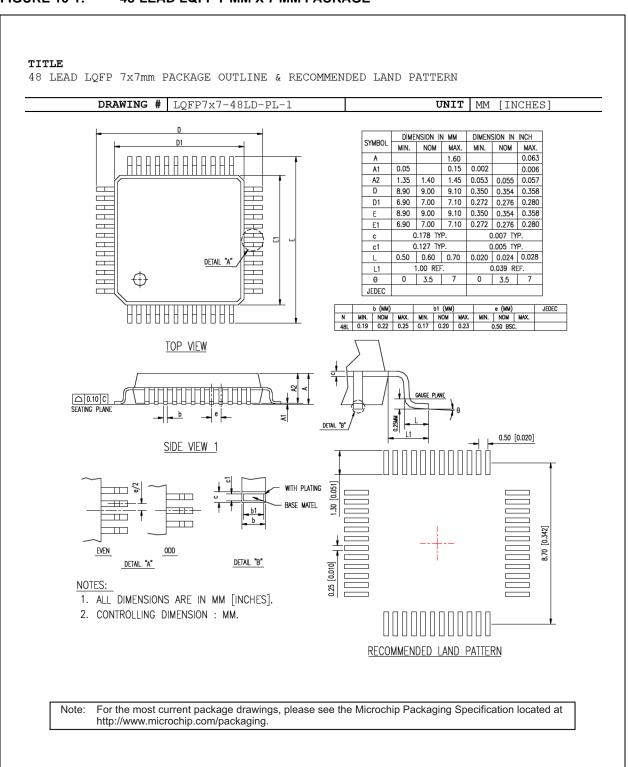

| 0                   | 0<br>(pull down by 1k)                              | 0<br>(pull down by 1k)                             | External 50 MHz OSC input to SMTXC3 /REFCLKI_3 and X1 pin directly                                                                | EN_REFCLKO_3 = 0 to<br>disable REFCLKO_3 for<br>better EMI              |