# **Switching Regulator - Automotive Buck, RESET**

# 1.2 A, 2 MHz

The NCV890103 is a fixed-frequency, monolithic, Buck switching regulator intended for Automotive, battery-connected applications that must operate with up to a 36 V input supply. The regulator is suitable for systems with low noise and small form factor requirements often encountered in automotive driver information systems. The NCV890103 is capable of converting the typical 4.5 V to 18 V automotive input voltage range to outputs as low as 3.3 V at a constant switching frequency above the sensitive AM band, eliminating the need for costly filters and EMI countermeasures. A Reset pin signals when the output is in regulation, and a pin is provided to adjust the delay before the RSTB signal goes high. The NCV890103 also provides several protection features expected in Automotive power supply systems such as current limit, short circuit protection, and thermal shutdown. In addition, the high switching frequency produces low output voltage ripple even when using small inductor values and an all-ceramic output filter capacitor - forming a space-efficient switching regulator solution.

#### Features

- Internal N-Channel Power Switch

- Low V<sub>IN</sub> Operation Down to 4.5 V

- High V<sub>IN</sub> Operation to 36 V

- Withstands Load Dump to 40 V

- 2 MHz Free-running Switching Frequency

- Logic level Enable Input Can be Directly Tied to Battery

- Reset with Adjustable Delay

- 1.4 A (min) Cycle-by-Cycle Peak Current Limit

- Short Circuit Protection enhanced by Frequency Foldback

- ±1.75% Output Voltage Tolerance

- Output Voltage Adjustable Down to 0.8 V

- 1.4 Millisecond Internal Soft-Start

- Thermal Shutdown (TSD)

# ON Semiconductor®

www.onsemi.com

#### **MARKING DIAGRAM**

#### DFN10 CASE 485C

A = Assembly Location

L = Wafer Lot Y = Year W = Work Week • Pb-Free Device

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 18 of this data sheet.

- Low Shutdown Current

- Wettable Flanks DFN (pin edge plating)

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb-Free and are RoHS Compliant

#### **Applications**

- Audio

- Infotainment

- Safety Vision Systems

- Instrumentation

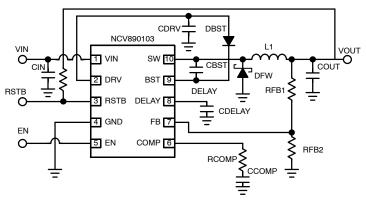

Figure 1. Typical Application

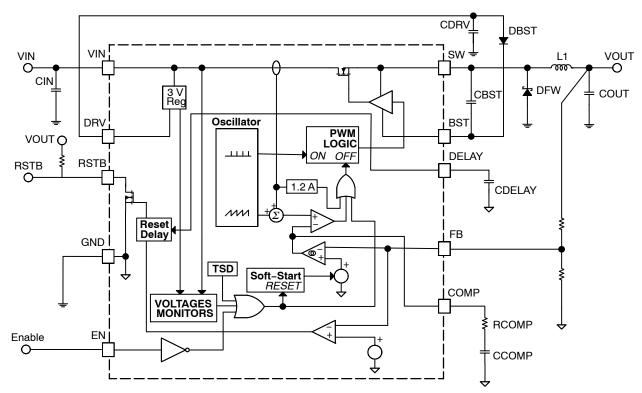

Figure 2. NCV890103 Block Diagram

# **MAXIMUM RATINGS**

| Rating                                           | Symbol           | Value       | Unit |

|--------------------------------------------------|------------------|-------------|------|

| Min/Max Voltage VIN, BST                         |                  | -0.3 to 40  | V    |

| Max Voltage VIN to SW                            |                  | 40          | V    |

| Min/Max Voltage SW                               |                  | -0.7 to 40  | V    |

| Min Voltage SW – 20ns                            |                  | -3.0        | V    |

| Min/Max Voltage BST to SW                        |                  | -0.3 to 3.6 | V    |

| Min/Max Voltage on EN                            |                  | -0.3 to 40  | V    |

| Min/Max Voltage COMP                             |                  | -0.3 to 2   | V    |

| Min/Max Voltage FB                               |                  | -0.3 to 18  | V    |

| Min/Max Voltage DRV, DELAY                       |                  | -0.3 to 3.6 | V    |

| Min/Max Voltage RSTB                             |                  | -0.3 to 6   | V    |

| Thermal Resistance, 3x3 DFN Junction-to-Ambient* | $R_{	hetaJA}$    | 50          | °C/W |

| Storage Temperature Range                        |                  | -55 to +150 | °C   |

| Operating Junction Temperature Range             | T <sub>J</sub>   | -40 to +150 | °C   |

| ESD withstand Voltage<br>Human Body Model        | V <sub>ESD</sub> | 2.0         | kV   |

| Moisture Sensitivity                             | MSL              | Level 1     |      |

| Peak Reflow Soldering Temperature                |                  | 260         | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

\*Mounted on 1 sq. in. of a 4-layer PCB with 1 oz. copper thickness.

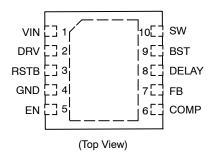

Figure 3. Pin Connections

# **PIN FUNCTION DESCRIPTIONS**

| Pin No.        | Symbol | Description                                                                                                                                                                                                                                |

|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | VIN    | Input voltage from battery. Place an input filter capacitor in close proximity to this pin.                                                                                                                                                |

| 2              | DRV    | Output voltage to provide a regulated voltage to the Power Switch gate driver.                                                                                                                                                             |

| 3              | RSTB   | RSTB open drain output. Goes high impedence when the output is above 94% of its regulation level, after the delay set by the DELAY pin times out. Goes low when the output is below 92 % of its regulation level (sensed on the FB signal) |

| 4              | GND    | Battery return, and output voltage ground reference.                                                                                                                                                                                       |

| 5              | EN     | This TTL compatible Enable input allows the direct connection of Battery as the enable signal. Grounding this input stops switching and reduces quiescent current draw to a minimum.                                                       |

| 6              | COMP   | Error Amplifier output, for tailoring transient response with external compensation components.                                                                                                                                            |

| 7              | FB     | Feedback input pin to program output voltage, and detect pre-charged or shorted output conditions.                                                                                                                                         |

| 8              | DELAY  | Delay adjust input. Connecting an external capacitor adjusts the delay for the RSTB function.                                                                                                                                              |

| 9              | BST    | Bootstrap input provides drive voltage higher than VIN to the N-channel Power Switch for optimum switch $R_{DS(on)}$ and highest efficiency.                                                                                               |

| 10             | SW     | Switching node of the Regulator. Connect the output inductor and cathode of the freewheeling diode to this pin.                                                                                                                            |

| Exposed<br>Pad |        | Connect to Pin 4 (electrical ground) and to a low thermal resistance path to the ambient temperature environment.                                                                                                                          |

## **ELECTRICAL CHARACTERISTICS**

$(V_{IN}$  = 4.5 V to 28 V,  $V_{EN}$  = 5 V,  $V_{BST}$  =  $V_{SW}$  + 3.0 V,  $C_{DRV}$  = 0.1  $\mu$ F, Min/Max values are valid for the temperature range  $-40^{\circ}C \le T_{J} \le 150^{\circ}C$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.)

| Parameter                                                     | Symbol                                     | Conditions                                                                                                             | Min          | Тур        | Max          | Unit |

|---------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------|------------|--------------|------|

| QUIESCENT CURRENT                                             |                                            |                                                                                                                        |              |            |              |      |

| Quiescent Current, shutdown                                   | $I_{qSD}$                                  | $V_{IN}$ = 13.2 V, $V_{EN}$ = 0 V, $T_{J}$ = 25°C                                                                      |              |            | 5            | μΑ   |

| Quiescent Current, enabled                                    | I <sub>qEN</sub>                           | V <sub>IN</sub> = 13.2 V                                                                                               |              |            | 3            | mA   |

| UNDERVOLTAGE LOCKOUT - VIN (UVLO)                             |                                            |                                                                                                                        |              |            |              |      |

| UVLO Start Threshold                                          | V <sub>UVLSTT</sub>                        | V <sub>IN</sub> rising                                                                                                 | 4.1          |            | 4.5          | V    |

| UVLO Stop Threshold                                           | V <sub>UVLSTP</sub>                        | V <sub>IN</sub> falling                                                                                                | 3.2          |            | 3.6          | V    |

| UVLO Hysteresis                                               | V <sub>UVLOHY</sub>                        |                                                                                                                        | 0.5          |            | 1.3          | V    |

| ENABLE (EN)                                                   |                                            |                                                                                                                        |              |            |              |      |

| Logic Low (Voltage input needed to guarantee logic low)       | V <sub>ENLO</sub>                          |                                                                                                                        |              |            | 0.8          | V    |

| Logic High (Voltage input needed to guarantee logic high)     | V <sub>ENHI</sub>                          |                                                                                                                        | 2            |            |              | V    |

| Input Current                                                 | I <sub>EN</sub>                            |                                                                                                                        | 8            |            | 30           | μΑ   |

| SOFT-START (SS)                                               |                                            |                                                                                                                        |              |            |              |      |

| Soft-Start Completion Time                                    | t <sub>SS</sub>                            |                                                                                                                        | 0.8          | 1.4        | 2.0          | ms   |

| VOLTAGE REFERENCE                                             |                                            |                                                                                                                        |              |            |              |      |

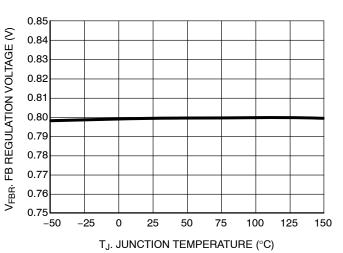

| FB Pin Voltage during regulation                              | $V_{FBR}$                                  | COMP shorted to FB                                                                                                     | 0.786        | 0.8        | 0.814        | V    |

| ERROR AMPLIFIER                                               |                                            |                                                                                                                        |              |            |              |      |

| FB Bias Current                                               | I <sub>FBBIAS</sub>                        | V <sub>FB</sub> = 0.8 V                                                                                                | 0.25         |            | 1            | μΑ   |

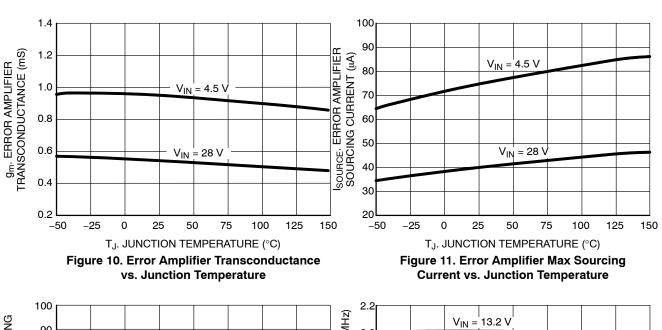

| Transconductance                                              | 9m<br>9m(HV)                               | V <sub>COMP</sub> = 1.3 V<br>4.5 V < V <sub>IN</sub> < 18 V<br>20 V < V <sub>IN</sub> < 28 V                           | 0.6<br>0.3   | 1<br>0.5   | 1.5<br>0.75  | mmho |

| Output Resistance                                             | R <sub>OUT</sub>                           |                                                                                                                        |              | 1.4        |              | МΩ   |

| COMP Source Current Limit                                     | I <sub>SOURCE</sub>                        | V <sub>FB</sub> = 0.63 V, V <sub>COMP</sub> = 1.3 V<br>4.5 V < V <sub>IN</sub> < 18 V<br>20 V < V <sub>IN</sub> < 28 V |              | 75<br>40   |              | μΑ   |

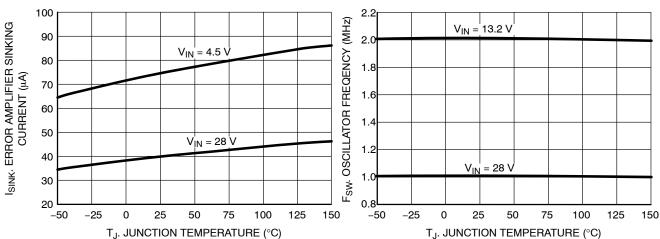

| COMP Sink Current Limit                                       | I <sub>SINK</sub>                          | V <sub>FB</sub> = 0.97 V, V <sub>COMP</sub> = 1.3 V<br>4.5 V < V <sub>IN</sub> < 18 V<br>20 V < V <sub>IN</sub> < 28 V |              | 75<br>40   |              | μΑ   |

| Minimum COMP voltage                                          | V <sub>CMPMIN</sub>                        | V <sub>FB</sub> = 0.97 V                                                                                               | 0.05         |            | 0.55         | V    |

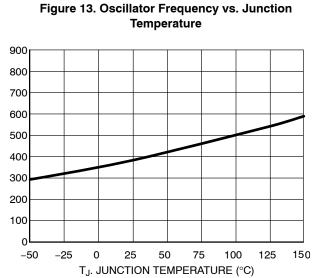

| OSCILLATOR                                                    |                                            |                                                                                                                        |              |            |              |      |

| Frequency                                                     | F <sub>SW</sub><br>F <sub>SW(HV)</sub>     | 4.5 < V <sub>IN</sub> < 18 V<br>20 V < V <sub>IN</sub> < 28 V                                                          | 1.8<br>0.9   | 2.0<br>1.0 | 2.2<br>1.1   | MHz  |

| VIN FREQUENCY FOLDBACK MONITOR                                |                                            |                                                                                                                        |              |            |              |      |

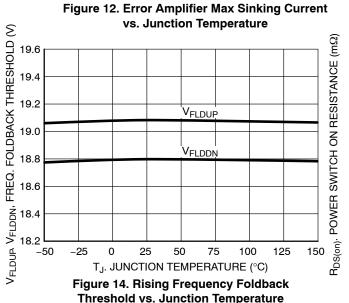

| Frequency Foldback Threshold $V_{IN}$ rising $V_{IN}$ falling | V <sub>FLDUP</sub><br>V <sub>FLDDN</sub>   | V <sub>FB</sub> = 0.63 V                                                                                               | 18.4<br>18   |            | 20<br>19.8   | V    |

| Frequency Foldback Hysteresis                                 | V <sub>FLDHY</sub>                         |                                                                                                                        | 0.2          | 0.3        | 0.4          | V    |

| SLOPE COMPENSATION                                            |                                            |                                                                                                                        |              |            |              |      |

| Ramp Slope (Note 1)<br>(With respect to switch current)       | S <sub>ramp</sub><br>S <sub>ramp(HV)</sub> | 4.5 < V <sub>IN</sub> < 18 V<br>20 V < V <sub>IN</sub> < 28 V                                                          | 1.70<br>0.80 |            | 3.20<br>1.60 | A/μs |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>1.</sup> Not tested in production. Limits are guaranteed by design.

# **ELECTRICAL CHARACTERISTICS** (continued)

$(V_{IN}=4.5~V~to~28~V, V_{EN}=5~V, V_{BST}=V_{SW}+3.0~V, C_{DRV}=0.1~\mu F$ , Min/Max values are valid for the temperature range  $-40^{\circ}C \leq T_{J} \leq 150^{\circ}C$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.)

| Parameter                                                                                    | Symbol                                                         | Conditions                                                                                                                                          | Min              | Тур              | Max              | Unit |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|------|

| RESET                                                                                        | •                                                              |                                                                                                                                                     |                  |                  | -                |      |

| Threshold (in percentage of targeted regulation $V_{\mbox{\scriptsize OUT}}$ ).              | K <sub>RESD</sub><br>K <sub>RESU</sub>                         | V <sub>OUT</sub> going down<br>V <sub>OUT</sub> going up                                                                                            | 90<br>92         | 92<br>94.5       | 94<br>97         | %    |

| Filtering delay (high-to-low transitions)                                                    | t <sub>RESD</sub>                                              | V <sub>OUT</sub> going down                                                                                                                         | 1.5              | 2.0              | 3.0              | μs   |

| Sink current                                                                                 | I <sub>RES</sub>                                               | V <sub>RESET</sub> = 0.4 V                                                                                                                          | 1                |                  |                  | mA   |

| DELAY                                                                                        |                                                                |                                                                                                                                                     |                  |                  |                  |      |

| Upper charging level                                                                         | V <sub>DELU</sub>                                              | V <sub>FB</sub> > K <sub>RESU</sub> x V <sub>FBR</sub>                                                                                              | 1.6              | 1.9              | 2.15             | V    |

| Lower detection threshold                                                                    | V <sub>DELTH</sub>                                             | V <sub>DELAY</sub> decreasing                                                                                                                       | 0.7              | 0.9              | 1.1              | V    |

| Discharging current                                                                          | I <sub>DELAY</sub>                                             | V <sub>DELAY</sub> = 1.5 V                                                                                                                          | 4.1              | 4.4              | 6.0              | μА   |

| Reset delay (low-to-high transition)                                                         | t <sub>RESU</sub>                                              | V <sub>OUT</sub> going up, C <sub>DELAY</sub> = 100 pF                                                                                              | 22               | 29               | 35               | μs   |

| POWER SWITCH                                                                                 | •                                                              |                                                                                                                                                     |                  |                  | -                |      |

| ON Resistance                                                                                | R <sub>DSON</sub>                                              | V <sub>BST</sub> = V <sub>SW</sub> + 3.0 V                                                                                                          |                  |                  | 650              | mΩ   |

| Leakage current VIN to SW                                                                    | I <sub>LKSW</sub>                                              | V <sub>EN</sub> = 0 V, V <sub>SW</sub> = 0, V <sub>IN</sub> = 18 V                                                                                  |                  |                  | 10               | μА   |

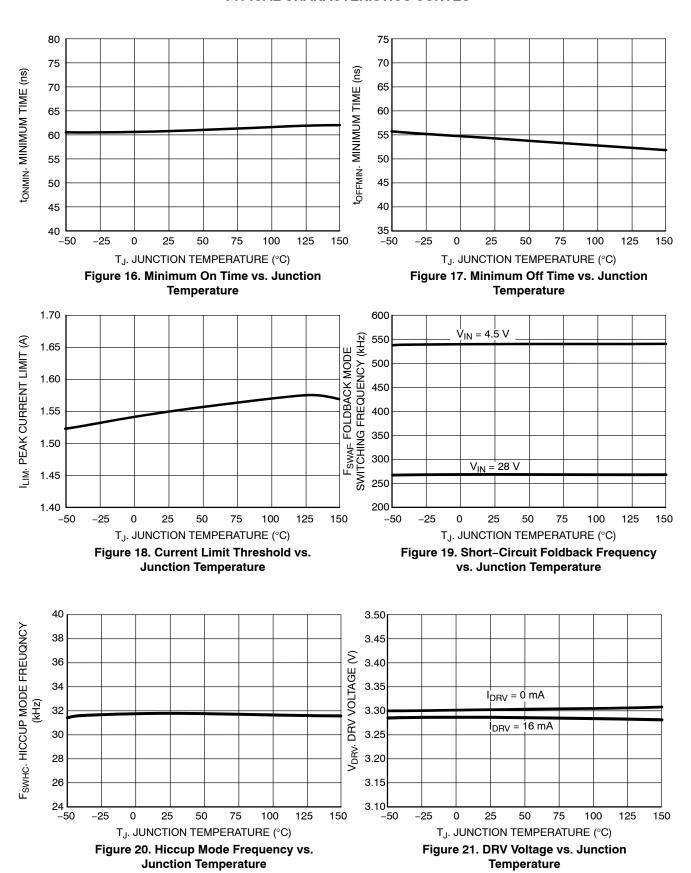

| Minimum ON Time                                                                              | tonmin                                                         | Measured at SW pin                                                                                                                                  | 45               |                  | 70               | ns   |

| Minimum OFF Time                                                                             | t <sub>OFFMIN</sub>                                            | Measured at SW pin At F <sub>SW</sub> = 2 MHz (normal) At F <sub>SW</sub> = 500 kHz (max duty cycle)                                                | 30               | 30<br>50         | 70               | ns   |

| PEAK CURRENT LIMIT                                                                           | •                                                              |                                                                                                                                                     |                  | •                |                  | •    |

| Current Limit Threshold                                                                      | I <sub>LIM</sub>                                               |                                                                                                                                                     | 2.1              | 2.35             | 2.6              | Α    |

| SHORT CIRCUIT FREQUENCY FOLDBAC                                                              | K                                                              |                                                                                                                                                     |                  |                  | •                |      |

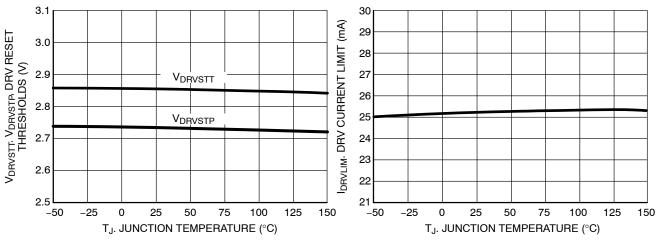

| Lowest Foldback Frequency<br>Lowest Foldback Frequency – High V <sub>in</sub><br>Hiccup Mode | F <sub>SWAF</sub><br>F <sub>SWAFHV</sub><br>F <sub>SWHIC</sub> | $V_{FB} = 0 \text{ V}, 4.5 \text{ V} < V_{IN} < 18 \text{ V} \\ V_{FB} = 0 \text{ V}, 20 \text{ V} < V_{IN} < 28 \text{ V} \\ V_{SW} = 0 \text{ V}$ | 400<br>200<br>24 | 500<br>250<br>32 | 600<br>300<br>40 | kHz  |

| GATE VOLTAGE SUPPLY (DRV pin)                                                                |                                                                |                                                                                                                                                     |                  |                  |                  |      |

| Output Voltage                                                                               | $V_{DRV}$                                                      |                                                                                                                                                     | 3.1              | 3.3              | 3.5              | V    |

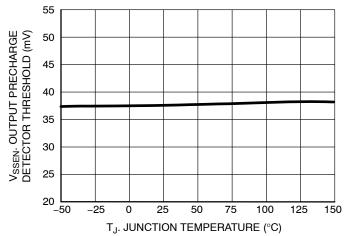

| DRV POR Start Threshold                                                                      | V <sub>DRVSTT</sub>                                            |                                                                                                                                                     | 2.7              | 2.9              | 3.05             | V    |

| DRV POR Stop Threshold                                                                       | V <sub>DRVSTP</sub>                                            |                                                                                                                                                     | 2.5              | 2.8              | 3.0              | V    |

| DRV Current Limit                                                                            | I <sub>DRVLIM</sub>                                            | V <sub>DRV</sub> = 0 V                                                                                                                              | 16               |                  | 45               | mA   |

| OUTPUT PRECHARGE DETECTOR                                                                    | •                                                              |                                                                                                                                                     |                  |                  | -                |      |

| Threshold Voltage                                                                            | $V_{SSEN}$                                                     |                                                                                                                                                     | 20               | 35               | 50               | mV   |

| THERMAL SHUTDOWN                                                                             | •                                                              |                                                                                                                                                     |                  | -                | -                | -    |

| Activation Temperature (Note 1)                                                              | T <sub>SD</sub>                                                |                                                                                                                                                     | 150              |                  | 190              | °C   |

| Hysteresis (Note 1)                                                                          | T <sub>HYS</sub>                                               |                                                                                                                                                     | 5                |                  | 20               | °C   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>1.</sup> Not tested in production. Limits are guaranteed by design.

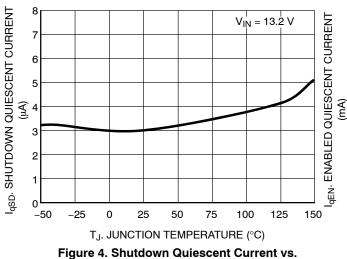

Figure 4. Shutdown Quiescent Current vs. Junction Temperature

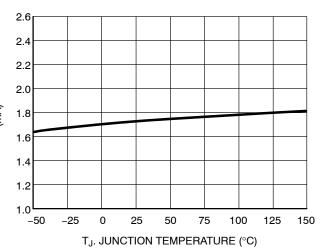

Figure 5. Enabled Quiescent Current vs.

Junction Temperature

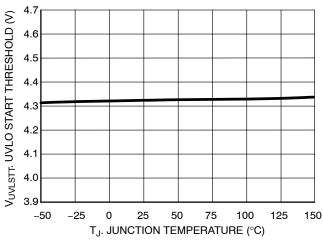

Figure 6. UVLO Start Threshold vs. Junction Temperature

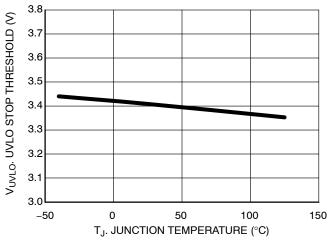

Figure 7. UVLO Stop Threshold vs. Junction Temperature

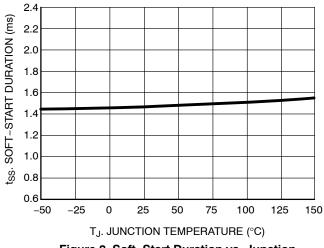

Figure 8. Soft-Start Duration vs. Junction Temperature

Figure 9. FB Regulation Voltage vs. Junction Temperature

Figure 22. DRV Reset Threshold vs. Junction Temperature

Figure 23. DRV Current Limit vs. Junction Temperature

Figure 24. Output Precharge Detector Threshold vs. Junction Temperature

#### **GENERAL INFORMATION**

#### **INPUT VOLTAGE**

An Undervoltage Lockout (UVLO) circuit monitors the input, and inhibits switching and resets the Soft–start circuit if there is insufficient voltage for proper regulation. The NCV890103 can regulate a 3.3 V output with input voltages above 4.5 V and a 5.0 V output with an input above 6.5 V.

The NCV890103 withstands input voltages up to 40 V.

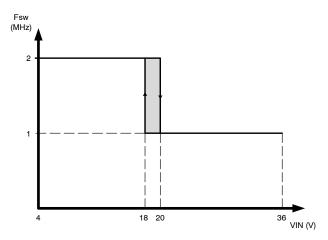

To limit the power lost in generating the drive voltage for the Power Switch, the switching frequency is reduced by a factor of 2 when the input voltage exceeds the  $V_{IN}$  Frequency Foldback threshold  $V_{FLDUP}$  (see Figure 25). Frequency reduction is automatically terminated when the input voltage drops back below the  $V_{IN}$  Frequency Foldback threshold  $V_{FLDDN}$ .

Figure 25. NCV890103 Switching Frequency Reduction at High Input Voltage

#### **ENABLE**

The NCV890103 is designed to accept either a logic level signal or battery voltage as an Enable signal. EN low induces a 'sleep mode' which shuts off the regulator and minimizes its supply current to a couple of  $\mu A$  typically ( $I_{qSD}$ ) by disabling all functions. Upon enabling, voltage is established at the DRV pin, followed by a soft–start of the switching regulator output.

#### SOFT-START

Upon being enabled or released from a fault condition, and after the DRV voltage is established, a soft–start circuit ramps the switching regulator error amplifier reference voltage to the final value. During soft–start, the average switching frequency is lower than its normal mode value (typically 2 MHz) until the output voltage approaches regulation.

#### **SLOPE COMPENSATION**

A fixed slope compensation signal is generated internally and added to the sensed current to avoid increased output voltage ripple due to bifurcation of inductor ripple current at duty cycles above 50%. The fixed amplitude of the slope compensation signal requires the inductor to be greater than a minimum value, depending on output voltage, in order to avoid sub–harmonic oscillations. For 3.3 V and 5 V output voltages, the recommended inductor value is 4.7 µH.

#### SHORT CIRCUIT FREQUENCY FOLDBACK

During severe output overloads or short circuits, the NCV890103 automatically reduces its switching frequency. This creates duty cycles small enough to limit the peak current in the power components, while maintaining the ability to automatically reestablish the output voltage if the overload is removed. If the current is still too high after the switching frequency folds back to 500 kHz, the regulator enters an auto-recovery burst mode that further reduces the dissipated power.

#### **CURRENT LIMITING**

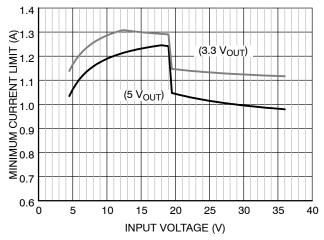

Due to the ripple on the inductor current, the average output current of a buck converter is lower than the peak current setpoint of the regulator. Figure 26 shows – for a 4.7  $\mu$ H inductor – how the variation of inductor peak current with input voltage affects the maximum DC current the NCV890103 can deliver to a load.

Figure 26. NCV890103 Load Current Capability with 4.7 µH Inductor

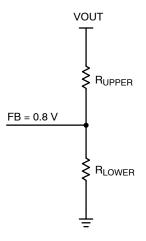

#### **OUTPUT VOLTAGE SELECTION**

The voltage output for the switcher is adjustable and can be set with a resistor divider. The FB reference for the switcher is 0.8 V.

Use the following equation:

$$R_{\text{UPPER}} = R_{\text{LOWER}} \, \frac{V_{\text{OUT}} \! - \! V_{\text{FB}}}{V_{\text{FB}}}$$

Some common setups are listed below:

| Desired<br>Output (V) | VREF (V) | R <sub>UPPER</sub><br>(Ω, 1%) | R <sub>LOWER</sub><br>(Ω, 1%) |

|-----------------------|----------|-------------------------------|-------------------------------|

| 1.2                   | 0.8      | 100                           | 200                           |

| 1.5                   | 0.8      | 100                           | 115                           |

| 1.8                   | 0.8      | 100                           | 80.6                          |

| 2.5                   | 0.8      | 100                           | 47.5                          |

| 3.3                   | 0.8      | 100                           | 32.4                          |

| 5.0                   | 0.8      | 100                           | 19.1                          |

# **RESET WITH ADJUSTABLE DELAY**

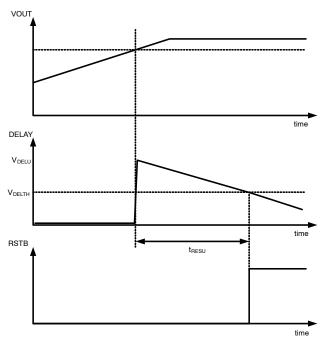

The RSTB pin is pulled low as long as the voltage on the FB pin is lower than 92% (typical) of the reference voltage (which corresponds to the output voltage being lower than 92% of its regulation level). It is high impedence when the voltage goes above 94% (typical) of the regulation level, after a delay adjusted by the capacitor on the DELAY pin.

The capacitor is held at ground until the output enters regulation:  $C_{DELAY}$  is then quickly charged to the internal rail voltage ( $V_{RESU}$ ), then discharged by the  $I_{delay}$  current until its voltage reaches the lower threshold  $V_{DELTH}$ . Only at this moment the RSTB pin voltage goes high, indicating the end of the Reset condition.

A small filtering delay (of duration  $t_{PG}$ ) ensures that the RSTB signal doesn't toggle from high to low in case of high frequency noise when the output is in regulation.

A pull-up resistor is needed on the RSTB pin, as it features an open collector output, capable of sinking 1 mA minimum at 400 mV.

The RSTB pin is also pulled low in case of UVLO ( $V_{IN}$  below the UVLO threshold), TSD (temperature shutdown) or Disable ( $V_{EN}$  below the enable threshold) events.

Figure 27. Typical Operation of the Reset with Delay Function

#### **BOOTSTRAP**

At the DRV pin an internal regulator provides a ground–referenced voltage to an external capacitor ( $C_{DRV}$ ), to allow fast recharge of the external bootstrap capacitor ( $C_{BST}$ ) used to supply power to the power switch gate driver. If the voltage at the DRV pin goes below the DRV UVLO Threshold  $V_{DRVSTP}$ , switching is inhibited and the Soft–start circuit is reset, until the DRV pin voltage goes back up above  $V_{DRVSTT}$ .

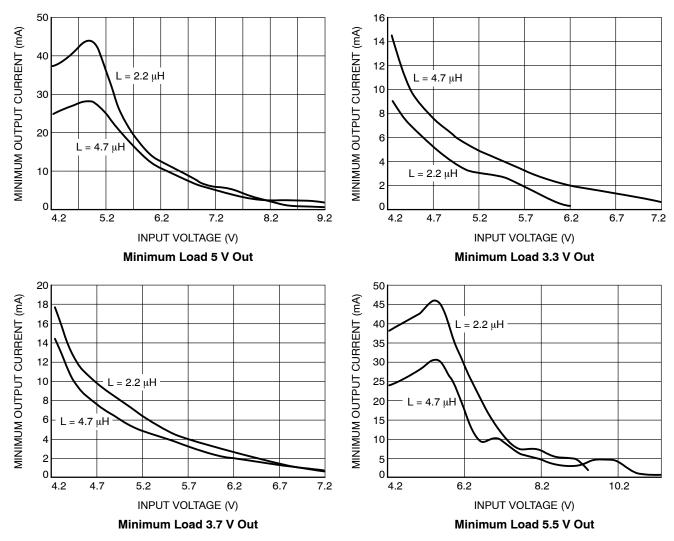

In order for the bootstrap capacitor to stay charged, the Switch node needs to be pulled down to ground regularly. In very light load condition, the NCV890103 skips switching cycles to ensure the output voltage stays regulated. When the skip cycle repetition frequency gets too low, the bootstrap voltage collapses and the regulator stops switching. Practically, this means that the NCV890103 needs a minimum load to operate correctly. Figure 28 shows the minimum current requirements for different input and output voltages.

Figure 28. Minimum Load Current with Different Input and Output Voltages

## **OUTPUT PRECHARGE DETECTION**

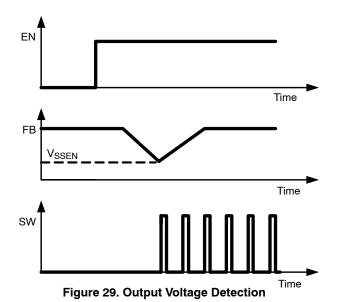

Prior to Soft–start, the FB pin is monitored to ensure the SW voltage is low enough to have charged the external bootstrap capacitor ( $C_{BST}$ ). If the FB pin is higher than  $V_{SSEN}$ , restart is delayed until the output has discharged. Figure 29 shows the IC starts to switch after the voltage on FB pin reaches VSSEN, even the EN pin is high. After the IC is switching, the FB pin follows the soft starts reference to reach the final set point.

#### THERMAL SHUTDOWN

A thermal shutdown circuit inhibits switching, resets the Soft-start circuit, and removes DRV voltage if internal temperature exceeds a safe level. Switching is automatically restored when temperature returns to a safe level.

#### MINIMUM DROPOUT VOLTAGE

When operating at low input voltages, two parameters play a major role in imposing a minimum voltage drop across the regulator: the minimum off time (that sets the maximum duty cycle), and the on state resistance.

When operating in continuous conduction mode (CCM), the output voltage is equal to the input voltage multiplied by the duty ratio. Because the NCV890103 needs a sufficient bootstrap voltage to operate, its duty cycle cannot be 100%: it needs a minimum off time ( $t_{OFFmin}$ ) to periodically re–fuel the bootstrap capacitor  $C_{BST}$ . This imposes a maximum duty ratio

$$D_{MAX} = 1 - t_{OFFmin} \cdot F_{SW(min)}$$

with the switching frequency being folded back down to  $F_{SW(min)} = 500 \text{ kHz}$  to keep regulating at the lowest input voltage possible.

The drop due to the on-state resistance is simply the voltage drop across the Switch resistance  $R_{DSON}$  at the given output current:

$$V_{SWdrop} = I_{OUT} \cdot R_{DSon}$$

Which leads to the maximum output voltage in low Vin condition:

$$V_{OUT} = D_{MAX} \cdot V_{IN(min)} - V_{SWdrop}$$

#### **EXPOSED PAD**

The exposed pad (EPAD) on the back of the package must be electrically connected to the electrical ground (GND pin) for proper, noise–free operation.

#### **DESIGN METHODOLOGY**

The NCV890103 being a fixed-frequency regulator with the switching element integrated, is optimized for one value of inductor. This value is set to 4.7 µH, and the slope compensation is adjusted for this inductor. The only components left to be designed are the input and output capacitor and the freewheeling diode. Please refer to the design spreadsheet <a href="https://www.onsemi.com">www.onsemi.com</a> NCV890103 page that helps with the calculation.

Output capacitor:

The minimum output capacitor value can be calculated based on the specification for output voltage ripple:

$$C_{OUTmin} = \frac{\Delta I_{L}}{8 \cdot \Delta V_{OUT} \cdot F_{SW}}$$

(eq. 1)

With

-  $\Delta I_L$  the inductor ripple current:

$$\Delta I_{L} = \frac{V_{OUT} \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}{L \cdot F_{SW}}$$

(eq. 2)

-  $\Delta V_{OUT}$  the desired voltage ripple.

However, the ESR of the output capacitor also contributes to the output voltage ripple, so to comply with the requirement, the ESR cannot exceed  $R_{\rm ESRmax}$ :

$$R_{ESR\,max} = \frac{V_{OUT} \cdot L \cdot F_{SW}}{V_{OUT} \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}$$

(eq. 3)

Finally, the output capacitor must be able to sustain the ac current (or RMS ripple current):

$$I_{OUTac} = \frac{\Delta I_{L}}{2\sqrt{3}}$$

(eq. 4)

Typically, with the recommended 4.7  $\mu H$  inductor, two ceramic capacitors of 10  $\mu F$  each in parallel give very good results.

Freewheeling diode:

The diode must be chosen according to its maximum current and voltage ratings, and to thermal considerations.

As far as max ratings are concerned, the maximum reverse voltage the diode sees is the maximum input voltage (with some margin in case of ringing on the Switch node), and the maximum forward current the peak current limit of the NCV890103, I<sub>LIM</sub>.

The power dissipated in the diode is P<sub>Dloss</sub>:

$$P_{Dloss} = I_{OUT} \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \cdot V_F + I_{DRMS} \cdot R_D \quad (eq. 5)$$

with:

- $I_{OUT}$  the average (dc) output current

- V<sub>F</sub> the forward voltage of the diode

- I<sub>DRMS</sub> the RMS current in the diode:

$$I_{DRMS} = \sqrt{(1 - D) \left(I_{OUT}^2 + \frac{\Delta I_L^2}{12}\right)}$$

(eq. 6)

R<sub>D</sub> the dynamic resistance of the diode (extracted from the V/I curve of the diode in its datasheet).

Then, knowing the thermal resistance of the package and the amount of heatsinking on the PCB, the temperature rise corresponding to this power dissipation can be estimated. Input capacitor:

The input capacitor must sustain the RMS input ripple current  $I_{INac}$ :

$$I_{\text{INac}} = \frac{\Delta I_{\text{L}}}{2} \sqrt{\frac{\overline{D}}{3}}$$

(eq. 7)

It can be designed in combination with an inductor to build an input filter to filter out the ripple current in the source, in order to reduce EMI conducted emissions.

For example, using a  $4.7 \,\mu\text{H}$  input capacitor, it is easy to calculate that an inductor of 200 nH will ensure that the input filter has a cut-off frequency below 200 kHz (low enough to attenuate the 2 MHz ripple).

#### **Error Amplifier and Loop Transfer Function**

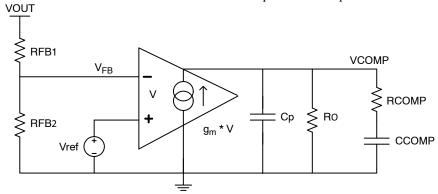

The error amplifier is a transconductance type amplifier. The output voltage of the error amplifier controls the peak inductor current at which the power switch shuts off. The Current Mode control method employed allows the use of a simple, type II compensation to optimize the dynamic response according to system requirements.

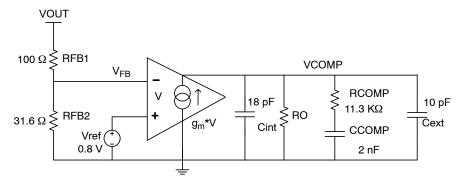

Figure 30 shows the error amplifier with the compensation components and the voltage feedback divider.

Figure 30. Feedback Compensator Network Model

The transfer function from VOUT to VCOMP is the product of the feedback voltage divider and the error amplifier.

$$Gdivider(s) = \frac{RFB2}{RFB1 + RFB2}$$

(eq. 8)

$$Gerr_{amp(s)} = gm \cdot Ro \cdot \frac{1 + \frac{s}{\omega z}}{\left(1 + \frac{s}{\omega pl}\right)\left(1 + \frac{s}{\omega ph}\right)} \quad (eq. 9)$$

$$\omega z = \frac{1}{RCOMP \cdot CCOMP}$$

(eq. 10)

$$\omega pI = \frac{1}{Ro \cdot CCOMP}$$

(eq. 11)

$$\omega ph = \frac{1}{RCOMP \cdot Cp}$$

(eq. 12)

The output resistor Ro of the error amplifier is  $1.4 \text{ M}\Omega$  and gm is 1 mA/V. The capacitor Cp is for rejecting noise at high frequency and is integrated inside the IC with a value of 18 pF.

The power stage transfer function (from Vcomp to output) is shown below:

$$Gps(s) = \frac{Rload}{Ri} \cdot \frac{1}{1 + \frac{Rload \cdot Tsw}{L} \cdot [Mc \cdot (1 - D) - 0.5]} \cdot \frac{1 + \frac{s}{\omega z}}{\left(1 + \frac{s}{\omega p}\right)} \cdot Fh(s) \text{ (eq. 13)}$$

$$\omega z = \frac{1}{\text{Resr} \cdot \text{Cout}}$$

(eq. 14)

$$\omega p = \frac{1}{\text{Rload} \cdot \text{Cout}} + \frac{\text{Mc} \cdot (1 - D) - 0.5}{\text{L} \cdot \text{Cout} \cdot \text{Fsw}} \quad (\text{eq. 15})$$

where

$$Mc = 1 + \frac{Se}{Sn}$$

(eq. 16)

$$Sn = \frac{Vin - Vout}{L} \cdot Ri$$

(eq. 17)

Ri represents the equivalent sensing resistor which has a value of  $0.31~\Omega$ , Se is the compensation slope which is 700~kV/S, Sn is the slope of the sensing resistor current during on time. Fh(s) represents the sampling effect from the current loop which has two poles at one half of the switching frequency:

Fh(s) =

$$\frac{1}{1 + \frac{s}{\omega n \cdot Qp} + \frac{s^2}{\omega n^2}}$$

(eq. 18)

$\omega n = \pi \cdot Fsw$

$$Qp = \frac{1}{\pi \cdot [Mc \cdot (1 - D) - 0.5]}$$

(eq. 19)

The total loop transfer function is the product of power stage and feedback compensation network.

$$Gloop(s) = Gdivider(s) \cdot Gerr_{amp(s)} \cdot Gps(s)$$

(eq. 20)

The bode plots of the open loop transfer function will show the gain and phase margin of the system. The compensation network is designed to make sure the system has enough phase margin and bandwidth.

### **Design of the Compensation Network**

The function of the compensation network is to provide enough phase margin at crossover frequency to stabilize the system as well as to provide high gain at low frequency to eliminate the steady state error of the output voltage. Please refer to the design spreadsheet <a href="www.onsemi.com">www.onsemi.com</a> NCV890103 page that helps with the calculation.

The design steps will be introduced through an example. Example:

Vin = 15.5 V, Vout = 3.3 V, Rload = 2.75

$$\Omega$$

, Iout = 1.2 A,

L = 4.7  $\mu$ H, Cout = 20  $\mu$ F (Resr = 7 m $\Omega$ )

The reference voltage of the feedback signal is 0.8 V and to meet the minimum load requirements, select RFB1 =  $100 \Omega$ , RFB2 =  $31.6 \Omega$ .

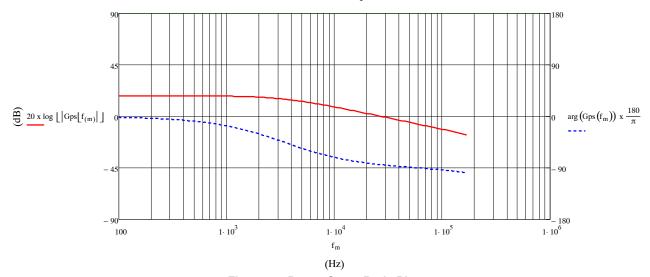

From the specification, the power stage transfer function can be plotted as below:

Figure 31. Power Stage Bode Plots

The crossover frequency is chosen to be Fc = 70 kHz, the power stage gain at this frequency is -8.6 dB (0.37) from calculation. Then the gain of the feedback compensation network must be 8.6 dB. Next is to decide the locations of one zero and one pole of the compensator. The zero is to provide phase boost at the crossover frequency and the pole is to reject the noise of high frequency. In this example, a zero is placed at 1/10 of the crossover frequency and a pole is placed at 1/5 of the switching frequency (Fsw = 2 MHz): Fz = 7000 Hz, Fp = 400000 Hz,

RCOMP, CCOMP and Cp can be calculated from the following equations:

$$\text{RCOMP} = \frac{\text{Fp} \cdot \text{gm}}{(\text{Fp} - \text{Fz}) \cdot |\text{Gps(Fc)}|} \cdot \frac{\text{Vout}}{\text{Vref}} \cdot \frac{\sqrt{1 + \left(\frac{Fc}{Fp}\right)^2}}{\sqrt{1 + \left(\frac{Fz}{Fc}\right)^2}}$$

$$CCOMP = \frac{1}{2\pi \cdot Fz \cdot RCOMP}$$

(eq. 22)

$$Cp = \frac{1}{2\pi \cdot Fp \cdot RCOMP}$$

(eq. 23)

Note: there is an 18 pF capacitor at the output of the OTA integrated in the IC, and if a larger capacitor needs to be used, subtract this value from the calculated Cp. Figure 32 shows Cp is split into two capacitors. Cint is the 18 pF in the IC. Cext is the extra capacitor added outside the IC.

From the calculation:

RCOMP =  $11.3 \text{ K}\Omega$ , CCOMP = 2 nF, Cp = 28 pF

So the feedback compensation network is as below:

Figure 32. Example of the Feedback Compensation Network

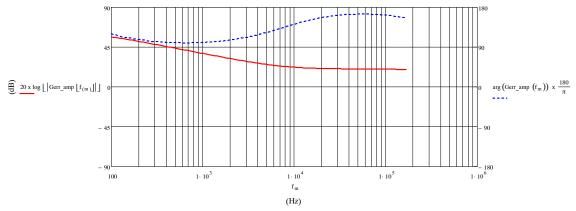

Figure 33 shows the bode plot of the OTA compensator

Figure 33. Bode Plot of the OTA Compensator

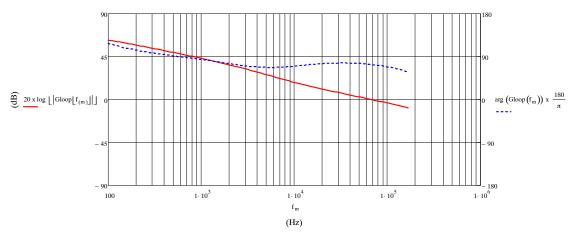

The total loop bode plot is as below:

Figure 34. Bode Plot of the Total Loop

The crossover frequency is at 70 KHz and phase margin is 75 degrees.

#### **PCB LAYOUT RECOMMENDATION**

As with any switching power supplies, there are some guidelines to follow to optimize the layout of the printed circuit board for the NCV890103. However, because of the high switching frequency extra care has to be taken.

- Minimize the area of the power current loops:

- Input capacitor → NCV890103 switch → Inductor

→ output capacitor → return through Ground

- Freewheeling diode → inductor → Output capacitor

→ return through ground

- Minimize the length of high impedance signals, and route them far away from the power loops:

- Feedback trace

- Comp trace

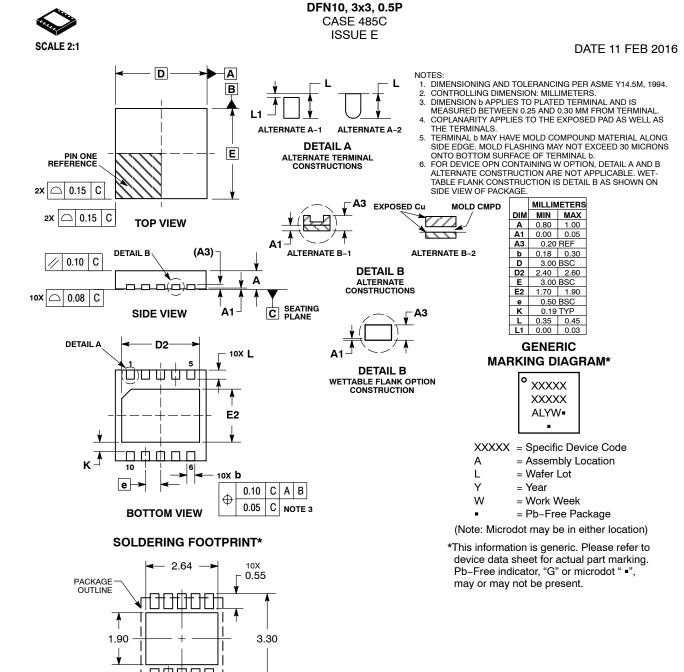

#### **ORDERING INFORMATION**

| Device         | Package                                 | Shipping <sup>†</sup> |  |

|----------------|-----------------------------------------|-----------------------|--|

| NCV890103MWTXG | DFN10 with wettable flanks<br>(Pb-Free) | 3000 / Tape & Reel    |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

| DESCRIPTION:     | DFN10, 3X3 MM, 0.5 MM P | ITCH                                                                                                                                                                                | PAGE 1 OF 1 |  |

|------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DOCUMENT NUMBER: | 98AON03161D             | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|                  |                         |                                                                                                                                                                                     |             |  |

10X 0.30

**DIMENSIONS: MILLIMETERS**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

0.50—

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative