# 3.3 V 12.288 MHz Audio Oversampling Clock Generator for USB Applications

# **NB3N3010B**

#### **Description**

The NB3N3010B is a precision, low noise clock multiplier that generates an output frequency of 12.288 MHz. This is accomplished by using Frequency–Locked–Loop (FLL) techniques where a 4 kHz reference input is multiplied by 3072, or an 8 kHz input by 1536. The frequency multiplier is selected by the S0 pin.

The two LVCMOS output drivers are disabled to a logic Low with the ENABLEn pin set HIGH. The NB3N3010B operates from a single  $+3.3~\rm V$  supply, and is available in the SOIC-8 pin package. The operating temperature range is from  $0^{\circ}\rm C$  to  $+85^{\circ}\rm C$ .

The NB3N3010B device provides the optimum combination of low cost, flexibility, and high performance. This makes it ideal for applications such as oversampling A-to-D and D-to-A converters from a low reference frequency, such as a USB start-of-frame (SOF) pulse.

#### **Features**

- Accepts 8 kHz or 4 kHz Reference Input Derived from USB Start-of-Frame

- Generates 12.288 MHz Frequency–Locked to the Reference

- Fully Integrated Frequency-Lock-Loop with Internal Loop Filter

- Low Skew Dual LVCMOS Outputs

- Very Low Phase Noise Preserves Codec Noise Floor

- Internal Voltage Regulator

- Supply Voltage Required: +3.3 V ±5%

- Temperature Range: 0°C to +85°C

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### ON Semiconductor®

#### www.onsemi.com

SOIC-8 D SUFFIX CASE 751

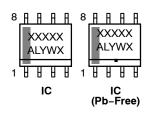

#### **MARKING DIAGRAM\***

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

\*For additional marking information, refer to Application Note <u>AND8002/D</u>.

#### **ORDERING INFORMATION**

| Device        | Package             | Shipping <sup>†</sup> |

|---------------|---------------------|-----------------------|

| NB3N3010BDR2G | SOIC-8<br>(Pb-Free) | 2500 / Tape<br>& Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

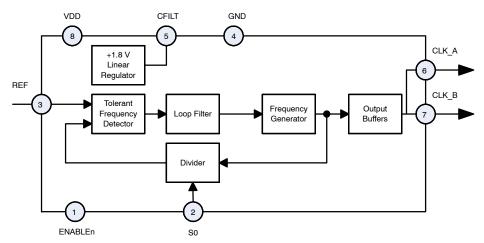

Figure 1. NB3N3010B Simplified Diagram

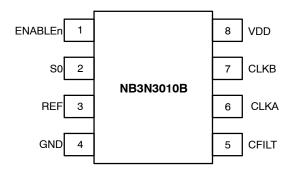

Figure 2. Pinout SOIC-8 (Top View)

**Table 1. PIN DESCRIPTION**

| Pin | Symbol  | I/O                    | Description                                                                                                                                       |

|-----|---------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ENABLEn | LVTTL/<br>LVCMOS Input | Low active Output Enable; Defaults HIGH when left open; Internal pull-up resistor to $V_{\text{DD}}.$                                             |

| 2   | S0      | LVTTL/<br>LVCMOS Input | Frequency Select Input. See input frequency select Table 2 for details. Defaults HIGH when left open. Internal pull–up resistor to $V_{\rm DD}$ . |

| 3   | REF     | Input                  | Reference Clock input                                                                                                                             |

| 4   | GND     | Power Supply           | Negative Supply Voltage; Ground 0 V. This pin provides GND return path to the VDD supply.                                                         |

| 5   | CFILT   | Analog                 | Connection for external filter capacitor for internal +1.8 V regulator; see Figure 4.                                                             |

| 6   | CLKA    | LVCMOS<br>Output       | Clock output, copy A (12.288 MHz)                                                                                                                 |

| 7   | CLKB    | LVCMOS<br>Output       | Clock output, copy B (12.288 MHz)                                                                                                                 |

| 8   | VDD     | Power Supply           | Positive Supply Voltage, +3.3 V ±5%                                                                                                               |

**Table 2. ATTRIBUTES**

| Characteristic                                                                                  | Value                |

|-------------------------------------------------------------------------------------------------|----------------------|

| ESD Protection Human Body Model Machine Model                                                   | > 4 kV<br>400 V      |

| R <sub>PU</sub> – ENABLEn Input Pull–up Resistor<br>R <sub>PU</sub> – SO Input Pull–up Resistor | 48 kΩ<br>48 kΩ       |

| Moisture Sensitivity (Note 1) Pb-Free                                                           | Level 1              |

| Flammability Rating Oxygen Index: 28 to 34                                                      | UL 94 V-0 @ 0.125 in |

| Transistor Count                                                                                | 12039                |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test                                          | •                    |

<sup>1.</sup> For additional information, see Application Note AND8003/D.

**Table 3. ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                | Condition 1        | Condition 2      | Rating                            | Unit         |

|------------------|------------------------------------------|--------------------|------------------|-----------------------------------|--------------|

| V <sub>DD</sub>  | Positive Power Supply                    | GND = 0 V          |                  | 4.6                               | V            |

| VI               | Input Voltage (VIN)                      | GND = 0 V          |                  | -0.3 V to V <sub>DD</sub> + 0.3 V | V            |

| T <sub>A</sub>   | Operating Temperature Range              |                    |                  | 0 to +85                          | °C           |

| T <sub>stg</sub> | Storage Temperature Range                |                    |                  | -40 to +150                       | °C           |

| θJA              | Thermal Resistance (Junction-to-Ambient) | 0 lfpm<br>500 lfpm | SOIC-8<br>SOIC-8 | 190<br>130                        | °C/W<br>°C/W |

| θJC              | Thermal Resistance (Junction-to-Case)    | (Note 2)           | SOIC-8           | 41 to 44                          | °C/W         |

| T <sub>sol</sub> | Wave Solder Pb-Free                      |                    |                  | 265                               | °C           |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

2. JEDEC standard multilayer board – 2S2P (2 signal, 2 power).

Table 4. DC CHARACTERISTICS V\_DD = 3.3 V  $\pm 5\%$ , GND = 0 V, T\_A = 0°C to +85°C, Note 3.

| Symbol             | Characteristic                                                         | Min       | Тур | Max                   | Unit |

|--------------------|------------------------------------------------------------------------|-----------|-----|-----------------------|------|

| $V_{DD}$           | Power Supply Voltage                                                   | 3.13      | 3.3 | 3.47                  | V    |

| I <sub>DDOEL</sub> | Power Supply Current (operating, i.e. ENABLEn is LOW) Outputs Unloaded |           | 21  | 35                    | mA   |

| I <sub>DDOEH</sub> | Power Supply Current (standby, i.e. ENABLEn is HIGH)                   |           | 415 | 600                   | uA   |

| V <sub>IH</sub>    | Input HIGH Voltage (REF, ENABLEn, S0)                                  | 2.0       |     | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IL</sub>    | Input LOW Voltage (REF, ENABLEn, S0)                                   | GND - 0.3 |     | 0.8                   | V    |

| V <sub>OH</sub>    | Output HIGH Voltage (CLKA, CLKB) , I <sub>OH</sub> = -12 mA            | 2.4       |     |                       | V    |

| V <sub>OL</sub>    | Output LOW Voltage (CLKA, CLKB), I <sub>OL</sub> = 12 mA               |           |     | 0.4                   | V    |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

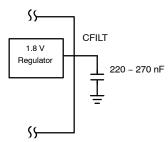

<sup>3.</sup> C<sub>FILT</sub> capacitor must be installed; see Figure 4.

Table 5. AC CHARACTERISTICS  $V_{DD}$  = 3.3 V  $\pm 5\%,\,GND$  = 0 V,  $T_{A}$  = 0°C to +85°C (Note 4)

| Symbol                    | Characteristic                                                                                            |                     | Min                  | Тур              | Max                  | Unit |

|---------------------------|-----------------------------------------------------------------------------------------------------------|---------------------|----------------------|------------------|----------------------|------|

| f <sub>out</sub>          | Output Clock Frequency: CLKA & CLKB<br>f <sub>OUT</sub> = 8 kHz x 1536<br>f <sub>OUT</sub> = 4 kHz x 3072 | S0 = 1<br>S0 = 0    | 12.25728<br>12.25728 | 12.288<br>12.288 | 12.31872<br>12.31872 | MHz  |

| f <sub>REF</sub>          | Reference Input Frequency                                                                                 | S0 = 1<br>S0 = 0    | 7.98<br>3.99         | 8<br>4           | 8.02<br>4.01         | kHz  |

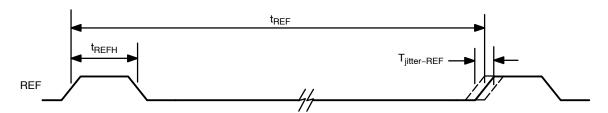

| t <sub>jit(per)-ref</sub> | Reference Input Period Jitter (pk-pk)                                                                     |                     |                      |                  | 250                  | ns   |

| t <sub>REFH</sub>         | Reference Input Pulse Width (high)                                                                        | S0 = 1<br>S0 = 0    | 33<br>33             |                  | 68000<br>136000      | ns   |

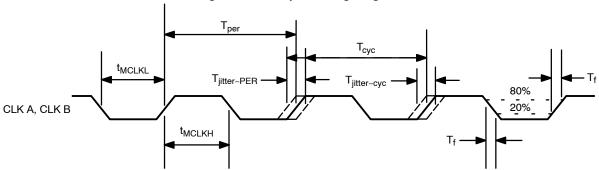

| t <sub>CLKH</sub>         | CLKA, CLKB output width, high                                                                             |                     | 13                   |                  |                      | ns   |

| t <sub>CLKL</sub>         | CLKA, CLKB output width, low                                                                              |                     | 13                   |                  |                      | ns   |

| t <sub>r</sub>            | CLKA, CLKB rise time 10% – 90%                                                                            |                     |                      |                  | 4                    | ns   |

| t <sub>f</sub>            | CLKA, CLKB fall time 90% – 10%                                                                            |                     |                      |                  | 4                    | ns   |

| t <sub>jit(per)</sub>     | CLKA, CLKB period jitter (over 10k cycles)                                                                | peak-to-peak<br>RMS |                      |                  | 250<br>20            | ps   |

| t <sub>jit(cc)</sub>      | CLK_A, CLKB cycle-to-cycle jitter (1k cycles)                                                             | peak-to-peak<br>RMS |                      |                  | 300<br>35            | ps   |

| t <sub>sk(LH)</sub>       | CLKA to CLKB output skew (low-to-high transitions)                                                        |                     |                      |                  | 700                  | ps   |

| t <sub>sk(HL)</sub>       | CLKA to CLKB output skew (high-to-low transitions)                                                        |                     |                      |                  | 700                  | ps   |

|                           | Power Valid to ENABLEn                                                                                    |                     |                      |                  | 10                   | ms   |

|                           | ENABLEn to CLKA/CLKB                                                                                      |                     |                      | 50               | 100                  | ms   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

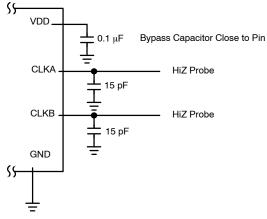

<sup>4.</sup> Outputs loaded with 15 pF max to ground. C<sub>FILT</sub> capacitor must be installed; see Figure 4.

5. Maximum time required after power is applied to the MCLK FLL until it is ready to accept ENABLEn active.

#### APPLICATION INFORMATION

Figure 1 shows the simplified block diagram of the NB3N3010B device.

The primary function of the NB3N3010B is to accept a selectable 4 kHz or 8 kHz input reference clock, REF, and then multiply it to 12.288 MHz output frequency.

#### Frequency Select - SO

Either of two expected input REF frequencies, 4 kHz or 8 kHz, will be multiplied by the FLL to achieve 12.288 MHz at the low-skew CLKA and CLKB outputs by selecting the S0 pin; see Table 6.

The pulse high time  $(T_{\rm HI})$  of the input reference signal may vary widely depending on the application. See AC specifications for details.

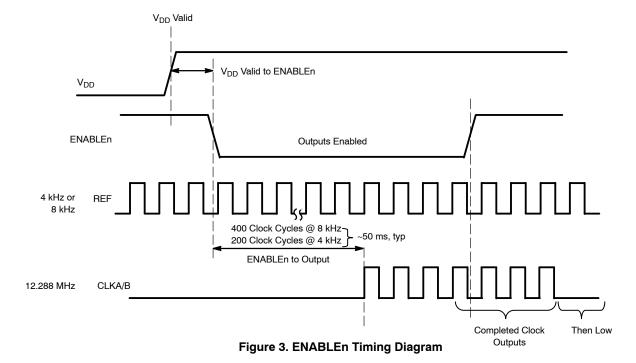

#### **Output Enable - ENABLEn**

A Low active output enable input pin, ENABLEn, is provided. When the ENABLEn input is High inactive, both clock outputs are driven to a logic Low.

The NB3N3010B implements a delay, specified as ENABLEn to Output Delay in the AC Specifications, from the assertion of ENABLEn to the first rising edges on the clock outputs. This delay insures that CLKA and CLKB output pulses are within specification before the output drivers are enabled. When ENABLEn transitions from Low to High (de-asserts), the current cycle of the clock outputs completes normally then the outputs will be held Low. The ENABLEn signal is asynchronous to either the REF input or CLK\_x outputs.

Table 6. INPUT FREQUENCY SELECT AND OUTPUT ENABLE FUNCTIONS

| ENABLEn* | S0* | f <sub>REF</sub> | FLL Multiplier | CLKA & CLKB Frequency |

|----------|-----|------------------|----------------|-----------------------|

| 0        | L   | 4 kHz            | 3072           | 12.288 MHz            |

| 0        | Н   | 8 kHz            | 1536           | 12.288 MHz            |

| 1        | х   | Х                | х              | Disabled Low          |

<sup>\*</sup>Defaults High when left open.

## **Typical Power On Sequence**

- 1. Power On

- 2. Reference Clock present; must be switching before ENABLEn goes High.

- 3. Output Enable, ENABLEn, High-to-Low

#### **CFILT for 1.8 V Regulator**

Figure 4. CFILT Capacitor

A low noise 1.8 V LDO/Regulator is integrated to provide a clean supply for the CLKA/CLKB output buffers. The LDO requires a decoupling capacitor in the range of 220 nF to 270 nF for compensation and high frequency PSR, and should be located near the device. The purpose of this design technique is to isolate the high switching noise of the digital outputs from the relatively sensitive internal analog phase–locked loop.

Figure 5. REF Input Timing Diagram

Figure 6. Clock Output Timing Diagram

Figure 7. Test Circuit

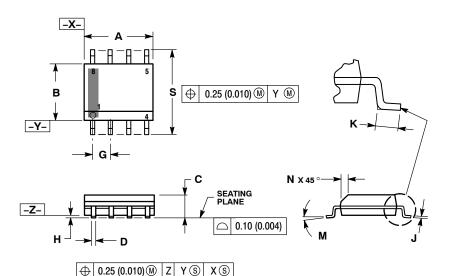

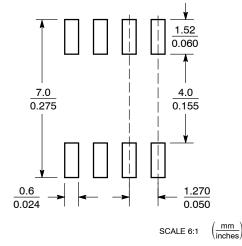

SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   | 4.80        | 5.00  | 0.189     | 0.197 |

| В   | 3.80        | 4.00  | 0.150     | 0.157 |

| C   | 1.35        | 1.75  | 0.053     | 0.069 |

| D   | 0.33        | 0.51  | 0.013     | 0.020 |

| G   | 1.27        | 7 BSC | 0.050 BSC |       |

| Н   | 0.10        | 0.25  | 0.004     | 0.010 |

| 7   | 0.19        | 0.25  | 0.007     | 0.010 |

| K   | 0.40        | 1.27  | 0.016     | 0.050 |

| M   | 0 °         | 8 °   | 0 °       | 8 °   |

| N   | 0.25        | 0.50  | 0.010     | 0.020 |

| S   | 5.80        | 6.20  | 0.228     | 0.244 |

#### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

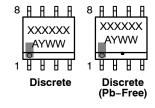

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot = Year = Work Week

= Pb-Free Package

XXXXXX = Specific Device Code = Assembly Location Α

= Year ww = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Report Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                             | PAGE 1 OF 2 |  |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

### SOIC-8 NB CASE 751-07 ISSUE AK

# DATE 16 FEB 2011

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                 | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1 8. EMITTER, #1               | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            |                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                               | STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                                    | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #2 7. EMITTER, #1 8. COLLECTOR, #1                              |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE              | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                 |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | 8. DHAIN 1  STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON   | STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                   |

| 6. VEE 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                   | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | 0 COLLECTOR/ANODE                                                                                                                                                       |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                    | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V_MON 6. VBULK 7. VBULK 8. VIN                                                                        |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                           |                                                                                                                                                     |                                                                                                                                                                         |

|                                                                                                                                                                    |                                                                                                                                                           |                                                                                                                                                     |                                                                                                                                                                         |

| DOCUMENT NUMBER: | R: 98ASB42564B Electronic versions are uncontrolled except when stamped "CONTROLLED COP" |  |             |

|------------------|------------------------------------------------------------------------------------------|--|-------------|

| DESCRIPTION:     | SOIC-8 NB                                                                                |  | PAGE 2 OF 2 |

ON Semiconductor and IN are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT

North American Technical Support:

Voice Mail: 1 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: a Phone: 00421 33 790 2910

Phone: 011 421 33 790 2910 For additional information, please contact your local Sales Representative