# 1/5-Inch Color CMOS NTSC/PAL Digital Image SOC with Overlay Processor

ASX350AT Datasheet, Rev. 5

For the latest datasheet, please visit www.onsemi.com

#### **Features**

- Low-power CMOS image sensor with integrated image flow processor (IFP) and video encoder

- 1/5-inch optical format, VGA resolution (640H x 480V)

- Up to 2x upscaling zoom and pan control

- ±40 additional columns and ±36 additional rows to compensate for lens alignment tolerances

- Option to use single 2.8 V power supply with off-chip bypass transistor

- Automatic 50Hz/60Hz flicker detection

- Independent control of colorburst parameters in the NTSC/PAL encoder

- Horizontal field of view adjustment between 700 and 720 pixels on the analog output

- Overlay generator for dynamic bitmap overlay

- Integrated video encoder for NTSC/PAL with overlay capability and 10-bit I-DAC

- Integrated microcontroller for flexibility

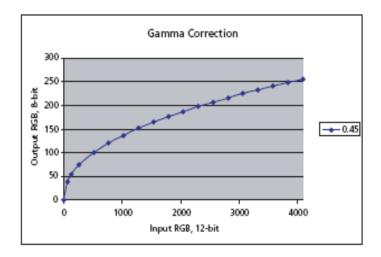

- On-chip image flow processor performs sophisticated processing, such as color recovery and correction, sharpening, gamma, lens shading correction, on-the-fly defect correction, auto white balancing, and auto exposure

- Auto black-level calibration

- 10-bit, on-chip analog-to-digital converter (ADC)

- Internal master clock generated by on-chip phaselocked loop (PLL)

- Two-wire serial programming interface

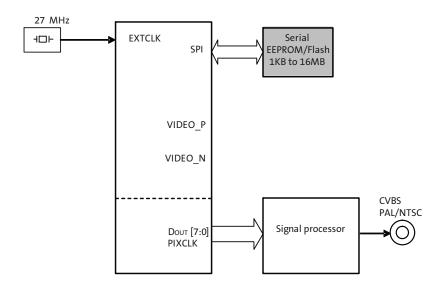

- Interface to low-cost EEPROM and Flash through SPI bus

- High-level host command interface

- Stand-alone operation support

- Comprehensive tool support for overlay generation and lens correction setup

- Development system with DevWare

# **Applications**

- Automotive rearview camera and side mirror

- · Blind spot and surround view

Table 1: Key Parameters

| Parameter                   | Typical Value                                                                                                                                                                                             |  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pixel size<br>and type      | 3.75 µm x 3.75 µm active pinned-<br>photodiode with high-sensitivity mode<br>for low-light conditions                                                                                                     |  |  |  |

| Sensor clear pixels         | 728H x 560V (includes VGA active pixels, demosaic and lens alignment pixels)                                                                                                                              |  |  |  |

| NTSC output                 | 720H x 487V                                                                                                                                                                                               |  |  |  |

| PAL output                  | 720H x 576V                                                                                                                                                                                               |  |  |  |

| Optical area (clear pixels) | 2.730 mm x 2.100 mm                                                                                                                                                                                       |  |  |  |

| Optical format              | 1/5-inch                                                                                                                                                                                                  |  |  |  |

| Frame rate                  | 50/60 fields/sec                                                                                                                                                                                          |  |  |  |

| Sensor scan mode            | Progressive scan                                                                                                                                                                                          |  |  |  |

| Color filter array          | RGB standard Bayer                                                                                                                                                                                        |  |  |  |

| Chief ray angle (CRA)       | 0°                                                                                                                                                                                                        |  |  |  |

| Shutter type                | Electronic rolling shutter (ERS)                                                                                                                                                                          |  |  |  |

| Automatic<br>Functions      | Exposure, white balance, black level offset correction, flicker detection and avoidance, color saturation control, on the-fly defect correction, aperture correction                                      |  |  |  |

| Programmable<br>Controls    | Exposure, white balance, horizontal and vertical blanking, color, sharpness, gamma correction, lens shading correction, horizontal and vertical image flip, zoom, windowing, sampling rates, GPIO control |  |  |  |

Key parameters are continued on next page.

See "New Feature" on page 3.

See "Ordering Information" on page 3

# Table 2: Key Parameters (continued)

| Parameter                        |                         | Typical Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|----------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Overlay Suppo                    | rt                      | Utilizes SPI interface to load overlay data from external flash/EEPROM memory with the following features:  •Available in Analog output and BT656 Digital output  •Overlay Size 360 x 480 pixel rendered into 720 x 480 (NTSC) or 720 x 576 (PAL)  •Up to two (2) overlays may be blended simultaneously  •Selectable readout: Rotating order user-selected  •Dynamic scenes by loading pre-rendered frames from external memory  •Palette of 32 colors out of 64,000  •8 colors per bitmap  •Blend factor dynamically-programmable for smooth transitions  •Fast update rate of up to 30 fps  •Every bitmap object has independent x/y position  •Statistic Engine to calibrate optical alignment  •Number Generator |  |  |  |  |

| Windowing                        |                         | Programmable to any size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Analog gain rai                  | nge                     | 0.5–16x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| ADC                              |                         | 10-bit, on-chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Output interface                 |                         | Analog composite video out, single-ended or differential; 8-, 10-bit parallel digital output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Output data formats <sup>1</sup> |                         | Digital: Raw Bayer 8-,10-bit, CCIR656, 565RGB, 555RGB, 444RGB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                                  |                         | Parallel: 27 MB/s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Data rate                        |                         | NTSC: 60 fields/sec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Data late                        |                         | PAL: 50 fields/sec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Control interface                |                         | Two-wire I/F for register interface plus high-level command exchange. SPI port to interface to external memory to load overlay data, register settings, or firmware extensions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Input clock for                  | PLL                     | 27 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SPI Clock Frequ                  | encies                  | 1.6875 – 18 MHz, programmable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                                  |                         | Analog: 2.8V ±5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Supply voltage                   |                         | Core: 1.8V ±5% (2.8V±5% power supply with off-chip bypass transistor generates a 1.70 - 1.95 V core voltage supply, which is acceptable for performance.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                                  |                         | IO: 2.8/1.8V ±5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Power                            | Analog output only      | Full resolution at 60 fps: 310 mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| consumption                      | Digital output only     | Full resolution at 60 fps: 215 mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

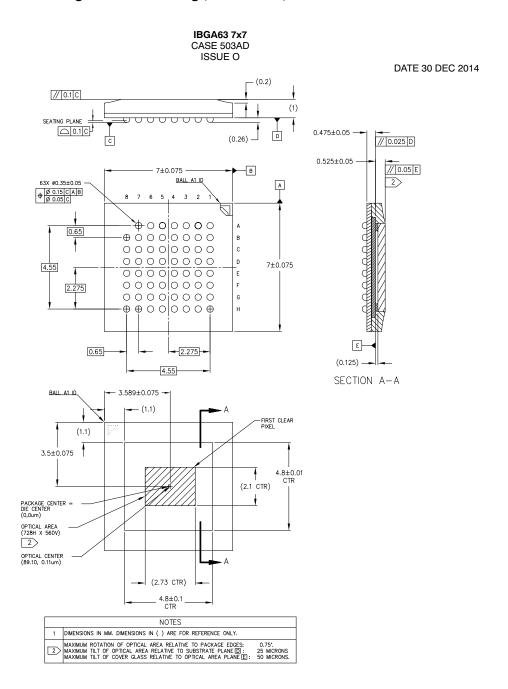

| Package                          |                         | 63-BGA, 7 mm x 7 mm, 0.65 mm pin pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                                  |                         | Operating: -40°C to 105°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Ambient temp                     | erature                 | Functional: -40°C to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                  |                         | Storage: -50°C to +150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Dark Current                     |                         | < 144e/s at 60°C junction temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Fixed pattern                    | Column                  | < 0.18% at 50% full-well                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| noise                            | Row                     | <0.1% at 50% full-well                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

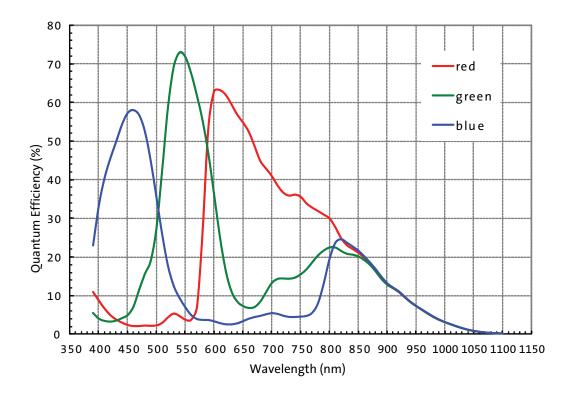

| Responsivity at                  | : 550 nm                | 6.67 V/lux-s (HCG), 2.44 V/lux-s (LCG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Maximum sign                     | al to noise ratio (SNR) | 42.6 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Pixel dynamic i                  | range                   | 82.2 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

ASX350AT/D Rev. 5, 7/16 EN 2 ©Semiconductor Components Industries, LLC, 2016.

# **New Feature**

• Up to 2x upscaling zoom and pan/tilt control (see "Zoom Support" on page 25 for details on restrictions.)

# **Ordering Information**

Table 3: Available Part Numbers

| Part Number             | Product Description           | Orderable Product Attribute Description |

|-------------------------|-------------------------------|-----------------------------------------|

| ASX350AT3C00XPEA0-DP    | Color, Odeg CRA, iBGA Package | Drypack, Protective Film                |

| ASX350AT3C00XPEA0-DR    | Color, Odeg CRA, iBGA Package | Drypack                                 |

| ASX350AT3C00XPEA0-TP    | Color, Odeg CRA, iBGA Package | Tape and Reel                           |

| ASX350AT3C00XPEAD3-GEVK | Color, Demo Kit               |                                         |

| ASX350AT3C00XPEAH3-GEVB | Color, Head Board             |                                         |

See the ON Semiconductor Device Nomenclature document (TND310/D) for a full description of the naming convention used for image sensors. For reference documentation, including information on evaluation kits, please visit our web site at www.onsemi.com.

# **Table of Contents**

| Features                             |    |

|--------------------------------------|----|

| Applications                         |    |

| New Feature                          |    |

| Ordering Information                 |    |

| General Description                  |    |

| Architecture                         |    |

| Pin Descriptions and Assignments     |    |

| SOC Description                      |    |

| Sensor Pixel Array                   |    |

| System Configuration and Usage Modes | 24 |

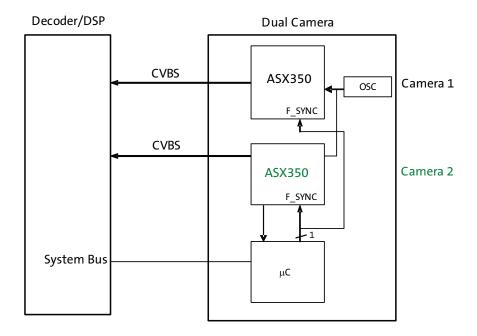

| Multicamera Support                  | 24 |

| External Signal Processing           |    |

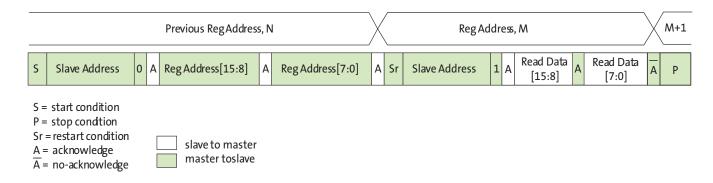

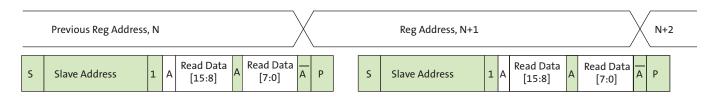

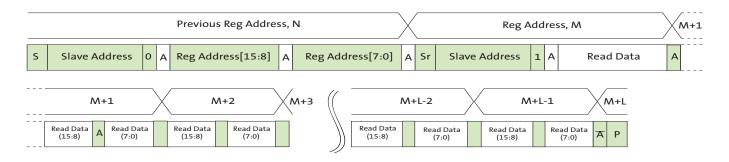

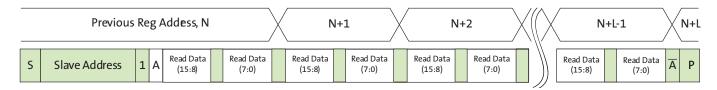

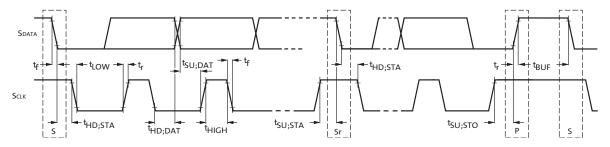

| Slave Two-Wire Serial Interface      |    |

| Overlay Capability                   |    |

| Serial Memory Partition              |    |

| Overlay Adjustment                   |    |

| Overlay Character Generator          |    |

| Modes and Timing                     |    |

| Electrical Specifications            | 57 |

| Spectral Characteristics             |    |

ASX350AT: 1/5-Inch Color CMOS NTSC/PAL Digital Image Sensor General Description

# **General Description**

The ON Semiconductor ASX350AT is a VGA-format, single-chip CMOS active-pixel digital image sensor for automotive applications. It captures high-quality color images at VGA resolution and outputs NTSC or PAL interlaced composite video.

The VGA CMOS image sensor features ON Semiconductor's breakthrough low-noise imaging technology that achieves superior image quality (based on signal-to-noise ratio and low-light sensitivity) while maintaining the inherent size, cost, low power, and integration advantages of ON Semiconductor's advanced active pixel CMOS process technology.

The ASX350AT is a complete camera-on-a-chip. It incorporates sophisticated camera functions on-chip and is programmable through a simple two-wire serial interface or by an attached SPI EEPROM or Flash memory that contains setup information that may be loaded automatically at startup.

The ASX350AT performs sophisticated processing functions including color recovery, color correction, sharpening, programmable gamma correction, auto black reference clamping, auto exposure, 50Hz/60Hz flicker detection and avoidance, lens shading correction, auto white balance (AWB), and on-the-fly defect identification and correction.

The ASX350AT outputs interlaced-scan images at 60 or 50 fields per second, supporting both NTSC and PAL video formats. The image data can be output on one or two output ports:

- Composite analog video (single-ended and differential output support)

- Parallel 8-, 10-bit digital

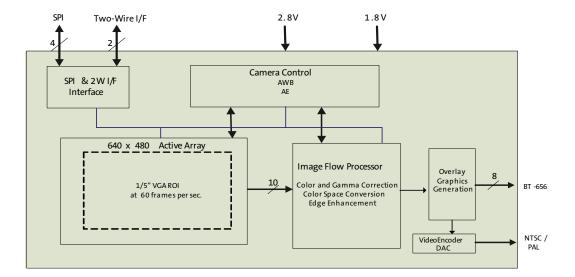

#### **Architecture**

#### **Internal Block Diagram**

Figure 1: Internal Block Diagram

ASX350AT: 1/5-Inch Color CMOS NTSC/PAL Digital Image Sensor Architecture

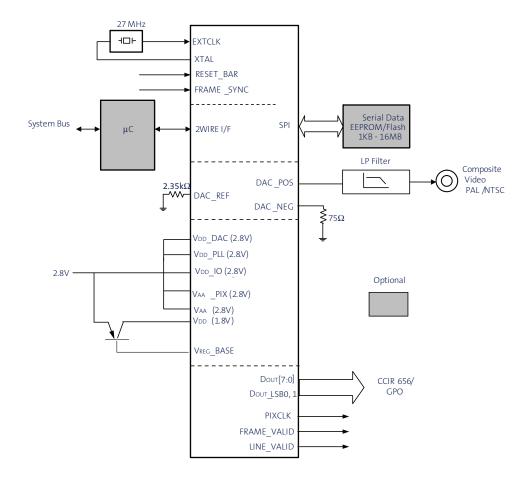

# **System Block Diagram**

The system block diagram will depend on the application. The system block diagram in Figure 2 shows all components; optional peripheral components are highlighted. Control information will be received by a microcontroller through the automotive bus to communicate with the ASX350AT through its two-wire serial bus. Optional components will vary by application.

Figure 2: System Block Diagram

ASX350AT: 1/5-Inch Color CMOS NTSC/PAL Digital Image Sensor Architecture

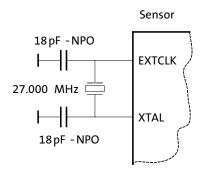

## **Crystal Usage**

As an alternative to using an external oscillator, a fundamental 27 MHz crystal may be connected between EXTCLK and XTAL. Two small loading capacitors of 10–22 pF of NPO dielectric should be added as shown in Figure 3.

ON Semiconductor does not recommend using the crystal option for applications above 85°C. A crystal oscillator with temperature compensation is recommended.

Figure 3: Using a Crystal Instead of an External Oscillator

Note: Value of load cap is Xtal-dependent. Xtal with small load cap is recommended.

ASX350AT: 1/5-Inch Color CMOS NTSC/PAL Digital Image Sensor Pin Descriptions and Assignments

# **Pin Descriptions and Assignments**

Table 4: Pin Descriptions

| Pin Number            | Pin Name           | Туре         | Description                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-----------------------|--------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                       |                    | 1            | Clock and Reset                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| НЗ                    | EXTCLK             | Input        | Master input clock (27MHz): This can either be a square-wave generated from an oscillator (in which case the XTAL input must be left unconnected) or connected directly to a crystal.                                                                                                                                                                |  |  |  |  |

| G2                    | XTAL               | Output       | If EXTCLK is connected to one pin of a crystal, this signal is connected to the other pin; otherwise this signal must be left unconnected.                                                                                                                                                                                                           |  |  |  |  |

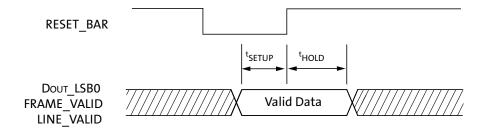

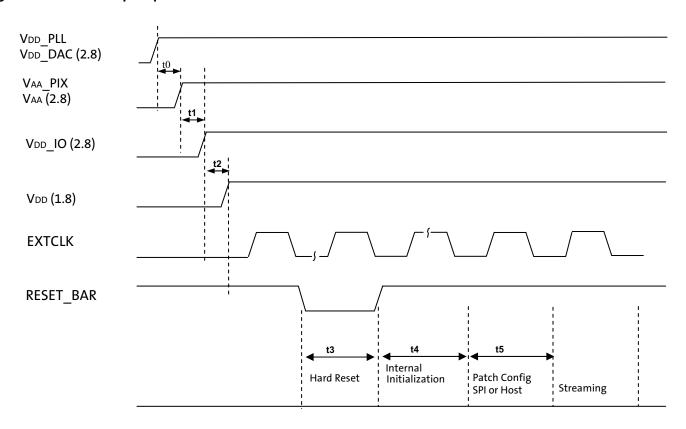

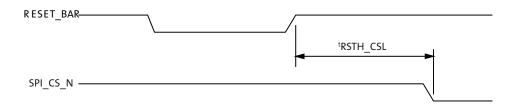

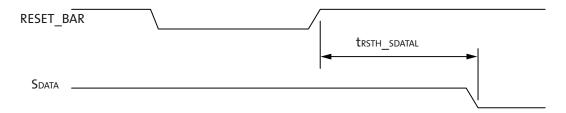

| C8                    | RESET_BAR          | Input        | Asynchronous active-low reset: When asserted, the device will return all interfaces to their reset state. When released, the device will initiate the boot sequence. This signal has an internal pull-up resistor.                                                                                                                                   |  |  |  |  |

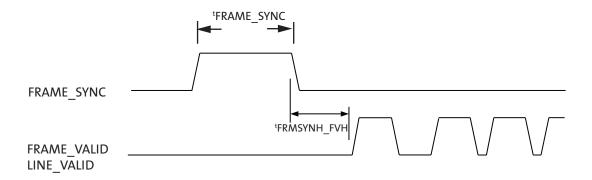

| A7                    | FRAME_SYNC         | Input        | This input can be used to set the output timing of the ASX350AT to a fixed point in the frame.  The input buffer associated with this input is permanently enabled. This signal must be connected to GND if not used.                                                                                                                                |  |  |  |  |

|                       |                    |              | Register Interface                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

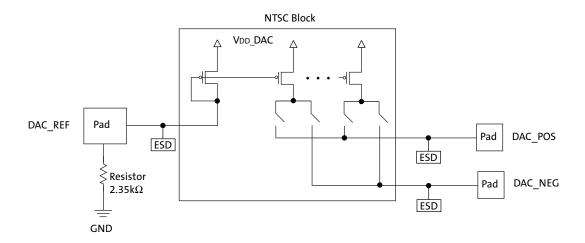

| C6                    | Sclk               | Input        | These two signals implement serial communications protocol for access to the                                                                                                                                                                                                                                                                         |  |  |  |  |

| C7                    | Sdata              | Input/Output | internal registers and variables.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| B8                    | SADDR              | Input        | This signal controls the device ID that will respond to serial communication commands.  Two-wire serial interface device ID selection: 0: 0x90 1: 0xBA                                                                                                                                                                                               |  |  |  |  |

|                       |                    |              | SPI Interface                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

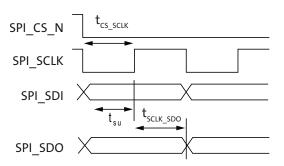

| G3                    | SPI_SCLK           | Output       | Clock output for interfacing to an external SPI memory such as Flash/EEPROM.  Tri-state when RESET_BAR is asserted.                                                                                                                                                                                                                                  |  |  |  |  |

| F2                    | SPI_SDI            | Input        | Data in from SPI device. This signal has an internal pull-up resistor.                                                                                                                                                                                                                                                                               |  |  |  |  |

| G4                    | SPI_SDO            | Output       | Data out to SPI device. Tri-state when RESET_BAR is asserted.                                                                                                                                                                                                                                                                                        |  |  |  |  |

| F4                    | SPI_CS_N           | Output       | Chip selects to SPI device. Tri-state when RESET_BAR is asserted.                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                       |                    |              | (Parallel) Pixel Data Output                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| D3                    | FRAME_VALID        | Input/Output | Pixel data from the ASX350AT can be routed out on this interface and processed                                                                                                                                                                                                                                                                       |  |  |  |  |

| C3                    | LINE_VALID         | Input/Output | externally.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| D5                    | PIXCLK             | Output       | To save power, these signals are driven to a constant logic level unless the parallel pixel data output or alternate (GPIO) function is enabled for these pins.                                                                                                                                                                                      |  |  |  |  |

| B6, C5, B5,           | Dоuт[ <b>7</b> :0] | Output       | This interface is disabled by default.                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| D4, A5, C4,<br>A4, E3 |                    |              | The slew rate of these outputs is programmable.                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                       |                    |              | These signals can also be used as general purpose input/outputs.                                                                                                                                                                                                                                                                                     |  |  |  |  |

| D2                    | DOUT_LSB1          | Input/Output | When the sensor core is running in bypass mode, it will generate 10 bits of output                                                                                                                                                                                                                                                                   |  |  |  |  |

| E2                    | Dout_LSB0          | Input/Output | data per pixel. These two pins make the two LSB of pixel data available externally. Leave Dout_LSB1 unconnected if not used. To save power, these signals are driven to a constant logic level unless the sensor core is running in bypass mode or the alternate function is enabled for these pins. The slew rate of these outputs is programmable. |  |  |  |  |

ASX350AT: 1/5-Inch Color CMOS NTSC/PAL Digital Image Sensor Pin Descriptions and Assignments

Table 4: Pin Descriptions (continued)

| Pin Number                                          | Pin Name  | Туре                                                                                                                                                                                                                                                                                          | Description                                                                                                                                             |  |  |  |

|-----------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                     |           | •                                                                                                                                                                                                                                                                                             | Composite Video Output                                                                                                                                  |  |  |  |

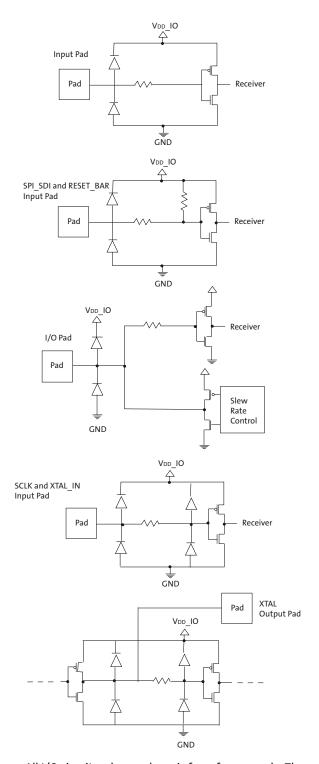

| D1                                                  | DAC_POS   | Output Positive video DAC output in differential mode. Video DAC output in single-ended mode. This interface is enabled by defaul NTSC/PAL signalling. For applications where composite video output is not required, the video DAC can be placed in a power-down state under softwa control. |                                                                                                                                                         |  |  |  |

| C1                                                  | DAC_NEG   | Output                                                                                                                                                                                                                                                                                        | Negative video DAC output in differential mode.                                                                                                         |  |  |  |

| C2                                                  | DAC_REF   | Output                                                                                                                                                                                                                                                                                        | External reference resistor for the video DAC.                                                                                                          |  |  |  |

|                                                     |           |                                                                                                                                                                                                                                                                                               | Manufacturing Test Interface                                                                                                                            |  |  |  |

| G6                                                  | TDI       | Input                                                                                                                                                                                                                                                                                         | JTAG Test pin (Reserved for Test Mode)                                                                                                                  |  |  |  |

| F5                                                  | TDO       | TDO Output JTAG Test pin (Reserved for Test Mode)                                                                                                                                                                                                                                             |                                                                                                                                                         |  |  |  |

| G5 TMS Input JTAG Test pin (Reserved for Test Mode) |           |                                                                                                                                                                                                                                                                                               |                                                                                                                                                         |  |  |  |

| E4 TCK Input JTAG Test pin (Reserved for Test Mode) |           |                                                                                                                                                                                                                                                                                               |                                                                                                                                                         |  |  |  |

| E6                                                  | TRST_BAR  | Input                                                                                                                                                                                                                                                                                         | Connect to GND.                                                                                                                                         |  |  |  |

| F6                                                  | ATEST1    | Input                                                                                                                                                                                                                                                                                         | Analog test input. Connect to GND in normal operation.                                                                                                  |  |  |  |

| D7                                                  | ATEST2    | Input                                                                                                                                                                                                                                                                                         | Analog test input. Connect to GND in normal operation.                                                                                                  |  |  |  |

|                                                     |           |                                                                                                                                                                                                                                                                                               | Power                                                                                                                                                   |  |  |  |

| H7                                                  | VREG_BASE | Supply                                                                                                                                                                                                                                                                                        | Voltage regulator control. Leave floating if not used.                                                                                                  |  |  |  |

| B2, B7, G8,<br>H2, H5, H8                           | VDD       | Supply                                                                                                                                                                                                                                                                                        | Supply for VDD core: 1.8V nominal. Can be connected to the output of the transistor of the off-chip bypass transistor or an external 1.8V power supply. |  |  |  |

| B3, B4, H4,<br>H6                                   | VDD_IO    | Supply                                                                                                                                                                                                                                                                                        | Supply for digital IOs: 2.8V/1.8V nominal.                                                                                                              |  |  |  |

| B1                                                  | VDD_DAC   | Supply                                                                                                                                                                                                                                                                                        | Supply for video DAC: 2.8V nominal.                                                                                                                     |  |  |  |

| F1                                                  | VDD_PLL   | Supply                                                                                                                                                                                                                                                                                        | Supply for PLL: 2.8V nominal.                                                                                                                           |  |  |  |

| D8, E8                                              | VAA       | Supply                                                                                                                                                                                                                                                                                        | Analog power: 2.8V nominal.                                                                                                                             |  |  |  |

| E7                                                  | VAA_PIX   | Supply                                                                                                                                                                                                                                                                                        | Analog pixel array power: 2.8V nominal. Must be at same voltage potential as VAA.                                                                       |  |  |  |

| F7                                                  | Agnd      | Supply                                                                                                                                                                                                                                                                                        | Analog ground.                                                                                                                                          |  |  |  |

| A1, E1                                              | GND_DAC   | Supply                                                                                                                                                                                                                                                                                        | Video DAC Ground.                                                                                                                                       |  |  |  |

| A2,A3,A6,<br>D6,E5,F3,F8                            | GND_IO    | Supply                                                                                                                                                                                                                                                                                        | Digital ground.                                                                                                                                         |  |  |  |

| G1, H1                                              | GND_PLL   | Supply                                                                                                                                                                                                                                                                                        | Ground for PLL                                                                                                                                          |  |  |  |

| G7                                                  | Reserved  | Supply                                                                                                                                                                                                                                                                                        | Leave floating for normal operation.                                                                                                                    |  |  |  |

ASX350AT: 1/5-Inch Color CMOS NTSC/PAL Digital Image Sensor Pin Descriptions and Assignments

# **Pin Assignments**

Pin 1 is not populated with a ball. That allows the device to be identified by an additional marking.

Table 5: Pin Assignments

|   | 1       | 2         | 3           | 4             | 5      | 6             | 7          | 8         |

|---|---------|-----------|-------------|---------------|--------|---------------|------------|-----------|

| Α | GND_DAC | GND_IO    | GND_IO      | <b>D</b> оит6 | Dout4  | GND_IO        | FRAME_SYNC |           |

| В | Vdd_DAC | Vdd       | VDD_IO      | VDD_IO        | Dоит2  | Dоит <b>0</b> | VDD        | SADDR     |

| С | DAC_NEG | DAC_REF   | LINE_VALID  | Dout5         | Dout1  | Sclk          | Sdata      | RESET_BAR |

| D | DAC_POS | Dout_LSB1 | FRAME_VALID | <b>D</b> оит3 | PIXCLK | GND_IO        | ATEST2     | VAA       |

| Е | GND_DAC | Dout_LSB0 | Dout7       | TCK           | GND_IO | TRST_BAR      | VAA_PIX    | VAA       |

| F | Vdd_PLL | SPI_SDI   | GND_IO      | SPI_CS_N      | TDO    | ATEST1        | Agnd       | GND_IO    |

| G | GND_PLL | XTAL      | SPI_SCLK    | SPI_SDO       | TMS    | TDI           | VPP        | Vdd       |

| Н | GND_PLL | VDD       | EXTCLK      | VDD_IO        | VDD    | VDD_IO        | VREG_BASE  | Vdd       |

#### Table 6: Reset/Default State of Interfaces

| Name                   | Reset State               | Default State            | Notes                                                                                                                                                                                                                                                                                                |

|------------------------|---------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTCLK                 | Clock running or stopped  | Clock running            | Input                                                                                                                                                                                                                                                                                                |

| XTAL                   | N/A                       | N/A                      | Input                                                                                                                                                                                                                                                                                                |

| RESET_BAR              | Asserted                  | De-asserted              | Input                                                                                                                                                                                                                                                                                                |

| SCLK                   | N/A                       | N/A                      | Input. Must always be driven to high via a pull-up resistor in the range of 1.5 to 4.7 $\Omega$ .                                                                                                                                                                                                    |

| Sdata                  | High impedance            | High impedance           | Input/Output. Must always be driven to high via a pull-up resistor in the range of 1.5 to 4.7 $\Omega$ .                                                                                                                                                                                             |

| SADDR                  | N/A                       | N/A                      | Input. Must be permanently tied to VDD_IO or GND.                                                                                                                                                                                                                                                    |

| SPI_SCLK               | High impedance.           | Driven, logic 0          | Output. Output enable is R0x0032[13].                                                                                                                                                                                                                                                                |

| SPI_SDI                | Internal pull-up enabled. | Internal pull-up enabled | Input. Internal pull-up is permanently enabled.                                                                                                                                                                                                                                                      |

| SPI_SDO                | High impedance            | Driven, logic 0          | Output enable is R0x0032[13].                                                                                                                                                                                                                                                                        |

| SPI_CS_N               | High impedance            | Driven, logic 1          | Output enable is R0x0032[13].                                                                                                                                                                                                                                                                        |

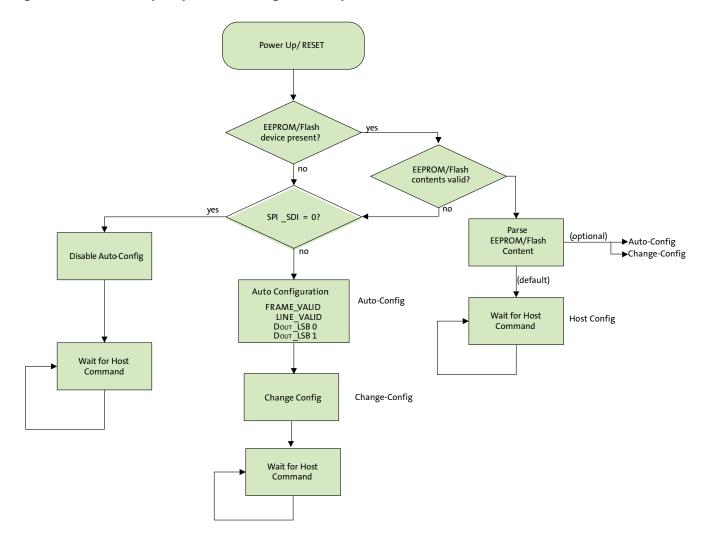

| FRAME_VALID LINE_VALID | High impedance            | High impedance           | Input/Output. This interface disabled by default. Input buffers (used for GPIO function) powered down by default, so these pins can be left unconnected (floating). After reset, these pins are powered up, sampled, then powered down again as part of the autoconfiguration mechanism. See Note 2. |

#### ASX350AT: 1/5-Inch Color CMOS NTSC/PAL Digital Image Sensor Pin Descriptions and Assignments

Table 6: Reset/Default State of Interfaces (continued)

| Name             | Reset State              | Default State            | Notes                                                                                                                                                                                                                                           |

|------------------|--------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIXCLK           | High impedance           | Driven, logic 0          |                                                                                                                                                                                                                                                 |

| Dout <b>7</b>    |                          |                          |                                                                                                                                                                                                                                                 |

| <b>D</b> оит6    |                          |                          |                                                                                                                                                                                                                                                 |

| <b>D</b> оит5    |                          |                          | Outside This intentant and include his defects                                                                                                                                                                                                  |

| Dout4            |                          |                          | Output. This interface disabled by default. See Note 1.                                                                                                                                                                                         |

| <b>D</b> оит3    |                          |                          | See Note 1.                                                                                                                                                                                                                                     |

| Dоит2            |                          |                          |                                                                                                                                                                                                                                                 |

| Dout1            |                          |                          |                                                                                                                                                                                                                                                 |

| Dout0            |                          |                          |                                                                                                                                                                                                                                                 |

| DOUT_LSB1        | High impedance           | High impedance           | Input/Output. This interface disabled by                                                                                                                                                                                                        |

| Dout_LSB0        | High impedance           | HIgh impedance           | default. Input buffers (used for GPIO function) powered down by default, so these pins can be left unconnected (floating). After reset, these pins are powered-up, sampled, then powered down again as part of the autoconfiguration mechanism. |

| DAC_POS          | High impedance           | Driven                   | Output. Interface disabled by hardware reset                                                                                                                                                                                                    |

| DAC_NEG  DAC_REF |                          |                          | and enabled by default when the device starts streaming.                                                                                                                                                                                        |

| TDI              | Internal pull-up enabled | Internal pull-up enabled | Input. Internal pull-up means that this pin can be left unconnected (floating).                                                                                                                                                                 |

| TDO              | High impedance           | High impedance           | Output. Driven only during appropriate parts of the JTAG shifter sequence.                                                                                                                                                                      |

| TMS              | Internal pull-up enabled | Internal pull-up enabled | Input. Internal pull-up means that this pin can be left unconnected (floating).                                                                                                                                                                 |

| TCK              | Internal pull-up enabled | Internal pull-up enabled | Input. Internal pull-up means that this pin can be left unconnected (floating).                                                                                                                                                                 |

| TRST_BAR         | N/A                      | N/A                      | Input. Must always be driven to a valid logic level. Must be driven to GND for normal operation.                                                                                                                                                |

| FRAME_SYNC       | N/A                      | N/A                      | Input. Must always be driven to a valid logic level. Must be driven to GND if not used.                                                                                                                                                         |

| ATEST1           | N/A                      | N/A                      | Must be driven to GND for normal operation.                                                                                                                                                                                                     |

| ATEST2           | N/A                      | N/A                      | Must be driven to GND for normal operation.                                                                                                                                                                                                     |

Notes:

- 1. The reason for defining the default state as logic 0 rather than high impedance is this: when wired in a system (for example, on ON Semiconductor's demo boards), these outputs will be connected, and the inputs to which they are connected will want to see a valid logic level. No current drain should result from driving these to a valid logic level (unless there is a pull-up at the system level).

- 2. These pads have their input circuitry powered down, but they are not output-enabled. Therefore, they can be left floating but they will not drive a valid logic level to an attached device.

ASX350AT: 1/5-Inch Color CMOS NTSC/PAL Digital Image Sensor SOC Description

# **SOC Description**

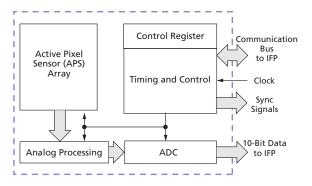

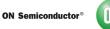

#### **Detailed Architecture Overview**

#### **Sensor Core**

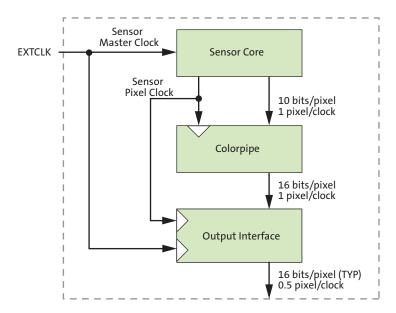

The sensor consists of a pixel array, an analog readout chain, a 10-bit ADC with programmable gain and black offset, and timing and control as illustrated in Figure 4.

Figure 4: Sensor Core Block Diagram

#### **Pixel Array Structure**

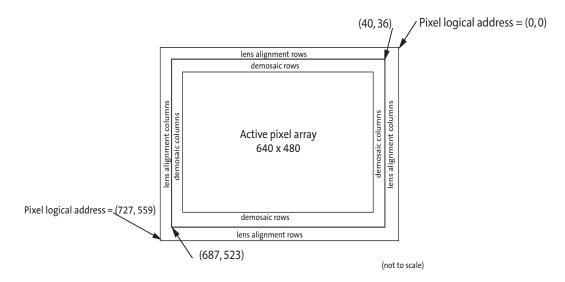

The sensor core pixel array is configured as 728 columns by 560 rows, as shown in Figure 5.

Figure 5: Pixel Array Description

Black rows used internally for automatic black level adjustment are not addressed by default, but can be read out in raw output mode via a register setting.

There are 728 columns by 560 rows of optically-active pixels (that is, clear pixels) that include a pixel boundary around the VGA (640 x 480) image to avoid boundary effects during color interpolation and correction. Among the 728 columns by 560 rows of clear

ASX350AT: 1/5-Inch Color CMOS NTSC/PAL Digital Image Sensor SOC Description

pixels, there are 36 lens alignment rows on the top and bottom, and 40 lens alignment columns on the left and right; and there are 4 demosaic rows and 4 demosaic columns on each side.

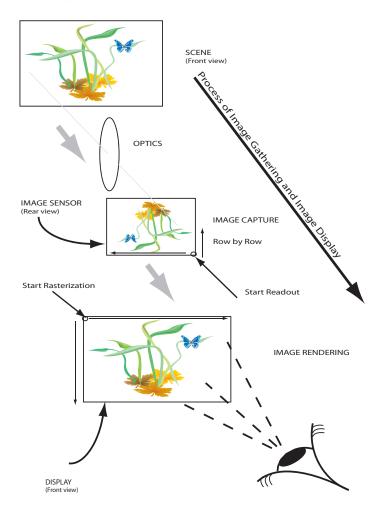

Figure 6 illustrates the process of capturing the image. The original scene is flipped and mirrored by the sensor optics. Sensor readout starts at the lower right corner. The image is presented in true orientation by the output display.

Figure 6: Image Capture Example

# **Sensor Pixel Array**

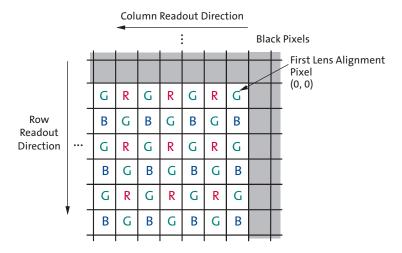

The active pixel array is 640 x 480 pixels. In addition, there are 72 rows and 80 columns for lens alignment and 8 rows and 8 columns for demosaic.

Figure 7: Pixel Color Pattern Detail (top right corner)

#### **Output Data Format**

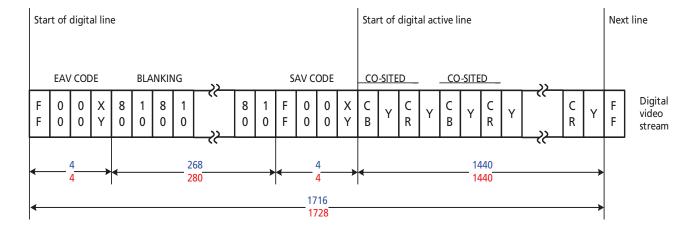

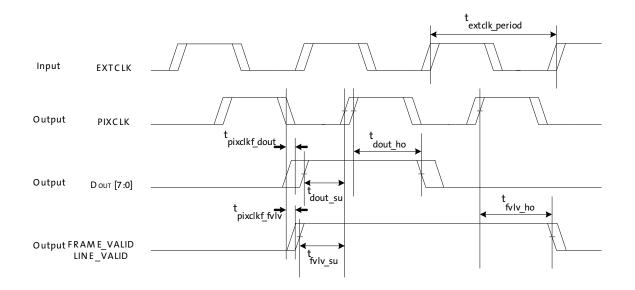

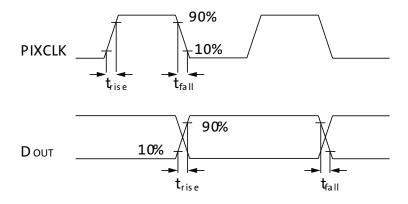

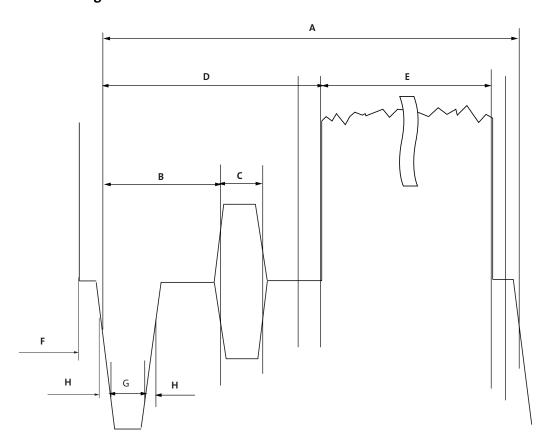

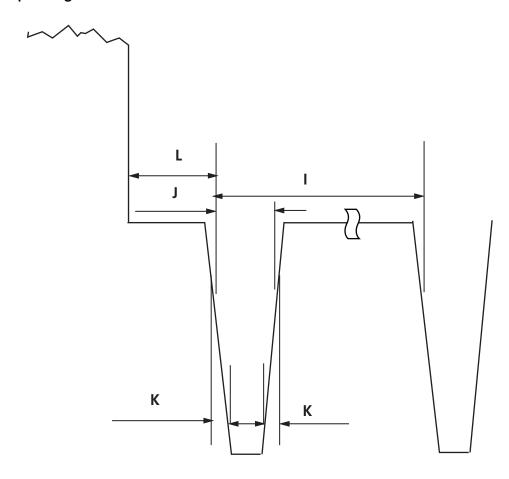

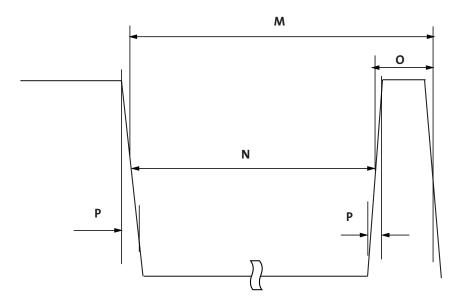

The sensor core image data are read out in progressive scan order. Valid image data are surrounded by horizontal and vertical blanking, shown in Figure 8.

For NTSC output, the horizontal size is stretched from 640 to 720 pixels. The vertical size is 243 pixels per field; 240 image pixels and 3 dark pixels that are located at the bottom of the image field.

For PAL output, the horizontal size is also stretched from 640 to 720 pixels. The vertical size is 288 pixels per field.

Figure 8: Spatial Illustration of Image Readout

| P <sub>0,0</sub> P <sub>0,1</sub> P <sub>0,2</sub>                                                                                     | 00 00 00 00 00 00 00 00 00 00 00       |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

| Valid Image Odd Field                                                                                                                  | Horizontal<br>Blanking                 |  |  |  |

| P <sub>m-2,0</sub> P <sub>m-2,1</sub> P <sub>m-2,n-1</sub> P <sub>m-2,n-1</sub> P <sub>m-2,n-1</sub> P <sub>m,0</sub> P <sub>m,n</sub> | 00 00 00 00 00 00 00 00 00 00 00       |  |  |  |

| 00 00 00 00 00 00<br>00 00 00 00 00 00                                                                                                 | 00 00 00 00 00 00 00 00 00 00 00 0     |  |  |  |

| Vertical Even Blanking                                                                                                                 | Vertical/Horizontal<br>Blanking        |  |  |  |

| 00 00 00                                                                                                                               | 00 00 00 00 00 00 00 00 00 00 00 0     |  |  |  |

| P <sub>1,0</sub> P <sub>1,1</sub> P <sub>1,2</sub>                                                                                     | 00 00 00 00 00 00 00 00 00 00 00       |  |  |  |

| Valid Image Even Field                                                                                                                 | Horizontal<br>Blanking                 |  |  |  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                   | 00 00 00 00 00 00 00 00 00 00 00 0     |  |  |  |

| 00 00 00 00 00 00<br>00 00 00 00 00 00                                                                                                 | 00 00 00 00 00 00<br>00 00 00 00 00 00 |  |  |  |

| Vertical Odd Blanking                                                                                                                  | Vertical/Horizontal<br>Blanking        |  |  |  |

| 00 00 00 00 00 00 00 00 00 00 00                                                                                                       | 00 00 00 00 00 00 00 00 00 00 00 0     |  |  |  |

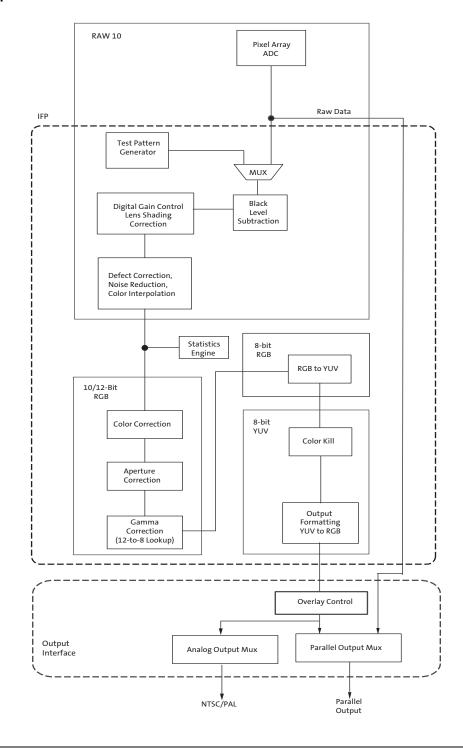

# **Image Flow Processor**

Image and color processing in the ASX350AT are implemented as an image flow processor (IFP) coded in hardware logic. During normal operation, the embedded microcontroller will automatically adjust the operation parameters. The IFP is broken down into different sections, as outlined in Figure 9.

Figure 9: Color Pipeline

#### **Test Patterns**

During normal operation of the ASX350AT, a stream of raw image data from the sensor core is continuously fed into the color pipeline. For test purposes, this stream can be replaced with a fixed image generated by a special test module in the pipeline. The module provides a selection of test patterns sufficient for basic testing of the pipeline.

## **NTSC/PAL Test Pattern Generation**

There is a built-in standard EIA (NTSC) and EBU (PAL) color bars to support hue and color saturation characterization. Each pattern consists of seven color bars (white, yellow, cyan, green, magenta, red, and blue). The Y, Cb and Cr values for each bar are detailed in Tables 7 and 8.

Figure 10: Color Bars

Table 7: EIA Color Bars (NTSC)

|    | Nominal Range | White | Yellow | Cyan | Green | Magenta | Red | Blue |

|----|---------------|-------|--------|------|-------|---------|-----|------|

| Υ  | 16 to 235     | 180   | 162    | 131  | 112   | 84      | 65  | 35   |

| Cb | 16 to 240     | 128   | 44     | 156  | 72    | 184     | 100 | 212  |

| Cr | 16 to 240     | 128   | 142    | 44   | 58    | 198     | 212 | 114  |

Table 8: EBU Color Bars (PAL)

|    | Nominal Range | White | Yellow | Cyan | Green | Magenta | Red | Blue |

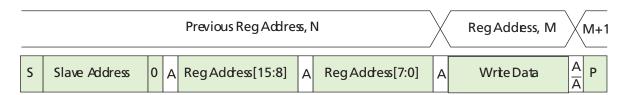

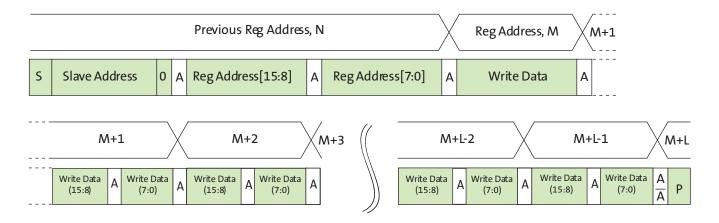

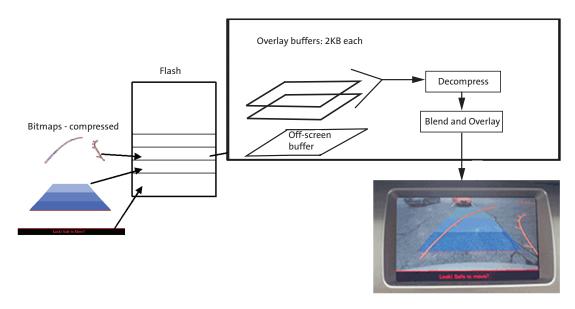

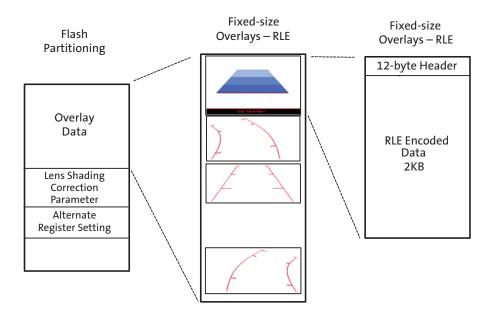

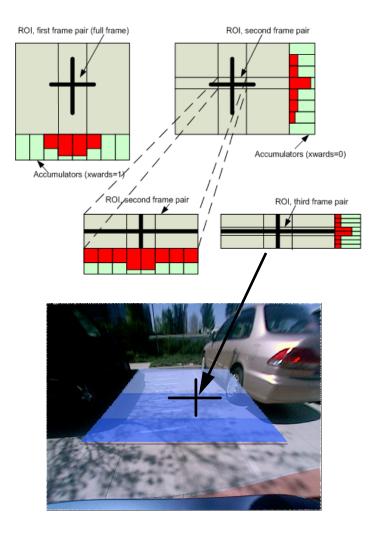

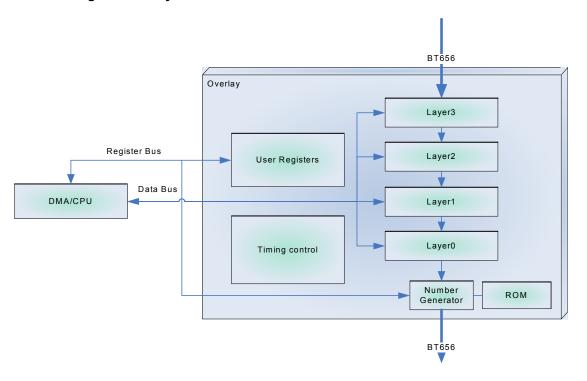

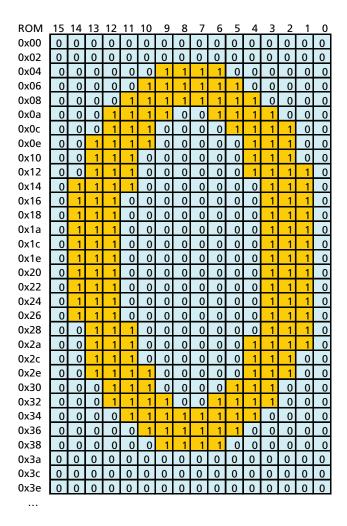

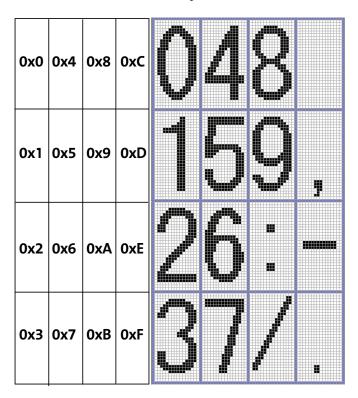

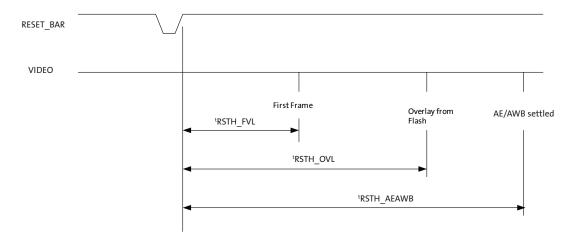

|----|---------------|-------|--------|------|-------|---------|-----|------|