# +5 Volt Electronic eFuse

# **NIS6151**

The NIS6151 is a cost effective, resettable fuse which can greatly enhance the reliability of a USB application from both catastrophic and shutdown failures.

It is designed to buffer the load device from excessive input voltage which can damage sensitive circuits and to protect the input side circuitry from reverse currents. It includes an overvoltage clamp circuit that limits the output voltage during transients but does not shut the unit down, thereby allowing the load circuit to continue its operation.

### Features

- 200 m $\Omega$  Max R<sub>DS(on)</sub>

- Integrated Reverse Current Protection

- Adjustable Output Current Limit Protection with Thermal Shutdown

- IEC61000–4–2 Level 4 ESD Protection for  $V_{bus}$  up to  $\pm 7 \text{ kV}$

- Fast Response Overvoltage Clamp Circuit with Selectable Level

- Internal Undervoltage Lockout Circuit

- Digital Enable with Separate FLAG for Fault Identification

- Integrated Current Monitoring

- Both Latching and Auto-Retry Options Available

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

### **Typical Applications**

- Automotive Infotainment

- USB 2.0/3.0/3.1 V<sub>BUS</sub>

- Solid State Drives

- Mother Boards

## **ON Semiconductor®**

www.onsemi.com

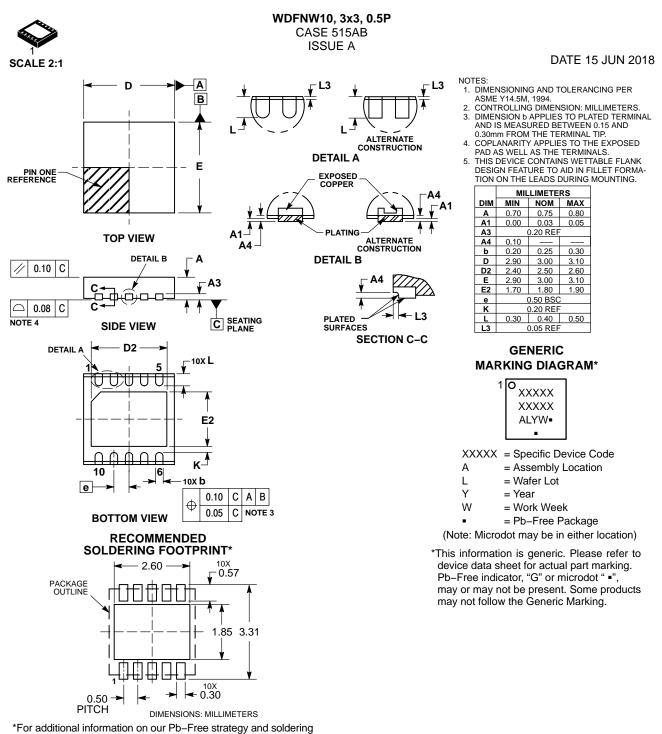

WDFNW10, 3 x 3 CASE 515AB

### MARKING DIAGRAM

= Assembly Location

= Wafer Lot L Υ

А

W

- = Year

- = Work Week

- = Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

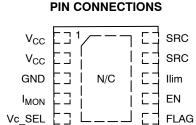

(Top View)

See detailed ordering, marking and shipping information on page 8 of this data sheet.

1

## NIS6151

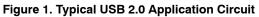

Figure 2. Block Diagram

#### **PIN FUNCTION DESCRIPTION**

| Pin No. | Pin Name         | Description                                                                                                                                                                                                            |

|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2    | V <sub>CC</sub>  | Positive input voltage to the device. (Low ESR capacitor of minimum 4.7 $\mu\text{F}$ from V_{CC} to GND is required)                                                                                                  |

| 3       | GND              | Negative input voltage to the device. This is used as the internal reference for the IC.                                                                                                                               |

| 4       | I <sub>MON</sub> | This pin can be used to monitor the output current by using an external pull-down resistor and de-coupling capacitor.                                                                                                  |

| 5       | Vc_SEL           | The Vc_SEL pin allows the overvoltage clamp to be set at either a 5.7 V or 6.5 V minimum.                                                                                                                              |

| 6       | FLAG             | If a thermal fault occurs, the voltage on this pin will go to a low state to signal a monitoring circuit that the device is in thermal shutdown.                                                                       |

| 7       | EN               | When this pin is pulled low the eFuse is turned off. It can be used to enable or disable the output of the device by pulling it to ground using an open drain or open collector device, as it has an internal pull-up. |

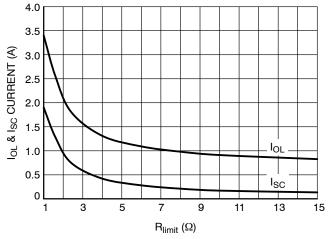

| 8       | llim             | A resistor between this pin and the source pin sets the overload and short circuit current limit levels.                                                                                                               |

| 9, 10   | Source           | Source of the internal power FET and the output terminal of the fuse                                                                                                                                                   |

| 11      | N/C (EP)         | (Exposed Pad) This pad to be used as heatsink only with no electrical connection. It should be connected to a large area of copper on the PCB, or to the PCB's GND plane.                                              |

## MAXIMUM RATINGS

| Rating                                                                                                                                                                    | Symbol            | Value          | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|------|

| Input Voltage, operating, steady-state (V <sub>CC</sub> to GND)                                                                                                           | V <sub>CC</sub>   | –0.3 to +10    | v    |

| Transient (100 ms)                                                                                                                                                        |                   | –0.3 to +10    | v    |

| Output Voltage, operating, steady-state (SRC to GND)                                                                                                                      | V <sub>OUT</sub>  | -0.3 to +20    | V    |

| Voltage range on ILIM pin                                                                                                                                                 | V <sub>ILIM</sub> | -0.3 to +20    | V    |

| Voltage range on Enable pin                                                                                                                                               | V <sub>EN</sub>   | –0.3 to 5      | V    |

| Voltage range on FLAG pin                                                                                                                                                 | V <sub>FLAG</sub> | –0.3 to 6      | V    |

| Voltage range on all other pins                                                                                                                                           |                   | –0.3 to 5      | V    |

| Electrostatic Discharge<br>Human Body Model (All pins)<br>Charged Device Model (All pins)<br>IEC61000-4-2 Contact (Source pins, with 22 μF C <sub>source</sub> condition) | ESD               | ±2<br>±1<br>±7 | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### THERMAL RATINGS

| Rating                                                                                                                                                 | Symbol           | Value      | Unit  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|-------|

| Thermal Resistance, Junction-to-Air<br>(4 layer High-K JEDEC JESD51-7 PCB, 100 mm <sup>2</sup> , 2 oz. Cu)                                             | θ <sub>JA</sub>  | 95         | °C/W  |

| Thermal Characterization Parameter, Junction-to-Lead (4 layer High-K JEDEC JESD51-7 PCB, 100 mm <sup>2</sup> , 2 oz. Cu)                               | ΨJ_L             | 21         | °C/W  |

| Thermal Characterization Parameter, Junction-to-Board (4 layer High-K JEDEC JESD51-7 PCB, 100 mm <sup>2</sup> , 2 oz. Cu)                              | ψЈ-В             | 13         | °C/W  |

| Thermal Characterization Parameter, Junction-to-Top<br>(4 layer High-K JEDEC JESD51-7 PCB, 100 mm <sup>2</sup> , 2 oz. Cu)                             | ΨJ–T             | 20         | °C/W  |

| Total Continuous Power Dissipation @ T <sub>A</sub> = 25°C<br>(4 layer High-K JEDEC JESD51–7 PCB, 100 mm <sup>2</sup> , 2 oz. Cu)<br>Derate above 25°C | P <sub>max</sub> | 1.3        | W     |

| Derate above 25°C                                                                                                                                      |                  | 10.4       | mW/°C |

| Operating Ambient Temperature Range                                                                                                                    | T <sub>A</sub>   | -40 to 125 | °C    |

| Operating Junction Temperature Range                                                                                                                   | TJ               | -40 to 150 | °C    |

| Non-operating Temperature Range                                                                                                                        | T <sub>STG</sub> | -55 to 155 | °C    |

| Lead Temperature, Soldering (10 Sec)                                                                                                                   | TL               | 260        | °C    |

# NIS6151

| Characteristics                                                                                                            | Symbol                  | Min  | Тур      | Max  | Unit  |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------|------|----------|------|-------|

| POWER FET                                                                                                                  | -                       |      |          |      |       |

| Delay Time (enabling of chip to ID = 100 mA with 5 $\Omega$ resistive load)                                                | T <sub>dly</sub>        |      | 1500     |      | μs    |

| ON Resistance (Note 1)                                                                                                     | R <sub>DS(on)</sub>     |      | 135      | 200  | mΩ    |

| T <sub>J</sub> = 140°C (Note 2)                                                                                            | DO(OII)                 |      | 200      |      | -     |

| Continuous Current @ $T_A = 25^{\circ}C$ (Note 2)                                                                          | l <sub>d</sub>          |      |          | 1.0  | Α     |

| Off State Leakage ( $V_{in} = 5 V, EN = 0$ )                                                                               | I <sub>OFF_LEAK</sub>   |      |          | 1    | μA    |

| THERMAL LATCH                                                                                                              | 0                       |      |          |      | ·     |

| Shutdown Temperature (Note 3)                                                                                              | T <sub>SD</sub>         | 150  | 175      | 200  | °C    |

| UNDER/OVERVOLTAGE PROTECTION                                                                                               |                         |      |          |      |       |

| V <sub>OUT</sub> Maximum (V <sub>CC</sub> = 10 V with Vc_SEL pin floating)                                                 | V <sub>out-clamp</sub>  | 6.5  | 6.9      | 7.5  | V     |

| $V_{OUT}$ Maximum ( $V_{CC}$ = 10 V with Vc_SEL pin pulled low (0V))                                                       | V <sub>out-clamp</sub>  | 5.7  | 6.1      | 6.5  | V     |

| Over Voltage Response Time                                                                                                 | T <sub>vout-clamp</sub> |      | 11       | 20   | μs    |

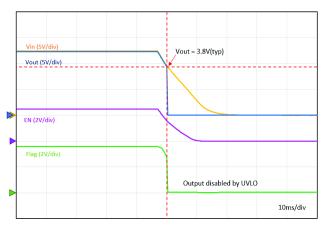

| Undervoltage Lockout (Turn on, Voltage Going High)                                                                         | V <sub>UVLO</sub>       | 3.5  | 3.8      | 4.3  | V     |

| UVLO Hysteresis                                                                                                            | V <sub>Hyst</sub>       |      | 0.35     |      | V     |

| Under Voltage Response Time, VCC Falling, -5 V/ms                                                                          | T <sub>uvlo</sub>       |      | 2        | 6    | μs    |

| Under Voltage Response, VCC Rising, +5 V/ms                                                                                |                         |      | 5        | 10   | μs    |

| CURRENT LIMIT                                                                                                              |                         |      |          |      |       |

| Current Limit                                                                                                              | I <sub>OL</sub>         |      | 1.2      |      | А     |

| Short Circuit Current                                                                                                      | I <sub>sc</sub>         | 0.15 | 0.25     | 0.35 | А     |

| Current Limit Response Time                                                                                                | T <sub>ilim</sub>       |      | 2        | 10   | μs    |

| REVERSE CURRENT LIMIT                                                                                                      | 1                       |      |          |      |       |

| Reverse current blocking threshold (Vout-Vin) (Note 4)                                                                     | V <sub>rev-th</sub>     | 25   | 100      | 250  | mV    |

| Reverse current limit response time (dV <sub>in</sub> /dt = $-5$ V/1 ms, 20 $\mu$ F Load)                                  | V <sub>rev-resp</sub>   | 4    | 7        | 12   | μs    |

| SLEW RATE CONTROL                                                                                                          | I ·                     |      |          |      |       |

| Slew Rate                                                                                                                  | SR                      |      | 1        | 3    | ms    |

| CURRENT MONITOR                                                                                                            |                         |      |          |      |       |

| No Load Current (EN = high, I <sub>load</sub> = 0 A)                                                                       | I <sub>mon-o</sub>      | 0    | 10       | 50   | μA    |

| Gain (I – I <sub>MON</sub> /I <sub>out</sub> , @ I <sub>out</sub> = 1 A, R <sub>MON</sub> = 1 kΩ, C <sub>MON</sub> = 1 μF) | I <sub>mon-gain</sub>   |      | 3.2      |      | mA/A  |

| Clamp voltage of current monitor                                                                                           | VIMON CLAMP             |      | 4.0      |      | V     |

| ENABLE                                                                                                                     |                         |      |          |      |       |

| Logic Level Low (Output Disabled)                                                                                          | V <sub>in-low</sub>     |      | Ι        | 0.4  | V     |

| Logic Level High (Output Enabled) (Note 5)                                                                                 | V <sub>in-high</sub>    | 1.1  |          |      | V     |

| High State Maximum Voltage                                                                                                 | V <sub>in-max</sub>     |      |          | 5    | V     |

| Logic Low Sink Current (V <sub>EN</sub> = 0 V)                                                                             | I <sub>in-low</sub>     |      | 15       | 35   | μA    |

| De-glitch Filter-delay                                                                                                     | Filter-delay            | 2    | 10       | 50   | μs    |

| FLAG                                                                                                                       |                         |      |          |      | . ·   |

| Fault Output Low Voltage (Fault Detected)                                                                                  | Fault-low               |      |          | 0.7  | V     |

| Fault Output High Voltage (No Fault Detected)                                                                              | Fault-high              | 2.5  |          | 5.0  | V     |

| Logic High Source Current                                                                                                  | Flag-I <sub>OH</sub>    |      | 60       |      | μA    |

| Maximum Fan Out for Fault Signal                                                                                           | Fan                     |      | <u> </u> | 2    | Units |

## NIS6151

#### **ELECTRICAL CHARACTERISTICS** (Unless otherwise noted: $V_{CC} = 5 \text{ V}$ , $C_L = 22 \mu\text{F}$ , $R_{limit} = 5.6 \Omega$ , $T_A = -40 \text{ to } 125^{\circ}\text{C}$ )

| Characteristics                                                                                                  | Symbol            | Min | Тур               | Max               | Unit |

|------------------------------------------------------------------------------------------------------------------|-------------------|-----|-------------------|-------------------|------|

| TOTAL DEVICE                                                                                                     |                   |     |                   |                   |      |

| Bias Current<br>Operational (I <sub>Load</sub> = 0 A, EN = 1, FLAG = high)<br>Shutdown (EN = 0)<br>Thermal Fault | I <sub>Bias</sub> |     | 300<br>100<br>100 | 800<br>200<br>200 | μΑ   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

1. Pulse test: Pulse width 300 s, duty cycle 2%

2. Verified by design.

- 3. eFuse is latched off until the En/Fault pin is pulled low and then released or a power on reset is applied to the device. If an auto-retry part is used the device will automatically attempt to turn on once the internal temperature is less than 135°C.

- Once the device has entered shutdown mode due to a reverse current event, it will re-enable its output when V<sub>IN</sub> > V<sub>OUT</sub> for at least 100 μs. The slew rate SR will be applied when the output is re-enabled.

- 5. A voltage level higher than Vin-high min (1.1 V) must be present to ensure a Logic Level High on the Enable pin.

Figure 3. Current Limit vs. R<sub>limit</sub> – Calculated

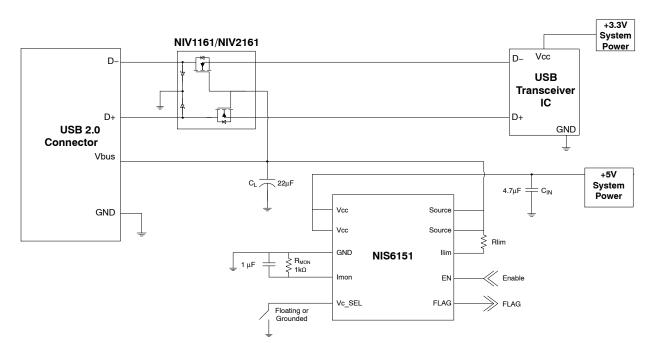

#### APPLICATIONS INFORMATION

#### **Basic Operation**

This device is a self-protected, resettable, electronic fuse. It contains circuits to monitor the input voltage, output voltage, output current and die temperature.

On application of the input voltage, the device will apply the input voltage to the load based on the restrictions of the controlling circuits. The output voltage, which is controlled by an internal dv/dt circuit, will slew from 0 V to the rated output voltage in 1 ms.

The device will remain on as long as the temperature does not exceed the 175°C limit that is programmed into the chip.

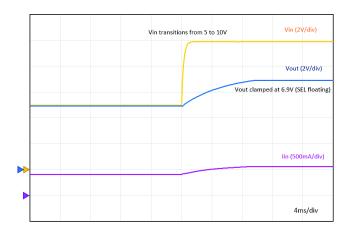

The internal current limit circuit does not shut down the part but will reduce the conductivity of the FET to maintain a constant current at the internally set current limit level. The input overvoltage clamp also does not shutdown the part, but will limit the output voltage in the event that the input exceeds the Vclamp level. This operation can be seen in Figure 5.

An internal charge pump provides bias for the gate voltage of the internal n-channel power FET and also for the current limit circuit. The remainder of the control circuitry operates between the input voltage (VCC) and ground.

The VCC line can generate spike noise in fast transient conditions such as short circuit, and this high peak can cause over–stress and malfunction. To prevent this, a low ESR capacitor (i.e. MLCC) of at least 4.7  $\mu$ F is required.

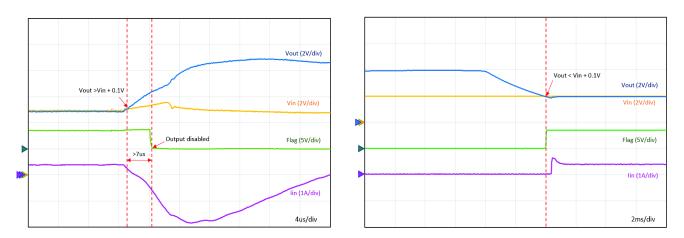

#### **Reverse Current Protection**

The NIS6151 monitors and protects against reverse current events, which can be the result of a malfunction in the power supply or noise induced in the input voltage rail under certain load characteristics (for example, when the load is largely capacitive).

The protection mechanism disables the eFuse's output and triggers when the reverse voltage drop exceeds 100 mV in magnitude and this condition remains for at least 4  $\mu$ s.

The NIS6151 automatically re–enables its output once the input voltage exceeds the output voltage for at least 100  $\mu$ s.

#### **Overvoltage Clamp**

The overvoltage clamp consists of an amplifier and reference. It monitors the output voltage and if the input voltage exceeds the Vclamp voltage, the gate drive of the main FET is reduced to limit the output. This is intended to allow operation through transients while protecting the load. If an overvoltage condition exists for many seconds, the device may overheat due to the voltage drop across the FET combined with the load current. In this event, the thermal protection circuit would shut down the device.

The Vc\_SEL pin can be used to select the Vclamp level. By allowing this pin to float high, the Vclamp value will be set to 6.5 - 7.5 V. By pulling this pin low (to 0V), the Vclamp value will be set to 5.7 - 6.5 V. This allows the NIS6151 to be used in both short and long haul USB applications where the VBUS voltage is adjusted for cable loss compensation. This operation can be seen in Figure 5.

#### **Thermal Protection**

The NIS6151 includes an internal temperature sensing circuit that senses the temperature on the die of the power FET. If the temperature reaches 175°C, the device will shut down, and remove power from the load. If a latching device is used, output power can be restored by either recycling the input power or toggling the enable pin. An auto-retry device will automatically try to restore output power on its own.

The thermal limit has been set high intentionally, to increase the trip time during high power transient events.

#### FLAG

The FLAG pin sends information to other devices regarding the state of the chip. This pin is connected to an internal pull–up so that it behaves as active high. The FLAG pin remains at logic level high during normal operation and gets pulled low and subsequently turns the device off when one of the following conditions occurs:

1. EN pin set to Logic Level Low (Output Disabled)

- 2. Thermal fault

- 3. UVLO Undervoltage Lockout

- 4. Reverse current fault

#### Enable

The Enable feature provides a digital interface to control the output of the eFuse. This pin is meant for push-pull operation and is connected to an internal pull-up so that it behaves as active high. When pulled low by an external circuitry (below 0.5 V), the eFuse output is turned off. Leakage current in this condition is described in the electrical characteristics table.

#### **IMON (Current Monitor)**

The current monitor "IMON" pin provides a small current proportional to the main device current which is passing through the device. This pin must have a decoupling capacitor to filter out internal sampling noise. A resistor connected between the IMON pin and GND converts the IMON current into a GND referenced voltage. The recommended resistor value of 1 k $\Omega$  will give about 1 V for every 1 A of device current. The IMON voltage to output current relationship is given in the below equation.

$$V_{MON} = 3.2 \times R_{MON} \times \left(\frac{I_d}{1000}\right)$$

Appropriate  $R_{MON}$  value should be selected keeping the max rating of the device of the interfacing circuit in mind. The value should be limited to 3 k $\Omega$  for best operation of the IMON function. This pin can be floated if this function is not needed thus saving a few mA of leakage current.

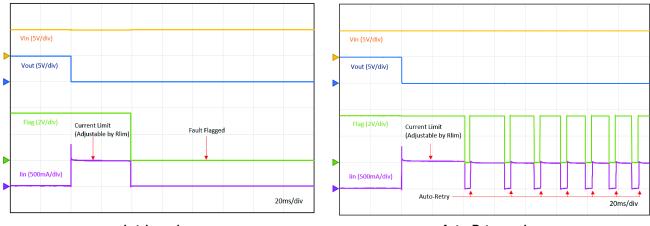

#### Latching vs. Auto-Retry

This device features two options regarding its reset ability after a thermal shutdown event. These are called latching and auto-retry which are respectively marked MT1 and MT2 as part number suffixes. Upon reaching a thermal shutdown state, a latching device (MT1) will remain shutdown with no power supplied to the output (SRC pins). The only way to reset the device is to either perform a power cycle on the VCC bus or pull the EN pin low (<0.4 V). By doing either of these actions, the fault state is cleared and the device is allowed to pull-up the output to its normal, high state.

Instead of remaining in thermal shutdown, an Auto–retry device (MT2) will automatically attempt to pull up the output once the die temperature cools to  $< 135^{\circ}$ C. If the fault remains on the output during this attempt, the device will once again enter a short period of current limiting that will eventually lead to thermal shutdown for which the auto–retry process will repeat indefinitely.

Figure 4. Output Short Circuit

Auto-Retry version

Figure 5. Output Voltage Protection

Figure 6. Reverse Current Protection

### **ORDERING INFORMATION**

| Device        | Shutdown Version | Marking | Package   | Shipping <sup>†</sup> |

|---------------|------------------|---------|-----------|-----------------------|

| NIS6151MT1TXG | Latching         | 6151    | WDFNW10   | 2000 / Tana and Baal  |

| NIS6151MT2TXG | Auto-Retry       | 6151H   | (Pb-Free) | 3000 / Tape and Reel  |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 98AON30588G        | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | WDFNW10, 3x3, 0.5P | PAGE 1 OF 1                                                                                                                                                                         |  |  |  |  |

| DESCRIPTION: WDFNW10, 3X3, 0.5P PAGE 1 OF 1 ON Semiconductor and (10) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.                                                                                                                                                                                                                                                                                                                                   |                    |                                                                                                                                                                                     |  |  |  |  |

| ON Semiconductor and up are trademarks or semiconductor components industries, LLC doa ON semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically |                    |                                                                                                                                                                                     |  |  |  |  |

the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor date sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use a a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor houteds for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

ON Semiconductor Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative