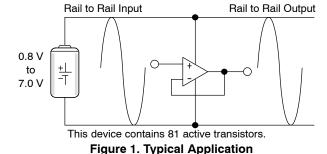

# Sub-One Volt Rail-to-Rail Operational Amplifier with Enable Feature

The NCS2002 is an industry first sub—one volt operational amplifier that features a rail—to—rail common mode input voltage range, along with rail—to—rail output drive capability. This amplifier is guaranteed to be fully operational down to 0.9 V, providing an ideal solution for powering applications from a single cell Nickel Cadmium (NiCd) or Nickel Metal Hydride (NiMH) battery. Additional features include no output phase reversal with overdriven inputs, trimmed input offset voltage of 0.5 mV, extremely low input bias current of 40 pA, and a unity gain bandwidth of 1.1 MHz at 5.0 V.

The NCS2002 also has an active high enable pin that allows external shutdown of the device. In the standby mode, the supply current is typically 1.9  $\mu A$  at 1.0 V. Because of its small size and enable feature, this amplifier represents the ideal solution for small portable electronic applications. The NCS2002 is available in the space saving SOT23–6 (TSOP–6) package with two industry standard pinouts.

#### **Features**

- 0.9 V Guaranteed Operation

- Standby Mode:  $I_D = 1.9 \mu A$  at 1.0 V, Typical

- Rail-to-Rail Common Mode Input Voltage Range

- Rail-to-Rail Output Drive Capability

- No Output Phase Reversal for Over-Driven Input Signals

- 0.5 mV Trimmed Input Offset

- 10 pA Input Bias Current

- 1.1 MHz Unity Gain Bandwidth at  $\pm 2.5$  V, 1.0 MHz at  $\pm 0.5$  V

- Tiny SOT23-6 (TSOP-6) Package

- NCV Parts AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb-Free and are RoHS Compliant

### **Typical Applications**

- Single Cell NiCd / NiMH Battery Powered Applications

- Cellular Telephones

- Pagers

- Personal Digital Assistants

- Electronic Games

- Digital Cameras

- Camcorders

- Hand Held Instruments

#### ON Semiconductor®

http://onsemi.com

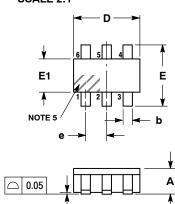

TSSOP-6 SN SUFFIX CASE 318G

#### **MARKING DIAGRAM**

AA = Device Code

x = Marking Defined on Page 15 in Ordering Information

A = Assembly Location

Y = Year W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

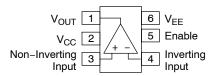

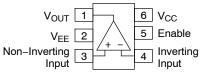

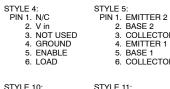

#### PIN CONNECTIONS

Style 1 Pinout (SN1T1)

Style 2 Pinout (SN2T1)

#### ORDERING AND MARKING INFORMATION

See detailed ordering, marking, and shipping information in the package dimensions section on page 15 of this data sheet.

#### **MAXIMUM RATINGS**

| Rating                                                                                                                                               | Symbol                             | Value                             | Unit       |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------|------------|

| Supply Voltage (V <sub>CC</sub> to V <sub>EE</sub> )                                                                                                 | V <sub>S</sub>                     | 7.0                               | V          |

| Input Differential Voltage Range (Note 1)                                                                                                            | V <sub>IDR</sub>                   | V <sub>EE</sub> – 300 mV to 7.0 V | V          |

| Input Common Mode Voltage Range (Note 1)                                                                                                             | V <sub>ICR</sub>                   | V <sub>EE</sub> – 300 mV to 7.0 V | V          |

| Output Short Circuit Duration (Note 2)                                                                                                               | t <sub>Sc</sub>                    | Indefinite                        | sec        |

| Junction Temperature                                                                                                                                 | TJ                                 | 150                               | °C         |

| Power Dissipation and Thermal Characteristics<br>SOT23–6 Package<br>Thermal Resistance, Junction–to–Air<br>Power Dissipation @ T <sub>A</sub> = 70°C | R <sub>eJA</sub><br>P <sub>D</sub> | 235<br>340                        | °C/W<br>mW |

| Operating Ambient Temperature Range<br>NCS2002<br>NCV2002 (Note 3)                                                                                   | T <sub>A</sub>                     | -40 to 105<br>-40 to 125          | °C         |

| Storage Temperature Range                                                                                                                            | T <sub>stg</sub>                   | -65 to 150                        | °C         |

| ESD Protection at any Pin Human Body Model (Note 4)                                                                                                  | V <sub>ESD</sub>                   | 1500                              | V          |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect

- Either or both inputs should not exceed the range of V<sub>EE</sub> 300 mV to V<sub>EE</sub> + 7.0 V.

Maximum package power dissipation limits must be observed to ensure that the maximum junction temperature is not exceeded. T<sub>J</sub>T<sub>A</sub> + (P<sub>D</sub> R<sub>θJA</sub>)

NCV prefix is for automotive and other applications requiring site and change control.

ESD data available upon request.

## **DC ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 2.5 \text{ V}$ , $V_{EE} = -2.5 \text{ V}$ , $V_{CM} = V_O = 0 \text{ V}$ , $R_L$ to GND, $T_A = 25^{\circ}C$ , unless otherwise noted)

| Rating                                                                                            | Symbol                       | Min         | Тур                                | Max | Unit  |

|---------------------------------------------------------------------------------------------------|------------------------------|-------------|------------------------------------|-----|-------|

| Input Offset Voltage<br>V <sub>CC</sub> = 0.45 V, V <sub>EE</sub> = -0.45 V                       | V <sub>IO</sub>              |             |                                    |     | mV    |

| $T_{\Delta} = 25^{\circ}C$                                                                        |                              | -6.0        | 0.5                                | 6.0 |       |

| $T_A = 0$ °C to 70°C                                                                              |                              | -8.5        | _                                  | 8.5 |       |

| $T_A = -40 \text{ to } +125^{\circ}\text{C}$                                                      |                              | -9.5        | _                                  | 9.5 |       |

| $V_{CC} = 1.5 \text{ V}, V_{EE} = -1.5 \text{ V}$                                                 |                              |             |                                    |     |       |

| $T_A = 25^{\circ}C$                                                                               |                              | -6.0        | 0.5                                | 6.0 |       |

| $T_A = 0^{\circ}C \text{ to } 70^{\circ}C$                                                        |                              | -7.0<br>7.5 | _                                  | 7.0 |       |

| $T_A = -40 \text{ to } +125^{\circ}\text{C}$<br>$V_{CC} = 2.5 \text{ V}, V_{FF} = -2.5 \text{ V}$ |                              | -7.5        | _                                  | 7.5 |       |

| $V_{CC} = 2.5 \text{ V}, V_{EE} = -2.5 \text{ V}$ $T_{A} = 25^{\circ}\text{C}$                    |                              | -6.0        | 0.5                                | 6.0 |       |

| $T_A = 0^{\circ}$ C to $70^{\circ}$ C                                                             |                              | -7.5        | 0.5                                | 7.5 |       |

| $T_A = -40 \text{ to } +125^{\circ}\text{C}$                                                      |                              | -7.5        | _                                  | 7.5 |       |

| Input Offset Voltage Temperature Coefficient ( $R_S = 50$ )<br>$T_A = -40$ to +125°C              | $\Delta V_{IO}$ / $\Delta T$ | _           | 8.0                                | -   | μV/°C |

| Input Bias Current (V <sub>CC</sub> = 1.0 V to 5.0 V)                                             | I <sub>IB</sub>              | -           | 10                                 | -   | pА    |

| Input Common Mode Voltage Range                                                                   | V <sub>ICR</sub>             | -           | $V_{\text{EE}}$ to $V_{\text{CC}}$ | =   | V     |

| Large Signal Voltage Gain                                                                         | A <sub>VOL</sub>             |             |                                    |     | kV/V  |

| $V_{CC} = 0.45 \text{ V}, V_{EE} = -0.45 \text{ V}$ $R_L = 10 \text{ k}$                          |                              | -           | 40                                 | -   |       |

| $V_{CC} = 1.5 \text{ V}, V_{EE} = -1.5 \text{ V}$ $R_L = 10 \text{ k}$                            |                              | -           | 40                                 | -   |       |

| $V_{CC} = 2.5 \text{ V}, V_{EE} = -2.5 \text{ V}$ $R_1 = 10 \text{ k}$                            |                              | 10          | 40                                 | _   |       |

| Output Voltage Swing, High State Output (V <sub>ID</sub> = + 0.5 V)                               | V <sub>OH</sub>              |             |                                    |     | V     |

| $T_A = T_{low}$ to $T_{high}$                                                                     |                              |             |                                    |     |       |

| $V_{CC} = 0.45 \text{ V}, V_{EE} = -0.45 \text{ V}$                                               |                              |             |                                    |     |       |

| R <sub>L</sub> = 10 k                                                                             |                              | 0.40        | 0.442                              | _   |       |

| $R_L = 2.0 \text{ k}$                                                                             |                              | 0.35        | 0.409                              | _   |       |

| $V_{CC} = 1.5 \text{ V}, V_{EE} = -1.5 \text{ V}$<br>$R_L = 10 \text{ k}$                         |                              | 1.45        | 1.494                              | _   |       |

| $R_1 = 2.0 \text{ k}$                                                                             |                              | 1.40        | 1.473                              | _   |       |

| $V_{CC} = 2.5 \text{ V}, V_{EE} = -2.5 \text{ V}$                                                 |                              | 1.40        | 1.475                              |     |       |

| R <sub>1</sub> = 10 k                                                                             |                              | 2.45        | 2.493                              | _   |       |

| $R_{L}^{L} = 2.0 \text{ k}$                                                                       |                              | 2.40        | 2.469                              | -   |       |

**DC ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 2.5 \text{ V}$ ,  $V_{EE} = -2.5 \text{ V}$ ,  $V_{CM} = V_O = 0 \text{ V}$ ,  $R_L$  to GND,  $T_A = 25^{\circ}C$ , unless otherwise noted)

| Rating                                                                                                                                                                                                                     | Symbol              | Min                          | Тур                            | Max                     | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------|--------------------------------|-------------------------|------|

| Output Voltage Swing, Low State Output ( $V_{ID} = -0.5 \text{ V}$ ) $T_A = -40 \text{ to } +125^{\circ}\text{C}$                                                                                                          | V <sub>OL</sub>     |                              |                                |                         | V    |

| $V_{CC} = 0.45 \text{ V}, V_{EE} = -0.45 \text{ V}$ $R_L = 10 \text{ k}$ $R_L = 2.0 \text{ k}$ $V_{CC} = 1.5 \text{ V}, V_{EE} = -1.5 \text{ V}$                                                                           |                     | _<br>_                       | -0.446<br>-0.432               | -0.40<br>-0.35          |      |

| $R_L = 10 \text{ k}$<br>$R_L = 2.0 \text{ k}$                                                                                                                                                                              |                     | -                            | -1.497<br>-1.484               | -1.45<br>-1.40          |      |

| $V_{CC} = 2.5 \text{ V}, V_{EE} = -2.5 \text{ V}$ $R_L = 10 \text{ k}$ $R_L = 2.0 \text{ k}$                                                                                                                               |                     | <u>-</u><br>-                | -2.496<br>-2.481               | -2.45<br>-2.40          |      |

| Common Mode Rejection Ratio (V <sub>in</sub> = 0 to 5.0 V)                                                                                                                                                                 | CMRR                | 60                           | 82                             | -                       | dB   |

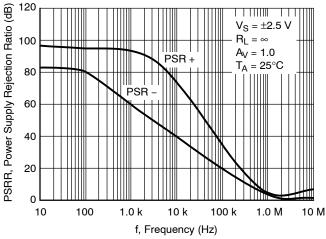

| Power Supply Rejection Ratio ( $V_{CC} = 0.5 \text{ V}$ to 2.5 V, $V_{EE} = -2.5 \text{ V}$ )                                                                                                                              | PSRR                | 60                           | 85                             | _                       | dB   |

| Output Short Circuit Current $V_{CC}$ = 0.45 V, $V_{EE}$ = -0.45 V, $V_{ID}$ = $\pm$ 0.4 V Source Current High Output State Sink Current Low Output State                                                                  | I <sub>SC</sub>     | 0.5                          | 1.0<br>-3.0                    | _<br>                   | mA   |

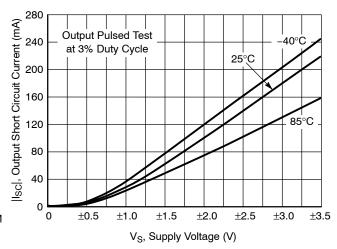

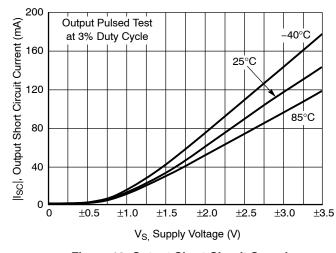

| $V_{CC} = 1.5 \text{ V}, V_{EE} = -1.5 \text{ V}, V_{ID} = \pm 0.5 \text{ V}$ Source Current High Output State Sink Current Low Output State $V_{CC} = 2.5 \text{ V}, V_{EE} = -2.5 \text{ V}, V_{ID} = \pm 0.5 \text{ V}$ |                     | 25<br>-                      | 32<br>–58                      | -<br>-<br>-45           |      |

| Source Current High Output State<br>Sink Current Low Output State                                                                                                                                                          |                     | 65<br>-                      | 86<br>-128                     | _<br>_100               |      |

| Power Supply Current (Per Amplifier, $V_O = 0 \text{ V}$ )<br>$T_A = -40 \text{ to } +125^{\circ}\text{C}$<br>$V_{CC} = 0.5 \text{ V to } V_{EE} = -0.5 \text{ V}$                                                         | I <sub>D</sub>      |                              |                                |                         | μΑ   |

| Venable = $V_{CC}$<br>Venable = $V_{EE}$<br>$V_{CC}$ = 1.5 V to $V_{EE}$ = -1.5 V                                                                                                                                          |                     | -<br>-                       | 480<br>1.5                     | 600<br>3.0              |      |

| Venable = $V_{CC}$<br>Venable = $V_{EE}$                                                                                                                                                                                   |                     | -<br>-                       | 720<br>2.2                     | 900<br>5.0              |      |

| $V_{CC}$ = 2.5 V to $V_{EE}$ = -2.5 V<br>Venable = $V_{CC}$<br>Venable = $V_{EE}$                                                                                                                                          |                     | -<br>-                       | 820<br>2.5                     | 1000<br>5.0             |      |

| Enable Input Threshold Voltage (V <sub>CC</sub> = 2.5 V, V <sub>EE</sub> = -2.5 V) Operating Disabled                                                                                                                      | V <sub>th(EN)</sub> | -<br>1.7 V + V <sub>EE</sub> | 2.7 V + V <sub>EE</sub><br>1.9 | 2.8 V + V <sub>EE</sub> | V    |

| Enable Input Current (V <sub>CC</sub> = 5.0 V, V <sub>EE</sub> = 0) Enable = 5.0 V Enable = GND                                                                                                                            | I <sub>Enable</sub> | -<br>-                       | 1.1<br>1.1                     | 2.0<br>2.0              | μΑ   |

$\textbf{AC ELECTRICAL CHARACTERISTICS} \ (V_{CC} = 2.5 \ \text{V}, \ V_{EE} = -2.5 \ \text{V}, \ V_{CM} = V_O = 0 \ \text{V}, \ R_L \ \text{to GND}, \ T_A = 25 ^{\circ}\text{C}, \ \text{unless otherwise noted})$

| Rating                                                                                                                                                                                          | Symbol           | Min           | Тур               | Max         | Unit          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|-------------------|-------------|---------------|

| Differential Input Resistance (V <sub>CM</sub> = 0 V)                                                                                                                                           | R <sub>in</sub>  | -             | >1.0              | -           | tera $\Omega$ |

| Differential Input Capacitance (V <sub>CM</sub> = 0 V)                                                                                                                                          | C <sub>in</sub>  | -             | 3.0               | _           | pf            |

| Equivalent Input Noise Voltage (f = 1.0 kHz)                                                                                                                                                    | e <sub>n</sub>   | -             | 100               | _           | nV/√Hz        |

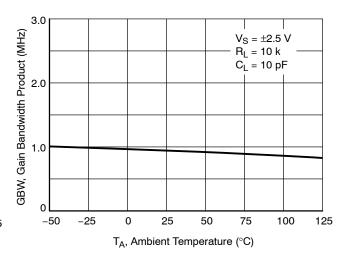

| Gain Bandwidth Product (f = 100 kHz) $V_{CC} = 0.45 \text{ V, } V_{EE} = -0.45 \text{ V}$ $V_{CC} = 1.5 \text{ V, } V_{EE} = -1.5 \text{ V}$ $V_{CC} = 2.5 \text{ V, } V_{EE} = -2.5 \text{ V}$ | GBW              | -<br>-<br>0.6 | 0.8<br>0.8<br>0.9 | _<br>_<br>_ | MHz           |

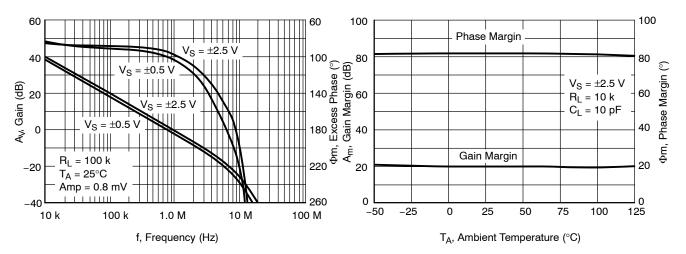

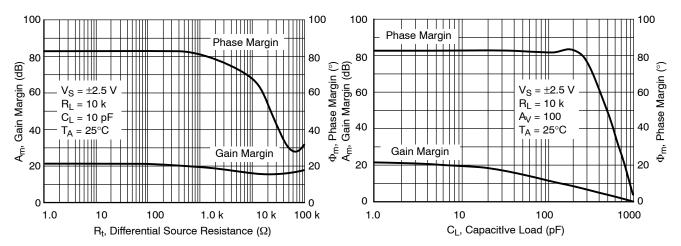

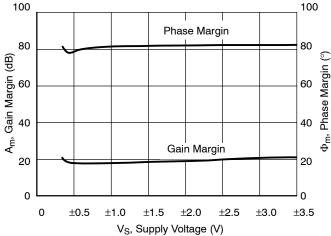

| Gain Margin (R <sub>L</sub> = 10 k, C <sub>L</sub> = 5.0 pf)                                                                                                                                    | Am               | -             | 6.5               | _           | dB            |

| Phase Margin (R <sub>L</sub> = 10 k, C <sub>L</sub> = 5.0 pf)                                                                                                                                   | φm               | -             | 60                | _           | Deg           |

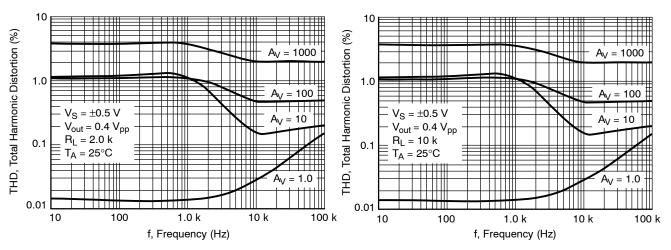

| Power Bandwidth (V <sub>O</sub> = 4.0 V <sub>PP</sub> , R <sub>L</sub> = 2.0 k, THD = 1.0 %, A <sub>V</sub> = 1.0)                                                                              | BW <sub>P</sub>  | -             | 80                | _           | kHz           |

| Total Harmonic Distortion ( $V_O$ = 4.0 $V_{PP}$ , $R_L$ = 2.0 k, $A_V$ = 1.0) f = 1.0 kHz f = 10 kHz                                                                                           | THD              | _<br>_<br>_   | 0.008<br>0.08     | _<br>_      | %             |

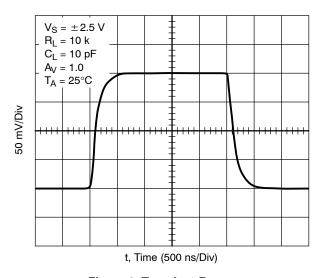

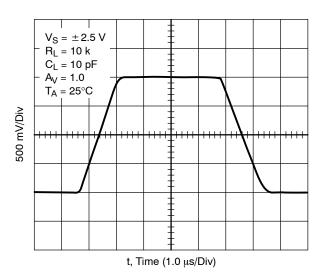

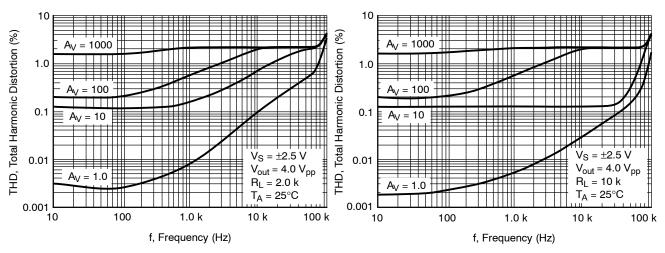

| Slew Rate (V <sub>S</sub> = $\pm 2.5$ V, V <sub>O</sub> = $-2.0$ V to $2.0$ V, R <sub>L</sub> = $2.0$ k, A <sub>V</sub> = $1.0$ )<br>Positive Slope<br>Negative Slope                           | SR               | 0.85<br>0.85  | 1.2<br>1.3        | -<br>-      | V/µs          |

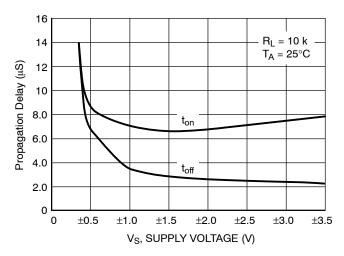

| Time Delay for Device to Turn On (R <sub>L</sub> = 10 k)                                                                                                                                        | t <sub>on</sub>  | -             | 5.5               | 7.5         | μs            |

| Time Delay for Device to Turn Off (R <sub>L</sub> = 10 k)                                                                                                                                       | t <sub>off</sub> | -             | 2.5               | 3.0         | μs            |

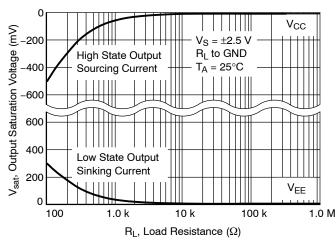

V<sub>sat</sub>, Output Saturation Voltage (V)  $V_{CC}$ -0.2 $V_S = \pm 2.5 V$ -0.3R<sub>L</sub> to GND High State Output  $T_A = 25^{\circ}C$ -0.4Sourcing Current -0.5 0.4 Low State Output 0.3 Sinking Current 0.2 0.1  $V_{EE}$ 4.0 8.0 12 16 0 20 I<sub>L</sub>, Load Current (mA)

Figure 2. Output Saturation Voltage versus

Load Resistance

Figure 3. Output Saturation Voltage versus Load Current

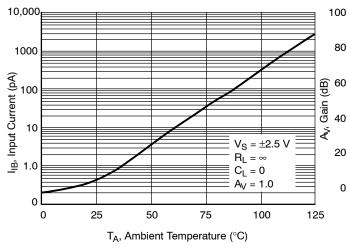

Figure 4. Input Bias Current versus Temperature

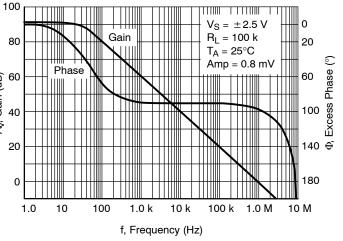

Figure 5. Gain and Phase versus Frequency

Figure 6. Transient Response

Figure 7. Slew Rate

90 CMRR, Common Mode Rejection Ratio (dB) 80 70  $A_{V} = 1.0$ 60 = 25°C 50 40 30 20 10 0 10 10 k 100 k 100 1.0 k 1.0 M 10 M f, Frequency (Hz)

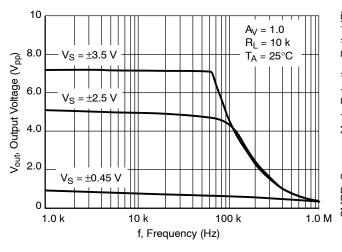

Figure 8. Output Voltage versus Frequency

Figure 9. Common Mode Rejection Ratio versus Frequency

Figure 11. Output Short Circuit Sinking Current versus Supply Voltage

Figure 12. Output Short Circuit Sourcing Current versus Supply Voltage

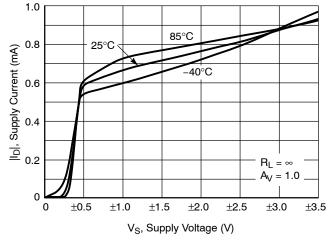

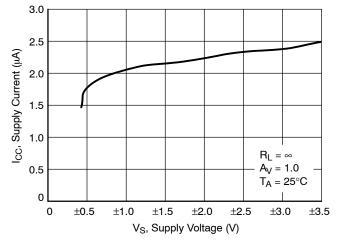

Figure 13. Supply Current versus Supply Voltage with No Load

Figure 14. Total Harmonic Distortion versus Frequency with 1.0 V Supply

Figure 15. Total Harmonic Distortion versus Frequency with 1.0 V Supply

Figure 16. Total Harmonic Distortion versus Frequency with 5.0 V Supply

Figure 17. Total Harmonic Distortion versus Frequency with 5.0 V Supply

Figure 18. Slew Rate versus Temperature

Figure 19. Gain Bandwidth Product versus Temperature

Figure 20. Voltage Gain and Phase versus Frequency

Figure 21. Gain and Phase Margin versus **Temperature**

Figure 22. Gain and Phase Margin versus **Differential Source Resistance**

8.0

V<sub>out</sub>, Output Voltage (V<sub>pp</sub>)

0

±0.5

±1.0

100 Phase Margin 80 Gain Margin (dB) 60 40 Å, Gain Margin 20

Figure 24. Output Voltage Swing versus **Supply Voltage**

±2.0

V<sub>S</sub>, Supply Voltage (V)

±2.5

±1.5

Figure 23. Gain and Phase Margin versus

**Output Load Capacitance**

Figure 25. Gain and Phase Margin versus **Supply Voltage**

$R_L = 10 k$

A<sub>V</sub> = 100 T<sub>A</sub> = 25°C

±3.0

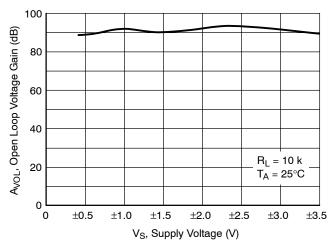

Figure 26. Open Loop Voltage Gain versus Supply Voltage

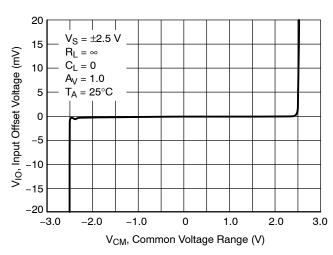

Figure 27. Input Offset Voltage versus Common Mode Input Voltage Range, V<sub>S</sub> = ±2.5 V

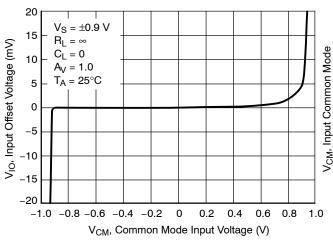

Figure 28. Input Offset Voltage versus Common Mode Input Voltage Range,  $V_S = \pm 0.9 \text{ V}$

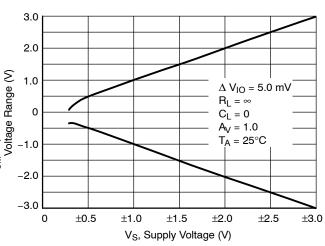

Figure 29. Common-Mode Input Voltage Range versus Power Supply Voltage

Figure 30. Supply Current versus Supply Voltage (Disabled)

Figure 31. Enable Input Voltage versus Supply Voltage

Figure 32. Propagation Delay versus Supply Voltage

#### APPLICATION INFORMATION AND OPERATING DESCRIPTION

#### **GENERAL INFORMATION**

The NCS2002 is an industry first rail-to-rail input, rail-to-rail output amplifier that features guaranteed sub one volt operation. This unique feature set is achieved with the use of a modified analog CMOS process that allows the implementation of depletion MOSFET devices. The amplifier has a 1.0 MHz gain bandwidth product, 1.2  $V/\mu s$  slew rate and is operational over a power supply range less than 0.9 V to as high as 7.0 V.

### Inputs

The input topology chosen for this device series is unconventional when compared to most low voltage operational amplifiers. It consists of an N-channel depletion mode differential transistor pair that drives a folded cascade stage and current mirror. This configuration extends the input common mode voltage range to encompass the  $V_{\rm EE}$  and  $V_{\rm CC}$  power supply rails, even when powered from a combined total of less than 0.9 volts. Figures 27, 28 and 29 show the input common mode voltage range versus power supply voltage.

The differential input stage is laser trimmed in order to minimize offset voltage. The N-channel depletion mode MOSFET input stage exhibits an extremely low input bias current of less than 10 pA. The input bias current versus temperature is shown in Figure 4. Either one or both inputs can be biased as low as  $V_{\rm EE}$  minus 300 mV to as high as 7.0 V without causing damage to the device. If the input common mode voltage range is exceeded, the output will not display a phase reversal. If the maximum input positive or negative voltage ratings are to be exceeded, a series resistor must be used to limit the input current to less than 2.0 mA.

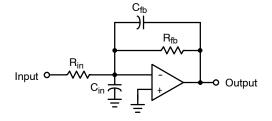

The ultra low input bias current of the NCS2002 allows the use of extremely high value source and feedback resistor without reducing the amplifier's gain accuracy. These high value resistors, in conjunction with the device input and printed circuit board parasitic capacitances  $C_{in}$ , will add an additional pole to the single pole amplifier in Figure 33. If low enough in frequency, this additional pole can reduce the phase margin and significantly increase the output settling time. The effects of  $C_{in}$ , can be canceled by placing a zero into the feedback loop. This is accomplished with the addition of capacitor  $C_{fb}$ . An approximate value for  $C_{fb}$  can be calculated by:

$$C_{fb} = \frac{R_{in} \times C_{in}}{R_{fb}}$$

Cin = Input and printed circuit board capacitance

Figure 33. Input Capacitance Pole Cancellation

#### Output

The output stage consists of complementary P and N channel devices connected to provide rail-to-rail output drive. With a 2.0 k load, the output can swing within 50 mV of either rail. It is also capable of supplying over 75 mA when powered from 5.0 V and 1.0 mA when powered from 0.9 V.

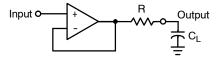

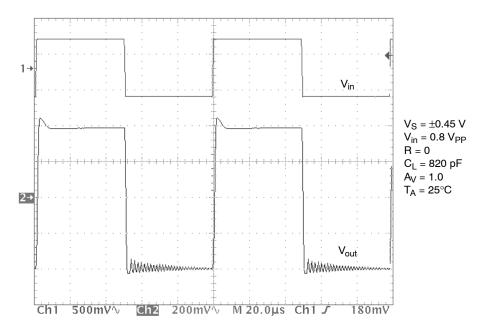

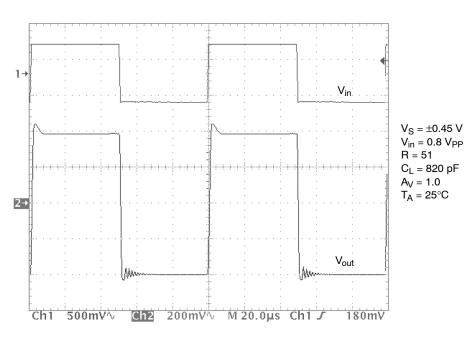

When connected as a unity gain follower, the NCS2002 can directly drive capacitive loads in excess of 820 pF at room temperature without oscillating but with significantly reduced phase margin. The unity gain follower configuration exhibits the highest bandwidth and is most prone to oscillations when driving a high value capacitive load. The capacitive load in combination with the amplifier's output impedance, creates a phase lag that can result in an under-damped pulse response or a continuous oscillation. Figure 35 shows the effect of driving a large capacitive load in a voltage follower type of setup. When driving capacitive loads exceeding 820 pF, it is recommended to place a low value isolation resistor between the output of the op amp and the load, as shown in Figure 34. The series resistor isolates the capacitive load from the output and enhances the phase margin. Refer to Figure 36. Larger values of R will result in a cleaner output waveform but excessively large values will degrade the

large signal rise and fall time and reduce the output amplitude. Depending upon the capacitor characteristics, the isolation resistor value will typically be between 50 to 500  $\Omega$ . The output drive capability for resistive and capacitive loads is shown in Figures 2, 3, and 23.

Isolation resistor R = 50 to 500

Figure 34. Capacitance Load Isolation

Note that the lowest phase margin is observed at cold temperature and low supply voltage.

#### **Enable Pin**

The enable pin allows the user to externally control the device. if the enable pin is pulled below the input disable threshold voltage ( $V_{EN} < 45\%~V_{CC}$ ), the amplifier is disabled. Once the enable pin is taken above the threshold voltage ( $V_{EN} = 60\%~V_{CC}$ ), the amplifier will turn on. In the event the enable pin is not connected, the amplifier will remain on by default

Figure 35. Small Signal Transient Response with Large Capacitive Load

Figure 36. Small Signal Transient Response with Large Capacitive Load and Isolation Resistor.

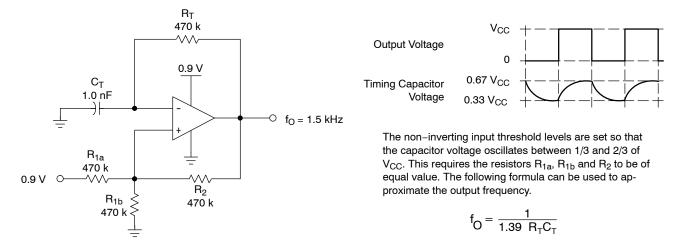

Figure 37. 0.9 V Square Wave Oscillator

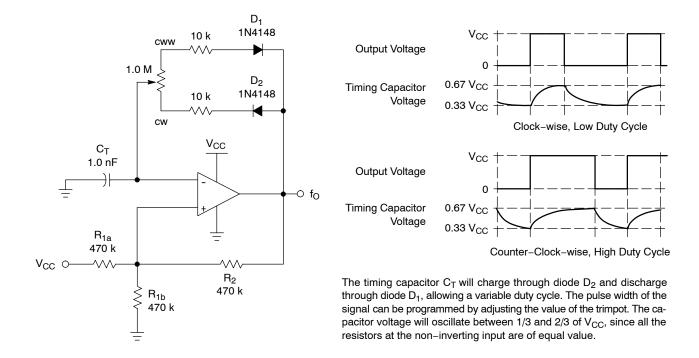

Figure 38. Variable Duty Cycle Pulse Generator

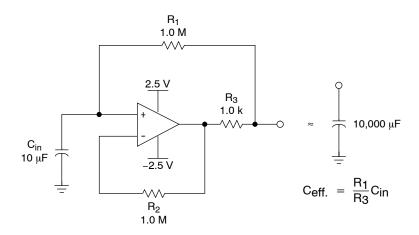

Figure 39. Positive Capacitance Multiplier

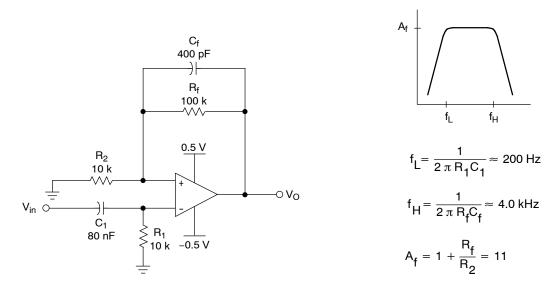

Figure 40. 1.0 V Voiceband Filter

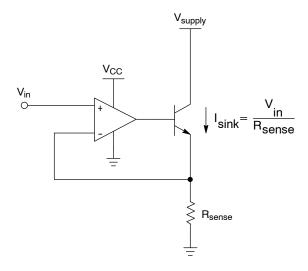

Figure 41. High Compliance Current Sink

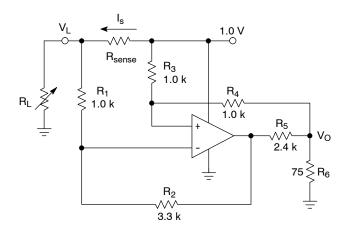

| Is     | v <sub>o</sub> |

|--------|----------------|

| 435 mA | 34.7 mV        |

| 212 mA | 36.9 mV        |

For best performance, use low tolerance resistors.

Figure 42. High Side Current Sense

#### **ORDERING INFORMATION1**

| Device        | Marking | Package             | Shipping <sup>†</sup> |

|---------------|---------|---------------------|-----------------------|

| NCS2002SN1T1G | Р       | TSOP-6<br>(Pb-Free) |                       |

| NCS2002SN2T1G | Q       |                     | 3000 / Tape & Reel    |

| NCV2002SN1T1G | Р       |                     | 3000 / Tape & Neel    |

| NCV2002SN2T1G | Q       |                     |                       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>\*</sup>NCV2002: T<sub>low</sub> = -40°C, T<sub>high</sub> = +125°C. Guaranteed by design. NCV prefix is for automotive and other applications requiring site and change control. AEC-Q100 Qualified and PPAP Capable.

#### TSOP-6 CASE 318G-02 **ISSUE V**

12

C SEATING PLANE

**DATE 12 JUN 2012**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM

- LEAD THIORNESS INCLUDES LEAD FINISH. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL. DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSIONS D

- AND E1 ARE DETERMINED AT DATUM H.

PIN ONE INDICATOR MUST BE LOCATED IN THE INDICATED ZONE.

|     | MILLIMETERS |      |      |  |

|-----|-------------|------|------|--|

| DIM | MIN         | NOM  | MAX  |  |

| Α   | 0.90        | 1.00 | 1.10 |  |

| A1  | 0.01        | 0.06 | 0.10 |  |

| b   | 0.25        | 0.38 | 0.50 |  |

| С   | 0.10        | 0.18 | 0.26 |  |

| D   | 2.90        | 3.00 | 3.10 |  |

| E   | 2.50        | 2.75 | 3.00 |  |

| E1  | 1.30        | 1.50 | 1.70 |  |

| е   | 0.85        | 0.95 | 1.05 |  |

| L   | 0.20        | 0.40 | 0.60 |  |

| L2  | 0.25 BSC    |      |      |  |

| M   | 00          |      | 100  |  |

**DETAIL Z**

Н

| , , ,                                                                         |                                                                                                            |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| STYLE 1: PIN 1. DRAIN 2. DRAIN 3. GATE 4. SOURCE 5. DRAIN 6. DRAIN            | STYLE 2:<br>PIN 1. EMITTER 2<br>2. BASE 1<br>3. COLLECTOR 1<br>4. EMITTER 1<br>5. BASE 2<br>6. COLLECTOR 2 |

| STYLE 7: PIN 1. COLLECTOR 2. COLLECTOR 3. BASE 4. N/C 5. COLLECTOR 6. EMITTER | STYLE 8: PIN 1. Vbus 2. D(in) 3. D(in)+ 4. D(out)+ 5. D(out) 6. GND                                        |

Δ1

STYLE 13: PIN 1. GATE 1

5. SOURCE 1

2. SOURCE 2

DRAIN 2

3. GATE 2

| 2<br>OR 1 | STYLE 3:<br>PIN 1. ENABLE<br>2. N/C<br>3. R BOOST |  |

|-----------|---------------------------------------------------|--|

| 1         | 4. Vz                                             |  |

|           | 5. V in                                           |  |

| OR 2      | 6. V out                                          |  |

|           |                                                   |  |

|           | CTVI E O:                                         |  |

|         | V in             |

|---------|------------------|

| ъ.      | V out            |

| STYLE 9 | ٥٠               |

|         | LOW VOLTAGE GATE |

|         |                  |

| 2.      | DRAIN            |

| 3       | SOURCE           |

| 6. HIGH VOLTA                         | GE GATE |

|---------------------------------------|---------|

| TYLE 15:<br>PIN 1. ANODE<br>2. SOURCE | STY     |

| 3. GATE<br>4. DRAIN                   |         |

4. DRAIN

| YLE 15:                  |

|--------------------------|

| PIN 1. ANODE             |

| <ol><li>SOURCE</li></ol> |

| <ol><li>GATE</li></ol>   |

| <ol><li>DRAIN</li></ol>  |

| 5. N/C                   |

| 6. CATHODE               |

|                          |

|                          |

STYLE 16: PIN 1. ANODE/CATHODE

FMITTER

CATHODE

COLLECTOR

2. BASE

3.

5. ANODE

| E 10:                     | STYL |

|---------------------------|------|

| 1. D(OUT)+                | PIN  |

| 2. GND                    |      |

| <ol><li>D(OUT)-</li></ol> |      |

| 4. D(IN)-                 |      |

| 5. VBUS                   |      |

| <ol><li>D(IN)+</li></ol>  |      |

LE 11: N 1. SOURCE 1 2. DRAIN 2 DRAIN 2 SOURCE 2 5. GATE 1 6. DRAIN 1/GATE 2

STYLE 17: PIN 1. EMITTER

BASE

CATHODE

COLLECTOR

3 ANODE/CATHODE

3. COLLECTOR 1 4. EMITTER 1

BASE 1 6. COLLECTOR 2

STYLE 12: 2. GROUND 3. I/O 4. I/O 6. I/O

STYLE 6: PIN 1. COLLECTOR 2. COLLECTOR

5. COLLECTOR 6. COLLECTOR

3 BASE 4. EMITTER

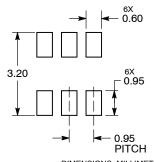

| S       | RECOMMENDED OLDERING FOOTPRI | NT* |

|---------|------------------------------|-----|

| DRAIN 1 | 6. CATHODE/DRAIN             | 6.  |

|         | 0. 0                         | ٠.  |

SOURCE

CATHODE/DRAIN

CATHODE/DRAIN

STYLE 14: PIN 1. ANODE

5.

3. GATE

**DIMENSIONS: MILLIMETERS**

#### **GENERIC** MARKING DIAGRAM\*

XXX = Specific Device Code Α =Assembly Location

Υ = Year

W = Work Week = Pb-Free Package XXX = Specific Device Code M = Date Code

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ", may or may not be present.

| DOCUMENT NUMBER: | 98ASB14888C | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | TSOP-6      |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative