### **ON Semiconductor**

### Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

ON Semiconductor

## FPF2290 Over-Voltage Protection Load Switch

#### **Features**

- Surge Protection

- IEC 61000-4-5: ±100 V

- Selectable Over-Voltage Protection (OVP) with OV1 and OV2 Logic inputs

- 5.9 V ±100 mV

- 10 V ±100 mV

- 14 V ±280 mV

- 23 V ±460 mV

- Over-Temperature Protection (OTP)

- Ultra-Low On-Resistance: Typ. 33 mΩ

- ESD Protection

Human Body Model (HBM): > 2 kV

Charged Device Model (CDM): > 1 kV

IEC 61000-4-2 Air Discharge: > 15 kV

### **Applications**

- Mobile Handsets and Tablets

- Portable Media Players

- MP3 Players

### **Description**

The FPF2290 features a low-RoN internal FET and an operating voltage range of  $2.5\,\mathrm{V}$  to  $23\,\mathrm{V}$ . An internal clamping circuit is capable of shunting surge voltages of  $\pm 100\,\mathrm{V}$ , protecting downstream components and enhancing system robustness. The FPF2290 features over-voltage protection that powers down the internal FET if the input voltage exceeds the OVP threshold. The OVP threshold is selectable via Logic select pins (OV1 and OV2). Over-temperature protection also powers down the device at  $130\,\mathrm{^{\circ}C}$  (typical).

The FPF2290 is available in a fully "green" compliant 1.3 mm × 1.8 mm Wafer-Level Chip-Scale Package (WLCSP) with backside laminate.

#### **Ordering Information**

| Part Number      | Operating Temperature<br>Range | Top Mark | Package                     | Packing<br>Method |

|------------------|--------------------------------|----------|-----------------------------|-------------------|

| FPF2290BUCX-F130 | -40°C – +85°C                  | HR       | 12-Ball, 0.4 mm Pitch WLCSP | Tape & Reel       |

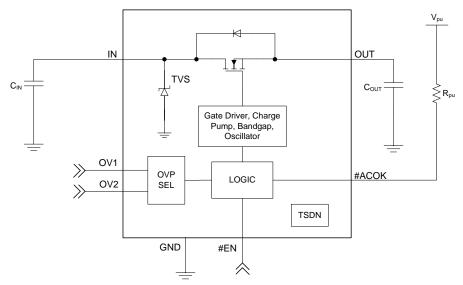

### **Block Diagram**

Functional Block Diagram Figure 1.

#### Note:

1. Setting OV1 and OV2 logic level are recommended before IN is applied.

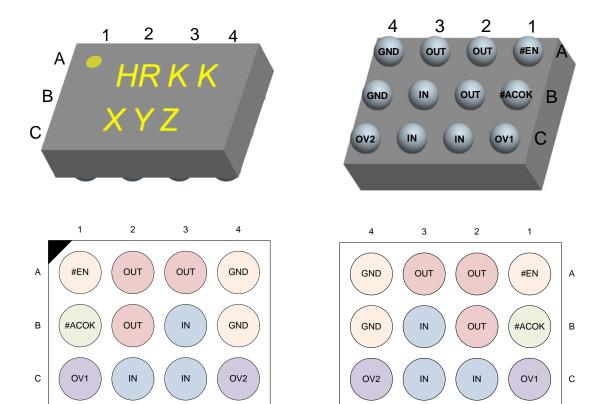

### **Pin Configuration**

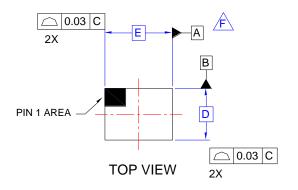

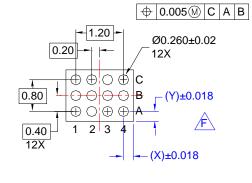

Figure 2. Pin Configuration (Top View)

Figure 3. Pin Configuration (Bottom View)

#### **Pin Definitions**

| Name    | Bump                  | Туре         | Description                                                |  |                                                                                    |  |  |

|---------|-----------------------|--------------|------------------------------------------------------------|--|------------------------------------------------------------------------------------|--|--|

| IN      | B3, C2, C3            | Input/Supply | Switch Input and Device Supply                             |  |                                                                                    |  |  |

| OUT     | A2, A3, B2            | Output       | Sw itch Output to Load                                     |  |                                                                                    |  |  |

| #ACOK   | B1                    | Output       | Pow er Good<br>(Open-Drain Output)                         |  | Hi-Z: V <sub>IN</sub> < V <sub>IN_MIN</sub> OR V <sub>IN</sub> > V <sub>OVLO</sub> |  |  |

| #710011 | D,                    | Catput       |                                                            |  | LOW: Voltage Stable                                                                |  |  |

| #EN     | A1                    | Input        | Device Enable (Active LOW)                                 |  |                                                                                    |  |  |

| OV 1/2  | C1, C4                | Input        | OVLO Selection Input (see Table 1)                         |  |                                                                                    |  |  |

| 01.72   | <b>3.</b> , <b>3.</b> |              | Note: Appy OV1 and OV2 Logic levels before VIN is applied. |  |                                                                                    |  |  |

| GND     | A4, B4                | Supply       | Device Ground                                              |  |                                                                                    |  |  |

Table 1. OVLO Selection

| OV1  | OV2  | OVP Trip Level |

|------|------|----------------|

| LOW  | LOW  | 5.9 V ±100 mV  |

| HIGH | LOW  | 10 V ±100 mV   |

| LOW  | HIGH | 14 V ±280 mV   |

| HIGH | HIGH | 23 V ±460 mV   |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol               | Parameter                                                     | Min.              | Max. | Unit                  |     |  |

|----------------------|---------------------------------------------------------------|-------------------|------|-----------------------|-----|--|

| V <sub>IN</sub>      | V_IN to GND & V_IN to V_OUT = GND or Float                    | -0.3              | 29.0 | V                     |     |  |

| V <sub>OUT</sub>     | V_OUT to GND                                                  |                   | -0.3 | V <sub>IN</sub> + 0.3 | V   |  |

| V <sub>OVn</sub>     | OV1 and OV2 to GND                                            |                   | -0.3 | 6.0                   | V   |  |

| V <sub>EN_ACOK</sub> | Maximum DC Voltage Allowed on #EN or #ACOK Pin                |                   |      | 6                     | V   |  |

| I <sub>IN</sub>      | Switch I/O Current (Continuous)                               |                   |      | 4.5                   | Α   |  |

| t <sub>PD</sub>      | Total Power Dissipation at T <sub>A</sub> = 25°C              |                   | 1.48 | W                     |     |  |

| T <sub>STG</sub>     | Storage Temperature Range                                     | -65               | +150 | °C                    |     |  |

| TJ                   | Maximum Junction Temperature                                  |                   | +150 | °C                    |     |  |

| $T_L$                | Lead Temperature (Soldering, 10 Seconds)                      |                   |      | +260                  | °C  |  |

| ΘЈА                  | Thermal Resistance, Junction-to-Ambient (2) (1-in. 2 Pad of 2 |                   | 84.1 | °C/W                  |     |  |

|                      | IFC 64000 4 2 System Loyal FCD                                | Air Discharge     | 15   |                       |     |  |

| ESD                  | IEC 61000-4-2 System Level ESD                                | Contact Discharge | 8    |                       | 147 |  |

| ESD                  | Human Body Model, ANSI/ESDA/JEDEC JS-001-2012                 | All Pins          | 2    |                       | kV  |  |

|                      | Charged Device Model, JESD22-C101 All Pins                    |                   |      |                       |     |  |

| Surge                | IEC 61000-4-5, Surge Protection V <sub>IN</sub>               |                   | ±100 |                       | V   |  |

#### Note:

2. Measured using 2S2P JEDEC std. PCB.

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. ON Semiconductor does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol          | Parameter             |     | Max. | Unit |

|-----------------|-----------------------|-----|------|------|

| V <sub>IN</sub> | Supply Voltage        | 2.5 | 23.0 | V    |

| T <sub>A</sub>  | Operating Temperature | -40 | +85  | °C   |

### **Electrical Characteristics**

$T_A$  = -40°C to 85°C,  $V_{IN}$  = 2.5 to 23 V, unless otherwise indicated. Typical values are  $V_{IN}$  = 5.0 V,  $I_{IN}$  ≤ 3 A,  $C_{IN}$  = 0.1  $\mu F$  and  $T_A$  = 25°C.

| Symbol                | Parameter                                           | Conditions                                                                                               |                            | Min.  | Тур.  | Max.   | Unit |

|-----------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------|-------|-------|--------|------|

| Basic Operat          | tion                                                |                                                                                                          |                            |       | •     |        |      |

| V <sub>IN_CLAMP</sub> | Input Clamping Voltage                              | I <sub>IN</sub> = 10 mA                                                                                  |                            |       | 35    |        | V    |

| lQ                    | Input Quiescent Current                             | V <sub>IN</sub> = 5 V, #EN = 0 V                                                                         |                            |       | 80    | 115    | μΑ   |

| l <sub>IN_Q</sub>     | OVLO Supply Current                                 | OV1 = LOW<br>V <sub>IN</sub> = 6.5 V,                                                                    | V, OV2 = LOW<br>VOUT = 0 V |       | 63    | 90     | μA   |

|                       |                                                     | V <sub>IN</sub> Rising                                                                                   | OV1 = LOW,                 | 5.80  | 5.90  | 6.00   | -    |

|                       |                                                     | V <sub>IN</sub> Falling                                                                                  | OV2 = LOW                  | 5.75  |       |        |      |

|                       |                                                     | V <sub>IN</sub> Rising                                                                                   | OV1 = HIGH,                | 9.90  | 10.00 | 10.10  |      |

| M                     | Over Veltana Tria Level                             | V <sub>IN</sub> Falling                                                                                  | OV2 = LOW                  | 9.85  |       |        | ,,   |

| V <sub>IN_OVLO</sub>  | Over-Voltage Trip Level                             | V <sub>IN</sub> Rising                                                                                   | OV1 = LOW,                 | 13.72 | 14.0  | 14.28  | V    |

|                       |                                                     | V <sub>IN</sub> Falling                                                                                  | OV2 = HIGH                 | 13.52 |       |        | -    |

|                       |                                                     | V <sub>IN</sub> Rising                                                                                   | OV1 = HIGH,                | 22.54 | 23.0  | 23.46  |      |

|                       |                                                     | V <sub>IN</sub> Falling                                                                                  | OV2 = HIGH                 | 22.34 |       |        |      |

| Ron                   | Resistance from V <sub>IN</sub> to V <sub>OUT</sub> | V <sub>IN</sub> = 5 V, I <sub>OUT</sub> = 1 A, T <sub>A</sub> = 25°C                                     |                            |       | 33    | 40     | mΩ   |

| C <sub>OUT</sub>      | OUT Load Capacitance <sup>(3)</sup>                 | V <sub>IN</sub> = 5 V                                                                                    |                            | 0.1   |       | 1000.0 | μF   |

| T <sub>SDN</sub>      | Thermal Shutdow n <sup>(3)</sup>                    |                                                                                                          |                            |       | 130   |        | °C   |

| T <sub>SDN_HYS</sub>  | Thermal Shutdown Hysteresis (3)                     |                                                                                                          |                            |       | 20    |        | °C   |

| Digital Signa         | ls                                                  |                                                                                                          |                            |       |       |        | •    |

| V <sub>OL</sub>       | #ACOK Output Low Voltage                            | I <sub>SINK</sub> = 1 mA                                                                                 |                            |       |       | 0.4    | V    |

| Іасок                 | #ACOK Leakage Current                               | V <sub>I/O</sub> = 3.0 V, #ACOK Deasserted                                                               |                            |       |       | 0.5    | μΑ   |

| V <sub>IH</sub>       | Input HIGH Voltage (#EN, OVx)                       | V <sub>IN</sub> = 2.5 V to V <sub>OVLO</sub>                                                             |                            | 1.2   |       |        | V    |

| V <sub>IL</sub>       | Input LOW Voltage (#EN, OVx)                        | V <sub>IN</sub> = 2.5 V to V <sub>OVLO</sub>                                                             |                            |       |       | 0.5    | V    |

| I <sub>IN</sub>       | Input Leakage Current (#EN, OVx)                    | V <sub>IN</sub> = 5.0 V, V <sub>OUT</sub> = Float                                                        |                            |       |       | 1.0    | μA   |

| Timing Chara          | acteristics                                         | •                                                                                                        |                            |       | •     |        |      |

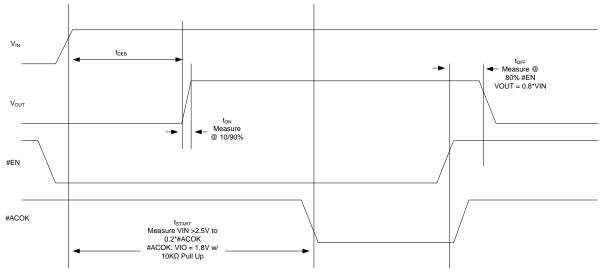

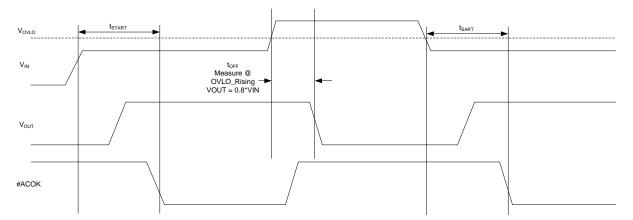

| t <sub>DEB</sub>      | Debounce Time                                       | Time from 2.5 V < $V_{IN}$ < $V_{IN\_OVLO}$ to $V_{OUT}$ = 0.1 x $V_{IN}$                                |                            | 10    | 15    | 20     | ms   |

| tstart                | Soft-Start Time                                     | Time from $V_{IN} = V_{IN\_min}$ to 0.2 × #ACOK, $V_{IO} = 1.8$ V w ith 10 k $\Omega$ Pull-up Resistor   |                            | 20    | 30    | 40     | ms   |

| ton                   | Sw itch Turn-On Time                                | $R_L$ = 100 $\Omega$ , $C_L$ = 22 $\mu$ F, $V_{OUT}$ from 0.1 $\times$ $V_{IN}$ to 0.9 $\times$ $V_{IN}$ |                            | 1     | 3     | 5      | ms   |

| toff                  | Sw itch Turn-Off Time <sup>(3)</sup>                | $R_L = 100 \ \Omega, \ C_L = 0 \ \mu F, \ V_{IN} > V_{OVLO}$ to $V_{OUT} = 0.8 \times V_{IN}$            |                            |       |       | 150    | ns   |

#### Note:

3. Guaranteed by characterization and design.

### **Timing Diagrams**

Figure 4. Timing for Power Up and Normal Operation

Figure 5. Timing for OVLO Trip

### **Product-Specific Dimensions**

| D              | Е              | Х             | Υ             |

|----------------|----------------|---------------|---------------|

| 1288 μm ±30 μm | 1828 μm ±30 μm | 314 μm ±18 μm | 244 μm ±18 μm |

### **Physical Dimensions**

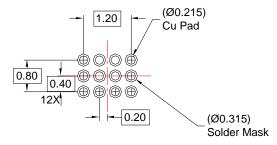

# RECOMMENDED LAND PATTERN (NSMD PAD TYPE)

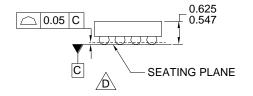

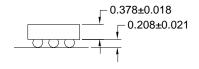

SIDE VIEWS

#### NOTES:

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 2009.

- D. DATUM C IS DEFINED BY THE SPHERICAL CROWNS OF THE BALLS.

- E.PACKAGE NOMINAL HEIGHT IS 586 MICRONS ±39 MICRONS (547-625 MICRONS).

F. FOR DIMENSIONS D, E, X, AND Y SEE PRODUCT DATASHEET.

G. DRAWING FILENAME: MKT-UC012ZCrev2.

H. ON SEMICONDUCTOR RECOMMENDS THAT LANDS IN THE LANDPATTERN ARE AT LEAST .215MM DIAMETER AS MEASURED AT THE BOTTOM OF THE LAND, NOT THE TOP EDGE.

**BOTTOM VIEW**

Figure 6. 12-Ball, 3x4 Array, 0.4 mm Pitch, Wafer-Level Chip-Scale Package (WLCSP)

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsi

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA **Phone**: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada.

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative