# High Voltage, High and Low Side Driver

The NCP5109 is a high voltage gate driver IC providing two outputs for direct drive of 2 N-channel power MOSFETs or IGBTs arranged in a half-bridge configuration version B or any other high-side + low-side configuration version A.

It uses the bootstrap technique to ensure a proper drive of the high–side power switch. The driver works with 2 independent inputs.

#### Features

- High Voltage Range: Up to 200 V

- dV/dt Immunity ±50 V/nsec

- Negative Current Injection Characterized Over the Temperature Range

- Gate Drive Supply Range from 10 V to 20 V

- High and Low Drive Outputs

- Output Source / Sink Current Capability 250 mA / 500 mA

- 3.3 V and 5 V Input Logic Compatible

- Up to V<sub>CC</sub> Swing on Input Pins

- Extended Allowable Negative Bridge Pin Voltage Swing to -10 V for Signal Propagation

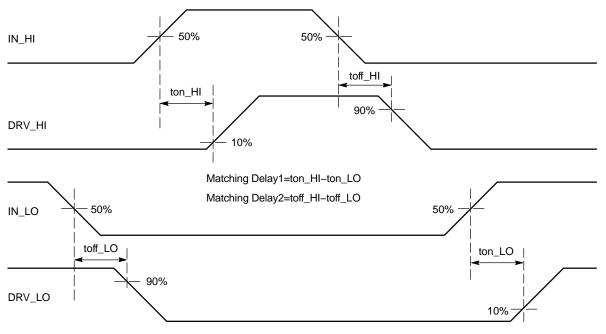

- Matched Propagation Delays Between Both Channels

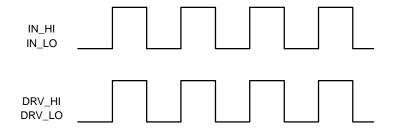

- Outputs in Phase with the Inputs

- Independent Logic Inputs to Accommodate All Topologies (Version A)

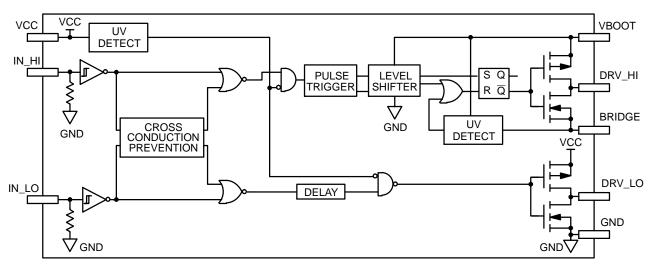

- Cross Conduction Protection with 100 ns Internal Fixed Dead Time (Version B)

- Under V<sub>CC</sub> LockOut (UVLO) for Both Channels

- Pin-to-Pin Compatible with Industry Standards

- These are Pb–Free Devices

#### **Typical Applications**

- Half-Bridge Power Converters

- Any Complementary Drive Converters (Asymmetrical Half–Bridge, Active Clamp) (A Version Only).

- Full-Bridge Converters

# **ON Semiconductor®**

www.onsemi.com

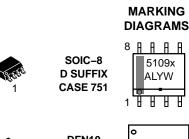

5109 = Specific Device Code

- x = A or B version

- A = Assembly Location

- L = Wafer Lot

- Y = Year

- W = Work Week

- = Pb–Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 16 of this data sheet.

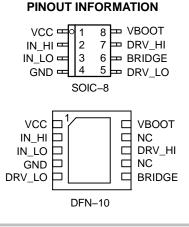

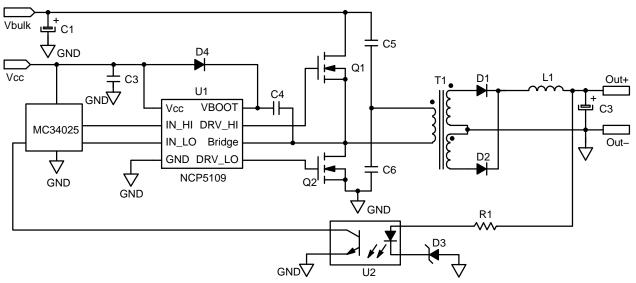

Figure 1. Typical Application Resonant Converter (LLC type)

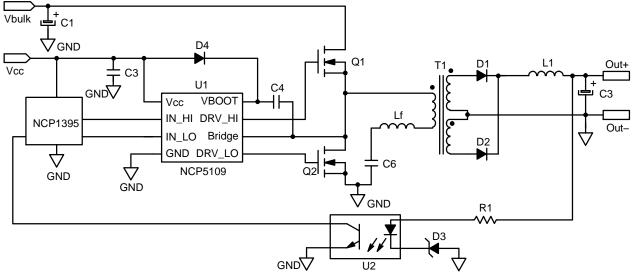

Figure 2. Typical Application Half Bridge Converter

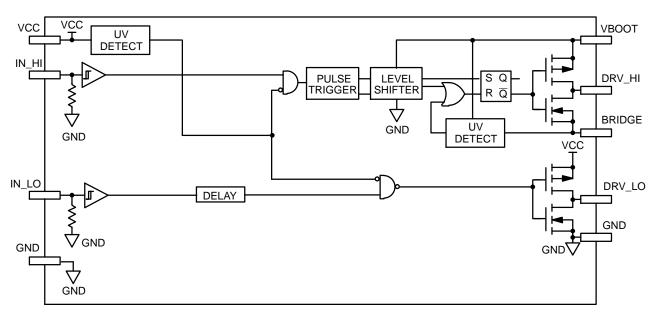

Figure 3. Detailed Block Diagram: Version A

Figure 4. Detailed Block Diagram: Version B

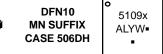

| Pin Name          | Description                                          |  |  |  |

|-------------------|------------------------------------------------------|--|--|--|

| IN_HI             | Logic Input for High Side Driver Output in Phase     |  |  |  |

| IN_LO             | Logic Input for Low Side Driver Output in Phase      |  |  |  |

| GND               | Ground                                               |  |  |  |

| DRV_LO            | Low Side Gate Drive Output                           |  |  |  |

| V <sub>CC</sub>   | Low Side and Main Power Supply                       |  |  |  |

| V <sub>BOOT</sub> | Bootstrap Power Supply                               |  |  |  |

| DRV_HI            | High Side Gate Drive Output                          |  |  |  |

| BRIDGE            | Bootstrap Return or High Side Floating Supply Return |  |  |  |

| NC                | Removed for creepage distance (DFN package only)     |  |  |  |

#### **PIN DESCRIPTION**

#### MAXIMUM RATINGS

| Rating                    | Symbol                                                                                                                                                                                                     | Value                                                   | Unit |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|

| V <sub>CC</sub>           | Main power supply voltage                                                                                                                                                                                  | -0.3 to 20                                              | V    |

| V <sub>CC_transient</sub> | Main transient power supply voltage:<br>IV <sub>CC_max</sub> = 5 mA during 10 ms                                                                                                                           | 23                                                      | V    |

| V <sub>BRIDGE</sub>       | VHV: High Voltage BRIDGE pin                                                                                                                                                                               | -1 to 200                                               | V    |

| V <sub>BRIDGE</sub>       | Allowable Negative Bridge Pin Voltage for IN_LO Signal Propagation to DRV_LO (see characterization curves for detailed results)                                                                            | -10                                                     | V    |

| $V_{BOOT-}V_{BRIDGE}$     | VHV: Floating supply voltage                                                                                                                                                                               | -0.3 to 20                                              | V    |

| V <sub>DRV_HI</sub>       | VHV: High side output voltage                                                                                                                                                                              | V <sub>BRIDGE</sub> – 0.3 to<br>V <sub>BOOT</sub> + 0.3 | V    |

| V <sub>DRV_LO</sub>       | Low side output voltage                                                                                                                                                                                    | -0.3 to V <sub>CC</sub> + 0.3                           | V    |

| dV <sub>BRIDGE</sub> /dt  | Allowable output slew rate                                                                                                                                                                                 | 50                                                      | V/ns |

| V <sub>IN_XX</sub>        | Inputs IN_HI, IN_LO                                                                                                                                                                                        | -1.0 to V <sub>CC</sub> + 0.3                           | V    |

|                           | ESD Capability:<br>– HBM model (all pins except pins 6–7–8 in 8 pins<br>package or 11–12–13 in 14 pins package)                                                                                            | 2                                                       | kV   |

|                           | <ul> <li>Machine model (all pins except pins 6–7–8 in 8 pins<br/>package or 11–12–13 in 14 pins package)</li> </ul>                                                                                        | 200                                                     | V    |

|                           | Latch up capability per JEDEC JESD78                                                                                                                                                                       |                                                         |      |

| $R_{	extsf{	heta}JA}$     | Power dissipation and Thermal characteristics<br>SO–8: Thermal Resistance, Junction–to–Air<br>DFN10 3x3: Thermal Resistance, Junction–to–Ambient 1 Oz Cu<br>50 mm <sup>2</sup> Printed Circuit Copper Clad | 178<br>172                                              | °C/W |

| T <sub>ST</sub>           | Storage Temperature Range                                                                                                                                                                                  | -55 to +150                                             | °C   |

| T <sub>J_max</sub>        | Maximum Operating Junction Temperature                                                                                                                                                                     | +150                                                    | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

|                                                                                                           |                         | T <sub>J</sub> –40°C to 125°C |     |     |       |

|-----------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------|-----|-----|-------|

| Rating                                                                                                    | Symbol                  | Min                           | Тур | Max | Units |

| OUTPUT SECTION                                                                                            |                         |                               |     |     |       |

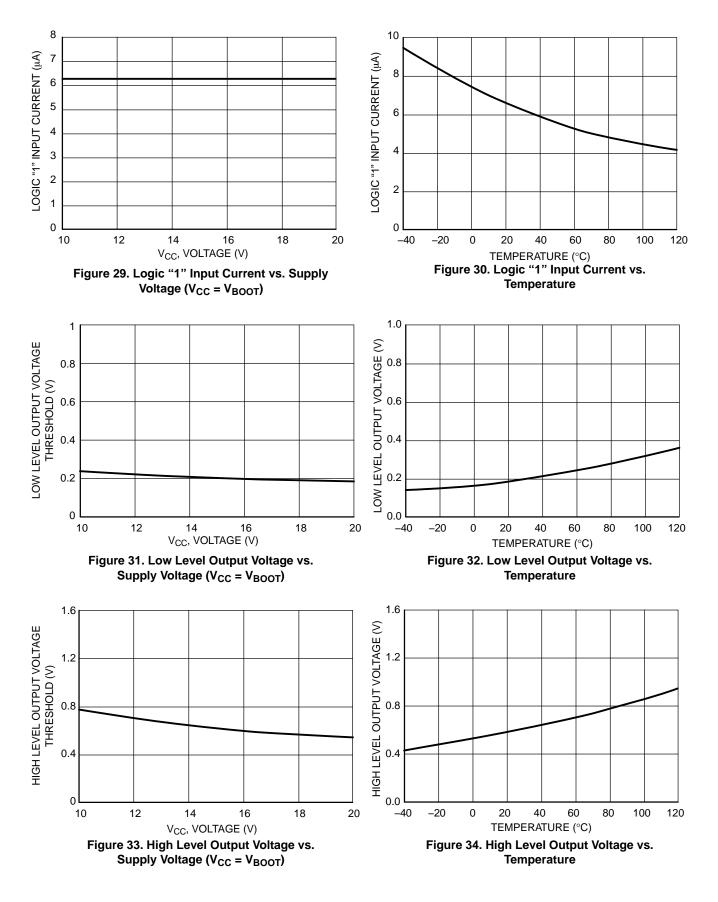

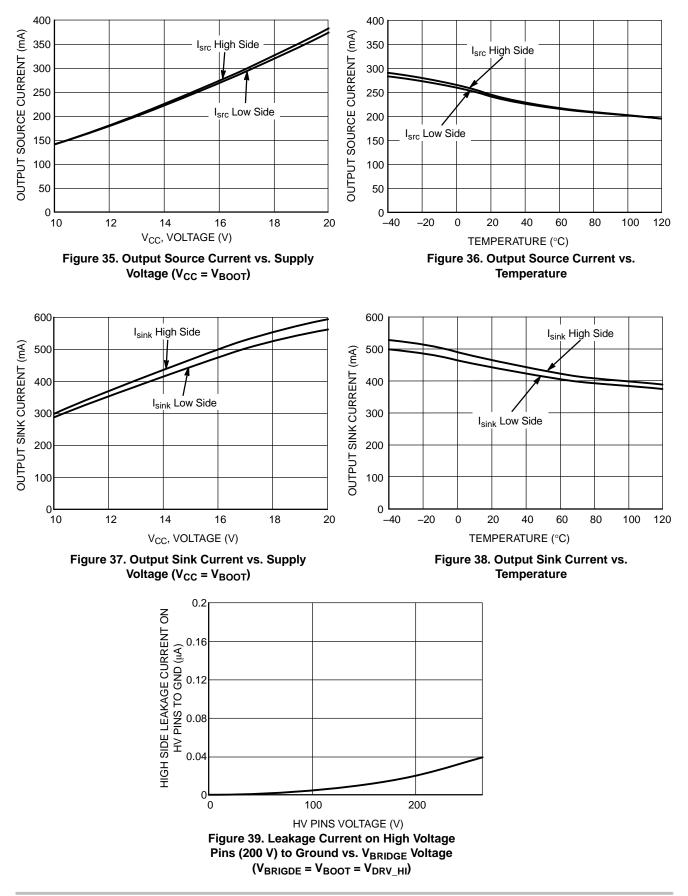

| Output high short circuit pulsed current V_{DRV} = 0 V, PW $\leq$ 10 $\mu$ s (Note 1)                     | I <sub>DRVsource</sub>  | _                             | 250 | _   | mA    |

| Output low short circuit pulsed current V <sub>DRV</sub> = V <sub>CC</sub> , PW $\leq$ 10 µs (Note 1)     | I <sub>DRVsink</sub>    | _                             | 500 | _   | mA    |

| Output resistor (Typical value @ 25°C) Source                                                             | R <sub>OH</sub>         | -                             | 30  | 60  | Ω     |

| Output resistor (Typical value @ 25°C) Sink                                                               | R <sub>OL</sub>         | -                             | 10  | 20  | Ω     |

| High level output voltage, V <sub>BIAS</sub> -V <sub>DRV_XX</sub> @ I <sub>DRV_XX</sub> = 20 mA           | V <sub>DRV_H</sub>      | -                             | 0.7 | 1.6 | V     |

| Low level output voltage V <sub>DRV_XX</sub> @ I <sub>DRV_XX</sub> = 20 mA                                | V <sub>DRV_L</sub>      | -                             | 0.2 | 0.6 | V     |

| DYNAMIC OUTPUT SECTION                                                                                    |                         |                               |     |     |       |

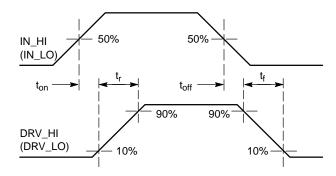

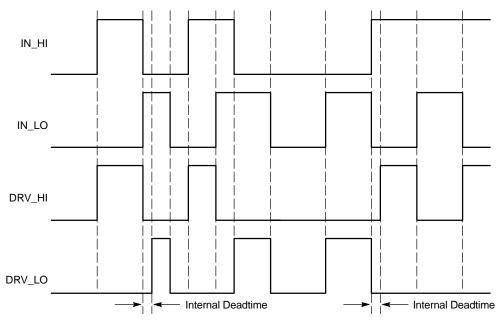

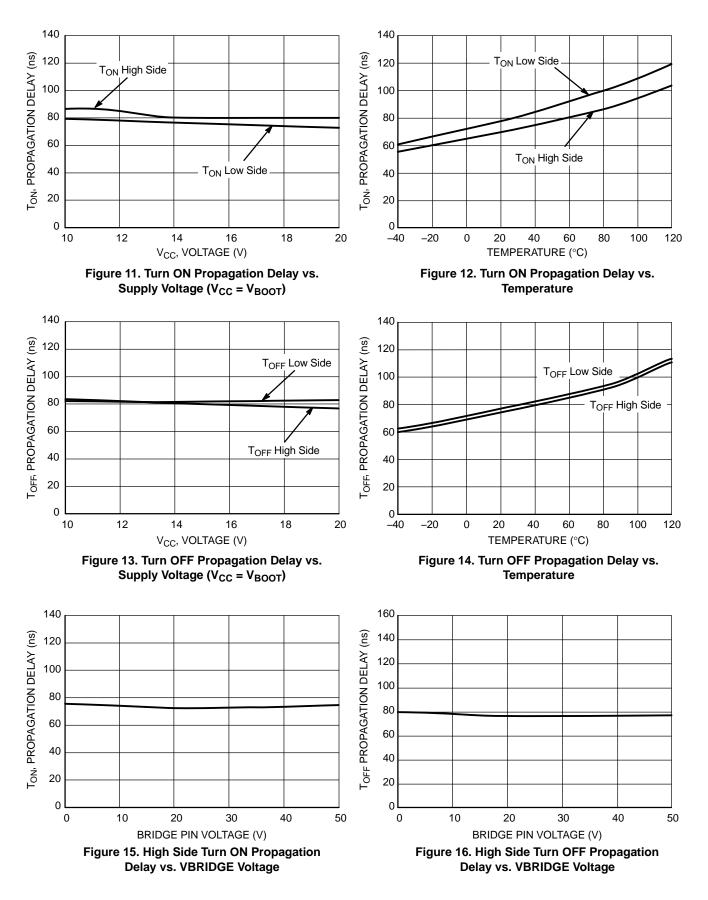

| Turn-on propagation delay (Vbridge = 0 V)                                                                 | t <sub>ON</sub>         | -                             | 100 | 170 | ns    |

| Turn–off propagation delay (Vbridge = 0 V or 50 V) (Note 2)                                               | t <sub>OFF</sub>        | -                             | 100 | 170 | ns    |

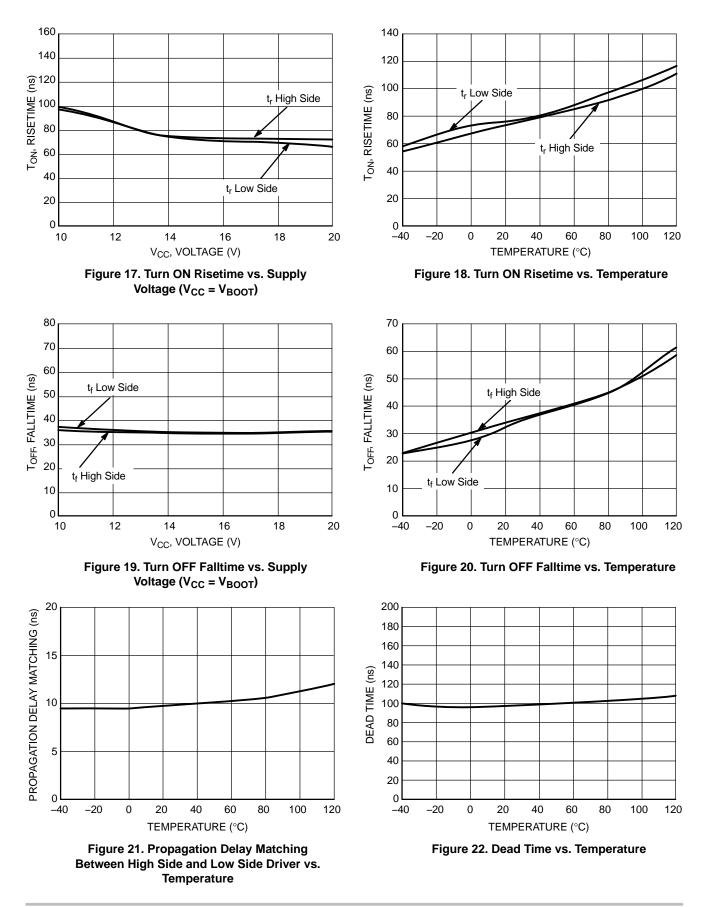

| Output voltage rise time (from 10% to 90% @ $V_{CC}$ = 15 V) with 1 nF load                               | tr                      | -                             | 85  | 160 | ns    |

| Output voltage fall time (from 90% to 10% $@V_{CC} = 15 \text{ V}$ ) with 1 nF load                       | tf                      | -                             | 35  | 75  | ns    |

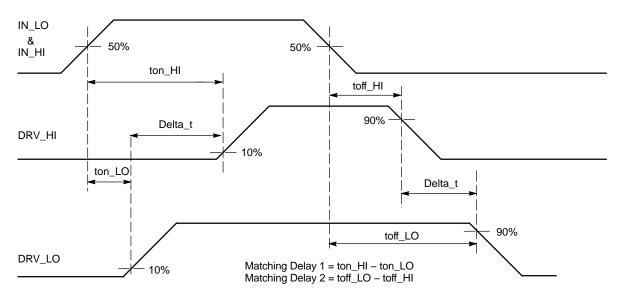

| Propagation delay matching between the High side and the Low side @ 25°C (Note 3)                         | Δt                      | -                             | 20  | 35  | ns    |

| Internal fixed dead time (only valid for B version) (Note 4)                                              | DT                      | 65                            | 100 | 190 | ns    |

| Minimum input width that changes the output                                                               | t <sub>PW1</sub>        | _                             | _   | 50  | ns    |

| Maximum input width that does not change the output SOIC-8 DFN10                                          | t <sub>PW2</sub>        | 20<br>15                      |     | -   | ns    |

| INPUT SECTION                                                                                             |                         |                               |     |     |       |

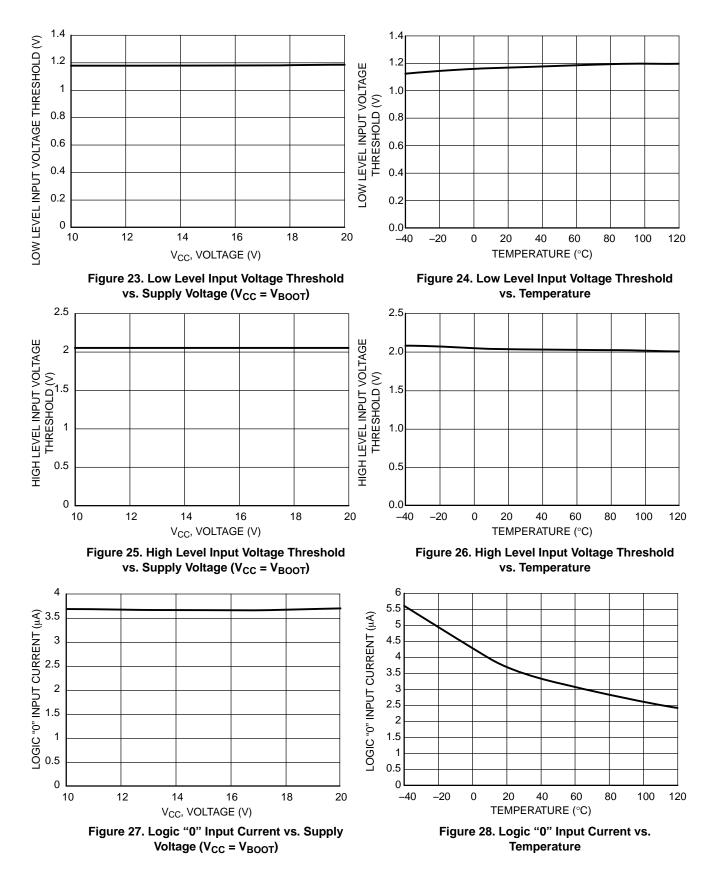

| Low level input voltage threshold                                                                         | V <sub>IN</sub>         | -                             | -   | 0.8 | V     |

| Input pull–down resistor (V <sub>IN</sub> < 0.5 V)                                                        | R <sub>IN</sub>         | -                             | 200 | -   | kΩ    |

| High level input voltage threshold                                                                        | V <sub>IN</sub>         | 2.3                           | -   | -   | V     |

| Logic "1" input bias current @ $V_{IN_XX} = 5 V$ @ $25^{\circ}C$                                          | I <sub>IN+</sub>        | -                             | 5   | 25  | μΑ    |

| Logic "0" input bias current @ V <sub>IN_XX</sub> = 0 V @ 25°C                                            | I <sub>IN-</sub>        | -                             | -   | 2.0 | μA    |

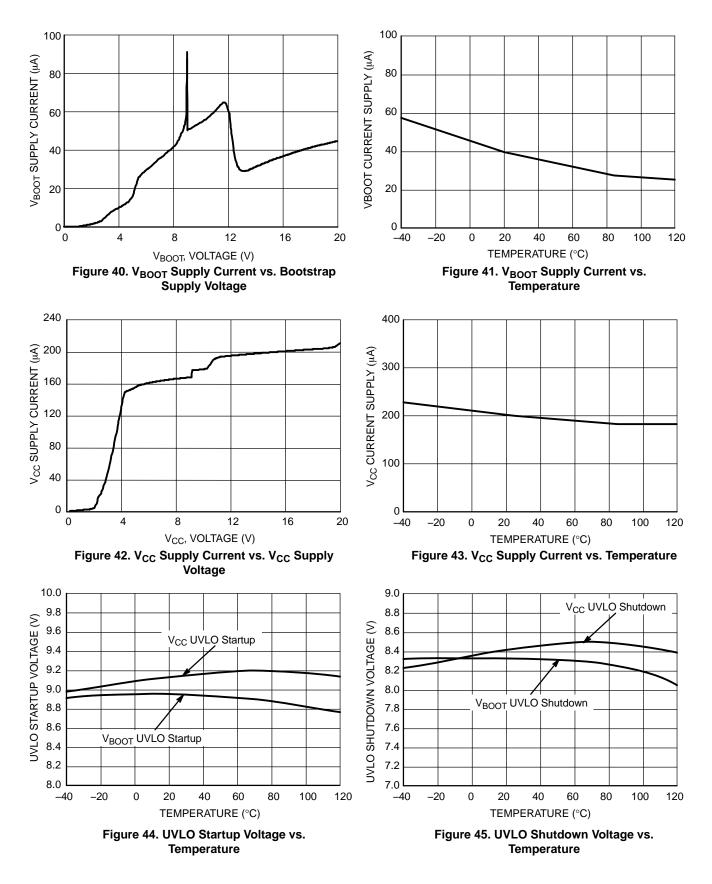

| SUPPLY SECTION                                                                                            |                         |                               |     |     |       |

| V <sub>CC</sub> UV Start-up voltage threshold                                                             | V <sub>CC</sub> _stup   | 8.0                           | 8.9 | 9.9 | V     |

| V <sub>CC</sub> UV Shut–down voltage threshold                                                            | V <sub>CC</sub> _shtdwn | 7.3                           | 8.2 | 9.1 | V     |

| Hysteresis on V <sub>CC</sub>                                                                             | V <sub>CC</sub> _hyst   | 0.3                           | 0.7 | -   | V     |

| Vboot Start–up voltage threshold reference to bridge pin<br>(Vboot_stup = Vboot – Vbridge)                | Vboot_stup              | 8.0                           | 8.9 | 9.9 | V     |

| Vboot UV Shut-down voltage threshold                                                                      | Vboot_shtdwn            | 7.3                           | 8.2 | 9.1 | V     |

| Hysteresis on Vboot                                                                                       | Vboot_hyst              | 0.3                           | 0.7 | _   | V     |

| Leakage current on high voltage pins to GND<br>(V <sub>BOOT</sub> = V <sub>BRIDGE</sub> = DRV_HI = 200 V) | I <sub>HV_LEAK</sub>    | -                             | 5   | 40  | μΑ    |

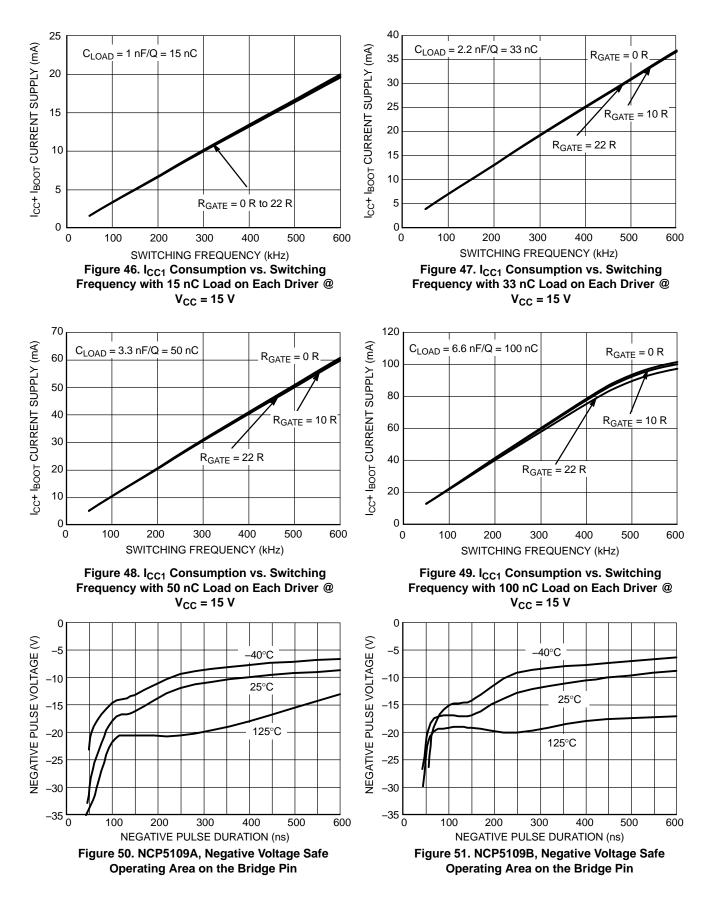

| Consumption in active mode ( $V_{CC}$ = Vboot, fsw = 100 kHz and 1 nF load on both driver outputs)        | ICC1                    | -                             | 4   | 5   | mA    |

| Consumption in inhibition mode (V <sub>CC</sub> = Vboot)                                                  | ICC2                    | -                             | 250 | 400 | μA    |

| V <sub>CC</sub> current consumption in inhibition mode                                                    | ICC3                    | -                             | 200 | -   | μA    |

| Vboot current consumption in inhibition mode                                                              | ICC4                    | _                             | 50  | _   | μA    |

ELECTRICAL CHARACTERISTIC (Vcc = Vhoot = 15 V. VcND = Vhoted a, -40°C < T | < 125°C, Outputs loaded with 1 nF)

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Parameter guaranteed by design.

Turn-off propagation delay @ Vbridge = 200 V is guaranteed by design.

See characterization curve for ∆t parameters variation on the full range temperature.

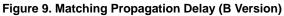

Version B integrates a dead time in order to prevent any cross conduction between DRV\_HI and DRV\_LO. See timing diagram of Figure 10.

5. Timing diagram definition see: Figure 7, Figure 8 and Figure 9.

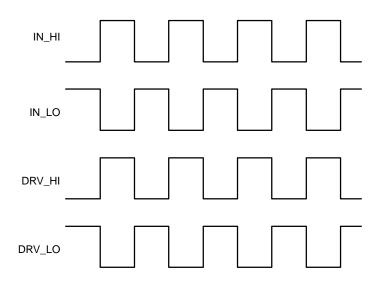

Figure 5. Input/Output Timing Diagram (A Version)

Figure 6. Input/Output Timing Diagram (B Version)

Figure 7. Propagation Delay and Rise / Fall Time Definition

Figure 10. Input/Output Cross Conduction Output Protection Timing Diagram (B Version)

#### APPLICATION INFORMATION

Summary:

follows:

IN F

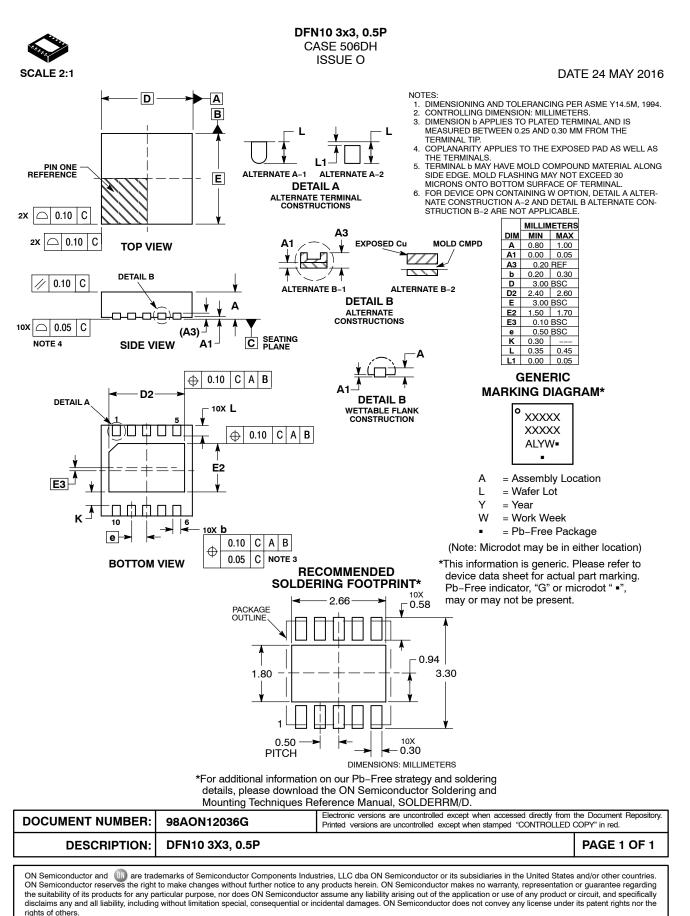

#### **Negative Voltage Safe Operating Area**

When the driver is used in a half bridge configuration, it is possible to see negative voltage appearing on the bridge pin (pin 6) during the power MOSFETs transitions. When the high-side MOSFET is switched off, the body diode of the low-side MOSFET starts to conduct. The negative voltage applied to the bridge pin thus corresponds to the forward voltage of the body diode. However, as pcb copper tracks and wire bonding introduce stray elements (inductance and capacitor), the maximum negative voltage of the bridge pin will combine the forward voltage and the oscillations created by the parasitic elements. As any CMOS device, the deep negative voltage of a selected pin can inject carriers into the substrate, leading to an erratic behavior of the concerned component. ON Semiconductor provides characterization data of its half-bridge driver to show the maximum negative voltage the driver can safely operate with. To prevent the negative injection, it is the designer duty to verify that the amount of negative voltage pertinent to his/her application does not exceed the characterization curve we provide, including some safety margin.

In order to estimate the maximum negative voltage accepted by the driver, this parameter has been characterized over full the temperature range of the component. A test fixture has been developed in which we purposely negatively bias the bridge pin during the freewheel period of a buck converter. When the upper gate voltage shows signs of an erratic behavior, we consider the limit has been reached.

Figure 50 (or 51), illustrates the negative voltage safe operating area. Its interpretation is as follows: assume a negative 10 V pulse featuring a 100 ns width is applied on the bridge pin, the driver will work correctly over the whole die temperature range. Should the pulse swing to -20 V, keeping the same width of 100 ns, the driver will not work properly or will be damaged for temperatures below 125°C.

# IN IO IN\_LO 0.1 GND

Figure 52. R1 and D1 Improves the Robustness of the Driver

• If the negative pulse characteristic (negative voltage

level & pulse width) is above the curves the driver

• If the negative pulse characteristic (negative voltage

level & pulse width) is below one or all curves the

Note, each curve of the Figure 50 (or 51) represents the

If in the application the bridge pin is too close of the safe

operating limit, it is possible to limit the negative voltage

to the bridge pin by inserting one resistor and one diode as

D2

MUR160

VBOOT

DRV\_HI

BRIDGE

DRV I O

D1

**MUR160**

Vbulk

M1

M2

0

C1

10R

100n

negative voltage and width level where the driver starts to

driver will NOT run in safe operating area.

fail at the corresponding die temperature.

U1

vcc

IN\_HI

NCP5109A

runs in safe operating area.

Vcc

R1 and D1 should be placed as close as possible of the driver. D1 should be connected directly between the bridge pin (pin 6) and the ground pin (pin 4). By this way the negative voltage applied to the bridge pin will be limited by D1 and R1 and will prevent any wrong behavior.

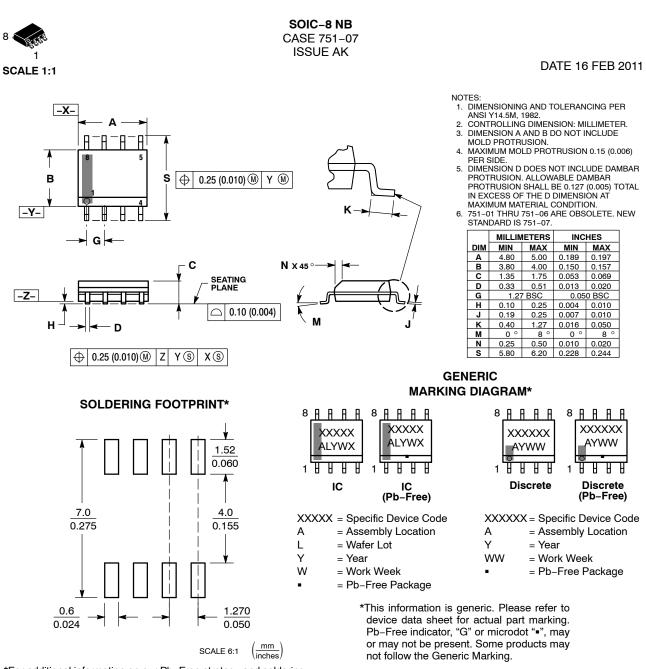

| Device        | Package          | Shipping <sup>†</sup> |

|---------------|------------------|-----------------------|

| NCP5109ADR2G  | SOIC-8 (Pb-Free) | 2500 / Tape & Reel    |

| NCP5109BDR2G  | SOIC-8 (Pb-Free) | 2500 / Tape & Reel    |

| NCP5109AMNTWG | DFN10 (Pb-Free)  | 3000 / Tape & Reel    |

| NCP5109BMNTWG | DFN10 (Pb-Free)  | 3000 / Tape & Reel    |

#### ORDERING INFORMATION

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98ASB42564B  | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I: SOIC-8 NB |                                                                                                                                                                                     | PAGE 1 OF 2 |  |  |  |

| ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights or the |              |                                                                                                                                                                                     |             |  |  |  |

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR 3. 4. EMITTER EMITTER 5. BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: CATHODE 1 PIN 1. 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: PIN 1. GROUND BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE P-SOURCE 3 P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE 2. ANODE SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC COMMON CATHODE/VCC 3 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 COMMON ANODE/GND 8. STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. 4. DRAIN, #2 GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 DRAIN 1 7. 8. **MIRROR 1** STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. LINE 1 OUT 8. STYLE 27: PIN 1. ILIMIT 2 OVI 0 UVLO З. 4. INPUT+ 5. SOURCE SOURCE 6. SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: ANODE ANODE PIN 1. 2. ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE #2 3. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. 4. GATE 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE 2. EMITTER 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98ASB42564B         | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | N: SOIC-8 NB PAGE 2 |                                                                                                                                                                                     | PAGE 2 OF 2 |  |  |

| ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |                     |                                                                                                                                                                                     |             |  |  |

SOURCE 1/DRAIN 2

7.

8. GATE 1

7.

8

rights of others

COLLECTOR, #1

COLLECTOR, #1

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor date sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use a a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor houteds for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

ON Semiconductor Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative