# **Current Mode PWM Controller**

## **GENERAL DESCRIPTION**

HG2269 is a highly integrated current mode PWM control IC optimized for high performance, low standby power and cost effective offline flyback converter applications.

PWM switching frequency at normal operation is externally programmable and trimmed to tight range. At no load or light load condition, the IC operates in extended 'burst mode' to minimize switching loss. Lower standby power and higher conversion efficiency is thus achieved.

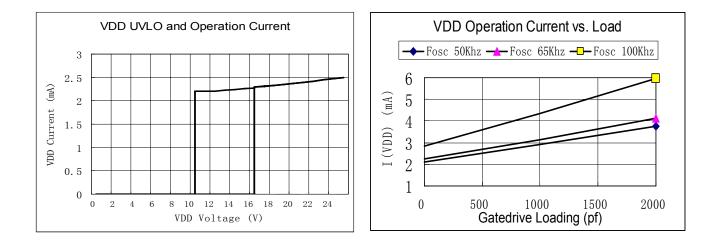

VDD low startup current and low operating current contribute to a reliable power on startup design with HG2269. A large value resistor could thus be used in the startup circuit to minimize the standby power.

The internal slope compensation improves system large signal stability and reduces the possible subharmonic oscillation at high PWM duty cycle output. Leading-edge blanking on current sense input removes the signal glitch due to snubber circuit diode reverse recovery. This greatly helps to reduce the external component count and system cost in application.

HG2269 offers complete pr otection coverage with automatic self-recovery feature including Cycle-by-Cycle current limiting (OCP), over load protection (OLP), over temperature protection (OTP), VDD over voltage protection (OVP) and under voltage lockout (UVLO). The Gate-drive output is clamped at 18V to protect the power MOSFET.

In HG2269, OCP threshold slope is internally optimized to reach constant output power limit over universal AC input range.

Excellent EMI performance is achieved with On-Bright proprietary frequency shuffling technique together with soft switching control at the totem pole gate drive output. The tone energy at below 20KHZ is minimized in operation. Consequently, audio noise performance is greatly improved.

HG2269 is offered in both SOP-8 and DIP-8 packages.

## **FEATURES**

- On-Bright Proprietary Frequency Shuffling Technology for Improved EMI Performance

- Extended Burst Mode Control For Improved Efficiency and Minimum Standby Power Design

- Audio Noise Free Operation

- External Programmable PWM Switching Frequency

- Internal Synchronized Slope Compensation

- Low VIN/VDD Startup Current(6.5uA) and Low Operating Current (2.3mA)

- Leading Edge Blanking on Current Sense Input

- Complete Protection Coverage With Auto Self-Recovery

- External Programmable Over Temperature Protection (OTP)

- With or Without On-chip VDD OVP for System OVP

- Under Voltage Lockout with Hysteresis (UVLO)

- Gate Output Maximum Voltage Clamp (18V)

- Line Compensated Cycle-by-Cycle Overcurrent Threshold Setting For Constant Output Current Limiting Over Universal Input Voltage Range (OCP)

- o Over Load Protection. (OLP)

### APPLICATIONS

Offline AC/DC flyback converter for

- Laptop Power Adaptor

- PC/TV/Set-Top Box Power Supplies

- Open-frame SMPS

- Battery Charger

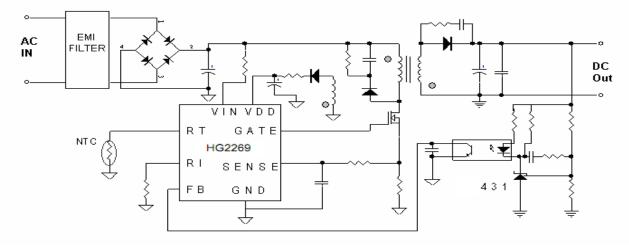

# **TYPICAL APPLICATION**

### **GENERAL INFORMATION**

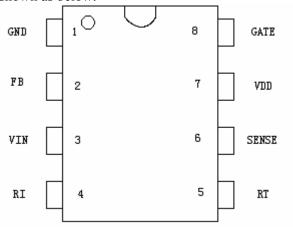

### **Pin Configuration**

The HG2269 is offered in DIP and SOP packages shown as below.

### **Package Dissipation Rating**

| Package | R0JA (°C/W) |

|---------|-------------|

| DIP8    | 90          |

| SOP8    | 150         |

#### **Absolute Maximum Ratings**

| Parameter                                 | Value            |

|-------------------------------------------|------------------|

| VDD/VIN DC Supply                         | 30 V             |

| Voltage                                   |                  |

| VDD Zener Clamp                           | VDD_Clamp+0.1V   |

| Voltage <sup>Note</sup>                   |                  |

| VDD Clamp Continuous                      | 10 mA            |

| Current                                   |                  |

| V <sub>FB</sub> Input Voltage             | -0.3 to 7V       |

| V <sub>SENSE</sub> Input Voltage to Sense | -0.3 to 7V       |

| Pin                                       |                  |

| V <sub>RT</sub> Input Voltage to RT Pin   | -0.3 to 7V       |

| V <sub>RI</sub> Input Voltage to RI Pin   | -0.3 to 7V       |

| Min/Max Operating Junction                | -20 to 150 °C    |

| Temperature T <sub>J</sub>                |                  |

| Min/Max Storage                           | -55 to 150 °C    |

| Temperature T <sub>stg</sub>              |                  |

| Lead Temperature (Soldering,              | 260 °C           |

| 10secs)                                   |                  |

| Note: VDD. Clamp has a nomina             | al value of 35\/ |

**Note:** VDD\_Clamp has a nominal value of 35V.

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

# **TERMINAL ASSIGNMENTS**

| Pin Num | Pin Name | I/O | Description                                                                                                              |

|---------|----------|-----|--------------------------------------------------------------------------------------------------------------------------|

| 1       | GND      | Р   | Ground                                                                                                                   |

| 2       | FB       | Ι   | Feedback input pin. PWM duty cycle is determined by voltage level into this pin and current-sense signal level at Pin 6. |

| 3       | VIN      | Ι   | Connected through a large value resistor to rectified line input for Startup IC supply and line voltage sensing.         |

| 4       | RI       | Ι   | Internal Oscillator frequency setting pin. A resistor connected between RI and GND sets the PWM frequency.               |

| 5       | RT       | Ι   | Temperature sensing input pin. Connected through a NTC resistor to GND.                                                  |

| 6       | SENSE    | Ι   | Current sense input pin. Connected to MOSFET current sensing resistor node.                                              |

| 7       | VDD      | Р   | DC power supply pin.                                                                                                     |

| 8       | GATE     | 0   | Totem-pole gate drive output for power MOSFET.                                                                           |

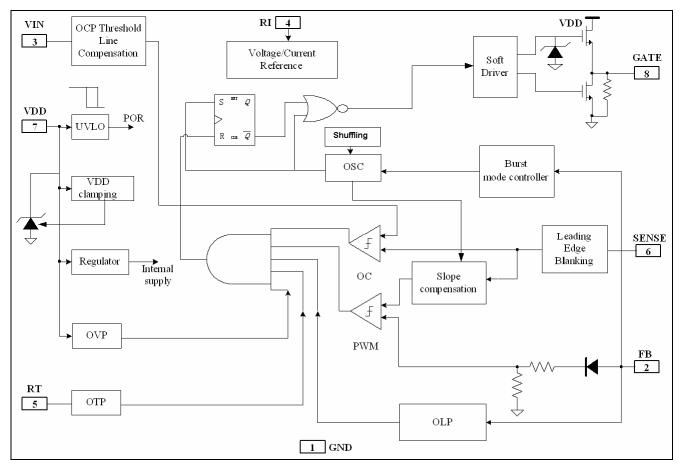

# **BLOCK DIAGRAM**

# **RECOMMENDED OPERATING CONDITION**

| Symbol         | Parameter                     | Min | Max | Unit |

|----------------|-------------------------------|-----|-----|------|

| VDD            | VDD Supply Voltage            | 12  | 23  | V    |

| RI             | RI Resistor Value             | 24  | 31  | Kohm |

| T <sub>A</sub> | Operating Ambient Temperature | -20 | 85  | °C   |

## **ESD INFORMATION**

| Symbol              | Parameter                              | Test Conditions | Min | Тур | Max | Unit |

|---------------------|----------------------------------------|-----------------|-----|-----|-----|------|

| HBM <sup>Note</sup> | Human Body Model<br>on All Pins Except | MIL-STD         |     | 3   |     | KV   |

|                     | VIN and VDD                            |                 |     |     |     |      |

| MM                  | Machine Model on<br>All Pins           | JEDEC-STD       |     | 250 |     | V    |

**Note:** HBM all pins pass 3KV except High Voltage Input pin. The details are VIN passes 1kV, VDD passes 1.5KV, all other I/Os pass 3KV. In system application, High Voltage Input pin is either a high impedance input or connected to a cap. The lower rating has minimum impacts on system ESD performance.

# **ELECTRICAL CHARACTERISTICS**

$(T_A = 25^{\circ}C, VDD=16V, RI=24Kohm if not otherwise noted)$

| Symbol                        | Parameter                    | Test Conditions                                     | Min       | Тур  | Max  | Unit |

|-------------------------------|------------------------------|-----------------------------------------------------|-----------|------|------|------|

| Supply Voltage (V             | DD)                          |                                                     | · · · · · |      |      |      |

| I_VDD_Startup                 | VDD Start up                 | VDD=15V, Measure                                    |           | 6.5  | 20   | uA   |

|                               | Current                      | current into VDD                                    |           |      |      |      |

| I VDD Operation               | Operation Current            | V <sub>FB</sub> =3V                                 |           | 2.3  |      | mA   |

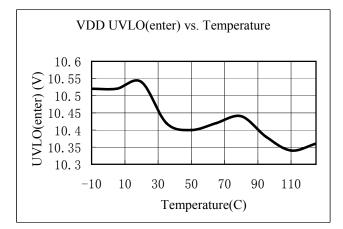

| UVLO(Enter)                   | VDD Under Voltage            |                                                     | 9.5       | 10.5 | 11.5 | V    |

|                               | Lockout Enter                |                                                     |           |      |      |      |

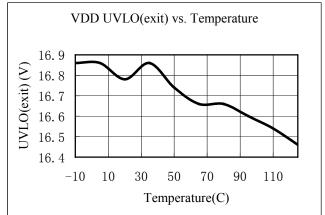

| UVLO(Exit)                    | VDD Under Voltage            |                                                     | 15.5      | 16.5 | 17.5 | V    |

|                               | Lockout Exit                 |                                                     |           |      |      |      |

|                               | (Startup)                    |                                                     |           |      |      |      |

| OVP(ON) <sup>*Optional</sup>  | VDD Over Voltage             |                                                     | 23.5      | 25   | 26.5 | V    |

|                               | Protection Enter             |                                                     |           |      |      |      |

| OVP(OFF) <sup>*Optional</sup> | VDD Over Voltage             |                                                     | 21.5      | 23   | 24.5 | V    |

|                               | Protection Exit              |                                                     |           |      |      |      |

|                               | (Recovery)                   |                                                     |           |      |      |      |

| OVP_Hys*Optional              | OVP Hysteresis               | OVP(ON)-OVP(OFF)                                    |           | 2    |      | V    |

| T <sub>D</sub> OVP            | VDD OVP                      |                                                     |           | 80   |      | uSec |

| —                             | Debounce time                |                                                     |           |      |      |      |

| V <sub>DD</sub> Clamp         | V <sub>DD</sub> Zener Clamp  | $I(V_{DD}) = 5mA$                                   |           | 35   |      | V    |

|                               | Voltage                      |                                                     |           |      |      |      |

| Feedback Input Se             | ection(FB Pin)               |                                                     |           |      |      |      |

| A <sub>VCS</sub>              | PWM Input Gain               | $\Delta$ V <sub>FB</sub> / $\Delta$ V <sub>cs</sub> |           | 2.8  |      | V/V  |

| V <sub>FB</sub> Open          | V <sub>FB</sub> Open Voltage |                                                     |           | 5.9  |      | V    |

| 1                             |                              |                                                     |           |      |      |      |

| I <sub>FB</sub> Short         | FB pin short circuit         | Short FB pin to GND,                                |           | 0.80 |      | mA   |

| —                             | current                      | measure current                                     |           |      |      |      |

| V <sub>TH</sub> _0D           | Zero Duty Cycle FB           |                                                     |           |      | 0.95 | V    |

| _                             | Threshold Voltage            |                                                     |           |      |      |      |

| V <sub>TH</sub> _BM           | Burst Mode FB                |                                                     |           | 1.7  |      | V    |

| —                             | Threshold Voltage            |                                                     |           |      |      |      |

| V <sub>TH</sub> _PL           | Power Limiting FB            |                                                     |           | 4.4  |      | V    |

| —                             | Threshold Voltage            |                                                     |           |      |      |      |

| T <sub>D</sub> _PL            | Power limiting               |                                                     |           | 80   |      | mSec |

| ~                             | Debounce Time                |                                                     |           |      |      |      |

| Z <sub>FB</sub> IN            | Input Impedance              |                                                     |           | 7.2  |      | Kohm |

| Current Sense Inp             |                              | •                                                   |           | •    |      |      |

| T blanking                    | Sense Input Leading          |                                                     |           | 250  |      | nS   |

| _ 0                           | Edge Blanking Time           |                                                     |           |      |      |      |

| Z <sub>SENSE</sub> _IN        | Sense Input                  |                                                     |           | 30   |      | Kohm |

|                         | Impedance                     |                        |       |       |       |      |

|-------------------------|-------------------------------|------------------------|-------|-------|-------|------|

| T <sub>D</sub> OC       | Over Current                  | CL=1nf at GATE,        |       | 120   |       | nSec |

| —                       | Detection and                 |                        |       |       |       |      |

|                         | Control Delay                 |                        |       |       |       |      |

| V <sub>TH</sub> OC_0    | Current Limiting              | I(VIN) = 0uA           | 0.85  | 0.90  | 0.95  | V    |

|                         | Threshold at No               |                        |       |       |       |      |

|                         | Compensation                  |                        |       |       |       |      |

| V <sub>TH</sub> OC_1    | Current Limiting              | I(VIN) = 150uA         |       | 0.81  |       | V    |

|                         | Threshold at                  |                        |       |       |       |      |

|                         | Compensation                  |                        |       |       |       |      |

| Oscillator              |                               |                        |       |       |       |      |

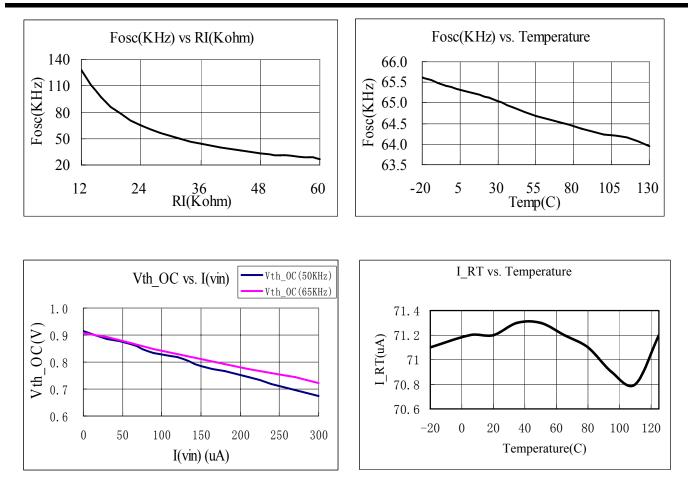

| F <sub>OSC</sub>        | Normal Oscillation            |                        | 60    | 65    | 70    | KHZ  |

|                         | Frequency                     |                        |       |       |       |      |

| Δf Temp                 | Frequency                     | -20°C to 100°C         |       | 2     |       | %    |

| _ 1                     | Temperature                   |                        |       |       |       |      |

|                         | Stability                     |                        |       |       |       |      |

| Δf VDD                  | Frequency Voltage             | VDD = 12-25V           |       | 2     | 1     | %    |

| _                       | Stability                     |                        |       |       |       |      |

| RI range                | Operating RI Range            |                        | 12    | 24    | 60    | Kohm |

| V RI open               | RI open voltage               |                        |       | 2.0   |       | V    |

| F BM                    | Burst Mode Base               |                        |       | 22    |       | KHZ  |

| _                       | Frequency                     |                        |       |       |       |      |

| DC max                  | Maxmum Duty                   |                        | 75    | 80    | 85    | %    |

| _                       | Cycle                         |                        |       |       |       |      |

| DC min                  | Minimum Duty                  |                        | -     | -     | 0     | %    |

| - <u>-</u>              | Cycle                         |                        |       |       | -     |      |

| Gate Drive Outp         | 2                             |                        | I     |       |       |      |

| VOL                     | Output Low Level              | Io = -20 mA            |       |       | 0.3   | V    |

| VOH                     | Output High Level             | $I_0 = +20 \text{ mA}$ | 11    |       |       | V    |

| VG Clamp                | Output Clamp                  | VDD=20V                |       | 18    |       | V    |

| ·                       | Voltage Level                 |                        |       |       |       |      |

| T r                     | Output Rising Time            | CL = 1nf               |       | 120   |       | nSec |

| T f                     | Output Falling Time           | CL = 1nf               |       | 50    |       | nSec |

| Over Temperatu          |                               |                        |       | 1     | 1     |      |

| I RT                    | Output Current of             |                        |       | 70    |       | uA   |

| <u>_</u>                | RT pin                        |                        |       | 10    |       | ui i |

| V <sub>TH</sub> OTP     | OTP Threshold                 |                        | 1.015 | 1.065 | 1.115 | V    |

| VIH_OII                 | Voltage                       |                        | 1.015 | 1.005 | 1.115 | •    |

| V <sub>TH</sub> OTP off | OTP Recovery                  |                        |       | 1.165 |       | V    |

| VIH_OII_OII             | Threshold Voltage             |                        |       | 1.105 |       | •    |

| T <sub>D</sub> OTP      | OTP De-bounce                 |                        |       | 100   |       | uSec |

|                         | Time                          |                        |       | 100   |       | ubee |

| V RT Open               | RT Pin Open                   |                        |       | 3.5   |       | V    |

| v_ivi_open              | Voltage                       |                        |       | 5.5   |       | v    |

| Frequency Shuff         |                               |                        |       | 1     | 1     | 1    |

|                         |                               |                        | -3    | 1     | 3     | %    |

| $\Delta f_{OSC}$        | Frequency<br>Modulation range |                        | -3    |       | 5     | 70   |

|                         | Modulation range              |                        |       |       |       |      |

| Eroa Shuffling          | /Base frequency               | $DI - 24V_{obm}$       |       | 22    |       | Ц7   |

| Freq_Shuffling          | Shuffling Frequency           | RI = 24Kohm            |       | 32    |       | HZ   |

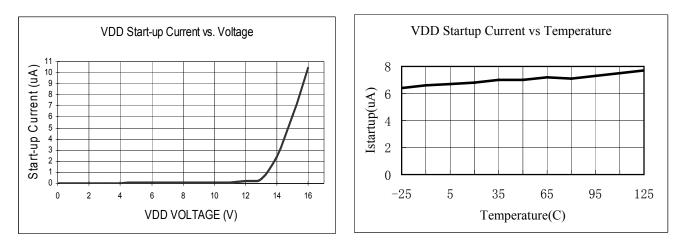

# **CHARACTERIZATION PLOTS**

HG2269

## **OPERATION DESCRIPTION**

The HG2269 is a highly integrated PWM controller IC optimized for offline flyback converter applications. The extended burst mode control greatly reduces the standby power consumption and helps the design easily meet the international power conservation requirements.

### • Startup Current and Start up Control

Startup current of HG2269 is designed to be very low so that VDD could be charged up above UVLO(exit) threshold level and device starts up quickly. A large value startup resistor can therefore be used to minimize the power loss yet reliable startup in application. For a typical AC/DC adaptor with universal input range design, a 2 M $\Omega$ , 1/8 W startup resistor could be used together with a VDD capacitor to provide a fast startup and yet low power dissipation design solution.

### • Operating Current

The Operating current of HG2269 is low at 2.3mA. Good efficiency is achieved with HG2269 low operating current together with extended burst mode control schemes.

### • Frequency shuffling for EMI improvement

The frequency Shuffling/jittering (switching frequency modulation) is implemented in HG2269. The oscillation frequency is modulated with a internally generated random source so that the tone energy is evenly spread out. The spread spectrum minimizes the conduction band EMI and therefore eases the system design in meeting stringent EMI requirement.

### • Burst Mode Operation

At zero load or light load condition, most of the power dissipation in a switching mode power supply is from switching loss on the MOSFET transistor, the core loss of the transformer and the loss on the snubber circuit. The magnitude of power loss is in proportion to the number of switching events within a fixed period of time. Reducing switching events leads to the reduction on the power loss and thus conserves the energy. HG2269 self adjusts the switching mode according to the loading condition. At from no load to light/medium load condition, the FB input drops below burst mode threshold level (1.8V). Device enters Burst Mode control. The Gate drive output switches only when VDD voltage drops below a preset level and FB input is active to output an on state. Otherwise the gate drive remains at off state

to minimize the switching loss thus reduce the standby power consumption to the greatest extend. The nature of high frequency switching also reduces the audio noise at any loading conditions.

### • Oscillator Operation

A resistor connected between RI and GND sets the constant current source to charge/discharge the internal cap and thus the PWM oscillator frequency is determined. The relationship between RI and switching frequency follows the below equation within the specified RI in Kohm range at nominal loading operational condition.

$$F_{OSC} = \frac{1560}{RI(Kohm)}(Khz)$$

# • Current Sensing and Leading Edge Blanking

Cycle-by-Cycle current limiting is offered in HG2269 current mode PWM control. The switch current is detected by a sense resistor into the sense pin. An internal leading edge blanking circuit chops off the sense voltage spike at initial MOSFET on state due to snubber diode reverse recovery so that the external RC filtering on sense input is no longer required. The current limit comparator is disabled and thus cannot turn off the external MOSFET during the blanking period. PWM duty cycle is determined by the current sense input voltage and the FB input voltage.

### • Internal Synchronized Slope Compensation

Built-in slope compensation circuit adds voltage ramp onto the current sense input voltage for PWM generation. This greatly improves the close loop stability at CCM and prevents the sub-harmonic oscillation and thus reduces the output ripple voltage.

### • Over Temperature Protection

A NTC resistor in series with a regular resistor should connect between RT and GND for temperature sensing and protection. NTC resistor value becomes lower when the ambient temperature rises. With the fixed internal current  $I_{RT}$  flowing through the resistors, the voltage at RT pin becomes lower at high temperature. The internal OTP circuit is triggered and shutdown the MOSFET when the sensed input voltage is lower than V<sub>TH</sub> OTP.

### • Gate Drive

HG2269 Gate is connected to the Gate of an external MOSFET for power switch control. Too weak the gate drive strength results in higher conduction and switch loss of MOSFET while too strong gate drive output compromises the EMI.

Good tradeoff is achieved through the built-in totem pole gate drive design with right output strength and dead time control. The low idle loss and good EMI system design is easier to achieve with this dedicated control scheme. An internal 18V clamp is added for MOSFET gate protection at higher than expected VDD input.

### • Protection Controls

Good system reliability is achieved with HG2269's rich protection features including Cycle-by-Cycle current limiting (OCP), Over Load Protection (OLP), over temperature protection (OTP), on-chip VDD over voltage protection (OVP, optional) and under voltage lockout (UVLO).

The OCP threshold value is self adjusted lower at higher current into VIN pin. This OCP threshold slope adjustment helps to compensate the increased output power limit at higher AC voltage caused by inherent Over-Current sensing and control delay. A constant output power limit is achieved with recommended OCP compensation scheme on HG2269.

At output overload condition, FB voltage is biased higher. When FB input exceeds power limit threshold value for more than 80mS, control circuit reacts to turnoff the power MOSFET.

Similarly, control circuit shutdowns the power MOSFET when an Over Temperature condition is detected. HG2269 resumes the operation when temperature drops below the hysteresis value.

VDD is supplied with transformer auxiliary winding output. It is clamped when VDD is higher than 35V. MOSFET is shut down when VDD drops below UVLO(enter) limit and device enters power on startup sequence thereafter.

Important statement:

Huaguan Semiconductor Co,Ltd. reserves the right to change the products and services provided without notice. Customers should obtain the latest relevant information before ordering, and verify the timeliness and accuracy of this information.

Customers are responsible for complying with safety standards and taking safety measures when using our products for system design and machine manufacturing to avoid potential risks that may result in personal injury or property damage.

Our products are not licensed for applications in life support, military, aerospace, etc., so we do not bear the consequences of the application of these products in these fields.

Our documentation is only permitted to be copied without any tampering with the content, so we do not accept any responsibility or liability for the altered documents.