# **Dual Channel Switch Interface IC**

### FEATURES AND BENEFITS

- 4.75 to 26.5 V operation

- Low V<sub>IN</sub>-to-V<sub>OUT</sub> voltage drop

- <sup>1</sup>/<sub>10</sub> current sense feedback

- Survive short-to-battery and short-to-ground faults

- Survive 40 V load dump

- >4 kV ESD rating on the output pins, >2 kV on all other pins

- Output current limiting

- Low operating and Sleep mode currents

- Integrates with Allegro A114x and A118x Hall effect two-wire sensor ICs

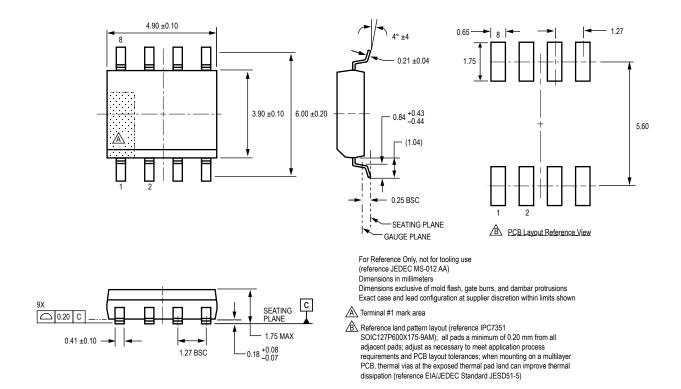

## PACKAGE: 8 pin SOIC (suffix L)

```

Approximate Footprint

```

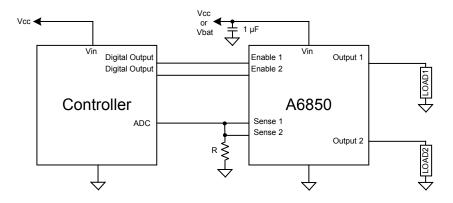

## DESCRIPTION

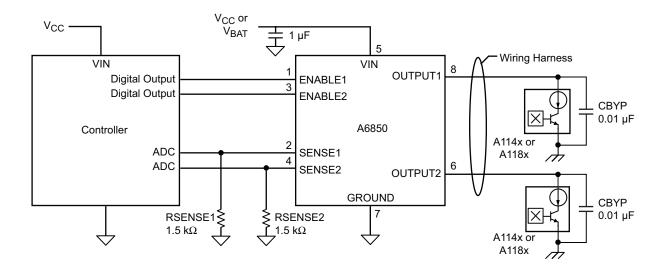

The Allegro<sup>TM</sup> A6850 is designed to interface between a microprocessor and a pair of 2-wire Hall effect sensor ICs. The A6850 uses protected high-side low resistance DMOS MOSFETs to switch the supply voltage to the two Hall effect devices. Each switch can be controlled independently via individual ENABLE pins and both switches are protected with current-limiting circuitry. The output switches are rated to operate to 26.5 V and will source at least 25 mA per channel before current limiting.

Typical two-wire Hall device applications require the user to measure the supply current to determine whether the Hall IC is switched on (magnetic field present) or switched off (no magnetic field present). This is usually accomplished by using an external series shunt resistor and protection circuits for the microprocessor. In many systems, the sensed voltage is used as the input to a microprocessor analog-to-digital (A-to-D) input. This provides the system with an indication of the status of the two-wire switch as well as provides the capability for diagnostic information if there is an open or shorted Hall device.

Continued on the next page ...

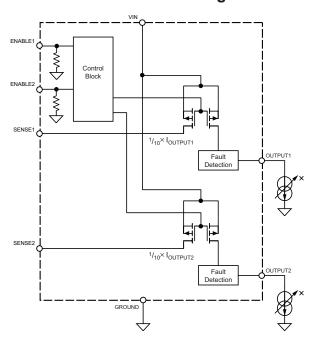

### **Functional Block Diagram**

#### **Description (continued)**

The A6850 eliminates the need for the external series shunt resistor in Hall device applications by incorporating an integrated current mirror which reports the Hall IC supply current as a  $1/_{10}$  value on the SENSE1 or SENSE2 output pin. A low current Sleep mode is available (<15  $\mu A)$  by driving both ENABLE pins low. Also, the A6850 can be used to interface to mechanical switches.

The A6850 is supplied in an 8-pin Pb (lead) free SOIC package, with 100% matte tin leadframe plating.

#### **Selection Guide**

| Part Number | Packing                       |

|-------------|-------------------------------|

| A6850KLTR-T | 13-in. reel, 3000 pieces/reel |

#### Absolute Maximum Ratings

| Characteristic                    | Symbol               | Notes                             | Rating     | Units |

|-----------------------------------|----------------------|-----------------------------------|------------|-------|

| Supply Voltage                    | V <sub>IN</sub>      |                                   | 40         | V     |

| Output Voltage                    | V <sub>OUTPUTx</sub> |                                   | -0.3 to 40 | V     |

| SENSEx Voltage Range              | V <sub>SENSEx</sub>  |                                   | –0.3 to 7  | V     |

| ENABLEx Voltage Range             | V <sub>ENABLEx</sub> |                                   | -0.3 to 7  | V     |

| Operating Ambient Temperature     | T <sub>A</sub>       |                                   | -40 to 150 | °C    |

| Maximum Junction Temperature      | T <sub>J</sub> (max) |                                   | 150        | °C    |

| Storage Temperature               | T <sub>stg</sub>     |                                   | –55 to 150 | °C    |

| ESD Rating - Human Body Model     | НВМ                  | AEC-Q100-002; OUTPUT1 and OUTPUT2 | 4.5        | kV    |

|                                   |                      | AEC-Q100-002; all other pins      | 2.5        | kV    |

| ESD Rating - Charged Device Model | CDM                  | AEC-Q100-011; all pins            | 1050       | V     |

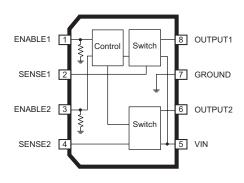

#### **Pinout Diagram**

#### **Terminal List Table**

| Name    | Number | Description                            |

|---------|--------|----------------------------------------|

| ENABLE1 | 1      | Digital input pulled to ground         |

| SENSE1  | 2      | Sensed current output                  |

| ENABLE2 | 3      | Digital input pulled to ground         |

| SENSE2  | 4      | Sensed current output                  |

| VIN     | 5      | Chip power supply voltage              |

| OUTPUT2 | 6      | Switchable voltage supply to sensor IC |

| GROUND  | 7      | Ground reference                       |

| OUTPUT1 | 8      | Switchable voltage supply to sensor IC |

#### THERMAL CHARACTERISTICS may require derating at maximum conditions, see application information

| Characteristic             | Symbol           | Test Conditions*                               | Value | Units |

|----------------------------|------------------|------------------------------------------------|-------|-------|

| Package Thermal Resistance | R <sub>θJA</sub> | 4-layer PCB based on JEDEC standard            | 80    | °C/W  |

|                            | θJA              | 1-layer PCB with copper limited to solder pads | 140   | °C/W  |

\*Additional thermal data available on the Allegro Web site.

# **Dual Channel Switch Interface IC**

#### ELECTRICAL CHARACTERISTICS at $T_J$ = -40 to +150°C (unless noted otherwise)

| Characteristics                                     | Symbol                    | Test Conditions                                                                                                                    | Min.  | Тур.  | Max.                | Units |

|-----------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---------------------|-------|

| Supply Input Voltage Range                          | V <sub>IN</sub>           |                                                                                                                                    | 4.75  | -     | 26.5                | V     |

|                                                     |                           | Operating mode, I <sub>OUTPUTx</sub> = 0 mA                                                                                        | _     | -     | 5.0                 | mA    |

| Supply Input Quiescent Current                      | I <sub>INQ</sub>          | Sleep mode:<br>ENABLE1 and ENABLE2 low<br>V <sub>OUTPUT1</sub> = V <sub>OUTPUT2</sub> = 0 V                                        | _     | _     | 15                  | μA    |

| Power-Up Time <sup>1</sup>                          | t <sub>on</sub>           |                                                                                                                                    | _     | _     | 20                  | μs    |

| Output Rise Time <sup>2</sup>                       | t <sub>rLH</sub>          | I <sub>OUTPUTx</sub> = 0 to –10 mA,<br>10% to 90%V <sub>SENSEx</sub>                                                               | _     | 0.18  | 1.5                 | μs    |

| Output Fall Time <sup>2</sup>                       | t <sub>fHL</sub>          | I <sub>OUTPUTx</sub> = 0 to –10 mA,<br>90% to 10%V <sub>SENSEx</sub>                                                               | _     | 1.4   | 3.5                 | μs    |

| Enable Delay Time <sup>2</sup>                      | t <sub>ENdlyLH</sub>      | I <sub>OUTPUTx</sub> = -5 mA,<br>50% ENABLEx to 50%V <sub>SENSEx</sub>                                                             | -     | 150   | 500                 | ns    |

| Disable Delay Time <sup>2</sup>                     | t <sub>ENdlyHL</sub>      | I <sub>OUTPUTx</sub> = -5 mA,<br>50% ENABLEx to 50%V <sub>SENSEx</sub>                                                             | _     | 4.0   | 7.5                 | μs    |

| OUTPUTx Source Resistance                           | R <sub>DS(on)</sub>       | I <sub>OUTPUTx</sub> = –20 mA                                                                                                      | -     | -     | 35                  | Ω     |

| OUTPUTx Leakage Current                             | I <sub>OUTPUTQ</sub>      | V <sub>OUTPUTx</sub> = 0 V; disabled                                                                                               | -     | -     | -20                 | μA    |

| SENSEx Output Current Offset <sup>3</sup>           | I <sub>SENSE(ofs)</sub>   | $I_{\text{SENSEx}} = (I_{\text{OUTPUTx}} / 10) + I_{\text{SENSE(ofs)}},$<br>$I_{\text{OUTPUT}} = -2 \text{ mA to } -20 \text{ mA}$ | -100  | -     | 100                 | μA    |

|                                                     | I <sub>SENSEQ</sub>       | V <sub>SENSEx</sub> = 0 V; disabled                                                                                                | -     | -     | 10                  | μA    |

| SENSEx Voltage <sup>4</sup>                         |                           | V <sub>IN</sub> > 7 V                                                                                                              | 0     | -     | 6                   | V     |

| SENSEX VOltage                                      | V <sub>SENSEx</sub>       | V <sub>IN</sub> < 7 V                                                                                                              | 0     | -     | V <sub>IN</sub> – 1 | V     |

| ENABLEx Input Voltage Range                         | V <sub>ENABLEH</sub>      |                                                                                                                                    | 2.0   | -     | -                   | V     |

| ENABLES Input voltage Range                         | V <sub>ENABLEL</sub>      |                                                                                                                                    | _     | -     | 0.4                 | V     |

| ENABLEx Input Hysteresis                            | V <sub>ENABLEhys</sub>    | At least one output enabled                                                                                                        | 125   | -     | 375                 | mV    |

|                                                     |                           | ENABLEx = 2.0 V                                                                                                                    | -     | 40    | 100                 | μA    |

| ENABLEx Current                                     | IENABLE                   | ENABLEx = 0.4 V                                                                                                                    | _     | 8.0   | 20                  | μA    |

| OUTPUT Current Limit                                | I <sub>OUTPUTM</sub>      |                                                                                                                                    | -25.0 | -35.0 | -45.0               | mA    |

| OUTPUT Reverse Bias Current                         | I <sub>OUTPUT(rvrs)</sub> | Reverse bias blocking: $V_{IN}$ = 4.75 V,<br>V <sub>OUTPUT</sub> = 26.5 V                                                          | _     | 500   | 750                 | μA    |

| Overvoltage Protection Threshold                    | V <sub>OVP</sub>          | Rising V <sub>IN</sub>                                                                                                             | 27.0  | -     | 33.0                | V     |

| Overvoltage Protection Hysteresis                   | V <sub>OVPhys</sub>       |                                                                                                                                    | _     | 2.0   | _                   | V     |

| Thermal Shutdown Threshold                          | T <sub>TSD</sub>          | Temperature Increasing                                                                                                             | _     | 175   | -                   | °C    |

| Thermal Shutdown Hysteresis                         | T <sub>TSDhys</sub>       |                                                                                                                                    | _     | 15    | _                   | °C    |

| <sup>1</sup> Delay from end of Sleep mode to output |                           | 1                                                                                                                                  | 1     | 1     |                     |       |

<sup>1</sup>Delay from end of Sleep mode to outputs enabled.

${}^{2}R_{SENSEx}$  = 1.5 k $\Omega$ .

<sup>3</sup>For input and output current specifications, negative current is defined as coming out of (sourced from) the specified device pin.

$^{4}$ User to ensure that V<sub>SENSEx</sub> remains within the specified range. If V<sub>SENSEx</sub> exceeds the maximum value, the device is self-protected by an internal clamp, but not all parameters perform as specified.

## **Characteristic Performance**

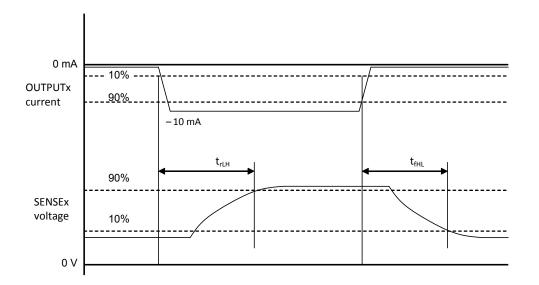

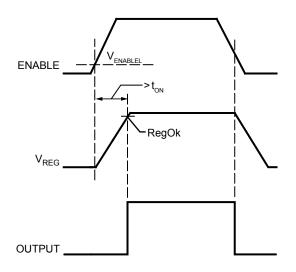

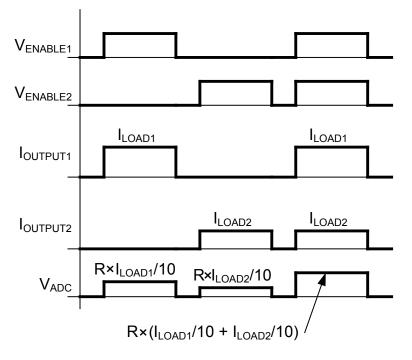

Figure 1. Signal Channel Timing, ENABLE1 = ENABLE1 = High,  $R_{SENSE}$  = 1.5 k $\Omega$

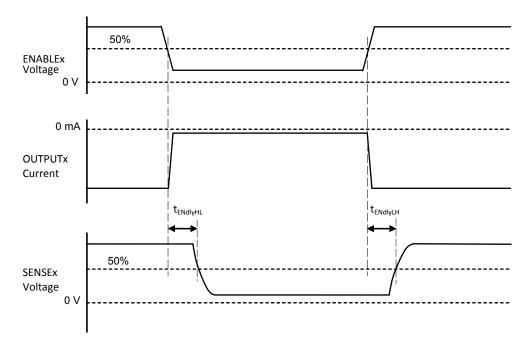

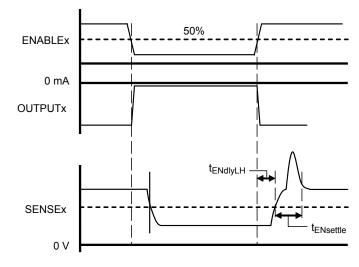

Figure 2. Enable Delays, one ENABLE input held high to prevent the IC going into Sleep mode

# **Functional Description**

#### **SENSE Pin Outputs**

The A6850 divides the OUTPUTx pin current by 10 and mirrors it onto the corresponding SENSEx pin. Putting sense resistors, RSENSE, from these pins to ground will create a voltage that can be read by an ADC (analog-to-digital converter). The value of  $R_{SENSE}$  should be chosen so that the voltage drop across the sense resistor ( $V_{RSENSE}$ ) does not exceed the maximum voltage rating of the ADC. For further protection of the ADC, an external clamping circuit, such as a Zener diode, can be used to clamp any transient current spikes that may occur on the output that would be translated onto the SENSE pins.

The sense current is one tenth of the output current, plus an offset current. This offset current is consistent across the whole range of the output current. The sense current can be calculated by the following formula:

$$I_{\text{SENSEx}} = (I_{\text{OUTPUTx}} / 10) + I_{\text{SENSE(ofs)}}.$$

(1)

The sense resistor must also be chosen to meet the voltage limits on the sense pin (see Electrical Characteristics table).

#### **Output Current Limit**

The A6850 limits the output current to a maximum current of  $I_{OUTPUTM}$ . The output current will remain at the current limit until the output load is reduced or the A6850 goes into thermal shutdown.

The high output current limit allows the bypass capacitor,  $C_{BYP}$ , on the Hall sensor IC to charge up quickly. This allows a high slew rate on the VCC pin of the Hall sensor IC, ensuring that the sensor IC Power-On State will be correct. See the Applications Information section for schematic diagrams and power calculations.

#### **Output Faults**

The A6850 withstands short-to-ground or short-to-battery of the OUTPUTx pins. In the case of short-to-ground, current is held to the current limit ( $I_{OUTPUTM}$ ).

If  $V_{OUTPUTx} > (V_{IN} + 0.7 V)$  during a short-to-battery event, the A6850 monitors  $V_{OUTPUTx}$  and disables the outputs. Because the protection circuitry requires a finite amount of time to disable the outputs, a bypass capacitor of 1  $\mu$ F is necessary on  $V_{IN}$ . Although OUTPUTx sinks current into the A6850 in this state, the reverse current is shunted to ground and does not appear on the VIN pin.

#### **Overvoltage Protection**

The A6850 has built-in overvoltage protection against a load dump on the supply bus. In the case of a load dump, or when  $V_{IN}$  is connected to the battery supply bus and  $V_{IN}$  rises above the overvoltage threshold,  $V_{OVP}$ , the A6850 will shut off the outputs.

#### Sleep Mode

Low-leakage or sleep modes are required in automotive applications to minimize battery drain when the vehicle is parked. The A6850 enters sleep mode when both ENABLE pins are low. In sleep mode, the internal regulators and all other internal circuitry are disabled.

When enabling an output, the part must first come out of sleep mode. Consequently, the wake-up time amounts to a propagation delay before the outputs turn on. Also, the ENABLE pins do not switch with hysteresis until the regulators stabilize.

After the internal regulators stabilize, internal circuitry is enabled and the outputs turn on, as shown in figure 3. As long as one ENABLE pin is held high, the A6850 operates with hysteresis.

Figure 3. Activation Timing Diagram. Exiting Sleep mode via ENABLE signal to output waveform.

#### Signal and Enable delays

When ENABLEx = 1, current signals applied to the OUTPUTx pins will appear scaled and delayed on the SENSEx pins. The transfer characteristic can be considered that of a low pass filter.

The response time definitions are given in figures 1 and 2, in the Characteristic Performance section.

The rise time response is dependent on the effective capacitance loading on the SENSEx pin.

The RC time constant,  $\tau$ , can be estimated using:

$$\tau = R_{\text{SENSEx}} \left(90 + C_{\text{SENSE}}\right) \tag{2}$$

where  $R_{SENSEx}$  is in k $\Omega$  and  $C_{SENSE}$  is in pF; the result will be in ns.

The 10% to 90% rise time,  $\Box t_{rLH}$ , may be estimated from:

$$t_{\rm rLH} = 2.2 \times \tau \tag{3}$$

The small signal low pass filter bandwidth based on a single pole response may be estimated using:

$$BW = 350 / t_{rLH}$$

<sup>(4)</sup>

The result is in MHz when t<sub>rLH</sub> is in ns.

If the values of  $t_{rLH}$  and  $t_{fHL}$  are significantly different then a better estimate may be given by:

$$BW = 700 / (t_{rLH} + t_{fHL})$$

(5)

The result is in MHz when  $t_{rLH}$  and  $t_{fHL}$  are in ns.

Each signal channel may be enabled or disabled individually via their respective ENABLEx pins, as shown in table 1.

| Table 1. | Enable/Disable   | Signal  | Channel | Truth | Table |

|----------|------------------|---------|---------|-------|-------|

| 10010 11 | Ellasio, Bioasio | orginar | onunior |       | 10010 |

| EN1 | EN2 | IOU1           | IOU2           | SEN1                | SEN2               |

|-----|-----|----------------|----------------|---------------------|--------------------|

| L*  | L*  | 0              | 0              | 0                   | 0                  |

| Н   | L   | I <sub>1</sub> | 0              | I <sub>1</sub> / 10 | 0                  |

| L   | Н   | 0              | l <sub>2</sub> | 0                   | l <sub>2</sub> /10 |

| Н   | Н   | l <sub>1</sub> | l <sub>2</sub> | I <sub>1</sub> / 10 | l <sub>2</sub> /10 |

\*Sleep mode

When a capacitor is added in parallel with the signal source connected to an OUTPUTx pin, additional allowance must be made for settling time caused by the inrush current needed to recharge a partially, or fully discharged, capacitor which has decayed during the disabled period.

During this time the current required may reach  $I_{OUTPUTM}$ , the current limit value for the OUTPUTx pins.

The effects will be most noticeable on a SENSEx pin and will usually cause a signal overshoot as shown as  $t_{ENsettle}$  in figure 4.

#### Thermal Shutdown (TSD)

The A6850 protects itself from excessive heat damage by disabling both outputs when the junction temperature,  $T_J$ , rises above the TSD threshold ( $T_{TSD}$ ). The outputs will remain off until the junction temperature falls below the  $T_{TSD}$  level minus the TSD hysteresis,  $T_{TSDhys}$ .

Figure 4. Overshoot resulting from additional capacitance.

# **Dual Channel Switch Interface IC**

$T_J$  can be estimated by calculating the power dissipation ( $P_D$ ) of the A6850. To calculate  $P_D$ :

$P_{\rm D} = V_{\rm IN} I_{\rm INQ} \tag{6}$

$$-V_{\text{OUTPUT1}} I_{\text{OUTPUT1}} - V_{\text{OUTPUT2}} I_{\text{OUTPUT2}}$$

$$-V_{\text{SENSE1}}I_{\text{SENSE1}}-V_{\text{SENSE2}}I_{\text{SENSE2}}$$

.

$P_{\rm D} = V_{\rm IN} I_{\rm INQ} \tag{7}$

+  $(V_{\text{IN}} - V_{\text{OUTPUT1}}) I_{\text{OUTPUT1}}$

+ (

$$V_{\rm IN} - V_{\rm OUTPUT2}$$

)  $I_{\rm OUTPUT2}$

$+ (V_{\rm IN} - V_{\rm SENSE1}) I_{\rm SENSE1}$

$$+ (V_{\rm IN} - V_{\rm SENSE2}) I_{\rm SENSE2}$$

When  $I_{OUTPUTx} \times R_{DS(on)} < approximately 700 mV$ , then:

$$(V_{IN} - V_{OUTPUTx}) = I_{OUTPUTx} \times R_{DS(on)}$$

.

When  $I_{OUTPUTx} \times R_{DS(on)}$  > approximately 700 mV, then:

$I_{OUTPUTx} = I_{OUTPUT}(max)$ ,

and  $V_{OUTPUTx}$  is set by the loading on the OUTPUTx pin.

The temperature rise of the A6850 can be calculated by multiplying  $P_D$  and the thermal resistance from junction to ambient,  $R_{\theta JA}$ . The formula for temperature rise,  $\Delta T$ , is:

$$\Box \quad \Delta T = P_{\rm D} \times \mathbf{R}_{\theta \rm JA} \,. \tag{8}$$

The  $R_{\theta JA}$  for an 8-pin SOIC (Allegro L package) on a one-layer board with minimum copper area is 140 °C/W. (More thermal data is available on the Allegro MicroSystems website.)

The total junction temperature can be calculated by:

$$T_{\rm J} = T_{\rm A} + \Delta T \,, \tag{9}$$

where  $T_A$  is the ambient air temperature.

*Example*: Calculating the power dissipation and temperature rise, given:

$$\begin{split} T_A &= 25^\circ C \ , \\ V_{IN} &= 5 \ V \ , \\ I_{INQ} &= 5 \ mA \ , \\ I_{OUTPUT1} &= I_{OUTPUT2} = 15 \ mA \ , \\ I_{SENSEx} &= I_{OUTPUTx} \ /10 = 1.5 \ mA \ , \\ R_{SENSE1} &= R_{SENSE2} = 2 \ k\Omega \ , \ and \\ I_{OUTPUTx} &\times R_{DS(on)} = 15 \times 35 = 525 \ mV = V_{IN} - V_{OUTPUTx} \ . \end{split}$$

Then:

$$\begin{split} P_D &= 5 \; V \times 5 \; mA \\ &+ \; 0.525 \; V \times 15 \; mA + [5 \; V - (1.5 \; mA \times 2 \; k\Omega)] \times 1.5 \; mA \\ &+ \; 0.525 \; V \times 15 \; mA + [5 \; V - (1.5 \; mA \times 2 \; k\Omega)] \times 1.5 \; mA \\ &= \; 46.75 \; mW \; . \end{split}$$

Substituting in equation 8:

$$\Delta T = 46.75 \text{ mW} \times 140 \text{ }^{\circ}\text{C/W} = 6.5 \text{ }^{\circ}\text{C}$$

Substituting in equation 9:

$$T_{\rm J} = 25^{\circ}{\rm C} + 6.5^{\circ}{\rm C} = 31.5^{\circ}{\rm C}$$

# **Applications Information**

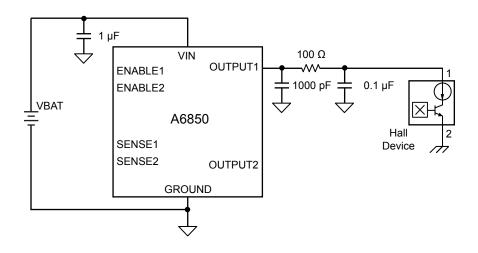

### **Two-Wire Hall IC Interfacing**

Signal and Fault Table

When voltage is applied to two-wire Hall effect ICs, current flows within one of two narrow ranges. Any current level not within these ranges indicates a fault condition. The following table describes some of the possible output conditions that can be monitored through the SENSE pins. Figure 5 is a typical application using the A6850 with dual Hall effect ICs.

| Condition                  | Output Pin Current<br>(mA) | Sense Pin Current<br>(mA) | Sense Pin Voltage,<br>R <sub>sense</sub> = 1.5 kΩ<br>(V) |

|----------------------------|----------------------------|---------------------------|----------------------------------------------------------|

| OUTPUT Pin Short-to-Ground | 25 to 45                   | 2.5 to 4.5                | 3.75 to 6.75                                             |

| Logic High from Hall IC    | 12 to 17                   | 1.2 to 1.7                | 1.8 to 2.55                                              |

| Short-to-Battery           | 0.0                        | 0.0                       | 0                                                        |

| Logic Low from Hall IC*    | 2 to 6.9                   | 0.2 to 0.69               | 0.3 to 1.04                                              |

| Thermal Shutdown           | 0.0                        | 0.0                       | 0                                                        |

| OUTPUT Pin Open            | 0.0                        | 0.0                       | 0                                                        |

\*This current range includes all A114x and A118x devices.

Figure 5. Typical Application with 2-Wire Hall Effect ICs

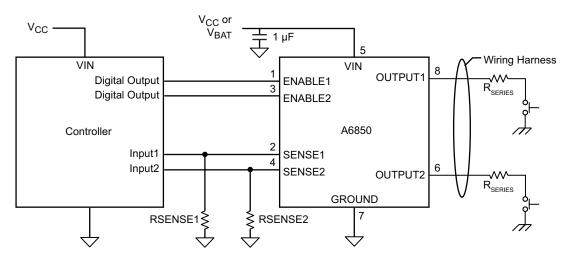

#### **Mechanical Switch Interfacing**

The A6850 can be used as an interface between mechanical switches, set in a switch-to-ground configuration, and a low voltage microprocessor. A series resistor must be placed in the circuit to limit current when the mechanical switch is closed, in order to prevent excessive power dissipation in the A6850.

For example, to calculate the power dissipation in the A6850 driving two mechanical switches with 1 k $\Omega$  series resistors, with V<sub>IN</sub> = 12 V, assume that the current limit for each of the outputs is set to the maximum value, I<sub>OUTPUTM</sub>(max) = 45 mA.

When the mechanical switch is closed without a series resistor, the A6850 will be at the current limit. The full 12 V of the power supply will drop across the A6850 at 45mA The power dissipation for one mechanical switch closed would be:

$$P_{D1} = V_{Drop1} \times I_{OUTPUT1}$$

$$= 12 V \times 45 mA$$

$$= 540 mW$$

(6)

A series resistor included in the circuit reduces power dissipation in the OUTPUTx section of the A6850.

The current is then limited to:

$$I_{\text{OUTPUT1}} = V_{\text{IN}} / (35 + R_{\text{SERIES}})$$

(7)

= 12 V / 1035  $\Omega$

= 11.59 mA

$V_{\text{Drop1}} = 35 \times I_{\text{OUTPUT1}}$ (8)

= 405.7 mV

The power dissipation in the A6850 from this switch is much lower:

$$P_{\text{D1}} = V_{\text{Drop1}} \times I_{\text{OUTPUT1}}$$

(9)

= 0.4057 V × 11.3 mA

= 4.58 mW

Figure 6. Typical Application with Mechanical Switches

### Ganging SENSE1 and SENSE2

In certain applications both outputs may be read with a single ADC channel. The OUTPUTx loads are enabled by alternatively activating ENABLEx. In fact, both ENABLE1

and ENABLE2 may be activated simultaneously, with the SENSE1 and SENSE2 currents added together. For valid measurements the load resistor need only be selected so that  $V_{\text{SENSEx}}$  remain within specification.

Figure 7. Outline of ganged configuration

Figure 8. Functional response in ganged configuration

### **Protection from EMI**

Transients generated by electromagnetic interference (EMI) can disturb operation of the A6850 or add unwanted noise to the signals being processed.

The scheme shown in figure 9 illustrates possible supply decoupling and signal filtering options. The selection of protection and filtering component values will depend on the details of the final application. The A6850 must be protected with a suitable bypass capacitor to prevent transients entering VIN. The capacitor should be as close to the VIN and GND pins as feasible.

A pi-filter placed between the OUTPUTx pins and the sensor IC has been shown to demonstrate excellent performance in normal automotive Bulk Cable Injection (BCI) testing. However, component selection and layout as well as cable specification and placement must be tailored to the individual application. EMC results should be validated.

Figure 9. Decoupling and filtering suggestions

### L Package, 8-Pin SOIC

**Revision Table**

| [ | Number | Date         | Description             |

|---|--------|--------------|-------------------------|

|   | 6      | May 29, 2020 | Minor editorial updates |

Copyright 2020, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website: www.allegromicro.com