### **TDA7803A**

# High efficiency digital input automotive quad power amplifier with built-in diagnostics features, 'start stop' compatible

Datasheet - production data

#### **Features**

- · AEC-Q100 qualified

- · 24-bit digital processing

- 115 dB dynamic range (A-weighted)

- SB-I (SB improved) high efficiency operation the highest 'non class D' efficiency

- · Parallel mode function availability

- High output power capability:

- $-4 \times 27 \text{ W } 4 \Omega @ 14.4 \text{ V}, 1 \text{ kHz}, \text{THD} = 10\%$

- $-4 \times 47 \text{ W } 2 \Omega @ 14.4 \text{ V}, 1 \text{ kHz}, \text{THD} = 10\%$

- Flexible mode control:

- Full I<sup>2</sup>C bus driving 1.8V/3.3V) with four addresses selectable (only for PowerSO36 package option)

- Independent front/rear play/ mute

- Selectable digital gains for very-low noise line-out function

- Digital diagnostic with DC and AC load detections

- Start-stop compatibility (operation down to 6V)

- Sample rates: 44.1 kHz, 48 kHz, 96 kHz, 192 kHz

- Flexible serial data port (1.8 V / 3.3 V):

- I<sup>2</sup>S standard, TDM 4Ch, TDM 8Ch, TDM 16ch (8+8ch)

- Offset detector

- Independent front/rear clipping detector

- Programmable diagnostic pin

- CMOS compatible enable pin

- Thermal protection

- Pop free in mute to play transitions and viceversa

#### **Description**

The TDA7803A is a single chip quad bridge amplifier in advanced BCD technology integrating: a full D/A converter, digital input for direct connection to I<sup>2</sup>S (or TDM) and powerful MOSFET output stages.

The integrated D/A converter allows the performance to reach an outstanding 115 dB S/N ratio with more than 110 dB of dynamic range.

Moreover the TDA7803A integrates an innovative high efficiency concept, optimized also for uncorrelated music signals. The device is designed to be compatible to battery modulation for class-G systems.

Thanks to this concept, the dissipated "output power" under average listening conditions can be reduced up to 50% when compared to the conventional class AB solutions.

The TDA7803A integrates also a programmable PLL that is able to lock at the input frequencies of 64\*Fs for all the input configurations.

The device is equipped with a full diagnostics array that communicates the status of each speaker through the I<sup>2</sup>C bus. The same I<sup>2</sup>C bus allows to control several configurations of the device.

The TDA7803A is able to play music down to 6 V supply voltage - so it is compatible with the so called 'start stop' battery profile recently adopted by several car makers (thus reducing the fuel consumption and the impact over the environment).

Contents TDA7803A

# **Contents**

| 1      | Bloc | ck diagram and pins description 8                  |

|--------|------|----------------------------------------------------|

|        | 1.1  | Block diagram                                      |

|        | 1.2  | Pins description 8                                 |

| 2      | Арр  | lication diagrams                                  |

| 3      | Elec | trical specification                               |

|        | 3.1  | Absolute maximum ratings                           |

|        | 3.2  | Thermal data                                       |

|        | 3.3  | Electrical characteristics                         |

|        | 3.4  | Electrical characteristics typical curves          |

| 4      | Ope  | ration states                                      |

|        | 4.1  | Standby state                                      |

|        | 4.2  | ECO-mode state                                     |

|        | 4.3  | Amplifier-mode state                               |

|        | 4.4  | Turn-on and permanent diagnostic                   |

| 5      | Оре  | ration compatibility vs. battery                   |

| 6      | Fun  | ctional description                                |

|        | 6.1  | Voltage regulators timing                          |

|        | 6.2  | Turn-on diagnostic description                     |

|        | 6.3  | Permanent diagnostic                               |

|        | 6.4  | AC diagnostic                                      |

|        | 6.5  | Input offset detector                              |

|        | 6.6  | Double faults 32                                   |

|        | 6.7  | Thermal protection                                 |

| 3<br>4 | 6.8  | Voltage monitoring feature and ADC characteristics |

|        | 6.9  | Mute management                                    |

|        |      | 6.9.1 Auto-mute threshold                          |

|        |      | 6.9.2 Mute and unmute commutation time             |

TDA7803A Contents

|    | 6.10                | Class SBI - Improved high efficiency principle                |

|----|---------------------|---------------------------------------------------------------|

|    | 6.11                | High power and parallel mode configuration                    |

|    | 6.12                | Power on reset threshold                                      |

| _  |                     |                                                               |

| 7  |                     | tional features                                               |

|    | 7.1                 | Noise gating                                                  |

|    | 7.2                 | Tri-state mode                                                |

| 8  | I <sup>2</sup> S a  | nd TDM bus interface                                          |

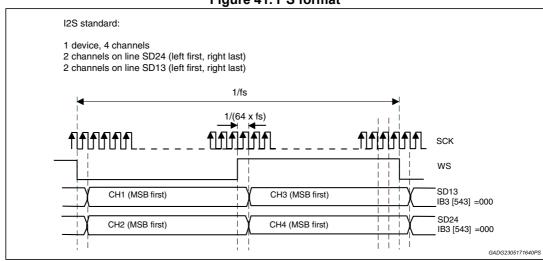

|    | 8.1                 | I <sup>2</sup> S and TDM input data frame format              |

|    | 8.2                 | I <sup>2</sup> S input data format                            |

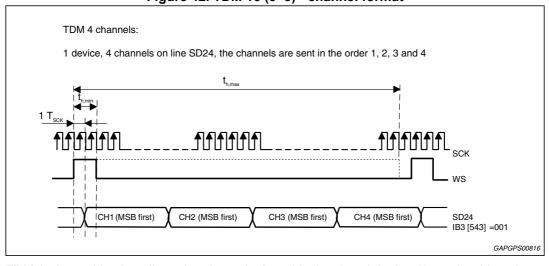

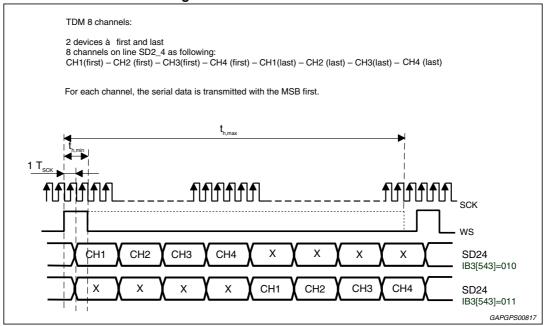

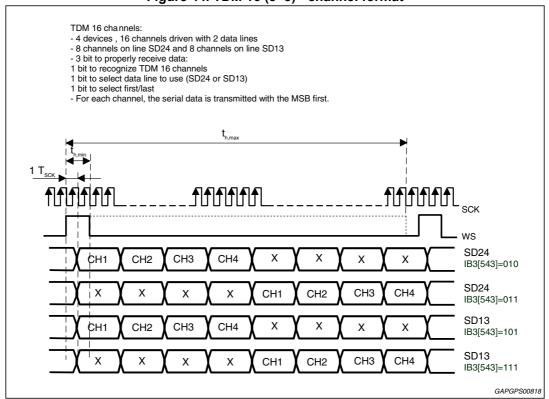

|    | 8.3                 | TDM input data format                                         |

|    | 8.4                 | Timings requirements                                          |

|    | 8.5                 | Group delay                                                   |

| _  | .2                  |                                                               |

| 9  |                     | us interface                                                  |

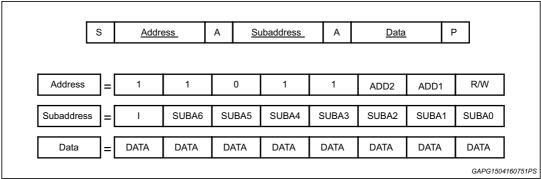

|    | 9.1                 | Writing procedure                                             |

|    | 9.2                 | Reading procedure                                             |

|    | 9.3                 | Data validity                                                 |

|    | 9.4                 | Start and stop conditions 44                                  |

|    | 9.5                 | Byte format                                                   |

|    | 9.6                 | Acknowledge                                                   |

|    | 9.7                 | Address selection                                             |

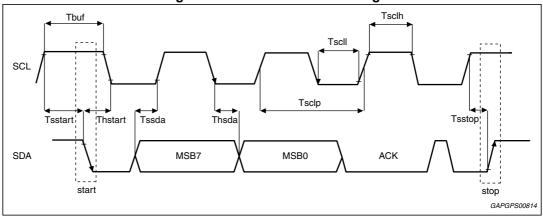

|    | 9.8                 | I <sup>2</sup> C bus timings                                  |

| 10 | l <sup>2</sup> C re | egisters                                                      |

|    | 10.1                | Instruction byte                                              |

|    | -                   | 10.1.1 IB0 - Subaddress "I0000000h" - default = "00000000"    |

|    |                     | 10.1.2 IB1 - Subaddress "I0000001h" - default = "00000000"    |

|    |                     | 10.1.3 IB2 - Subaddress "I0000010h" - default = "00000000"    |

|    |                     | 10.1.4 IB3 - Subaddress "I0000011h" - default = "00000000"    |

|    |                     | 10.1.5 IB4 - Subaddress "I0000100h" - default = "00000000" 50 |

|    |                     | 10.1.6 IB5 - Subaddress "I0000101h" - default = "00000000"    |

|    |                     | 10.1.7 IB6 - Subaddress "I0000110h" - default = "00000000"    |

|    |                     | 10.1.8 IB7 - Subaddress "I0000111h" - default = "00000000"    |

Contents TDA7803A

|    | 10.2  | Data byte 54                                                       |

|----|-------|--------------------------------------------------------------------|

|    |       | 10.2.1 DB0 - Subaddress: "I0010000h"                               |

|    |       | 10.2.2 DB1 - Subaddress: "I0010001h" - Channel 1                   |

|    |       | 10.2.3 DB2 - Subaddress: "I0010010h" - Channel 2                   |

|    |       | 10.2.4 DB3 - Subaddress: "I0010011h" - Channel 3                   |

|    |       | 10.2.5 DB4 - Subaddress: "I0010100h" - Channel 4                   |

|    |       | 10.2.6 DB5 - Subaddress: "I0010101h"                               |

|    |       | 10.2.7 DB6 - Subaddress: "I0010110h"                               |

|    |       | 10.2.8 DB7 - Subaddress: "I0010111h" - Vcc level ADC conversion 60 |

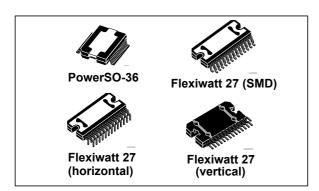

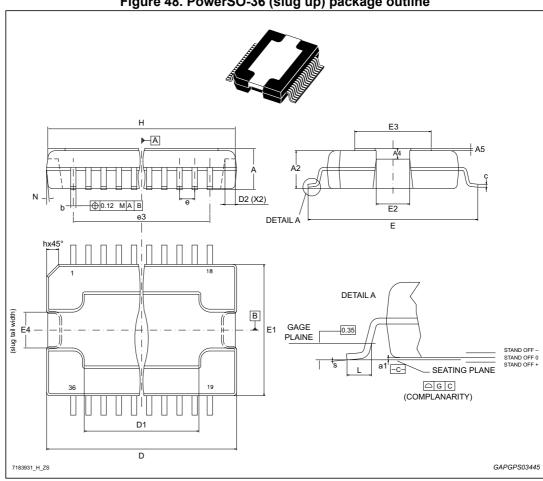

| 11 | Pack  | ge information                                                     |

|    | 11.1  | PowerSO-36 (slug up) package information                           |

|    | 11.2  | Flexiwatt 27 (vertical) package information 63                     |

|    | 11.3  | Flexiwatt 27 (SMD) package information 65                          |

|    | 11.4  | Flexiwatt 27 (horizontal) package information 67                   |

|    | 11.5  | Package marking information                                        |

| 12 | Orde  | codes 70                                                           |

| 13 | Revis | ion history                                                        |

TDA7803A List of tables

# List of tables

| Table 1.  | Flexiwatt27 pins description                                  | . 9 |

|-----------|---------------------------------------------------------------|-----|

| Table 2.  | PowerSO36 pins description                                    | 10  |

| Table 3.  | Absolute maximum ratings                                      | 12  |

| Table 4.  | Thermal data                                                  | 12  |

| Table 5.  | Electrical characteristics                                    | 13  |

| Table 6.  | Start-up pulse typical timings (F <sub>s</sub> = 48 kHz)      | 28  |

| Table 7.  | Double faults priority                                        | 32  |

| Table 8.  | V <sub>CC</sub> value express by 8 bit with thermometric code | 33  |

| Table 9.  | Transition play to mute strategy                              | 34  |

| Table 10. | Mute and unmute commutation time                              | 35  |

| Table 11. | System input frequencies                                      | 38  |

| Table 12. | I <sup>2</sup> S interface timing                             | 41  |

| Table 13. | Address threshold                                             | 45  |

| Table 14. | I <sup>2</sup> C bus interface timing                         |     |

| Table 15. | IB0 - Subaddress "I0000000h" - default = "00000000"           | 46  |

| Table 16. | IB1 - Subaddress "I0000001h" - default = "00000000"           |     |

| Table 17. | IB2 - Subaddress "I0000010h" - default = "00000000"           |     |

| Table 18. | IB3 - Subaddress "I0000011h" - default = "00000000"           |     |

| Table 19. | IB4 - Subaddress "I0000100h" - default = "00000000"           |     |

| Table 20. | IB5 - Subaddress "I0000101h" - default = "00000000"           |     |

| Table 21. | IB6 - Subaddress "I0000110h" - default = "00000000"           |     |

| Table 22. | IB7 - Subaddress "I0000111h" - default = "00000000"           |     |

| Table 23. | DB0 - Subaddress: "I0010000h"                                 |     |

| Table 24. | DB1 - Subaddress: "I0010001h" - Channel 1                     |     |

| Table 25. | DB2 - Subaddress: "I0010010h" - Channel 2                     |     |

| Table 26. | DB3 - Subaddress: "I0010011h" - Channel 3                     |     |

| Table 27. | DB4 - Subaddress: "I0010100h" - Channel 4                     |     |

| Table 28. | DB5 - Subaddress: "I0010101h"                                 |     |

| Table 29. | DB6 - Subaddress: "I0010110h"                                 |     |

| Table 30. | DB7 - Subaddress: "I0010111h" - Vcc level ADC conversion      |     |

| Table 31. | PowerSO-36 (slug up) package mechanical data                  |     |

| Table 32. | Flexiwatt 27 (vertical) package mechanical data               |     |

| Table 33. | Flexiwatt 27 (SMD) package mechanical data                    |     |

| Table 34. | Flexiwatt 27 (horizontal) package mechanical data             |     |

| Table 35. | Ordering information                                          | 70  |

| Table 36. | Document revision history                                     | 71  |

DS12195 Rev 5 5/72

List of figures TDA7803A

# List of figures

| Figure 1.  | Block diagram (Flexiwatt27)                                                                   | . 8 |

|------------|-----------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Pins connection diagrams                                                                      | . 8 |

| Figure 3.  | I <sup>2</sup> C bus mode application diagram (Flexiwatt))                                    | 11  |

| Figure 4.  | I <sup>2</sup> C bus mode application diagram (PowerSO)                                       | 11  |

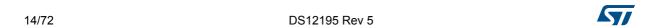

| Figure 5.  | Quiescent current vs. supply voltage                                                          | 17  |

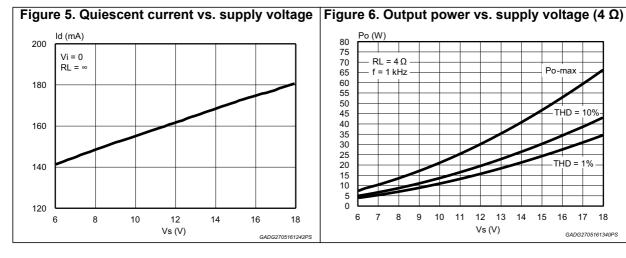

| Figure 6.  | Output power vs. supply voltage (4 $\Omega$ )                                                 | 17  |

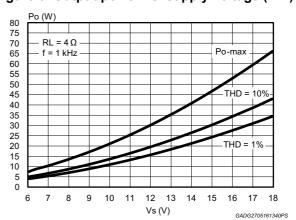

| Figure 7.  | Output power vs. supply voltage (2 Ω, STD mode)                                               |     |

| Figure 8.  | Distortion vs. output power (4 Ω, STD mode)                                                   |     |

| Figure 9.  | Distortion vs. output power (4 Ω, SBI mode)                                                   |     |

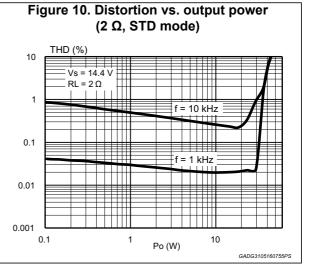

| Figure 10. | Distortion vs. output power (2 Ω, STD mode)                                                   |     |

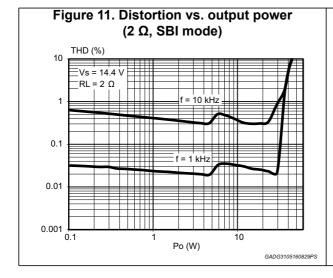

| Figure 11. | Distortion vs. output power (2 Ω, SBI mode)                                                   |     |

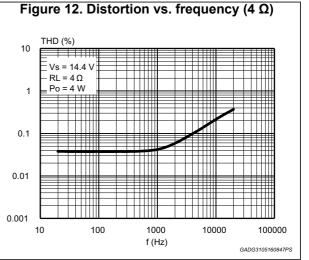

| Figure 12. | Distortion vs. frequency (4 $\Omega$ )                                                        |     |

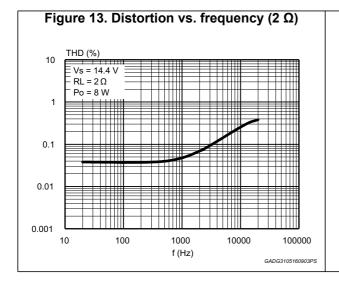

| Figure 13. | Distortion vs. frequency $(2 \Omega)$                                                         |     |

| Figure 14. | Distortion vs. output power (4 $\Omega$ , Vs = 6 V)                                           |     |

| Figure 15. | Distortion vs. output power (2 $\Omega$ , Vs = 6 V)                                           |     |

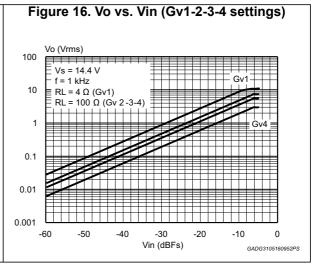

| Figure 16. | Vo vs. Vin (Gv1-2-3-4 settings)                                                               |     |

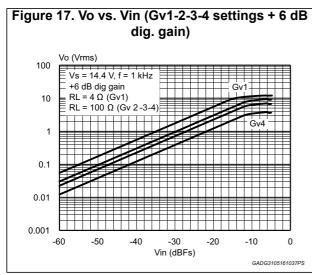

| Figure 17. | Vo vs. Vin (Gv1-2-3-4 settings + 6 dB dig. gain)                                              |     |

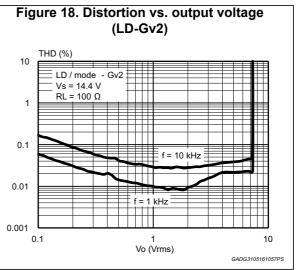

| Figure 18. | Distortion vs. output voltage (LD-Gv2)                                                        |     |

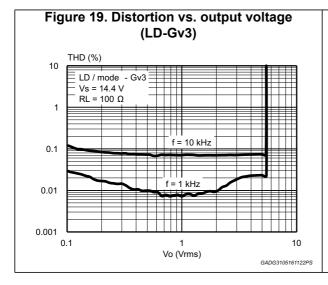

| Figure 19. | Distortion vs. output voltage (LD-Gv3)                                                        |     |

| Figure 20. | Distortion vs. output voltage (LD-Gv4)                                                        |     |

| Figure 21. | Output attenuation vs. Vs                                                                     |     |

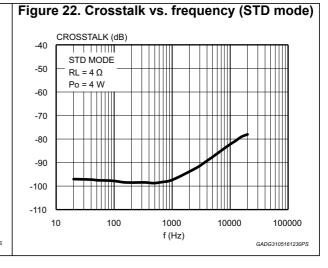

| Figure 22. | Crosstalk vs. frequency (STD mode)                                                            |     |

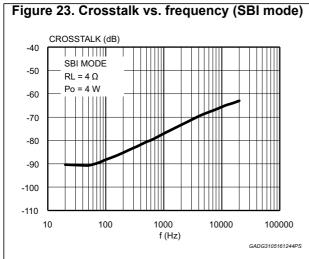

| Figure 23. | Crosstalk vs. frequency (SBI mode)                                                            |     |

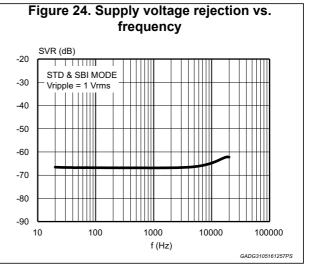

| Figure 24. | Supply voltage rejection vs. frequency                                                        |     |

| Figure 25. | Total power dissipation & efficiency vs. Po (4 Ω, STD, Sine)                                  |     |

| Figure 26. | Total power dissipation & efficiency vs. Po (4 Ω, SBI, Sine)                                  |     |

| Figure 27. | Total power dissipation & efficiency vs. Po (2 Ω, SBI, Sine)                                  |     |

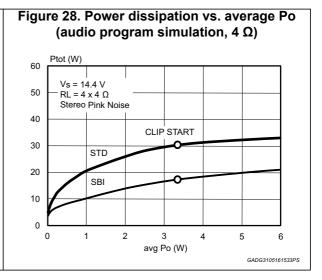

| Figure 28. | Power dissipation vs. average Po (audio program simulation, $4 \Omega$ )                      |     |

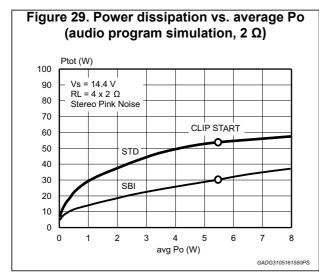

| Figure 29. | Power dissipation vs. average Po (audio program simulation, 2 $\Omega$ )                      |     |

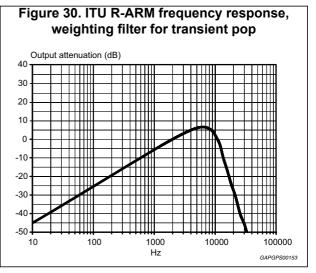

| Figure 30. | ITU R-ARM frequency response, weighting filter for transient pop                              |     |

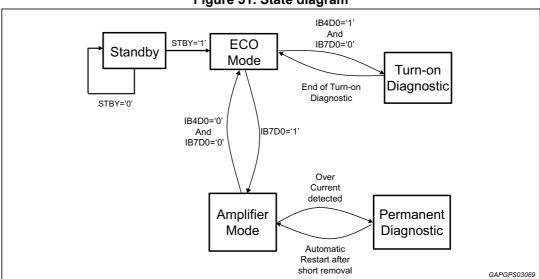

| Figure 31. | State diagram                                                                                 |     |

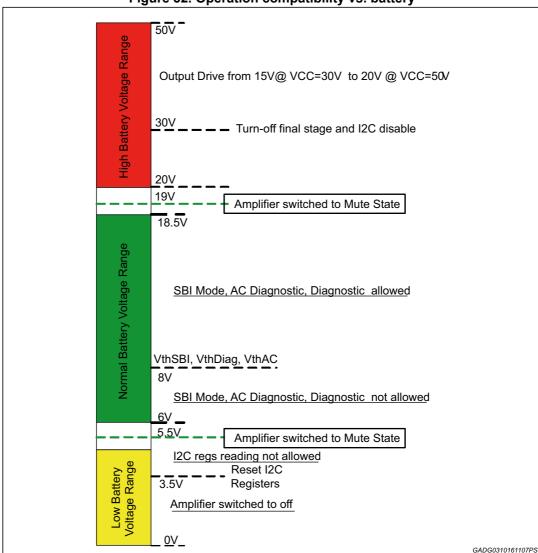

| Figure 32. | Operation compatibility vs. battery                                                           |     |

| Figure 33. | Soft short diagnostic                                                                         |     |

| Figure 34. | Short circuit and open load diagnostic                                                        |     |

| Figure 35. | Short to GND and short to V <sub>s</sub> , threshold description                              |     |

| Figure 36. | Short across the speaker and open load threshold description, in speaker mode                 |     |

| Figure 37. | Short across the speaker and open load threshold description, line driver mode                |     |

| Figure 38. | Permanent diagnostic flow-chart                                                               |     |

| Figure 39. | Thermal muting diagram                                                                        |     |

| Figure 40. | Low voltage mute attenuation, supply voltage variation (Vs); result digital attenuation (At). |     |

| Figure 41. | I <sup>2</sup> S format                                                                       |     |

| Figure 42. | TDM 16 (8+8) - channel format                                                                 |     |

| Figure 43. | TDM 8-channel format                                                                          |     |

| Figure 44. | TDM 16 (8+8) - channel format.                                                                |     |

| Figure 45. | Audio interface timing                                                                        |     |

| Figure 46. | I <sup>2</sup> C bus protocol description                                                     |     |

| Figure 47. | I <sup>2</sup> C bus interface timing                                                         |     |

| Figure 48  | <del>-</del>                                                                                  | 61  |

| TDA7803A   | List of figures                           |

|------------|-------------------------------------------|

| Figure 49. | Flexiwatt 27 (vertical) package outline   |

| Figure 50. | Flexiwatt 27 (SMD) package outline        |

| Figure 51. | Flexiwatt 27 (horizontal) package outline |

#### Block diagram and pins description 1

#### **Block diagram** 1.1

I<sup>2</sup>C CD/DIAG VCC12 VCC34 SDA SCL 25 7 21 26 27 I<sup>2</sup>C ▶ 10 OUT1+ Thermometric 64 x 2 Current Diagn. Fully Balanced PLL generators 8 OUT1array DDWA Thermometric **4** OUT2+ Code Fully Balanced WS Current Conversiio generators 6 OUT2-SCK array DDWA 128 Noise SD24 18 <sub>OUT3+</sub> shaper Code Fully Balanced Current Conversion SD13 ≥20 <sub>OUT3-</sub> array DDWA rmometri 22 <sub>OUT4-</sub> 64 x 2 Current Fully Balanced Conversion ST-BY STBY generators 24 OUT4+ Power Filter array DDWA A2D †<sub>vcc</sub> 16 14 17 15 23 19 9 5 D3V3 DGND PWGND4 PWGND3 PWGND1 PWGND2 A3V3 AGND TAB GAPGPS02388

Figure 1. Block diagram (Flexiwatt27)

#### **Pins description** 1.2

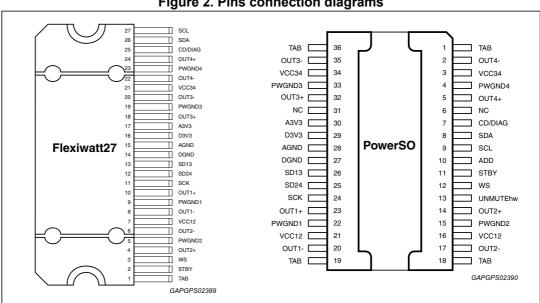

Figure 2. Pins connection diagrams

Table 1. Flexiwatt27 pins description

| N° | Pin Function |                                                     |                   |  |  |

|----|--------------|-----------------------------------------------------|-------------------|--|--|

| 1  | TAB          | TAB connection                                      | Ground            |  |  |

| 2  | STBY         | STBY pin                                            | Input             |  |  |

| 3  | WS           | Word select (I <sup>2</sup> S bus)                  | Logic Input       |  |  |

| 4  | OUT2+        | Channel 2 (Left Rear) positive output               | Power Output      |  |  |

| 5  | PWGND2       | Power ground channels 2                             | Power Ground      |  |  |

| 6  | OUT2-        | Channels 2 (Left Rear) negative output              | Power Output      |  |  |

| 7  | VCC12        | Channel 1 and 2 positive supply                     | Battery           |  |  |

| 8  | OUT1-        | Channel 1 (Left Front) negative output              | Power Output      |  |  |

| 9  | PWGND1       | Power ground channel 1                              | Power Ground      |  |  |

| 10 | OUT1+        | Channel 1 (Left Front) positive output              | Power Output      |  |  |

| 11 | SCK          | Serial clock (I <sup>2</sup> S bus)                 | Logic Input       |  |  |

| 12 | SD24         | Serial data channels 2 and 4 (I <sup>2</sup> S bus) | Logic Input       |  |  |

| 13 | SD13         | Serial data channels 1 and 3 (I <sup>2</sup> S bus) | Logic Input       |  |  |

| 14 | DGND         | Digital ground                                      | Signal Ground     |  |  |

| 15 | AGND         | Analog ground                                       | Signal Ground     |  |  |

| 16 | D3V3         | Digital 3.3V supply filter                          | Digital Regulator |  |  |

| 17 | A3V3         | Analog 3.3V supply filter                           | Analog Regulator  |  |  |

| 18 | OUT3+        | Channels 3 (right front) positive output            | Power Output      |  |  |

| 19 | PWGND3       | Power ground channel 3                              | Power Ground      |  |  |

| 20 | OUT3-        | Channels 3 (right front) negative output            | Power Output      |  |  |

| 21 | VCC34        | Channels 3 and 4 positive supply                    | Battery           |  |  |

| 22 | OUT4-        | Channels 4 (right rear) negative output             | Power Output      |  |  |

| 23 | PWGND4       | Power ground channel 4                              | Power Ground      |  |  |

| 24 | OUT4+        | Channels 4 (right rear) positive output             | Power Output      |  |  |

| 25 | CD/DIAG      | Clip detector and diagnostic output                 | Open Drain Output |  |  |

| 26 | SDA          | I <sup>2</sup> C data                               | Signal Input      |  |  |

| 27 | SCL          | I <sup>2</sup> C clock                              | Signal Input      |  |  |

|    |              |                                                     |                   |  |  |

DS12195 Rev 5 9/72

Table 2. PowerSO36 pins description

| N° | Pin      | Function                                            |                   |  |  |  |

|----|----------|-----------------------------------------------------|-------------------|--|--|--|

| 1  | TAB      | Device slug connection                              | Ground            |  |  |  |

| 2  | OUT4-    | Channels 4 (right rear) negative output             | Power Output      |  |  |  |

| 3  | VCC34    | Channels 3 and 4 positive supply                    | Battery           |  |  |  |

| 4  | PWGND4   | Power ground channel 4                              | Power Ground      |  |  |  |

| 5  | OUT4+    | Channels 4 (right rear) positive output             | Power Output      |  |  |  |

| 6  | NC       | Not connected                                       | -                 |  |  |  |

| 7  | CD/DIAG  | Clip detector and diagnostic output                 | Open Drain Output |  |  |  |

| 8  | SDA      | I <sup>2</sup> C data                               | Signal Input      |  |  |  |

| 9  | SCL      | I <sup>2</sup> C clock                              | Signal Input      |  |  |  |

| 10 | ADD      | I <sup>2</sup> C Address                            | Logic Input       |  |  |  |

| 11 | STBY     | STBY pin                                            | Input             |  |  |  |

| 12 | WS       | Word select (I <sup>2</sup> S bus)                  | Logic Input       |  |  |  |

| 13 | UNMUTEhw | Unmute Hardware                                     | Logic Input       |  |  |  |

| 14 | OUT2+    | Channel 2 (Left Rear) positive output               | Power Output      |  |  |  |

| 15 | PWGND2   | Power ground channels 2                             | Power Ground      |  |  |  |

| 16 | VCC12    | Channel 1 and 2 positive supply                     | Battery           |  |  |  |

| 17 | OUT2-    | Channels 2 (Left Rear) negative output              | Power Output      |  |  |  |

| 18 | TAB      | Device slug connection                              | Ground            |  |  |  |

| 19 | TAB      | Device slug connection                              | Ground            |  |  |  |

| 20 | OUT1-    | Channel 1 (Left Front) negative output              | Power Output      |  |  |  |

| 21 | VCC12    | Channel 1 and 2 positive supply                     | Battery           |  |  |  |

| 22 | PWGND1   | Power ground channel 1                              | Power Ground      |  |  |  |

| 23 | OUT1+    | Channel 1 (Left Front) positive output              | Power Output      |  |  |  |

| 24 | SCK      | Serial clock (I <sup>2</sup> S bus)                 | Logic Input       |  |  |  |

| 25 | SD24     | Serial data channels 2 and 4 (I <sup>2</sup> S bus) | Logic Input       |  |  |  |

| 26 | SD13     | Serial data channels 1 and 3 (I <sup>2</sup> S bus) | Logic Input       |  |  |  |

| 27 | DGND     | Digital ground                                      | Signal Ground     |  |  |  |

| 28 | AGND     | Analog ground                                       | Signal Ground     |  |  |  |

| 29 | D3V3     | Digital 3.3V supply filter                          | Digital Regulator |  |  |  |

| 30 | A3V3     | Analog 3.3V supply filter                           | Analog Regulator  |  |  |  |

| 31 | NC       | Not connected                                       | -                 |  |  |  |

| 32 | OUT3+    | Channels 3 (right front) positive output            | Power Output      |  |  |  |

| 33 | PWGND3   | Power ground channel 3                              | Power Ground      |  |  |  |

| 34 | VCC34    | Channels 3 and 4 positive supply                    | Battery           |  |  |  |

| 35 | OUT3-    | Channels 3 (right front) negative output            | Power Output      |  |  |  |

| 36 | TAB      | Device slug connection                              | Ground            |  |  |  |

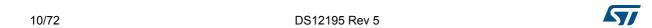

#### 2 **Application diagrams**

C4 = 2.200µF = 1 C3 0.22µF VCC12 STBY OUT RF / OUT3 19 20 OUT RR / OUT4 23 22 TDA7803A 10 OUT LF / OUT1 WS C OUT LR / OUT2 SD13 C A3V3 D3V3 DGND AGND 22µF (\*) Ceramic (X7R) types recommended. CD/DIAG GADG1701170816PS

Figure 3. I<sup>2</sup>C bus mode application diagram (Flexiwatt))

Figure 4. I<sup>2</sup>C bus mode application diagram (PowerSO)

1. Refer to Section 9: I<sup>2</sup>C bus interface for connection suggestions.

577

# 3 Electrical specification

### 3.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol                            | Parameter                                            | Value                                | Unit |

|-----------------------------------|------------------------------------------------------|--------------------------------------|------|

| V <sub>S</sub>                    | DC supply voltage                                    | -0.3 to 28                           | V    |

| V <sub>peak</sub>                 | Transient supply voltage for t = 100 ms              | -0.3 to 50                           | V    |

| V <sub>i2c</sub>                  | I <sup>2</sup> C bus pins voltage                    | -0.3 to 4.6                          | V    |

| V <sub>i2s</sub>                  | I <sup>2</sup> S bus pins voltage                    | -0.3 to 4.6                          | V    |

| V <sub>unmute</sub>               | Unmute hardware voltage (PSO36 only)                 | -0.3 to 4.6                          | V    |

| V <sub>cd</sub>                   | CD/Diag pin voltage                                  | -0.3 to 20                           | V    |

| V <sub>stby</sub>                 | STBY pin voltage                                     | -0.3 to 4.6                          | V    |

| Io                                | Output peak current (repetitive f > 10 Hz)           | internally<br>limited <sup>(1)</sup> | А    |

| P <sub>tot</sub>                  | Power dissipation T <sub>case</sub> = 70 °C          | 85                                   | W    |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and junction temperature                     | -55 to 150                           | °C   |

| T <sub>amb</sub>                  | Operative temperature range <sup>(2)</sup>           | -40 to 105                           | °C   |

| C <sub>max</sub>                  | Maximum capacitor vs. ground connected to the output | 4.7                                  | nF   |

| ESD <sub>HBM</sub>                | ESD protection HBM <sup>(3)</sup>                    | 2000                                 | V    |

| ESD <sub>CDM</sub>                | ESD protection CDM (3)                               | 500                                  | V    |

<sup>1.</sup> Internally limited by overcurrent protection.

#### 3.2 Thermal data

Table 4. Thermal data

| Symbol                 | Parameter                                  | Value | Unit |

|------------------------|--------------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal resistance junction-to-case (max.) | 1     | °C/W |

<sup>2.</sup> A suitable heatsink/dissipation system should be used to keep  $T_i$  inside the specified limits.

<sup>3.</sup> Conforming to Q100 ESD standard.

### 3.3 Electrical characteristics

Referred to the test setup  $V_S$  = 14.4 V;  $R_L$  = 4  $\Omega$ ; f = 1 kHz; tested at  $T_{amb}$  = 25 °C; functionality guaranteed for  $T_j$  = -40 °C to 150 °C; SB-I mode; unless otherwise specified.

**Table 5. Electrical characteristics**

| Symbol                  | Parameter                                                                          | Test condition                                            | Min. | Тур.  | Max. | Unit |

|-------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------|------|-------|------|------|

| General                 |                                                                                    | 1                                                         |      |       | ı    | I    |

|                         |                                                                                    | R <sub>L</sub> = 4 Ω                                      | 6    | -     | 18.5 | V    |

| $V_S$                   | Supply voltage range                                                               | R <sub>L</sub> = 2 Ω, std_bridge                          | 6    | -     | 16   | V    |

|                         |                                                                                    | $R_L = 2 \Omega$ , SBI                                    | 6    | -     | 16   | V    |

| I <sub>SB</sub>         | Standby current                                                                    | -                                                         | -    | 1     | 4    | μA   |

| Iq                      | Total quiescent current in amplifier mode                                          | Mute condition                                            | -    | 170   | 210  | mA   |

| I <sub>qECO</sub>       | Total quiescent current in ECO mode                                                | ECO mode                                                  | -    | 35    | 40   | mA   |

| A <sub>M</sub>          | Mute attenuation                                                                   | -                                                         | 80   | -     | -    | dB   |

| V <sub>OS</sub>         | Offset voltage                                                                     | Mute and play                                             | -25  | -     | +25  | mV   |

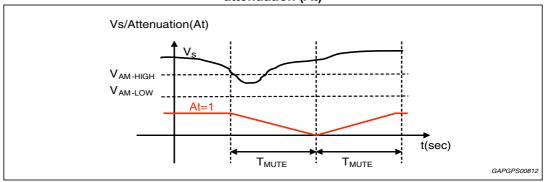

| V                       | V <sub>CC</sub> low supply mute threshold (Min I <sup>2</sup> C setting - default) | Attenuation <0.5 dB, digital mute disabled                | -    | -     | 5.6  | V    |

| $V_{lowM}$              |                                                                                    | Attenuation ≥60 dB, digital mute disabled                 | 5    | -     | -    | V    |

| V <sub>POWONRESET</sub> | Supply voltage of power-on reset                                                   | -                                                         | -    | 3.5   | -    | V    |

| V <sub>highM</sub>      | High supply mute threshold                                                         | Attenuation = -6 dB                                       | 19   | -     | 21   | V    |

| Audio perfor            | mances                                                                             |                                                           |      |       |      |      |

|                         | Output nower                                                                       | $R_L$ = 4 Ω; max power <sup>(1)</sup>                     | 40   | 43    | -    | W    |

|                         |                                                                                    | THD = 10 %                                                | 25   | 27    | -    | W    |

| P <sub>O</sub>          |                                                                                    | THD = 1 %                                                 | 20   | 22    | -    | W    |

| 10                      | Output power                                                                       | R <sub>L</sub> = 2 Ω; THD 10%                             | 44   | 47    | -    | W    |

|                         |                                                                                    | R <sub>L</sub> = 2 Ω; THD 1%                              | 34   | 37    | -    | W    |

|                         |                                                                                    | $R_L$ = 2 Ω; max power <sup>(1)</sup>                     | 69   | 72    | -    | W    |

|                         |                                                                                    | P <sub>O</sub> = 4 W, f=1 kHz, G <sub>V1</sub>            | -    | 0.015 | 0.04 | %    |

| THD <sub>SB</sub>       | Total harmonic distortion                                                          | P <sub>O</sub> = 4 W, f=10 kHz, G <sub>V1</sub>           | -    | 0.15  | 0.5  | %    |

| 11.122R                 | (Standard bridge)                                                                  | $R_L$ =100 Ω input=-10 dBFS,<br>f = 1 kHz, $G_{V1,2,3,4}$ | -    | 0.01  | 0.02 | %    |

| TUD                     | Total harmonic distortion                                                          | P <sub>O</sub> = 2 W, f = 1 kHz, G <sub>V1</sub>          | -    | 0.015 | 0.04 | %    |

| THD                     | (SBI mode)                                                                         | P <sub>O</sub> = 6 W, f =1 kHz, G <sub>V1</sub>           | -    | 0.02  | 0.06 | %    |

**Table 5. Electrical characteristics (continued)**

| Symbol                        | Parameter                                                                                                     | Test condition                                          | Min.               | Тур.     | Max.    | Unit |

|-------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------|----------|---------|------|

| (2)                           |                                                                                                               | f = 1 kHz                                               | -                  | 100      | -       | dB   |

| C <sub>T</sub> <sup>(2)</sup> | Cross talk                                                                                                    | f = 10 kHz                                              | -                  | 80       | -       | dB   |

| G <sub>V1</sub>               | Voltage gain 1                                                                                                |                                                         | 2.3                | 2.5      | -       | Vp   |

| G <sub>V2</sub>               | Voltage gain 2                                                                                                | A acceptance 40 dDE-                                    | 1.25               | 1.35     | -       | Vp   |

| G <sub>V3</sub>               | Voltage gain 3                                                                                                | @ Amplitude = -18 dBFs                                  | 0.9                | 1        | -       | Vp   |

| G <sub>V4</sub>               | Voltage gain 4                                                                                                |                                                         | 0.4                | 0.55     | -       | Vp   |

| DR <sup>(2)</sup>             | Dynamic range                                                                                                 | A-wtd values, G <sub>V1</sub> gain                      | -                  | 115      | -       | dB   |

| E <sub>out1</sub>             | Output noise voltage $G_V = G_{V1}$ $G_V = G_{V4}$                                                            | A-wtd values                                            |                    | 27<br>18 | 40<br>- | μV   |

| E <sub>out2</sub>             | Output noise voltage $G_V = G_{V1}$ $G_V = G_{V4}$                                                            | ITU-R 468                                               |                    | 70<br>45 | 96<br>- | μV   |

| SNR <sup>(2)</sup>            | Signal to noise ratio                                                                                         | A-wtd values, G <sub>V1</sub> gain                      | -                  | 115      | -       | dB   |

| ΔG <sub>v</sub>               | Channel Gain Mismatch                                                                                         | -                                                       | -0.5               | -        | 0.5     | dB   |

| SSR                           | Supply slew rate                                                                                              | -                                                       | -                  | 1        | -       | V/µs |

| PSRR                          | Power supply rejection ratio                                                                                  | f = 1 kHz;<br>V <sub>r</sub> = 1 Vpk;                   | 60                 | 70       | -       | dB   |

| 14V 1                         | ITU Pop filter output voltage (standard bridge mode)                                                          | Eco mode to mute transition and vice versa              | -                  | -        | 4       | mV   |

| ΔV <sub>OITU</sub>            |                                                                                                               | Mute to Play and Play to Mute transition <sup>(3)</sup> | -                  | 0        | -       | mV   |

| Clipping det                  | ector                                                                                                         |                                                         |                    |          |         |      |

| CD <sub>LK</sub>              | Clip det high leakage current                                                                                 | CD off, V = 3.3 V                                       | -                  | 0        | 1       | μА   |

| CD <sub>SAT</sub>             | Clip det sat. voltage                                                                                         | CD on; I <sub>CD</sub> = 1 mA                           | -                  | 50       | -       | mV   |

| CD1 <sub>THD</sub>            | Clip det THD threshold 1                                                                                      | -                                                       | -                  | 2        | 3       | %    |

| CD2 <sub>THD</sub>            | Clip det THD threshold 2                                                                                      | -                                                       | 4                  | 6        | 8       | %    |

| CD3 <sub>THD</sub>            | Clip det THD threshold 3                                                                                      | -                                                       | 9                  | 12       | 14      | %    |

| Turn on diag                  | nostics for parallel mode con                                                                                 | figuration                                              |                    |          |         |      |

| Pgnd                          | Short to GND det. (below this limit, the output is considered in short circuit to GND)                        | -                                                       | -                  | -        | 1       | V    |

| P <sub>vs</sub>               | Short to V <sub>S</sub> det. (above this limit, the output is considered in short circuit to V <sub>S</sub> ) | -                                                       | V <sub>s</sub> - 1 | -        | -       | V    |

**Table 5. Electrical characteristics (continued)**

|                      | Table 5. Electrical characteristics (continued)                                                  |                |                    |      |                    |      |  |  |

|----------------------|--------------------------------------------------------------------------------------------------|----------------|--------------------|------|--------------------|------|--|--|

| Symbol               | Parameter                                                                                        | Test condition | Min.               | Тур. | Max.               | Unit |  |  |

| Pnop                 | Normal operation thresholds. (within these limits, the output is considered without faults).     | -              | 2                  | -    | V <sub>s</sub> - 2 | V    |  |  |

| Lsc                  | Shorted load det.                                                                                | -              | -                  | -    | 0.7                | Ω    |  |  |

| Lop                  | Normal load det.                                                                                 | -              | 1.3                | -    | 30                 | Ω    |  |  |

| Lnop                 | Open load det.                                                                                   | -              | 70                 | -    | -                  | Ω    |  |  |

| Turn-on diag         | nostic for parallel mode conf                                                                    | iguration      |                    |      |                    |      |  |  |

| Lsc                  | Shorted load det.                                                                                | -              | -                  | -    | 0.35               | Ω    |  |  |

| Lop                  | Normal load det.                                                                                 | -              | 0.65               | -    | 15                 | Ω    |  |  |

| Lnop                 | Open load det.                                                                                   | -              | 35                 | -    | -                  | Ω    |  |  |

| Rss                  | Soft Short Diagnostic<br>threshold (below this value,<br>soft short resistance is<br>recognized) | -              | 500                | -    | -                  | Ω    |  |  |

| Turn-on diag         | nostic for line driver mode co                                                                   | onfiguration   | •                  |      |                    |      |  |  |

| Pgnd                 | Short to GND det. (below this limit, the output is considered in short circuit to GND)           | -              | -                  | -    | 1                  | V    |  |  |

| Pvs                  | Short to $V_s$ det. (above this limit, the output is considered in short circuit to $V_s$ )      | -              | V <sub>s</sub> - 1 | -    | -                  | V    |  |  |

| Pnop                 | Normal operation thresholds. (within these limits, the output is considered without faults).     | -              | 2                  | -    | V <sub>s</sub> - 2 | V    |  |  |

| Lsc                  | Shorted load det.                                                                                | -              | -                  | -    | 20                 | Ω    |  |  |

| Lop                  | Normal load det.                                                                                 | -              | 60                 | -    | 1400               | Ω    |  |  |

| Lnop                 | Open load det.                                                                                   | -              | 2600               | -    | -                  | Ω    |  |  |

| Rss                  | Soft Short Diagnostic<br>threshold (below this value,<br>soft short resistance is<br>recognized) | -              | 5.8 <sup>(4)</sup> | -    | -                  | kΩ   |  |  |

| AC-diagnost          | tic                                                                                              |                | •                  |      |                    |      |  |  |

|                      | AC diagnostic current                                                                            | IB4 – D4= '0'  | 250                | 375  | 500                | mA   |  |  |

| I <sub>ACTRESH</sub> | threshold                                                                                        | IB4 – D4= '1'  | 125                | 187  | 250                | mA   |  |  |

|                      | <u> </u>                                                                                         | L              | •                  |      |                    |      |  |  |

**Table 5. Electrical characteristics (continued)**

| Symbol                     | Parameter                                                                                   | Test condition                                                                   | Min.               | Тур.   | Max.               | Unit |  |  |

|----------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------|--------|--------------------|------|--|--|

| Permanent o                | diagnostics                                                                                 |                                                                                  |                    |        |                    |      |  |  |

| Pgnd                       | Short to GND det. (below this limit, the output is considered in short circuit to GND)      | Power amplifier in Mute or Play, one or more short circuits protection activated | -                  | -      | 1                  | V    |  |  |

| Pvs                        | Short to $V_s$ det. (above this limit, the Output is considered in short circuit to $V_s$ ) | -                                                                                | V <sub>s</sub> - 1 | -      | -                  | V    |  |  |

| Pnop                       | Normal operation thresholds. (Within these limits, the output is considered without faults) | -                                                                                | 2                  | -      | V <sub>s</sub> - 2 | V    |  |  |

|                            |                                                                                             | Parallel mode                                                                    | -                  | -      | 0.35               |      |  |  |

| $L_{SC}$                   | Shorted load det.                                                                           | Speaker mode                                                                     | -                  | -      | 0.7                | Ω    |  |  |

|                            |                                                                                             | Line driver mode                                                                 | -                  | -      | 20                 |      |  |  |

| L <sub>OP</sub>            | Normal load det.                                                                            | Parallel mode                                                                    | 0.65               | -      | -                  |      |  |  |

|                            |                                                                                             | Speaker mode                                                                     | 1.3                | -      | -                  | Ω    |  |  |

|                            |                                                                                             | Line driver mode                                                                 | 60                 | -      | -                  |      |  |  |

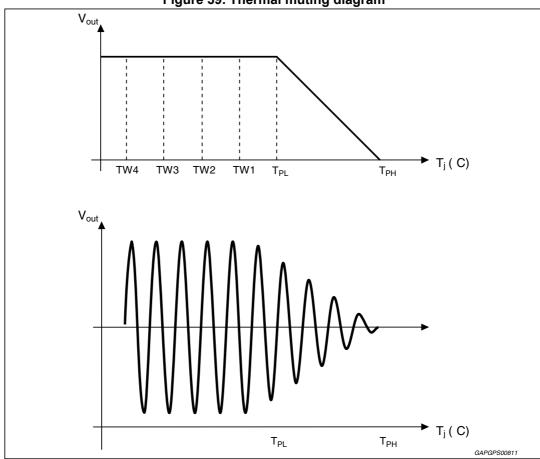

| T <sub>ph</sub>            | Thermal protection junction                                                                 | Attenuation ≥60 dB                                                               | -                  | 165    | -                  | °C   |  |  |

| T <sub>pl</sub>            | temperature                                                                                 | Attenuation <0.5 dB                                                              | -                  | 155    | -                  | °C   |  |  |

| T <sub>w1</sub>            |                                                                                             | -                                                                                | -                  | Tpl-5  | -                  | °C   |  |  |

| T <sub>w2</sub>            | Thermal warning junction                                                                    | -                                                                                | -                  | Tpl-10 | -                  | °C   |  |  |

| T <sub>w3</sub>            | temperature <sup>(5)</sup>                                                                  | -                                                                                | -                  | Tpl-20 | -                  | °C   |  |  |

| T <sub>w4</sub>            |                                                                                             | -                                                                                | -                  | Tpl-30 | -                  | °C   |  |  |

| I <sup>2</sup> C bus inter | rface                                                                                       |                                                                                  | !                  |        |                    |      |  |  |

| f <sub>SCL</sub>           | Clock frequency                                                                             | -                                                                                | _                  | -      | 400                | kHz  |  |  |

| V <sub>IL</sub>            | Input low voltage                                                                           | -                                                                                | -                  | -      | 0.8                | V    |  |  |

| V <sub>IH</sub>            | Input high voltage                                                                          | -                                                                                | 1.3                | -      | -                  | V    |  |  |

|                            | Maximum I2C data pin low                                                                    | I <sub>sink</sub> = 2 mA                                                         | -                  | -      | 0.27               | V    |  |  |

| $V_{olmax}$                | voltage when current Isink is sinked                                                        | I <sub>sink</sub> = 8 mA                                                         | -                  | -      | 0.7                | V    |  |  |

| I <sub>limax</sub>         | Maximum input leakage current                                                               | V = 3.6 V                                                                        | -                  | -      | 1                  | μA   |  |  |

| STBY pin                   |                                                                                             |                                                                                  |                    |        |                    |      |  |  |

| V <sub>ILSTBY</sub>        | Input low voltage                                                                           | -                                                                                | -                  | -      | 1.2                | V    |  |  |

| V <sub>IHSTBY</sub>        | Input high voltage                                                                          | -                                                                                | 2.4                | -      | -                  | V    |  |  |

Table 5. Electrical characteristics (continued)

| Symbol                 | Parameter                 | Test condition                     | Min. | Тур. | Max. | Unit |  |  |  |  |

|------------------------|---------------------------|------------------------------------|------|------|------|------|--|--|--|--|

| I <sub>ILSTBY</sub>    | Logic '0' output current  | V <sub>IN</sub> = 0.45 V           | -    | -    | 1    | μΑ   |  |  |  |  |

| I <sub>IHSTBY</sub>    | Logic '1' input current   | V <sub>IN</sub> = 2.3 V (IB0 D4=0) | -    | -    | 1    | μΑ   |  |  |  |  |

| I <sup>2</sup> S pins  | I <sup>2</sup> S pins     |                                    |      |      |      |      |  |  |  |  |

| V <sub>IL-I2S</sub>    | Input low voltage         | -                                  | -    | -    | 0.8  | V    |  |  |  |  |

| V <sub>IH-I2S</sub>    | Input high voltage        | -                                  | 1.3  | -    | -    | ٧    |  |  |  |  |

| I <sub>IH</sub>        | Input high current        | @ V <sub>I</sub> = 3.3 V           | -    | -    | 1    | μΑ   |  |  |  |  |

| I <sub>IL</sub>        | Input low current         | @ V <sub>I</sub> = 0 V             | -    | -    | 1    | μΑ   |  |  |  |  |

| Unmute hard            | ware (pin 13)             |                                    |      |      |      |      |  |  |  |  |

| V                      | Hardware unmute threshold | Attenuation ≥60 dB                 | -    | -    | 1.2  | V    |  |  |  |  |

| V <sub>HW_UNMUTE</sub> | (PSO36 only)              | Attenuation <0.5 dB                | 2.6  | -    | -    | ٧    |  |  |  |  |

| l                      | Input high current        | @ V <sub>I</sub> = 3.3 V           | -    | -    | 1    | μΑ   |  |  |  |  |

| IUNMUTE                | Input low current         | @ V <sub>I</sub> = 0 V             | -    | -    | 1    | μΑ   |  |  |  |  |

- 1. Square-wave input / saturated output.

- 2. Evaluated at bench during product validation.

- 3. Guaranteed by design (intrinsically immune from any pop at mute to play and play to mute transitions)

- The values are the ones that guarantee the correct working of the diagnostic. Since the value is strongly dependent on the loudspeaker, we decided to target the values for the limits of open load and short load diagnostic.

- 5. Thermal warning junction temperature values could be changed via I<sup>2</sup>C bits IB5-d6,d7.

#### 3.4 **Electrical characteristics typical curves**

Figure 8. Distortion vs. output power (4  $\Omega$ , STD mode)

THD (%)

Vs = 14.4 V

RL = 4  $\Omega$ 0.01

0.001

Po (W)

GADG3009161544PS

Figure 9. Distortion vs. output power

(4 Ω, SBI mode)

10

THD (%)

Vs = 14.4 V

RL = 4Ω

1

0.01

0.01

0.01

Po (W)

GADG3105160725PS

577

Figure 14. Distortion vs. output power  $(4 \Omega, Vs = 6 V)$ 10

THD (%)

Vs = 6 V

11

O.1

O.01

O.01 f = 10 kHzPo (W)

GADG3105160917PS

Figure 20. Distortion vs. output voltage (LD-Gv4)

10 THD (%)

10 Vs = 14.4 V

11 RL = 100 Ω

10 O.001

10 Vo (Vrms)

Figure 21. Output attenuation vs. Vs 10 STD = SBI MODE 0 RL = 4 Ω Vo = 2 Vrms -10 -20 -30 -40 NORMAL START-STOP -50 -60 -70 -80 -90 8 6 9 10 Vs (V)

57

Figure 25. Total power dissipation & efficiency vs. Po (4 Ω, STD, Sine) Ptot (W) Vs = 14.4 V RL =  $4 \times 4\Omega$ f = 1 kHz SINEη STD mode Ptot Po (W) GADG0803170956PS

Figure 26. Total power dissipation & efficiency vs. Po (4 Ω, SBI, Sine) η (%) Ptot (W) Vs = 14.4 V RL = 4 x 4Ω η = 1 kHz SINE SBI mode Ptot Λ 0.1 Po (W) GADG0803171132PS

Figure 27. Total power dissipation & efficiency vs. Po (2 Ω, SBI, Sine) Ptot (W) Vs = 14.4 V  $RI = 4 \times 20$ f = 1 kHz SINE SBI mode Ptot 12 14 16 18 20 22 24 26 28 Po (W)

Operation states TDA7803A

### 4 Operation states

TDA7803A functionality is regulated by means of a finite state machine.

Finite state machine diagram is reported in *Figure 31*.

Main states are:

- Standby

- ECO-mode

- Amplifier mode

- Turn-on diagnostic

- Permanent diagnostic

#### 4.1 Standby state

When STBY pin is under VILSTBY voltage the amplifier is in stand-by state and the current consumption is very low.

#### 4.2 ECO-mode state

When STBY pin is over VIHSTBY the amplifier is in a state of low current absorption, the ECO-mode. The short circuit protections are active and the amplifier is ready for receiving commands from micro-controller through I<sup>2</sup>C interface.

Outputs and A3V3 supply are biased at 0 V.

### 4.3 Amplifier-mode state

When TDA7803A is in ECO-mode state, IB7-d0 is set to "1", (Amplifier-ON), and I<sup>2</sup>S clock is present the amplifier moves to Amplifier-mode state.

The outputs are biased from 0 V to Vcc/2 and the current consumption reaches "Iq" level until the amplifier is set in MUTE or in PLAY with low level signal. User can move the amplifier from MUTE to PLAY and viceversa acting on IB2-d4, d3 bits.

A hardware unmute pin is available in PSO36 package only.

### 4.4 Turn-on and permanent diagnostic

TDA7803A provides a powerful and precise diagnostic both with speaker and line driver loads.

There are two main diagnostic states:

- Turn-on diagnostic

- Permanent diagnostic.

The Turn-on diagnostic could be run in ECO-mode state and is suggested for sensing the presence of faults before amplifier turn-on, in order to avoid unwanted or dangerous conditions due to wrong connections or absence of load.

TDA7803A Operation states

The Permanent diagnostic is automatically run by TDA7803A when a fault occurs during PLAY and over current protections are triggered.

Turn-on and Permanent diagnostic functionality are described in Section 6.

Figure 31. State diagram

## 5 Operation compatibility vs. battery

Here below the operation compatibility vs. the battery value is shown. For each battery voltage range, only a limited number of functions are available as it is shown below:

Figure 32. Operation compatibility vs. battery

### 6 Functional description

#### 6.1 Voltage regulators timing

Pins D3V3 and A3V3 are respectively digital and analog internal regulators outputs. The D3V3 rises right after the STBY pin is at the logical value "1" and its rising time depends on the filter capacitor; the minimum value suggested for this filter is  $4.7 \, \mu F$ .

The A3V3 rises after any command that moves the amplifier from ECO - mode; the rising time depends on the combined effect of the external capacitor on the pin and of an internal 2 ms ramp: if the capacitor value is  $22~\mu F$  or lower, the internal ramp effect is dominant and the rising time will be about 2 ms. On the other hand, when the capacitor has a higher value, the rise time will be higher as well. The suggested value for this capacitor is  $22~\mu F$  at least.

#### 6.2 Turn-on diagnostic description

The turn-on diagnostic is triggered on the rising edge of bit IB4 D0 when IB7 D0 is "0". This happens when the amplifier is in ECO - mode. It is possible to run one or more turn-on diagnostic sequences according to the following procedure:

- 1. wait the previous cycle is over

- 2. read the data bytes DB1,DB2,DB3 and DB4

Please note that all these instructions must be sent while the amplifier is still in ECO - mode (IB7 D0 = "0"), otherwise they won't be executed.

Turn-on diagnostic does not start if  $V_{CC}$  is below 8 V or one of the muting condition is present, (low battery mute, high voltage mute, PLL-unlock mute, thermal mute, hardware pin mute).

Note:

The diagnostic enable bit (IB4 D0) must be set before the amplifier mode bit (IB7 D0). DB1, DB2, DB3 must be read before DB4 (after DB4 is read the DB1-2-3-4 are reset).

The detected faults are here described:

**Soft Short to GND**: it detects the presence of a resistor (see *Table 5* in "Turn-on diagnostic" section) connected between an output and ground, which could result in a wrong open load or short across load diagnostic result (causing an anomalous current consumption in some cases).

**Soft Short to VS**: it detects the presence of a resistor (see *Table 5* in "Turn-on diagnostic" section) connected between an output and battery, which could result in a wrong open load or short across load diagnostic result (causing an anomalous current consumption in some cases).

**Short to GND**: it detects the hard connection between an output and ground. The value of the short is able to pull the output between 1.5 V and ground.

**Short to VS**: it detects the hard connection between an output and battery. The value of the short is able to pull the output between (battery - 1.5 V) and battery.

**Short across the speaker**: it detects the hard connection across the speaker that is below a certain value. This value guarantees that the IC is able to drive any speaker configuration within the range specified in the datasheet.

DS12195 Rev 5 25/72

Open Load: it detects a non connected speaker condition.

The diagnostic's results are stored into DB1, DB2, DB3 and DB4 data registers (one for each channel) after the diagnostic is over.

The flow of the diagnostic includes some steps as described below.

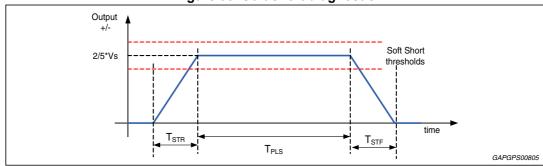

• During the first part, the soft-short evaluation is performed. The outputs and an internal reference line are pulled up to a voltage of 2/5\*Vbattery in a time TSTR and then compared for a time TPLS. During the plateau time, the comparator outputs are read from the digital part. The outputs are then pulled down to zero (see *Figure 33*). The A3V3 supply is 0V and the output stage is in tri-state during this phase.

Figure 33. Soft short diagnostic

• If a soft short is detected, the short to GND/VCC evaluation follows. Pin A3V3 goes up as the amplifier stage is turned on; the power and the outputs are risen up to 1/2\*V<sub>battery</sub> and then compared to (V<sub>battery</sub> - 1.5 V) and 1.5 V for a time TPLS. At the end of the plateau (TPLS) output and A3V3 go back to 0V and the results obtained are written into the I<sup>2</sup>C Bus registers once the diagnostic is over. For soft short resistance above the defined thresholds, the normal, short or open load recognition is guaranteed.

In case the short to VCC or GND is detected during this phase a '1' is written in DBx-D1/D0 (VCC/GND) but not in DBx-D6. In case the hard short is not detected a '1' is written all DBx-D6.

The turn-on diagnostic is then completed and the amplifier goes back to the ECO - mode.

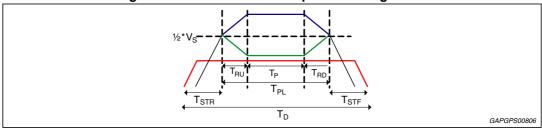

- However, if a soft short is not detected, then we can also exclude the Short to Vs/GND, and don't need to be checked. In this case, short across the speaker and the open load evaluation can be performed. Pin A3V3 goes up as the amplifier stage is turned on and the outputs are risen up to 1/2\*V<sub>battery</sub>. A first pulse for "Short load detection" is done: exploiting the presence of a D/A converter, a subsonic (inaudible) voltage pulse is digitally and internally generated and converted. The pulse amplitude increasing is stopped when the current flowing through the speaker I<sub>speaker</sub> is the same as a prefixed one I<sub>high</sub> (high current) or because it reaches the maximum value permitted. Since the differential output voltage V<sub>o</sub> is well known, it is possible to keep monitored the value of the connected speaker during the transition and plateau. In the case the I<sub>speaker</sub> will get to an higher value then I<sub>high</sub>, V<sub>o</sub>< V<sub>short</sub> (short circuit threshold) the result is short load (DBx D3 = '1'), otherwise it is normal load (DBx D3 = '0'); when I<sub>speaker</sub> does not reach I<sub>high</sub> the turn-on diagnostic is not completed yet because the result could be still normal or open load.

- This is called "Open load detection". If IB4 D1/D2 = 1 the power DMOS need to be changed again: the outputs are pulled down to zero, the DMOS are switched and then the outputs raised up to 1/2\*V<sub>battery</sub> again. This sequence is done in order to avoid any pop noise during the power set. The procedure is the same as the previous case or in

case of IB4 (D1/D2) = 0. The pulse amplitude is stopped when the current flowing through the speaker  $I_{speaker}$  is the same as prefixed one  $I_{low}$  (low current) or because it reaches the maximum value permitted. When  $I_{speaker}$  reaches the value  $I_{low}$  and  $V_o < V_{open}$  (open load threshold) then the speaker can be considered as a normal load (DBx-D2='0'). In all other cases the result will be open load (DBx-D2='1') (see *Figure 34*).

Figure 34. Short circuit and open load diagnostic

The whole diagnostic time depends on the number of pulses that are done. At least two pulses are done, but they could be three in case of open load. The values inserted into the Table 6, are calculated basing on Fs = 48000 Hz.

In all cases the fault is sent out to the registers only if it is stable throughout the whole plateau period. If this condition is not respected, any possible misconnections (Soft-short, Short to VCC/GND, Short Across or Open Load) won't be reported. The faults for the turn-on diagnostic are written in DB (1, 2, 3, 4) (D1, D2, D3, D4) (a byte for each channel and a bit for each fault). They are consistent if DB0 D6 = "1". After a reading the data byte are reset.

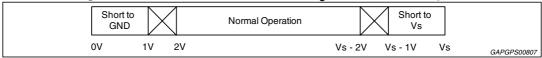

The fault-detection thresholds for short to GND/ Vs remain unchanged independently from the gain setting. They are as in *Figure 35*.

Figure 35. Short to GND and short to V<sub>s</sub>, threshold description

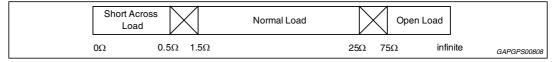

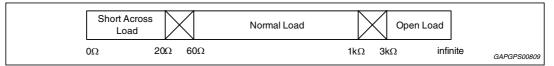

Concerning the short across the speaker / open speaker, the threshold changes from line driver mode and speaker mode diagnostic setting, as load expected are pretty different (either normal speaker's impedance or high impedance). Speaker or line driver mode is selectable from IB4 D2 for channels 1 and 3 and IB4 D1 for channel 2 and 4. The values in case of speaker mode are as in *Figure 36*. The same thresholds will change as in *Figure 37*, if line driver mode diagnostic is selected.

Figure 36. Short across the speaker and open load threshold description, in speaker mode

57

DS12195 Rev 5 27/72

Figure 37. Short across the speaker and open load threshold description, line driver mode

Table 6. Start-up pulse typical timings ( $F_s = 48 \text{ kHz}$ )

| Symbol                           | Parameter                                                            | Min | Тур                | Max                  | Unit | Note                                                                                                         |

|----------------------------------|----------------------------------------------------------------------|-----|--------------------|----------------------|------|--------------------------------------------------------------------------------------------------------------|

| T <sub>STR</sub>                 | Time to rise the outputs from 0V to a certain battery's percentage   | -   | 10 (+ 10)          | -                    | ms   | When A3V3 goes up, the reported number has to be added                                                       |

| T <sub>STF</sub>                 | Time to rise the outputs from a certain battery's percentage to 0V   | -   | 10 (+ 10)          | -                    | ms   | When A3V3 goes down, the reported number has to be added                                                     |

| T <sub>PLS</sub>                 | Plateau time for soft-short<br>and short to VCC/GND<br>diagnostic    | -   | 80                 | -                    | ms   | This time parameter is load independent and is not stretchable setting bit IB6[7:5]                          |

| _                                | Plateau time for short circuit or open load                          |     | 80 <sup>(1)</sup>  |                      |      | $T_P$ = 86 ms · X<br>when 140 ms - 2 · $T_{RU}$ > 80 ms                                                      |

| T <sub>P</sub>                   | diagnostic detection phase                                           | -   | 80 (1)             | -                    | ms   | $T_P = (140 \text{ ms} - 2 \cdot T_{RU}) \cdot X$<br>when 140 ms - 2 · $T_{RU}$ < 80 ms                      |

| T <sub>PL</sub>                  | Pulse time for short circuit or open load diagnostic detection phase | -   | 120                | 122.4 <sup>(2)</sup> | ms   | $T_{P} = (2 \cdot T_{RU} + T_{P}) \cdot X$                                                                   |

| Х                                | Multiplier factor in case of diagnostic active                       | -   | 1,2,4,8            | -                    | -    | IB6[7:5] setting                                                                                             |

|                                  | Ramp-up and ramp-down                                                | -   | 5.8 <sup>(3)</sup> | -                    | -    | 2 ohm case                                                                                                   |

| T <sub>RU</sub> =T <sub>RD</sub> | diagnostic pulse's time                                              | -   | 8.3 <sup>(3)</sup> | -                    | ms   | 4 ohm case                                                                                                   |

| T <sub>SS</sub>                  | Soft-short diagnostic time                                           | -   | 100                | -                    | ms   | Output rising time + Output falling time + plateau time (no A3V3)                                            |

| T <sub>HS</sub>                  | Short to VCC and GND diagnostic time                                 | -   | 120                | -                    | ms   | A3V3 rising and falling time<br>(10 ms x2) + Output rising and falling<br>time + plateau time                |

| _                                | Short load and open load                                             | -   | 148                | -                    | ms   | 2 ohm case (X=1)                                                                                             |

| T <sub>D</sub>                   | diagnostic time                                                      | -   | 160                | -                    | ms   | 4 ohm case (X=1)                                                                                             |

|                                  |                                                                      | -   | 260                | -                    | ms   | 4 ohm load and no faults<br>(T <sub>tot</sub> = T <sub>SS</sub> + T <sub>D</sub> )                           |

| T <sub>tot</sub>                 | Total diagnostic time                                                | -   | 220                | -                    | ms   | Hard or soft short to supplies (T <sub>tot</sub> = T <sub>SS</sub> + T <sub>HS</sub> )                       |

|                                  |                                                                      | -   | 420                | -                    | ms   | Open load (X = 1, IB4 (D1/D2) = 0)<br>T <sub>tot</sub> = T <sub>SS</sub> + T <sub>D1</sub> + T <sub>D2</sub> |

| Symbol            | Parameter                             | Min | Тур       | Max | Unit | Note                                     |

|-------------------|---------------------------------------|-----|-----------|-----|------|------------------------------------------|

| I <sub>high</sub> | Test current for the short load pulse | -   | 200<br>40 | -   | mA   | For speaker mode<br>For line driver mode |

| I <sub>low</sub>  | Test current for the open load pulse  | -   | 40<br>2   | -   | mA   | For speaker mode<br>For line driver mode |

Table 6. Start-up pulse typical timings ( $F_s = 48 \text{ kHz}$ ) (continued)

- 1. For typical loudspeaker of 2 and 4 ohm.

- 2. These numbers are evaluated in simulation.

- 3. Typical values for 4  $\Omega$  and 2  $\Omega$  and zero offset. These numbers depend on the loudspeaker and also on the intrinsic offset of the amplifier. For 2  $\Omega$  loudspeaker, -30 mV offset and Fs = 48 kHz  $T_{RU}$  = 21.2 ms; for 4  $\Omega$  and same surrounding conditions  $T_{RU}$  = 22.1 ms. Under these conditions  $T_{PL}$  = 122.4 ms for 2  $\Omega$  and 124.4 for 4  $\Omega$ . For higher values the number are not reported here.

When the amplifier is biased and the IB4 D0 = "1", the permanent diagnostic is enabled. The turn-on diagnostic state is held until an over current event is triggered. When this happens, a new diagnostic cycle can start.

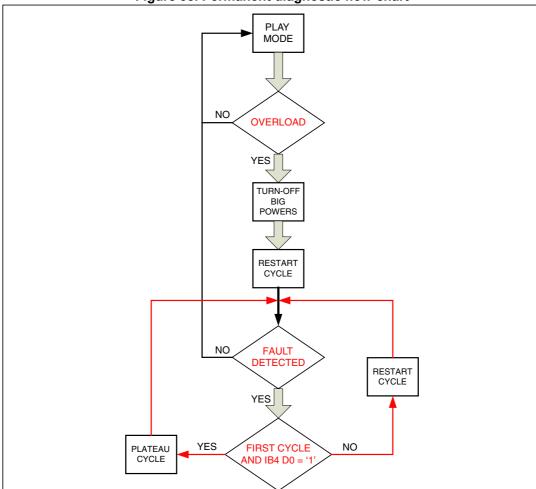

#### 6.3 Permanent diagnostic

The detectable faults are (see *Table 5* for definitions):

- Short to GND

- Short to Vs

- Short across the speaker

Then following additional features are also provided:

- Input offset detection

- AC diagnostic

When an over current event occurs, TDA7803A has two different cycles that could react with:

- Restart cycle: it is a 2 ms pulse. During this period a check of the output is performed.

- Plateau cycle: it is an 80 ms cycle. During this period a check of the outputs is performed and the results of diagnostic analysis are written into the I<sup>2</sup>C bus.

TDA7803A has two different operating behaviors when an over current event is detected:

- Restart mode, (IB4 D0 = "0"). The diagnostic is not enabled. Each audio channel operates independently from each other. If any of the above mentioned faults occurs, only the channel(s) where the fault happened is shut down. The diagnostic performs restart cycles every 2 ms until the fault condition is present. The amplifier restarts in play only once the overload is removed. In Restart mode reporting diagnostic results are turned off and the corresponding bits in the channels' data byte registers will be reset accordingly.