# 5.5V Input, 1.8A/3.1A Switch Buck-Boost Converter with 6µA I<sub>O</sub>

#### **General Description**

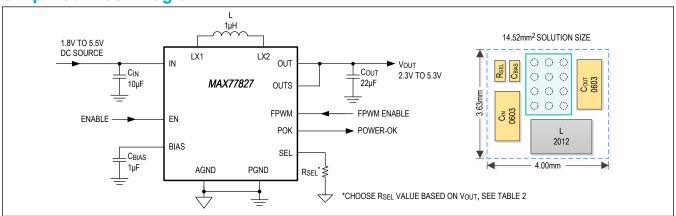

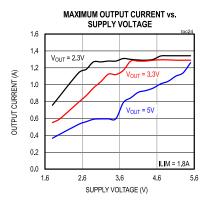

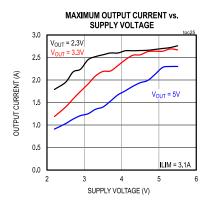

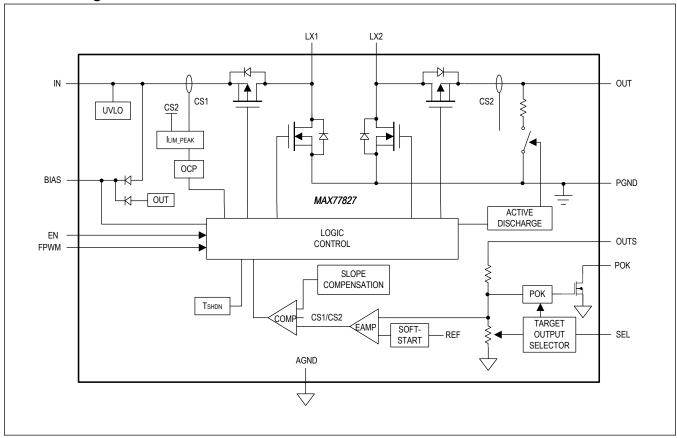

The MAX77827 is a high-efficiency buck-boost regulator targeted for one-cell Li-ion powered applications with the lowest typical quiescent current in the industry of  $6\mu A$ . It supports input voltages of 1.8V to 5.5V and an output voltage range of 2.3V to 5.3V. The IC provides two different switching current levels (1.8A and 3.1A) to optimize external component sizing based on given load current requirements. With the 1.8A switching current-limit option, the IC can support up to 1.0A load current in buck mode and 900mA in boost mode ( $V_{IN}$  = 3.0V,  $V_{OUT}$  = 3.3V).

The peak efficiency of 96% makes the IC one of the best solutions as a DC/DC converter to supply a rail for battery-powered portable applications.

The IC features an adjustable output voltage, which can be programmed from 2.3V to 5.3V through a single resistor. Two GPIO pins are available to support force PWM enable function and power-OK (POK) indicator. A unique control algorithm allows high-efficiency, outstanding line/load transient response, and seamless transition between buck and boost modes. These options provide design flexibility that allow the IC to cover a wide range of applications and use cases while minimizing board space.

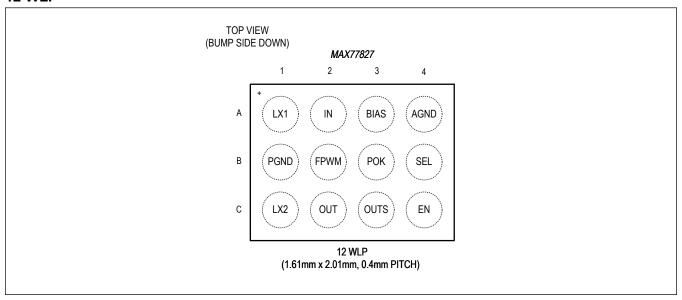

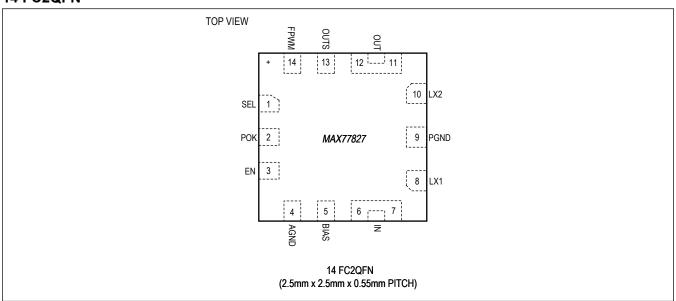

The MAX77827 is available in a 1.61mm x 2.01mm, 12-bump wafer-level package (WLP), and a 2.5mm x 2.5mm, 14-lead FC2QFN package.

## **Applications**

- 1-Cell Li+ Battery Powered Equipment

- Smartphones/Portable/Wearables

- Internet of Things (IoT) Devices

- LPWAN (LTE/NB-IoT, LTE/Cat-M1)

#### **Benefits and Features**

- 1.8V to 5.5V Input Voltage Range

- 2.3V to 5.3V Single Resistor Adjustable Output Voltage

- 1.6A Maximum Output Current (3.1A I<sub>LIM</sub> Option, Buck Mode)

- 900mA Maximum Output Current (1.8A I<sub>LIM</sub> Option, Boost Mode 3.0V<sub>IN</sub>, 3.3V<sub>OUT</sub>)

- 96% Peak Efficiency (3.3V<sub>IN</sub>, 3.3V<sub>OUT</sub>)

- SKIP Mode for Higher Light-Load Efficiency

- 6μA Ultra-Low Typical Quiescent Current (At T<sub>J</sub> = +25°C)

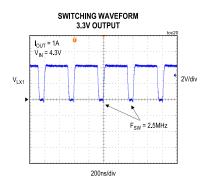

- 2.5MHz Nominal Switching Frequency

- Enable Pin

- GPIO Pins for System Design Convenience

- FPWM (Forced PWM) Mode Selection Pin

- POK Indicator Pin

- UVLO, Soft-Start, Active-Output Discharge, Overcurrent, and Thermal Shutdown Protections

- 1.61mm x 2.01mm, 12-Bump WLP

- 2.5mm x 2.5mm, 14-Lead FC2QFN

Ordering Information appears at end of data sheet.

## **Simplified Block Diagram**

# 5.5V Input, 1.8A/3.1A Switch Buck-Boost Converter with $6\mu A I_Q$

#### **TABLE OF CONTENTS**

| General Description               |    |

|-----------------------------------|----|

| Applications                      | 1  |

| Benefits and Features             | 1  |

| Simplified Block Diagram          | 1  |

| Absolute Maximum Ratings          | 6  |

| Package Information               | 6  |

| 12 WLP                            | 6  |

| 14 FC2QFN                         | 6  |

| Electrical Characteristics        | 7  |

| Typical Operating Characteristics | 9  |

| Pin Configurations                | 12 |

| 12 WLP                            | 12 |

| 14 FC2QFN                         | 12 |

| Pin Description                   |    |

| Functional Diagrams               |    |

| Function Diagram                  |    |

| Detailed Description              |    |

| Start Up                          |    |

| Immediate Shutdown Conditions     |    |

| Power Down                        |    |

| Buck-Boost Regulator              |    |

| Buck-Boost Control Scheme         |    |

| Output Voltage Configuration      |    |

| FPWM Mode Enable                  |    |

| Power-OK (POK) Indicator          |    |

| Protection Features               |    |

| Undervoltage Lockout (UVLO)       |    |

| Soft-Start                        |    |

| Output Active Discharge           |    |

| Overcurrent Protection (OCP)      |    |

| Thermal Shutdown                  |    |

| Applications Information          |    |

| Inductor Selection                |    |

| Input Capacitor Selection         |    |

| Output Capacitor Selection        |    |

| PCB Layout Guidelines             |    |

| Typical Application Circuits      |    |

| Typical Application Circuit       | 22 |

# 5.5V Input, 1.8A/3.1A Switch Buck-Boost Converter with 6µA I<sub>Q</sub>

| TABLE OF CONTENTS (CONTINUED) |      |

|-------------------------------|------|

| Ordering Information          | . 23 |

| Revision History              | . 24 |

# 5.5V Input, 1.8A/3.1A Switch Buck-Boost Converter with 6µA I<sub>Q</sub>

| LIST OF FIGURES                                       |    |  |  |  |

|-------------------------------------------------------|----|--|--|--|

| Figure 1. Start-Up Waveform                           | 15 |  |  |  |

| Figure 2. Buck-Boost H-Bridge Topology                | 17 |  |  |  |

| Figure 3. Short-Circuit Waveform                      | 19 |  |  |  |

| Figure 4. PCB Layout Example (WLP—B and D Options)    | 21 |  |  |  |

| Figure 5. PCB Layout Example (FC2QFN—B and D Options) | 22 |  |  |  |

# 5.5V Input, 1.8A/3.1A Switch Buck-Boost Converter with 6µA I<sub>Q</sub>

| LIST OF TABLES                            |      |

|-------------------------------------------|------|

| Table 1. I <sub>LIM</sub> Levels          | . 15 |

| Table 2. R <sub>SEL</sub> Selection Table | . 17 |

| Table 3. Inductor Recommendations         | . 20 |

# 5.5V Input, 1.8A/3.1A Switch Buck-Boost Converter with 6µA I<sub>Q</sub>

## **Absolute Maximum Ratings**

| IN, OUT, BIAS to PGND0.3V to +6V PGND to AGND0.3V to +0.3V | Maximum Junction Temperature+150°C<br>Storage Temperature Range65°C to +150°C |

|------------------------------------------------------------|-------------------------------------------------------------------------------|

| EN, SEL, FPWM, POK to AGND0.3V to V <sub>BIAS</sub> + 0.3V | Soldering Temperature (reflow)+260°C                                          |

| FB to AGND0.3V to V <sub>OUT</sub> + 0.3V                  | Continuous Power Dissipation                                                  |

| LX1 to PGND0.3V to +6.0V                                   | WLP Package ( $T_A = +70^{\circ}C$ , derate 13.73mW/°C above                  |

| LX2 to PGND0.3V to +6.0V                                   | +70°C)1098.4mW                                                                |

| IN, LX1, LX2, OUT Continuous RMS current                   | FC2QFN Package (T <sub>A</sub> = +70°C, derate 15.77mW/°C above               |

| Operating Junction Temperature Range40°C to +125°C         | +70°C)1261.8mW                                                                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### **12 WLP**

| Package Code                                       | W121H2+1         |  |  |

|----------------------------------------------------|------------------|--|--|

| Outline Number                                     | <u>21-100302</u> |  |  |

| Land Pattern Number Refer to Application Note 1891 |                  |  |  |

| Thermal Resistance, Four-Layer Board:              |                  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )             | 72.82 C°/W       |  |  |

| Junction to Case (θ <sub>JC</sub> )                | N/A              |  |  |

#### **14 FC2QFN**

| Package Code                           | F142A2F+1        |  |  |  |

|----------------------------------------|------------------|--|--|--|

| Outline Number                         | <u>21-100382</u> |  |  |  |

| Land Pattern Number                    | 90-100127        |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 63.4°C/W         |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | N/A              |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{IN} = 3.8V, V_{OUT} = 3.3V, typicals are at T_A \approx T_J = +25^{\circ}C$ . Limits are 100% production tested at  $T_J = +25^{\circ}C$ . Limits over the operating temperature range  $(T_J = -40^{\circ}C \text{ to } +125^{\circ}C)$  are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                      | SYMBOL                             | CONDITIONS                                                                                                                         | MIN  | TYP  | MAX  | UNITS  |  |

|--------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|--|

| GENERAL                        |                                    |                                                                                                                                    |      |      |      | ,      |  |

| In and Mallana Danasa          | .,                                 | For A and D options                                                                                                                | 1.8  |      | 5.5  | .,     |  |

| Input Voltage Range            | V <sub>IN</sub>                    | For B and C options                                                                                                                | 2.6  |      | 5.5  | - V    |  |

| Shutdown Supply                |                                    | EN = Low, T <sub>J</sub> = +25°C                                                                                                   |      | 0.1  | 2    |        |  |

| Current                        | ISHDN                              | EN = Low, T <sub>J</sub> = -40°C to +125°C (Note 2)                                                                                |      | 3    | 8    | μA     |  |

| Innut Cumply Cumpnt            | I <sub>Q_SKIP</sub>                | SKIP mode, no switching                                                                                                            |      | 6    | 14   | μA     |  |

| Input Supply Current           | I <sub>Q_PWM</sub>                 | FPWM mode, no load, no switching                                                                                                   |      | 2    | 6    | mA     |  |

| Active Discharge<br>Resistance | R <sub>DISCHG</sub>                |                                                                                                                                    |      | 100  |      | Ω      |  |

| Thermal Shutdown               | T <sub>SHDN</sub>                  | Rising, +20°C hysteresis                                                                                                           |      | 165  |      | °C     |  |

| H-BRIDGE                       | •                                  |                                                                                                                                    |      |      |      | •      |  |

| Output Voltage Range           | V <sub>OUT</sub>                   | External resistor programmable                                                                                                     | 2.3  |      | 5.3  | V      |  |

| • • • • • • •                  | V                                  | PWM mode, T <sub>J</sub> = +25°C                                                                                                   | -1   |      | +1   |        |  |

| Output Voltage<br>Accuracy     | V <sub>OUT_ACC1</sub>              | PWM mode, T <sub>J</sub> = -40°C to +125°C                                                                                         | -2   |      | +2   | %      |  |

| 7 toodraby                     | V <sub>OUT_ACC2</sub>              | SKIP mode, no load, T <sub>J</sub> = +25°C                                                                                         | -1   |      | +4.5 |        |  |

| Line Regulation                |                                    | V <sub>IN</sub> = 1.8V to 5.5V (for A and D options)                                                                               |      | 0.4  |      | %/V    |  |

| Line Regulation                |                                    | V <sub>IN</sub> = 2.6V to 5.5V (for B and C options)                                                                               |      | 0.4  |      |        |  |

| Load Regulation                |                                    | Note 1                                                                                                                             |      | 0.25 |      | %/A    |  |

| Line Transient<br>Response     | V <sub>OS1</sub> /V <sub>US1</sub> | I <sub>OUT</sub> = 0.5A, V <sub>IN</sub> changes from 3.4V to 2.9V in 25μs (20mV/μs), L = 1μH, C <sub>OUT_NOM</sub> = 8μF (Note 1) |      | 50   |      | mV     |  |

| Load Transient<br>Response     | V <sub>OS2</sub> /V <sub>US2</sub> | $I_{OUT}$ changes from 10mA to 0.5A in 15 $\mu$ s, L = 1 $\mu$ H, C <sub>OUT_NOM</sub> = 8 $\mu$ F (Note 1)                        |      | 250  |      | mV     |  |

| LX1/2 Current Limit            |                                    | $T_J$ = -40°C to +125°C, for A and C options                                                                                       | 2.5  | 3.1  | 3.7  |        |  |

| LX 1/2 Current Limit           | I <sub>LIM_LX</sub>                | $T_J$ = -40°C to +125°C, for B and D options                                                                                       | 1.3  | 1.8  | 2.3  | Α      |  |

| High-Side PMOS On Resistance   | R <sub>DSON_P</sub>                | I <sub>LX</sub> = 100mA per switch                                                                                                 | 10   |      | 130  | mΩ     |  |

| Low-Side NMOS On<br>Resistance | R <sub>DSON_N</sub>                | I <sub>LX</sub> = 100mA per switch                                                                                                 | 15   |      | 110  | mΩ     |  |

| Switching Frequency            | f <sub>SW</sub>                    | PWM mode, T <sub>J</sub> = +25°C                                                                                                   | 2.25 | 2.5  | 2.75 | N41.1- |  |

|                                |                                    | PWM mode, $T_J = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$                                                                    | 2.2  | 2.5  | 2.8  | MHz    |  |

| Turn-On Delay Time             | ton_dly                            | From EN asserting to SEL detection (Note 2)                                                                                        |      | 100  |      | μs     |  |

| SEL Detection Time             | t <sub>SEL</sub>                   | After turn-on delay to LX switching (Note 2)                                                                                       |      | 600  |      | μs     |  |

## **Electrical Characteristics (continued)**

$(V_{IN} = 3.8V, V_{OUT} = 3.3V, typicals are at T_A \approx T_J = +25^{\circ}C$ . Limits are 100% production tested at  $T_J = +25^{\circ}C$ . Limits over the operating temperature range  $(T_J = -40^{\circ}C \text{ to } +125^{\circ}C)$  are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                               | SYMBOL               | CONDITIONS                                                       |                                                             | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------|----------------------|------------------------------------------------------------------|-------------------------------------------------------------|------|------|------|-------|

| Soft-Start Time                         | Fimo to a            | After SEL detection to soft-start timer                          | I <sub>OUT</sub> = 10mA (Note<br>1), for B and D<br>options |      | 1500 |      |       |

| Soit-Start Time                         | t <sub>SS</sub>      | finish                                                           | I <sub>OUT</sub> = 10mA (Note<br>1), for A and C<br>options |      | 200  |      | - µs  |

| Minimum Effective<br>Output Capacitance | C <sub>EFF_MIN</sub> | 0A < I <sub>OUT</sub> < 1A                                       |                                                             |      | 8    |      | μF    |

| LX1, LX2 Leakage<br>Current             | I <sub>LK_85</sub>   | $V_{LX1/2} = 0V \text{ or } 5.5V,$<br>5.5V, $T_J = +85^{\circ}C$ | V <sub>OUT</sub> = 5.5V, V <sub>IN</sub> =                  |      | 0.1  | 2    | μA    |

|                                         | V                    | SYS rising, options E                                            | 3 and C                                                     | 2.4  | 2.5  | 2.6  |       |

| SYS Undervoltage-                       | $V_{UVLO_R}$         | SYS rising, options A                                            | A and D                                                     | 1.70 | 1.75 | 1.80 | V     |

| Lockout Threshold                       | V                    | SYS falling, options                                             | B and C                                                     | 1.9  | 2.05 | 2.2  | ]     |

|                                         | V <sub>UVLO_F</sub>  | SYS falling, options                                             | A and D                                                     | 1.62 | 1.68 | 1.74 |       |

| ENABLE INPUT (EN)                       |                      |                                                                  |                                                             |      |      |      |       |

| EN Logic-Low Threshold                  | $V_{EN\_L}$          |                                                                  |                                                             |      |      | 0.4  | V     |

| EN Logic-High<br>Threshold              | V <sub>EN_H</sub>    |                                                                  |                                                             | 1.3  |      |      | V     |

| FPWM INPUT                              |                      |                                                                  |                                                             |      |      |      |       |

| FPWM Logic-Low<br>Threshold             | V <sub>IL</sub>      |                                                                  |                                                             |      |      | 0.4  | V     |

| FPWM Logic-High<br>Threshold            | $V_{IH}$             |                                                                  |                                                             | 1.3  |      |      | V     |

| FPWM Internal<br>Pulldown Resistance    | R <sub>PD</sub>      | Pulldown resistor to GND                                         |                                                             | 400  | 800  | 1600 | kΩ    |

| POK OUTPUT                              |                      |                                                                  |                                                             |      |      |      |       |

| POK Output Low<br>Voltage               | V <sub>POK_L</sub>   | I <sub>SINK</sub> = 1mA                                          |                                                             |      |      | 0.4  | V     |

| POK Output High<br>Leakage              | I <sub>POK_25C</sub> | T <sub>J</sub> = +25°C                                           |                                                             | -1   |      | +1   | μA    |

| DOK Three hold                          | 'POK_R   of \        | V <sub>OUT</sub> rising, express of V <sub>OUT</sub>             | sed as a percentage                                         |      | 92.5 |      | - %   |

| POK Threshold                           | l <sub>POK_</sub> F  | V <sub>OUT</sub> falling, express<br>of V <sub>OUT</sub>         | sed as a percentage                                         |      | 90   |      | 70    |

**Note 1:** Guaranteed by ATE characterization. Not directly tested in production.

Note 2: Guaranteed by design. Production tested through scan.

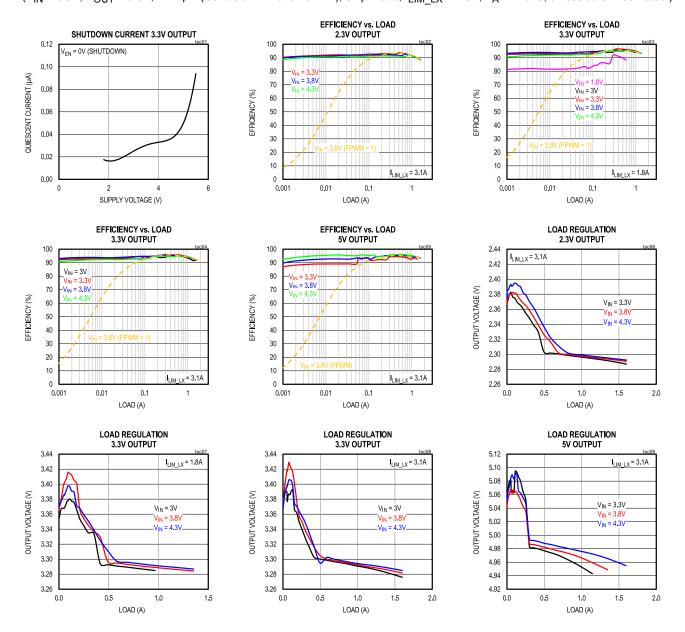

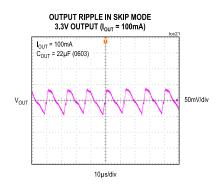

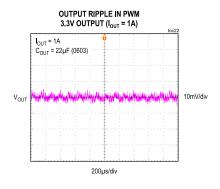

## **Typical Operating Characteristics**

$(V_{IN} = 3.8V, V_{OUT} = 3.3V, L = 1\mu H (Coilcraft XAL4020-102ME), Skip Mode, I_{LIM} LX = 1.8A, T_A = +25°C, unless otherwise noted.)$

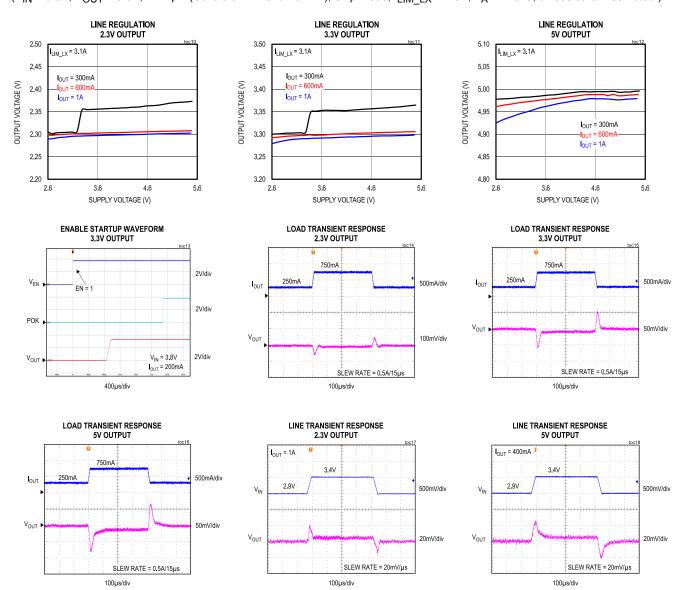

## **Typical Operating Characteristics (continued)**

$(V_{IN} = 3.8V, V_{OUT} = 3.3V, L = 1\mu H (Coilcraft XAL4020-102ME), Skip Mode, I_{LIM} LX = 1.8A, T_A = +25^{\circ}C, unless otherwise noted.)$

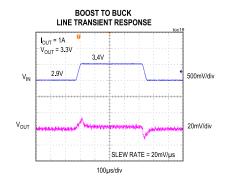

## **Typical Operating Characteristics (continued)**

$(V_{IN} = 3.8V, V_{OUT} = 3.3V, L = 1 \mu H \text{ (Coilcraft XAL4020-102ME)}, Skip \text{ Mode, } I_{LIM\_LX} = 1.8A, T_A = +25 ^{\circ}\text{C}, unless \text{ otherwise noted.)}$

# **Pin Configurations**

#### **12 WLP**

#### **14 FC2QFN**

# 5.5V Input, 1.8A/3.1A Switch Buck-Boost Converter with 6µA I<sub>Q</sub>

# **Pin Description**

| F      | PIN       | NAME   | NAME FUNCTION                                                  |                |  |

|--------|-----------|--------|----------------------------------------------------------------|----------------|--|

| 12 WLP | 14 FC2QFN | NAIVIE | FUNCTION                                                       | TYPE           |  |

| A1     | 8         | LX1    | Switching Node 1                                               | Power          |  |

| A2     | 6, 7      | IN     | Input. Bypass to PGND with a 10V 10µF capacitor.               | Power          |  |

| A3     | 5         | BIAS   | Internal Bias. Bypass to PGND with a 10V 1µF capacitor.        | Analog         |  |

| A4     | 4         | AGND   | Analog Ground                                                  | Ground         |  |

| B1     | 9         | PGND   | Power Ground                                                   | Ground         |  |

| B2     | 14        | FPWM   | FPWM Mode Selection (active-high)                              | Digital Input  |  |

| В3     | 2         | POK    | Power-OK Open-Drain Output (active-high)                       | Digital Output |  |

| B4     | 1         | SEL    | Select the output voltage with resistor (see <u>Table 2</u> ). | Analog         |  |

| C1     | 10        | LX2    | Switching Node 2                                               | Power          |  |

| C2     | 11, 12    | OUT    | Output. Bypass to PGND with a 10V 22µF capacitor.              | Power          |  |

| C3     | 13        | OUTS   | Output Sense Ar                                                |                |  |

| C4     | 3         | EN     | Enable Pin                                                     | Digital Input  |  |

# **Functional Diagrams**

## **Function Diagram**

### **Detailed Description**

#### Start Up

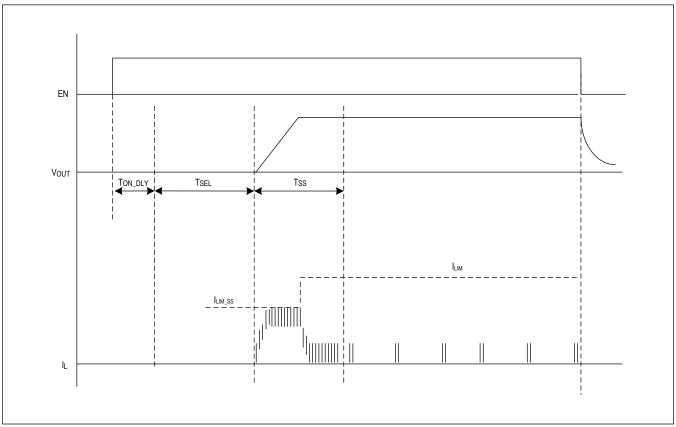

When the EN pin is set to high, the IC turns on the internal bias circuitry which takes typically  $100\mu s$  ( $t_{ON\_DLY}$ ) to settle. After the internal bias circuitry is settled, the controller senses the SEL pin resistance to set the reference voltage. The R<sub>SEL</sub> reading takes about  $600\mu s$  (typ). After the IC reads the R<sub>SEL</sub> value, it begins the soft-start process. During the soft-start process, the IC lowers the I<sub>LIM</sub> level from normal I<sub>LIM</sub> level and ramps the output voltage. This prevents the buck-boost from drawing too much current from the input supply during start up. The soft-start process takes 1.5ms (typ) for options B and D, and takes  $200\mu s$  (typ) for options A and C.

Figure 1. Start-Up Waveform

The buck-boost is in FPWM mode for the entire duration of  $T_{SS}$ . Current limit during soft-start ( $I_{LIM\_SS}$ ) increases to  $I_{LIM}$  after approximately half of  $T_{SS}$ . See <u>Table 1</u> for a list of parts with their respective soft-start and normal operation  $I_{LIM}$  levels.

## Table 1. I<sub>LIM</sub> Levels

| PART NUMBER                                                    | I <sub>LIM_SS</sub> (A) | I <sub>LIM</sub> (A) |

|----------------------------------------------------------------|-------------------------|----------------------|

| MAX77827BEWC+T, MAX77827BEFD+T, MAX77827DEWC+T, MAX77827DEFD+T | 1.15                    | 1.8                  |

| MAX77827AEWC+T, MAX77827AEFD+T, MAX77827CEWC+T, MAX77827CEFD+T | 1.8                     | 3.1                  |

# 5.5V Input, 1.8A/3.1A Switch Buck-Boost Converter with 6µA I<sub>O</sub>

#### **Immediate Shutdown Conditions**

The following events immediately shutdown the buck-boost:

- Thermal Protection (T<sub>.I</sub> > +165°C)

- V<sub>SYS</sub> < SYS UVLO Falling Threshold (V<sub>UVLO F</sub>)

The events in this category shutdown the output until fault conditions are removed from the system.

#### **Power Down**

When EN pin is set to low, the IC stops switching and turns on the discharge switches until the output is discharged.

#### **Buck-Boost Regulator**

The IC buck-boost regulator utilizes a four-switch H-bridge configuration to realize buck and boost operating modes. This topology maintains output voltage regulation when the input voltage is greater than, equal to, or less than the output voltage. The buck-boost is ideal in one-cell Li-ion battery powered applications and two-cell Alkaline battery powered applications, providing 2.3V to 5.3V of output voltage range. High-switching frequency and a unique control algorithm allow for the smallest solution size, low output noise, and the highest-efficiency across a wide input voltage and output current range.

#### **Buck-Boost Control Scheme**

The buck-boost converter operates using a 2.5MHz fixed-frequency pulse-width modulated (PWM) control scheme with current-mode compensation. The buck-boost utilizes an H-bridge topology using a single inductor and output capacitor.

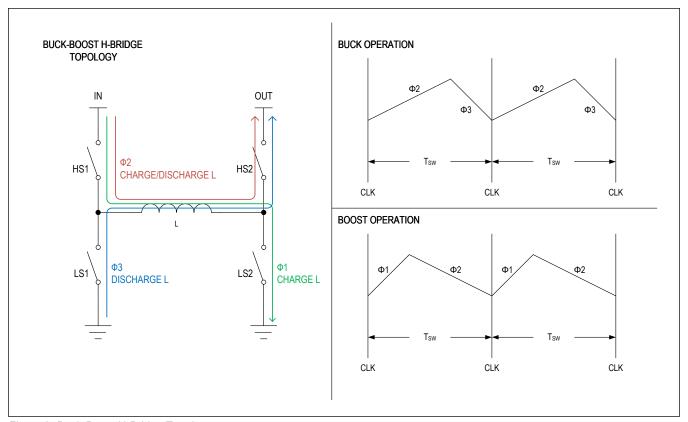

The H-bridge topology has three switching phases. See Figure 2 for details.

- $\Phi$ 1 Switch period (Phase 1: HS1 = ON, LS2 = ON) stores energy in the inductor. Inductor current ramps up at a rate proportional to the input voltage divided by inductance:  $V_{IN}/L$ .

- Φ2 Switch period (Phase 2: HS1 = ON, HS2 = ON) ramps inductor current up or down depending on the differential voltage across the inductor: (V<sub>IN</sub> – V<sub>OUT</sub>)/L.

- Φ3 Switch period (Phase 3: LS1 = ON, HS2 = ON) ramps inductor current down at a rate proportional to the output voltage divided by inductance: (-V<sub>OUT</sub>/L).

Boost operation ( $V_{IN} < V_{OUT}$ ) utilizes phase 1 and phase 2 within a single clock period. See the representation of inductor current waveform for boost mode operation in <u>Figure 2</u>.

Buck operation ( $V_{IN} > V_{OUT}$ ) utilizes phase 2 and phase 3 within a single clock period. See the representation of inductor current waveform for buck mode operation in Figure 2.

Figure 2. Buck-Boost H-Bridge Topology

#### **Output Voltage Configuration**

The IC allows a SEL pin to configure the output voltage. Resistors with 1% tolerance (or better) should be chosen, with nominal values specified in  $\underline{\mathsf{Table 2}}$ .

**Table 2. R<sub>SEL</sub> Selection Table**

| R <sub>SEL</sub> (kΩ) | V <sub>OUT</sub> (V) |

|-----------------------|----------------------|

| Open                  | 3.3                  |

| 909                   | 2.3                  |

| 768                   | 2.4                  |

| 634                   | 2.5                  |

| 536                   | 2.6                  |

| 452                   | 2.7                  |

| 383                   | 2.8                  |

| 324                   | 2.8                  |

| 267                   | 2.85                 |

| 226                   | 5.2                  |

| 191                   | 2.9                  |

| 162                   | 5.3                  |

| 133                   | 3                    |

| 113                   | 3                    |

Table 2. R<sub>SEL</sub> Selection Table (continued)

| R <sub>SEL</sub> (kΩ) | V <sub>OUT</sub> (V) |

|-----------------------|----------------------|

| 95.3                  | 3.1                  |

| 80.6                  | 3.15                 |

| 66.5                  | 3.15                 |

| 56.2                  | 3.2                  |

| 47.5                  | 3.4                  |

| 40.2                  | 3.45                 |

| 34                    | 3.5                  |

| 28                    | 3.6                  |

| 23.7                  | 3.7                  |

| 20                    | 3.75                 |

| 16.9                  | 3.8                  |

| 14                    | 3.9                  |

| 11.8                  | 4                    |

| 10                    | 4.1                  |

| 8.45                  | 4.2                  |

| 7.15                  | 4.4                  |

| 5.9                   | 4.5                  |

| 4.99                  | 5                    |

| Short to GND          | 3.3                  |

#### **FPWM Mode Enable**

The IC automatically defaults to SKIP mode operation at no load and light load conditions. Transition from skip mode to PWM occurs when load current increases past a certain threshold. Another way to enable PWM operation is by connecting the FPWM pin to logic HIGH level. This forces PWM mode (FPWM) regardless of load current at the output. FPWM mode benefits applications where the lowest output ripple is required, whereas skip mode helps maximize the buck-boost regulator's efficiency at light loads.

#### Power-OK (POK) Indicator

The device features an open-drain POK output to monitor the output voltage. The POK pin requires an external pull-up resistor and goes high (high-impedance) after the output increases above 92.5% (typ) of the target output voltage (V<sub>OUT TARGET</sub>). The POK pin goes low when the regulator output drops below 90% (typ) of V<sub>OUT TARGET</sub>.

#### **Protection Features**

#### **Undervoltage Lockout (UVLO)**

The device supports a UVLO feature that prevents operation in abnormal input voltage conditions when  $V_{IN}$  falls below the  $V_{IN\_UVLO\_F}$  threshold. Regardless of the EN pin status, the device disables until the input voltage  $V_{IN}$  rises above the  $V_{IN\_UVLO\_R}$  threshold.

#### **Soft-Start**

The IC is equipped with a soft-start feature to limit large input-current draw from the system supply during device start-up. During the soft-start time, the IC lowers the switching current-limit level from normal level and operates in FPWM mode. See Table 1 for the  $I_{LIM}$  levels of each part number.

#### **Output Active Discharge**

The buck-boost provides an internal  $100\Omega$  switch for output active discharge function. The internal switch provides a path to discharge the energy stored in the output capacitor to PGND whenever the regulator is disabled. While the regulator remains enabled, the internal switch is disconnected from the output.

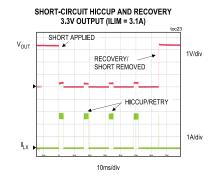

#### **Overcurrent Protection (OCP)**

The device features a robust switching current-limit scheme that protects the device and the inductor during overload and fast transient conditions. The current-sense circuit takes current information from the high-side MOSFETs to determine the peak-switching current ( $R_{DS(ON)} \times I_L$ ).

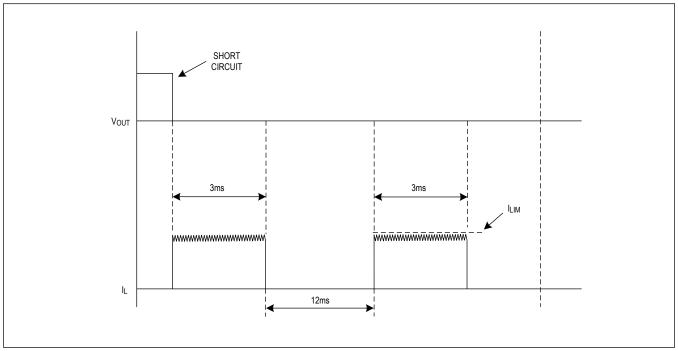

The IC provides two different cycle-by-cycle current limit levels (1.8A (typ) and 3.1A (typ)) for the high-side MOSFET. If the switching current (I<sub>LIM</sub>) hits current limit for about 3ms, the IC shuts off the output for about 12ms, retries, and repeats this cycle until the over-current condition is removed from the system.

Figure 3. Short-Circuit Waveform

#### **Thermal Shutdown**

The device has an internal thermal-protection circuit which monitors die temperature. The buck-boost disables if the die temperature exceeds  $T_{SHDN}$  (+165°C typ). The buck-boost enables again after the die temperature cools by approximately +20°C.

### **Applications Information**

#### **Inductor Selection**

Buck-boost is optimized for a  $1\mu H$  inductance. The lower the inductor DCR, the higher the buck-boost efficiency. Users need to trade off inductor size with DCR value and choose a suitable inductor for the buck-boost.

The saturation current of the inductor should be higher than the maximum switching current limit to avoid inductor saturation during operation. See the *Electrical Characteristics* table specifications for the maximum I<sub>LIM</sub> of each IC option.

<u>Table 3</u> lists recommended inductors for the IC. Always choose the inductor carefully by consulting the manufacturer's latest released data sheet.

**Table 3. Inductor Recommendations**

| MFGR.           | SERIES             | NOMINAL<br>INDUCTANCE<br>(µH) | TYPICAL DC<br>RESISTANCE<br>(mΩ) | CURRENT<br>RATING (A)<br>-30 (ΔL/L) | CURRENT RATING (A) $\Delta T = 40^{\circ}C$ RISE | DIMENSIONS<br>L x W x H<br>(mm) | OPTIONS    |

|-----------------|--------------------|-------------------------------|----------------------------------|-------------------------------------|--------------------------------------------------|---------------------------------|------------|

| Murata          | DFE18SBN1R0ME0     | 1.0                           | 120                              | 3.1                                 | 2.4                                              | 1.6 x 0.8 x 0.8                 | B, D       |

| Samsung         | CIGT201610EH1R0MNE | 1.0                           | 38                               | 4.5                                 | 4.3                                              | 2.0 x 1.6 x 1.0                 | A, B, C, D |

| Taiyo-<br>Yuden | MEKK2016H1R0M      | 1.0                           | 41                               | 4.5                                 | 3.7                                              | 2.0 x 1.6 x 1.0                 | A, B, C, D |

| Cyntec          | HTEH20120H-1R0MSR  | 1.0                           | 45                               | 3.8                                 | 3.5                                              | 2.0 x 1.2 x 0.8                 | A, B, C, D |

| Samsung         | CIGT252010EH1R0MNE | 1.0                           | 26                               | 5.0                                 | 4.3                                              | 2.5 x 2.0 x 1.0                 | A, B, C, D |

| Sumida          | CDMT40D20HF-1R0NC  | 1.0                           | 26                               | 8.7                                 | 9.6                                              | 4.3 x 4.3 x 2.1                 | A, B, C, D |

| Coilcraft       | XAL4020-102MEB     | 1.0                           | 13                               | 8.7                                 | 9.6                                              | 4.0 x 4.0 x 2.1                 | A, B, C, D |

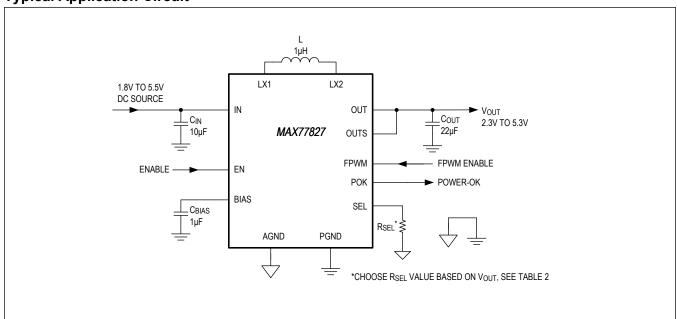

#### **Input Capacitor Selection**

The input capacitor,  $C_{IN}$ , reduces the current peaks drawn from the battery or input power source and reduces switching noise in the device. The impedance of  $C_{IN}$  at the switching frequency should be kept very low. Ceramic capacitors with X5R or X7R dielectrics are highly recommended due to their small size, low ESR, and small temperature coefficients. For most applications, a 10V  $10\mu$ F capacitor is sufficient.

#### **Output Capacitor Selection**

The output capacitor,  $C_{OUT}$ , is required to keep the output-voltage ripple small and to ensure regulation loop stability.  $C_{OUT}$  must have low impedance at the switching frequency. Ceramic capacitors with X5R or X7R dielectric are highly recommended due to their small size, low ESR, and small temperature coefficients. For stable operation, the buck-boost requires  $8\mu F$  of minimum effective output capacitance. Considering DC bias characteristic of ceramic capacitors, a 10V  $22\mu F$  capacitor is recommended for most applications.

#### **PCB Layout Guidelines**

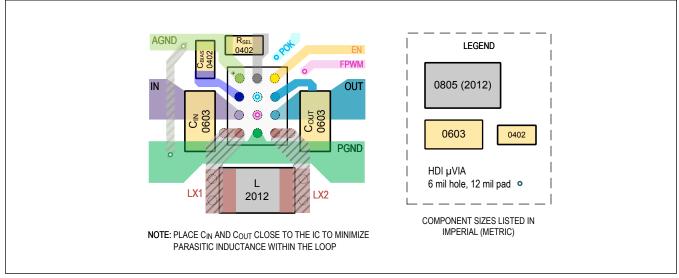

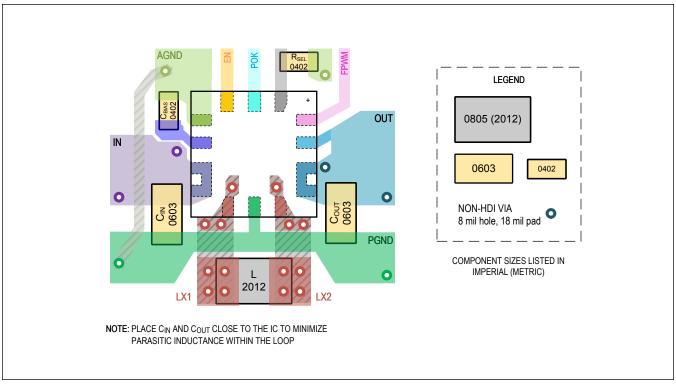

Careful circuit board layout is critical to achieve low switching power losses and clean, stable operation. <u>Figure 5</u> shows an example PCB layout for the MAX77827 FC2QFN package. For the WLP package, a high density interconnect (HDI) PCB is required. <u>Figure 4</u> shows an example HDI PCB layout for the MAX77827 WLP package.

When designing the PCB, follow these guidelines:

Place the input capacitors C<sub>IN</sub> and output capacitors C<sub>OUT</sub> immediately next to the IN pin and OUT pin, respectively, of the IC. Since the IC operates at a high switching frequency, this placement is critical for minimizing parasitic inductance within the input and output current loops, which can cause high voltage spikes and can damage the internal switching MOSFETs.

# 5.5V Input, 1.8A/3.1A Switch Buck-Boost Converter with 6µA I<sub>O</sub>

- 2. Place the inductor next to the LX bumps/pins (as close as possible) and make the traces between the LX bumps/pins and the inductor short and wide to minimize PCB trace impedance. Excessive PCB impedance reduces converter efficiency. When routing LX traces on a separate layer (as in the examples), make sure to include enough vias to minimize trace impedance. Routing LX traces on multiple layers is recommended to further reduce trace impedance. Furthermore, do not allow LX traces to take up an excessive amount of area. The voltage on this node switches very quickly and additional area creates more radiated emissions.

- 3. Prioritize the low-impedance ground plane of the PCB directly underneath the IC, C<sub>OUT</sub>, C<sub>IN</sub>, and the inductor. Cutting this ground plane risks interrupting the switching current loops.

- 4. AGND must carefully connect to PGND on the PCBs low-impedance ground plane. Connect AGND to the low-impedance ground plane on the PCB (the same net as PGND) away from any critical loops.

- 5. The IC requires a supply input (BIAS) which is often the same net as IN. Carefully bypass BIAS to PGND with a dedicated capacitor (C<sub>BIAS</sub>) as close as possible to the IC. Route a dedicated trace between C<sub>BIAS</sub> and the BIAS bump/pin. Avoid connecting BIAS directly to the nearest IN bumps/pins without dedicated bypassing.

- 6. Connect the OUTS bump/pin to the regulating point with a dedicated trace away from noisy nets such as LX1 and LX2.

- 7. Keep the power traces and load connections short and wide. This is essential for high converter efficiency.

- 8. Do not neglect ceramic capacitor DC voltage derating. Choose capacitor values and case sizes carefully. See the <a href="Output Capacitor Selection">Output Capacitor Selection</a> section and refer to <a href="Tutorial 5527">Tutorial 5527</a> for more information.

Figure 4. PCB Layout Example (WLP—B and D Options)

Figure 5. PCB Layout Example (FC2QFN—B and D Options)

# **Typical Application Circuits**

## **Typical Application Circuit**

# **Ordering Information**

| PART NUMBER    | TYP I <sub>LIM</sub> (A) | UVLO RISING MAX (V) | PIN-PACKAGE |

|----------------|--------------------------|---------------------|-------------|

| MAX77827AEWC+T | 3.1                      | 1.8                 | 12 WLP      |

| MAX77827BEWC+T | 1.8                      | 2.6                 | 12 WLP      |

| MAX77827CEWC+T | 3.1                      | 2.6                 | 12 WLP      |

| MAX77827DEWC+T | 1.8                      | 1.8                 | 12 WLP      |

| MAX77827AEFD+T | 3.1                      | 1.8                 | 14 FC2QFN   |

| MAX77827BEFD+T | 1.8                      | 2.6                 | 14 FC2QFN   |

| MAX77827CEFD+T | 3.1                      | 2.6                 | 14 FC2QFN   |

| MAX77827DEFD+T | 1.8                      | 1.8                 | 14 FC2QFN   |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

# 5.5V Input, 1.8A/3.1A Switch Buck-Boost Converter with 6µA I<sub>Q</sub>

#### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                | PAGES<br>CHANGED             |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 0                  | 4/19             | Initial release                                                                                                                                                                                                                                                                                                            | _                            |

| 1                  | 5/19             | Updated Ordering Information table                                                                                                                                                                                                                                                                                         | 22                           |

| 2                  | 6/19             | Updated Ordering Information table                                                                                                                                                                                                                                                                                         | 22                           |

| 3                  | 10/19            | Updated General Description, Applications, Benefits and Features, and Package Information sections, replaced all Typical Operating Characteristics and FC2QFN Pin Configuration, updated Pin Description table, Table 1, Figure 2, and Table 3, replaced PCB Layout Guidelines section, updated Ordering Information table | 1, 6, 9–13, 15,<br>17, 20–22 |

| 4                  | 3/20             | Updated <i>Electrical Characteristics</i> table, <i>Start Up</i> section, Table 1, Table 3, and <i>Ordering Information</i> table                                                                                                                                                                                          | 7, 8, 15, 20, 23             |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.