ARM Cortex<sup>®</sup>-M0

**32-bit Microcontroller**

# NuMicro<sup>®</sup> Family Mini57 Series Technical Reference Manual

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing this document only for reference purposes of NuMicro microcontroller based system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation.

www.nuvoton.com

| TABLE OF | CONTENTS                                                                                                |     |

|----------|---------------------------------------------------------------------------------------------------------|-----|

| 1 GENE   | RAL DESCRIPTION                                                                                         | 12  |

| 2 FEAT   | URES                                                                                                    | 13  |

| 3 ABBF   | REVIATIONS                                                                                              | 17  |

| 4 PART   | S INFORMATION LIST AND PIN CONFIGURATION                                                                | 18  |

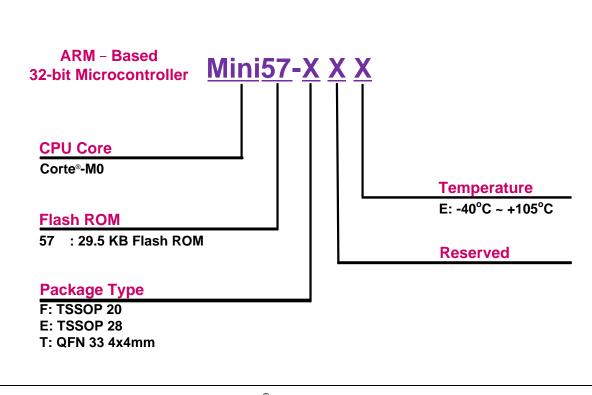

| 4.1      | NuMicro <sup>®</sup> Mini57 Naming Rule                                                                 |     |

| 4.2      | NuMicro <sup>®</sup> Mini57 Series Selection Guide                                                      |     |

| 4.3      | Pin Configuration                                                                                       |     |

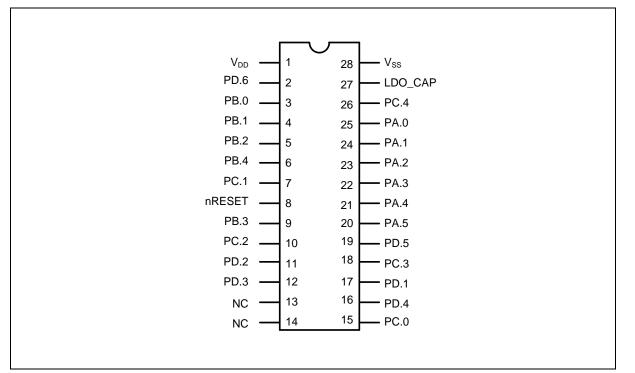

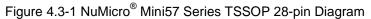

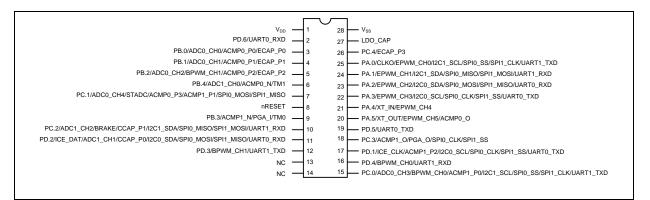

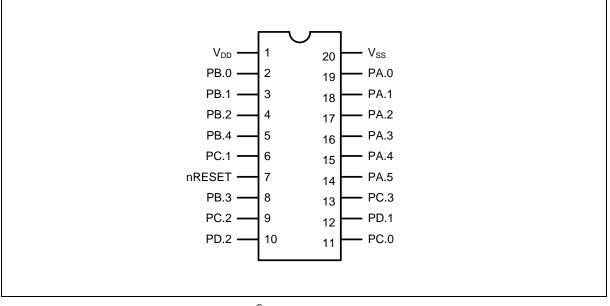

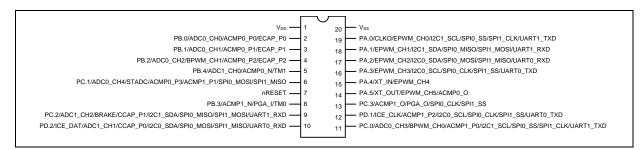

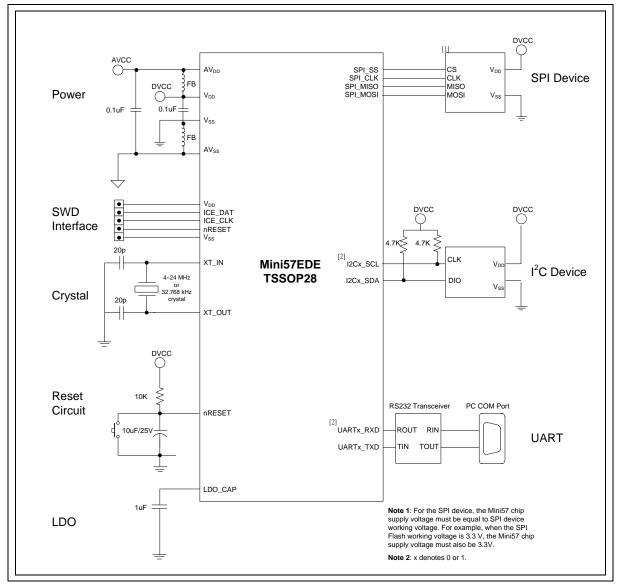

|          | 4.3.1 TSSOP 28-Pin                                                                                      |     |

|          | 4.3.2 TSSOP 20-Pin                                                                                      | 21  |

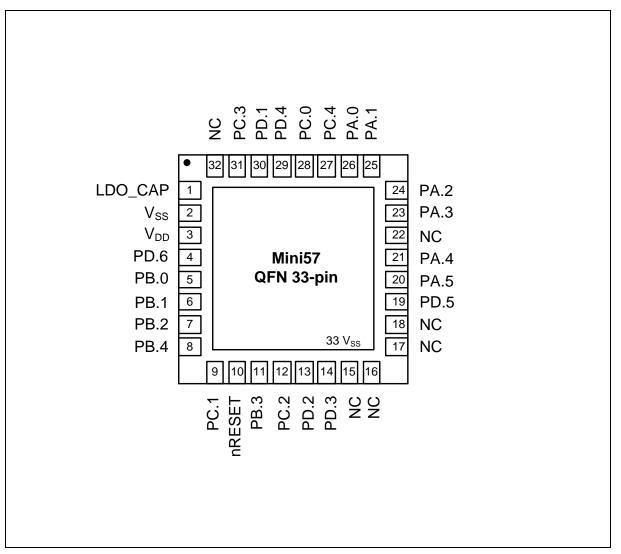

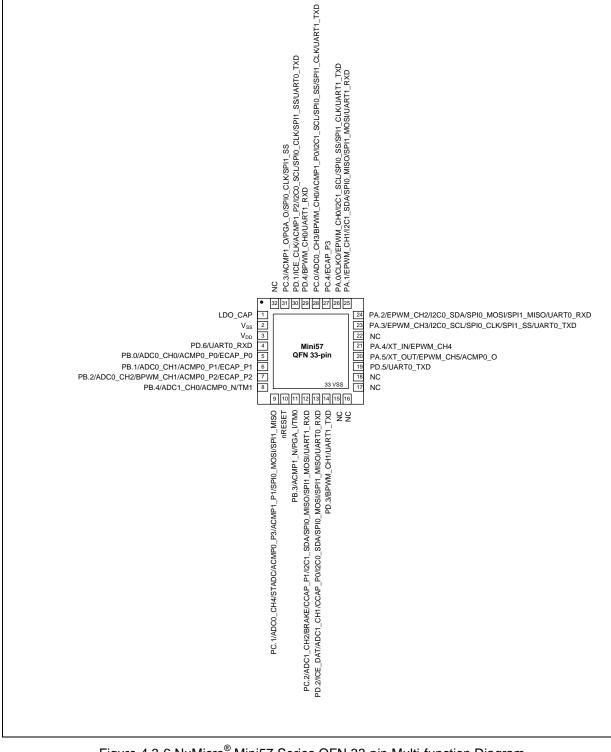

|          | 4.3.3 QFN 33-Pin                                                                                        |     |

| 4.4      | Pin Description                                                                                         | 24  |

|          | 4.4.1 Mini57 Series Pin Description                                                                     |     |

|          | 4.4.2 GPIO Multi-function Pin Summary                                                                   |     |

|          |                                                                                                         |     |

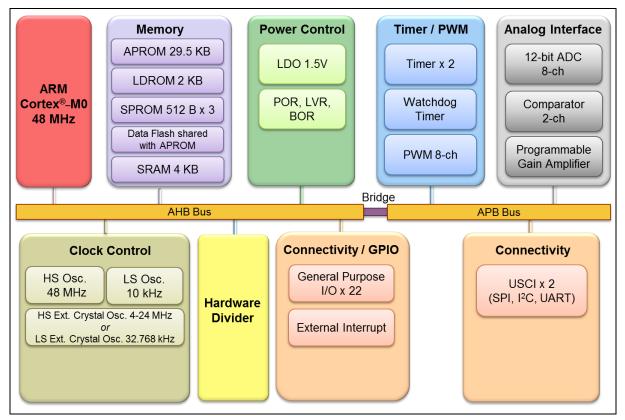

| 5.1      | NuMicro <sup>®</sup> Mini57 Block Diagram                                                               |     |

| 6 FUNC   | TIONAL DESCRIPTION                                                                                      |     |

| 6.1      | ARM <sup>®</sup> Cortex <sup>®</sup> -M0 Core                                                           | 40  |

|          | 6.1.1 Overview                                                                                          | 40  |

|          | 6.1.2 Features                                                                                          |     |

| 6.2      |                                                                                                         |     |

|          | 6.2.1 Overview                                                                                          |     |

|          | <ul><li>6.2.2 System Reset</li><li>6.2.3 Power Modes and Wake-up Sources</li></ul>                      |     |

|          | <ul><li>6.2.3 Power Modes and Wake-up Sources</li><li>6.2.4 System Power Architecture</li></ul>         |     |

|          | 6.2.5 System Memory Mapping                                                                             |     |

|          | 6.2.6 Register Protection                                                                               |     |

|          | 6.2.7 Memory Organization                                                                               | 55  |

|          | 6.2.8 Register Map                                                                                      |     |

|          | 6.2.9 Register Description                                                                              |     |

|          | <ul><li>6.2.10 System Timer (SysTick)</li><li>6.2.11 Nested Vectored Interrupt Control (NVIC)</li></ul> |     |

|          | 6.2.12 System Control Registers                                                                         |     |

| 6.3      |                                                                                                         |     |

|          | 6.3.1 Overview                                                                                          | 113 |

|          | 6.3.2 Auto Trim                                                                                         | 115 |

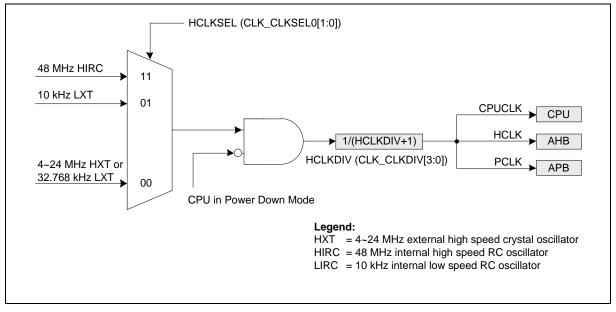

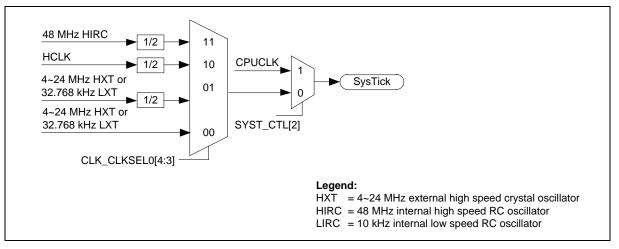

|          | 6.3.3 System Clock and SysTick Clock                                                                    | 115 |

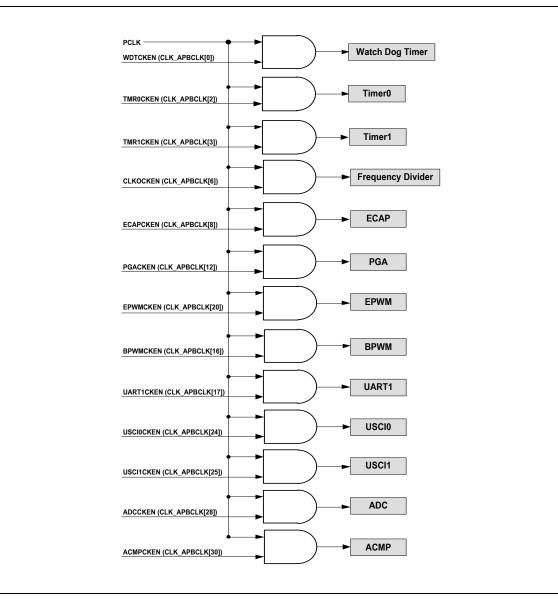

|          | 6.3.4 Peripherals Clock Source Selection                                                                |     |

|          | 6.3.5 Power-down Mode Clock                                                                             |     |

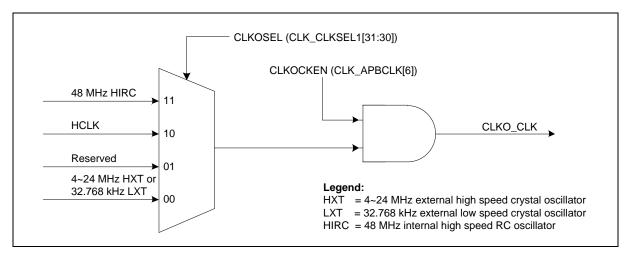

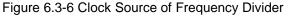

|          | <ul><li>6.3.6 Frequency Divider Output</li><li>6.3.7 Register Map</li></ul>                             |     |

|          | 6.3.8 Register Description                                                                              |     |

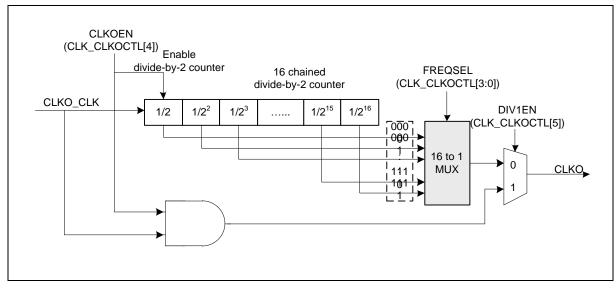

| 6.4      | •                                                                                                       |     |

|          |                                                                                                         |     |

|     | 6.4.1          | Overview                                           | 133    |

|-----|----------------|----------------------------------------------------|--------|

|     | 6.4.2          | Features                                           |        |

|     | 6.4.3          | Block Diagram                                      |        |

|     | 6.4.4          | Functional Description                             |        |

|     | 6.4.5          | Register Map                                       |        |

|     | 6.4.6          | Register Description                               |        |

| 6.5 |                | eral Purpose I/O (GPIO)                            |        |

| 0.0 |                |                                                    |        |

|     | 6.5.1<br>6.5.2 | Overview                                           | -      |

|     |                | Features                                           |        |

|     | 6.5.3          | Block Diagram                                      |        |

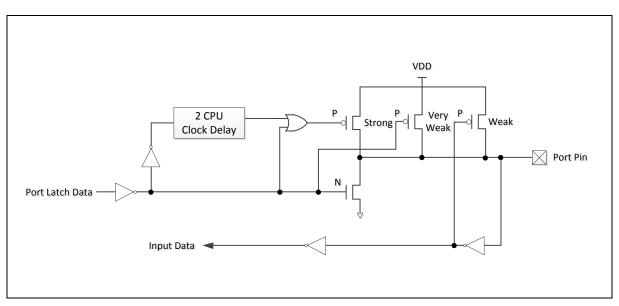

|     | 6.5.4          | Basic Configuration                                |        |

|     | 6.5.5          | Functional Description                             |        |

|     | 6.5.6          | GPIO Interrupt and Wake-up Function                |        |

|     | 6.5.7          | Register Map                                       |        |

|     | 6.5.8          | Register Description                               |        |

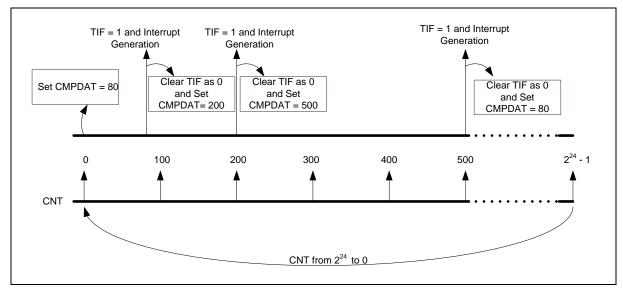

| 6.6 | Time           | er Controller (TIMER)                              | 187    |

|     | 6.6.1          | Overview                                           | 187    |

|     | 6.6.2          | Features                                           | 187    |

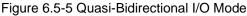

|     | 6.6.3          | Block Diagram                                      | 188    |

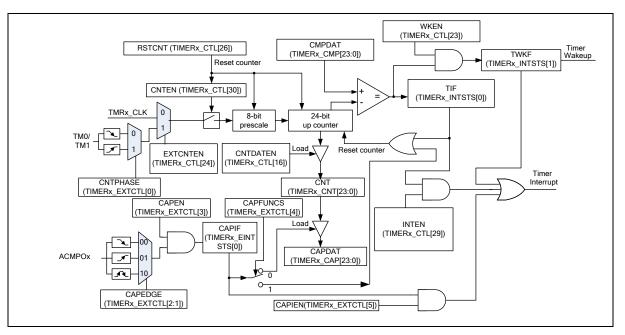

|     | 6.6.4          | Basic Configuration                                | 189    |

|     | 6.6.5          | Functional Description                             | 189    |

|     | 6.6.6          | Register Map                                       | 196    |

|     | 6.6.7          | Register Description                               | 197    |

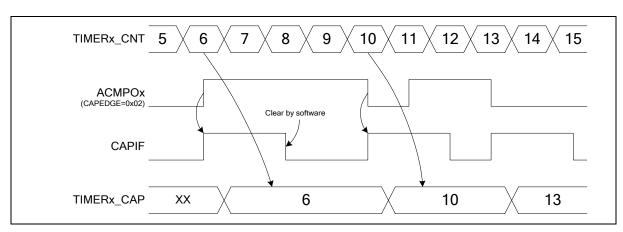

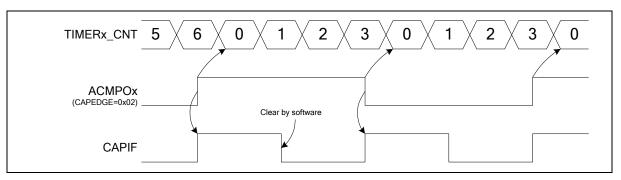

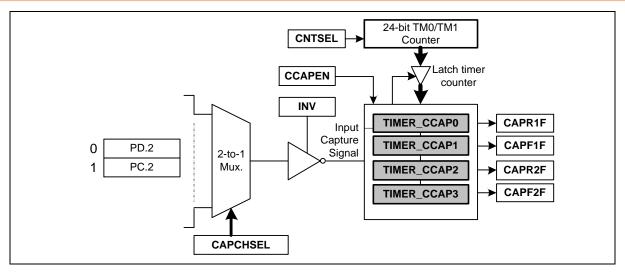

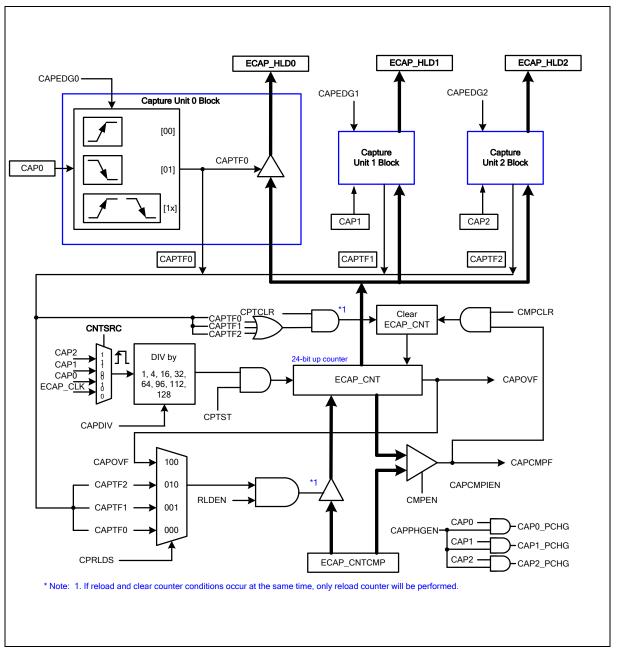

| 6.7 | Enha           | anced Input Capture Timer (ECAP)                   | 209    |

|     | 6.7.1          | Overview                                           |        |

|     | 6.7.2          | Features                                           |        |

|     | 6.7.3          | Block Diagram                                      |        |

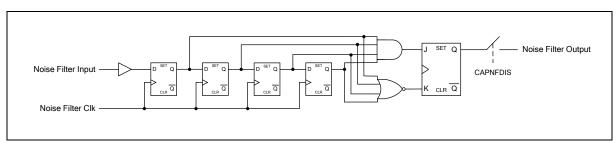

|     | 6.7.4          | Input Noise Filter                                 |        |

|     | 6.7.5          | Operation of Input Capture Timer/Counter           |        |

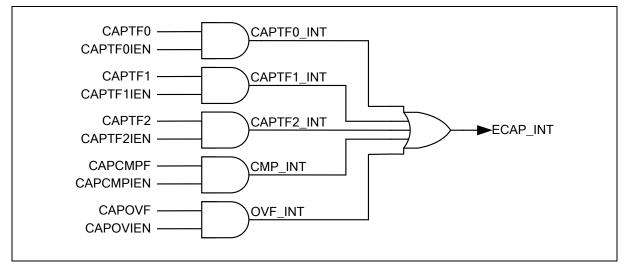

|     | 6.7.6          | Input Capture Timer/Counter Interrupt Architecture |        |

|     | 6.7.7          | Register Map                                       |        |

|     | 6.7.8          | Register Description                               |        |

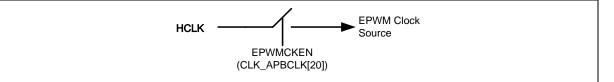

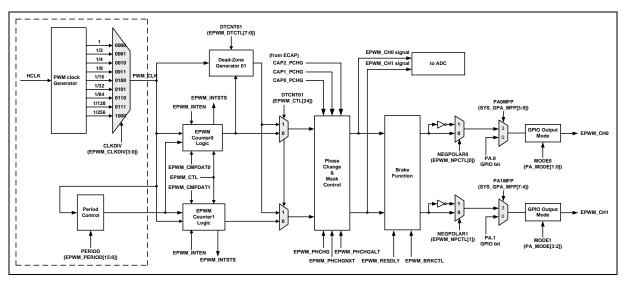

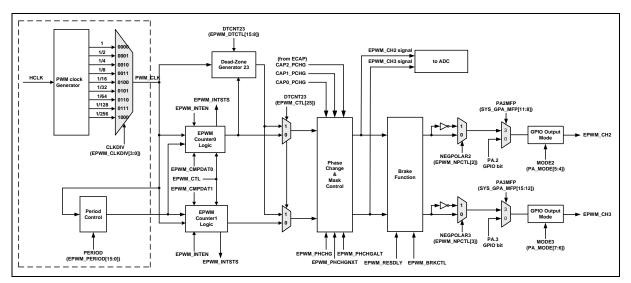

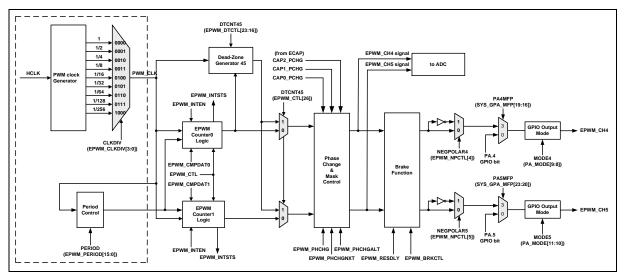

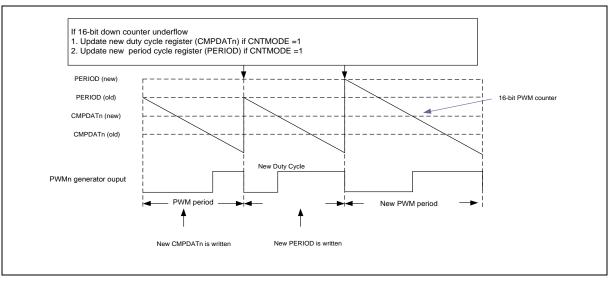

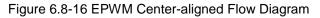

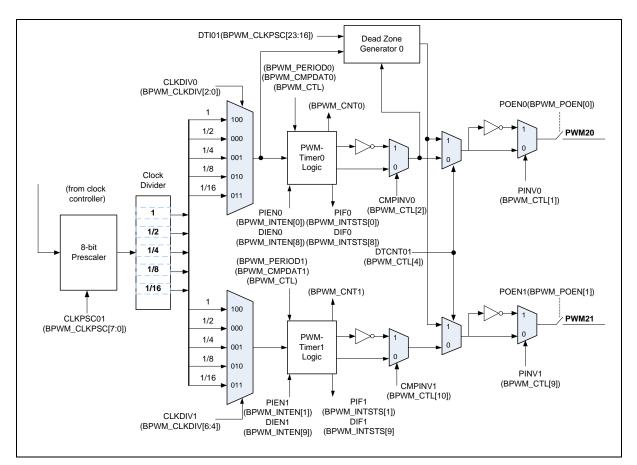

| 6.8 |                | anced PWM Generator (EPWM)                         |        |

| 0.0 | 6.8.1          | Overview                                           |        |

|     | 6.8.2          |                                                    |        |

|     |                | Features                                           |        |

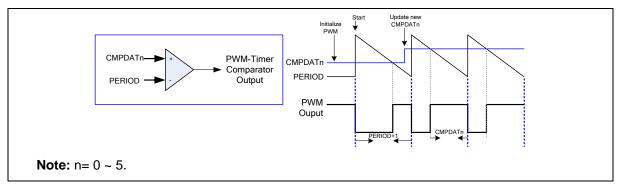

|     | 6.8.3          | Block Diagram                                      |        |

|     | 6.8.4          | Basic Configuration                                |        |

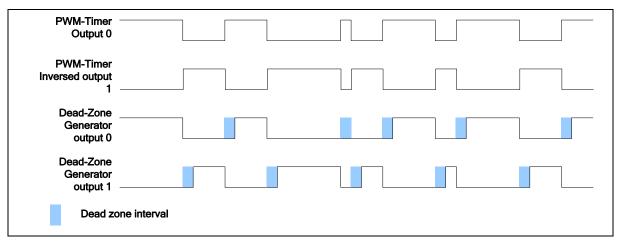

|     | 6.8.5          | Functional Description                             |        |

|     | 6.8.6          | Register Map                                       |        |

| ~ ~ | 6.8.7          | Register Description                               |        |

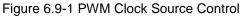

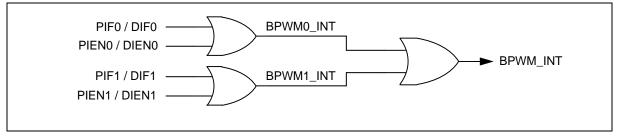

| 6.9 |                | c PWM Generator (BPWM)                             |        |

|     | 6.9.1          | Overview                                           |        |

|     | 6.9.2          | Features                                           |        |

|     | 6.9.3          | Block Diagram                                      |        |

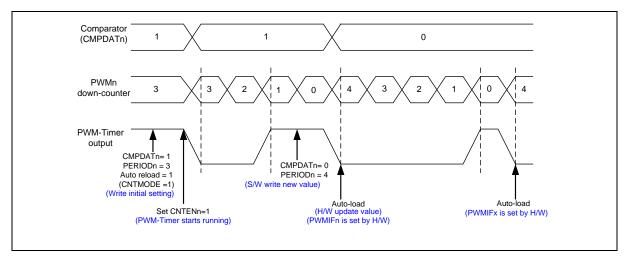

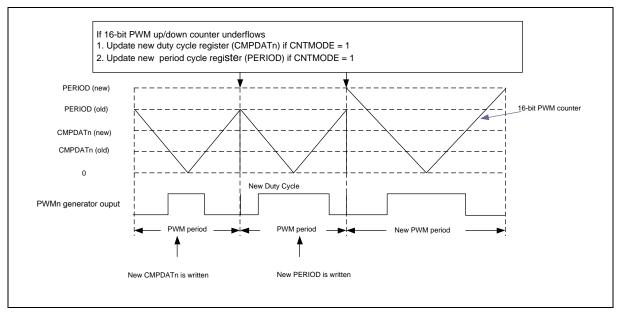

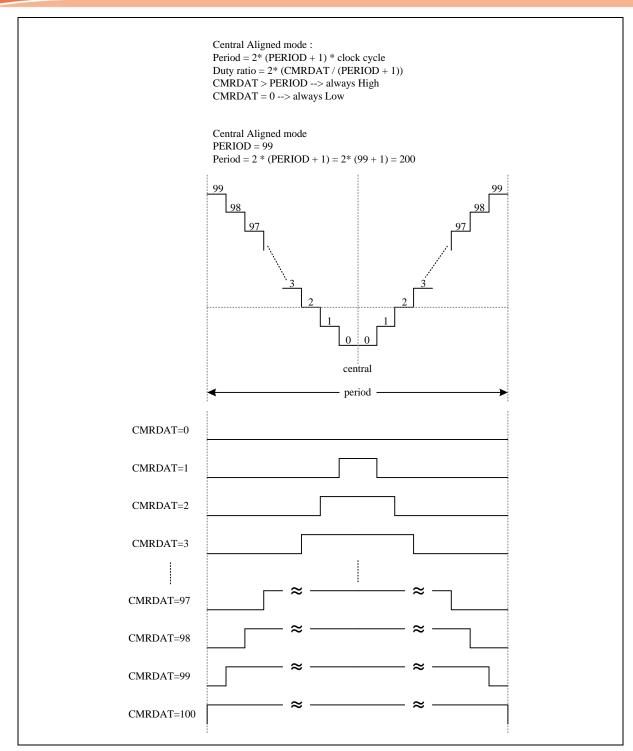

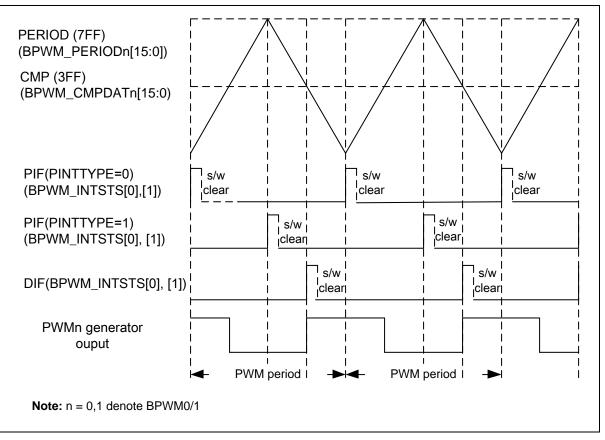

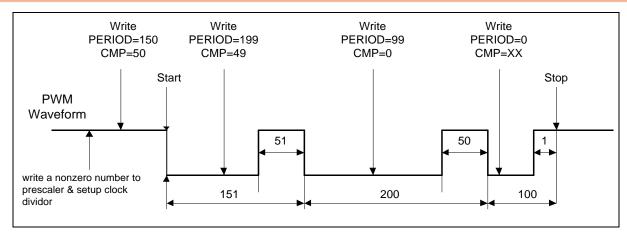

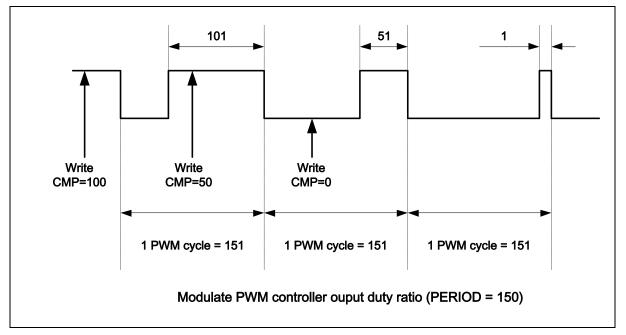

|     | 6.9.4          | PWM-Timer Operation                                |        |

|     | 6.9.5          | Register Map                                       | 284    |

|     | -              |                                                    | D 4 00 |

| 6.9.6 Register Description                                |     |

|-----------------------------------------------------------|-----|

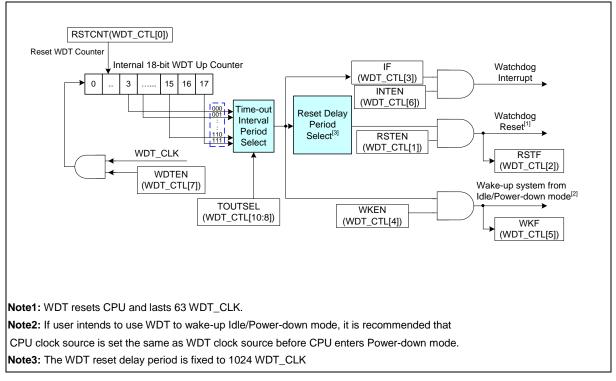

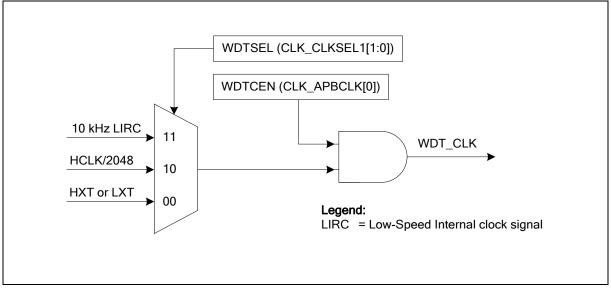

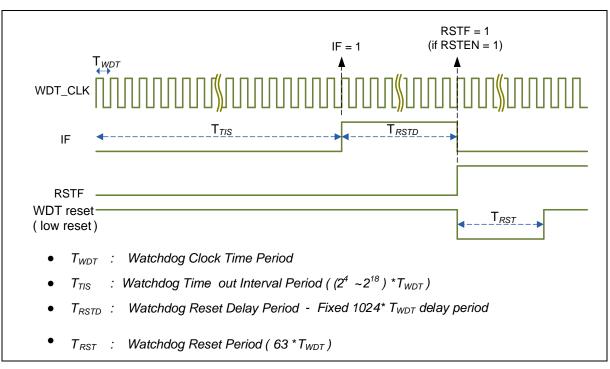

| 6.10 Watchdog Timer (WDT)                                 |     |

| 6.10.1 Overview                                           | 295 |

| 6.10.2 Features                                           |     |

| 6.10.3 Block Diagram                                      |     |

| 6.10.4 Clock Control                                      |     |

| 6.10.5 Basic Configuration                                |     |

| 6.10.6 Functional Description                             | 296 |

| 6.10.7 Registers Map                                      | 298 |

| 6.10.8 Register Description                               | 299 |

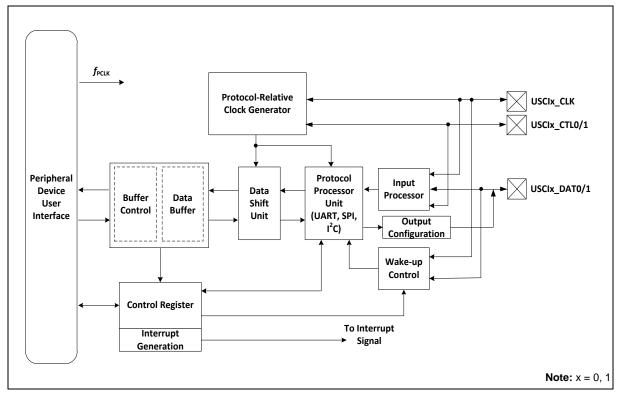

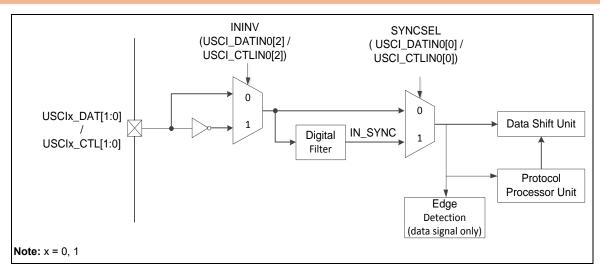

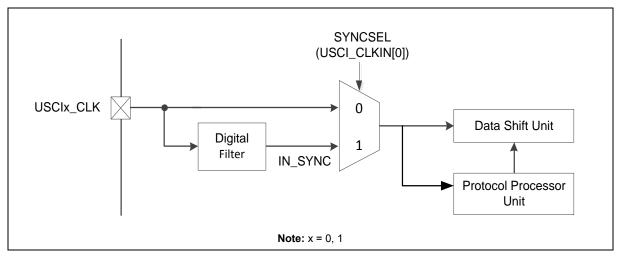

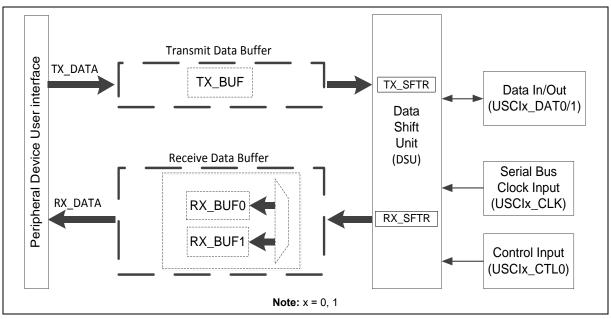

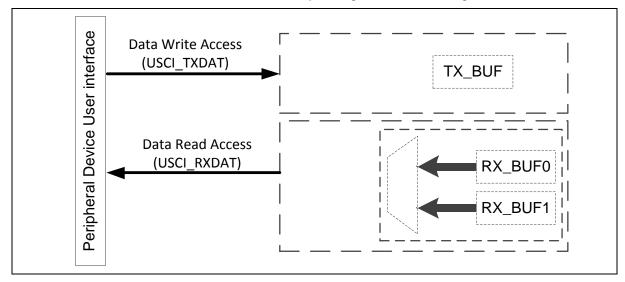

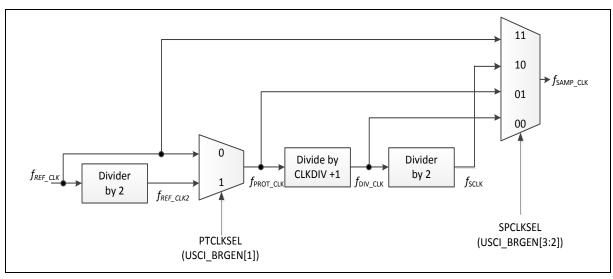

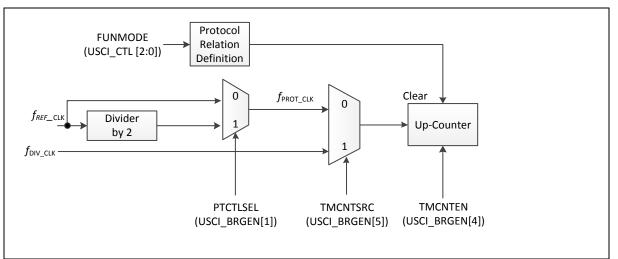

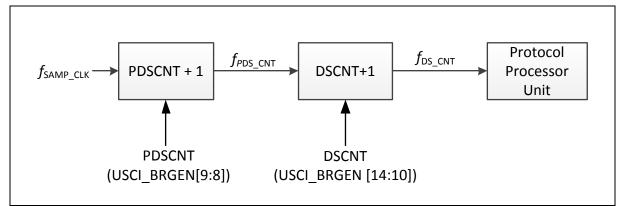

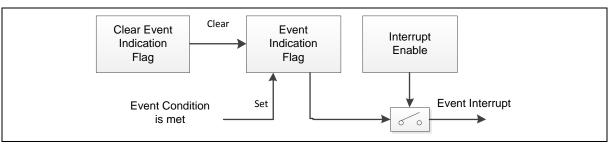

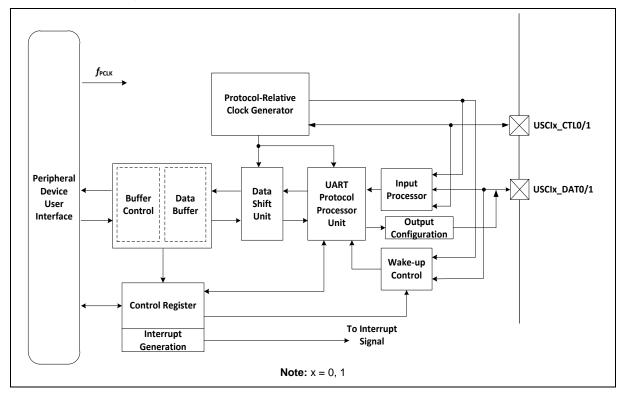

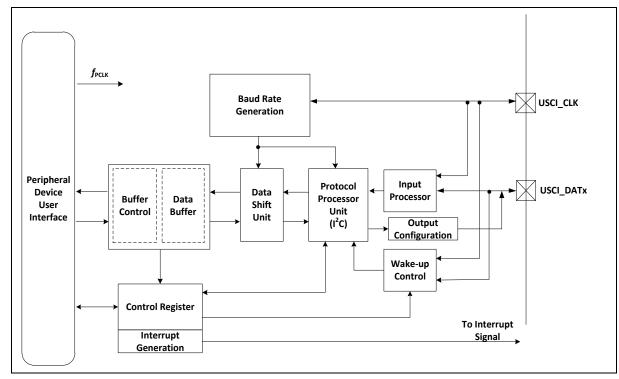

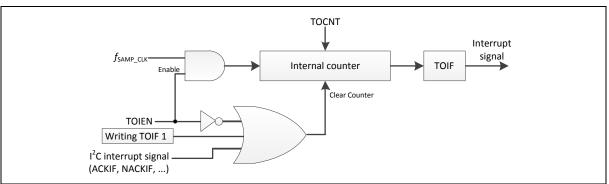

| 6.11 USCI – Universal Serial Control Interface Controller | 301 |

| 6.11.1 Overview                                           |     |

| 6.11.2 Features                                           | 301 |

| 6.11.3 Block Diagram                                      | 301 |

| 6.11.4 Functional Description                             | 302 |

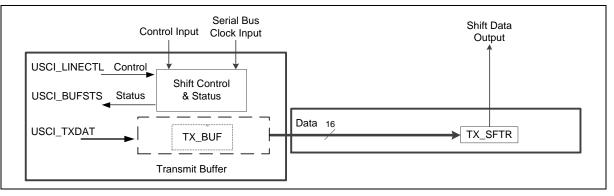

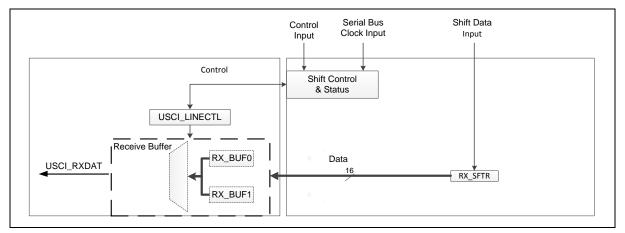

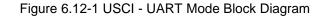

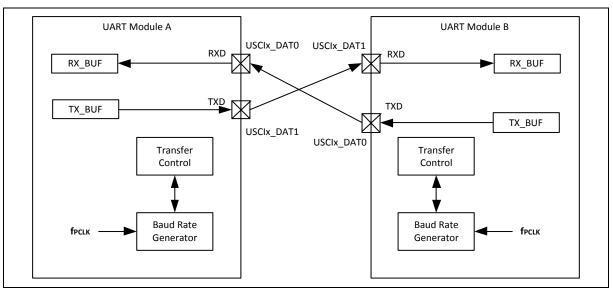

| 6.12 USCI – UART Mode                                     | 313 |

| 6.12.1 Overview                                           | 313 |

| 6.12.2 Features                                           | 313 |

| 6.12.3 Block Diagram                                      | 313 |

| 6.12.4 Basic Configuration                                | 314 |

| 6.12.5 Functional Description                             |     |

| 6.12.6 Register Map                                       | 324 |

| 6.12.7 Register Description                               |     |

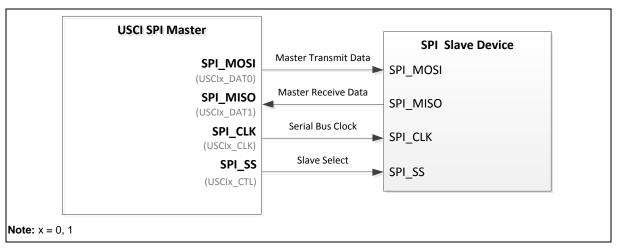

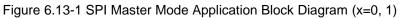

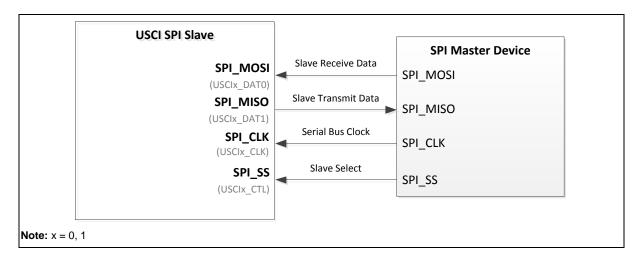

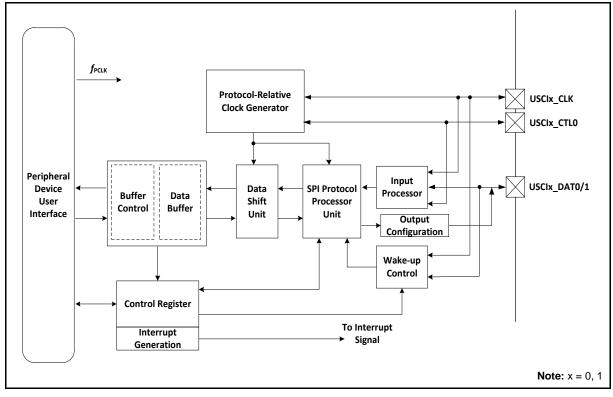

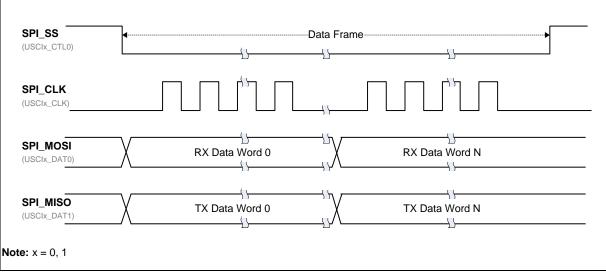

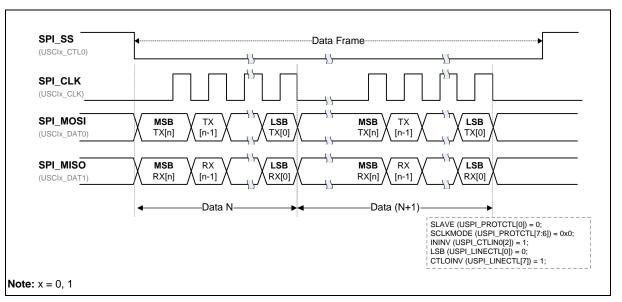

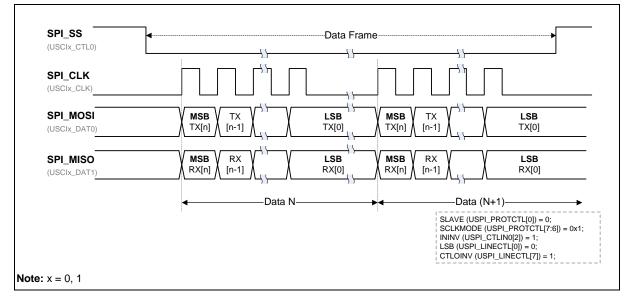

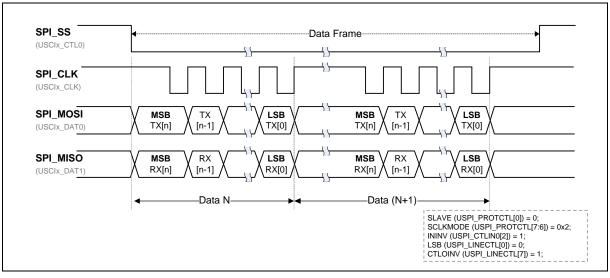

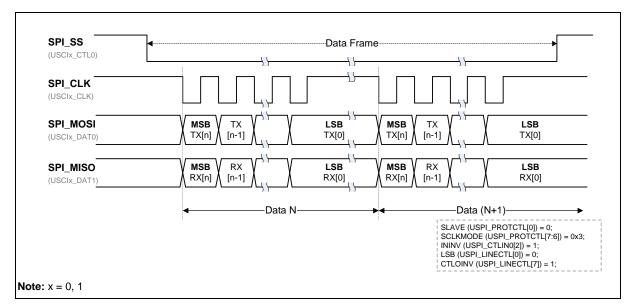

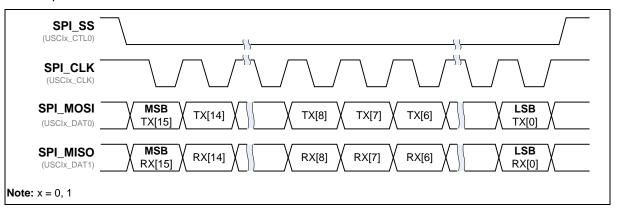

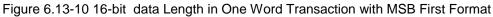

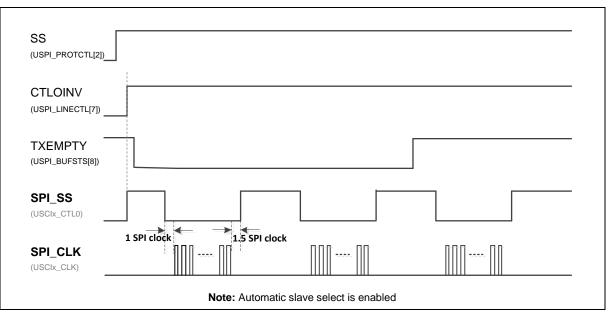

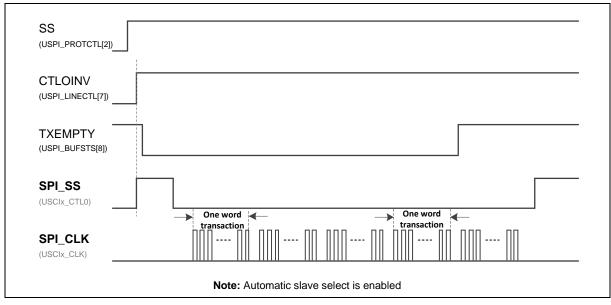

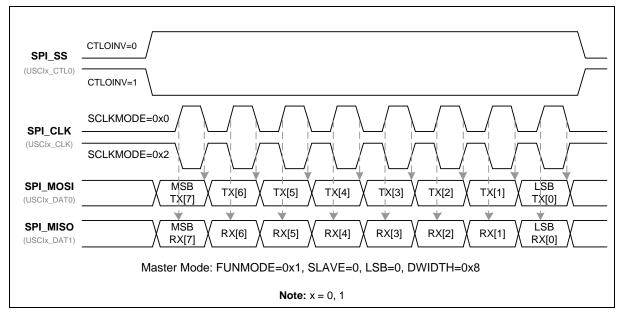

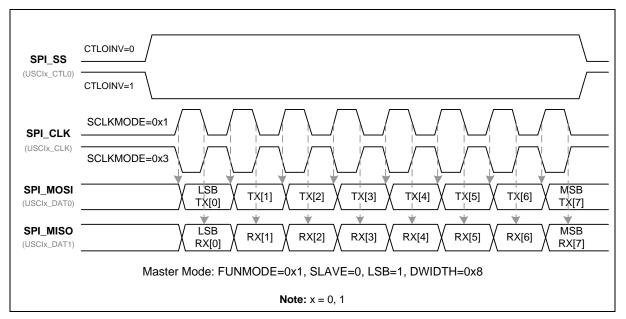

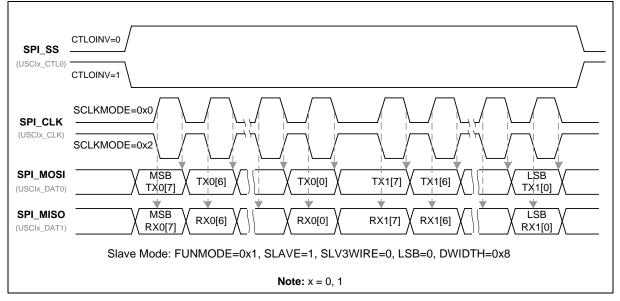

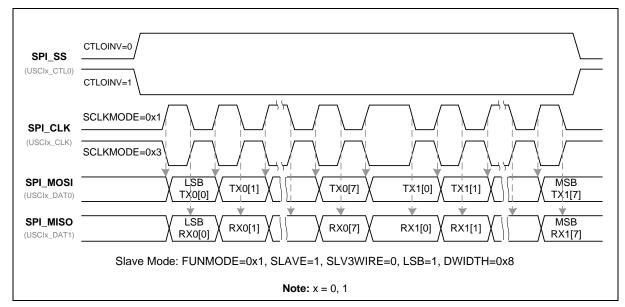

| 6.13 USCI – SPI Mode                                      | 346 |

| 6.13.1 Overview                                           | 346 |

| 6.13.2 Features                                           | 346 |

| 6.13.3 Block Diagram                                      | 347 |

| 6.13.4 Basic Configuration                                |     |

| 6.13.5 Functional Description                             | 348 |

| 6.13.6 Register Map                                       |     |

| 6.13.7 Register Description                               |     |

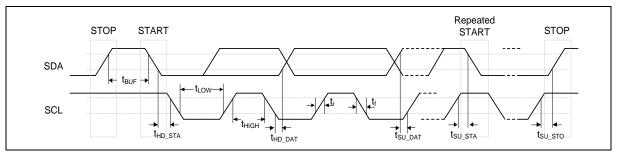

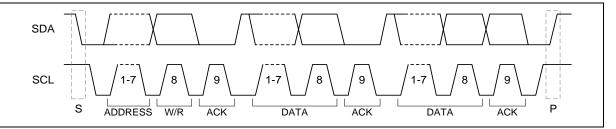

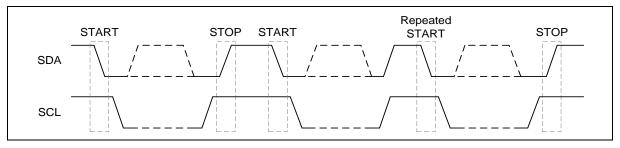

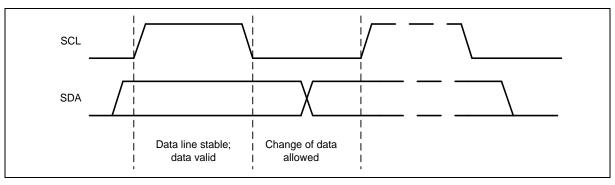

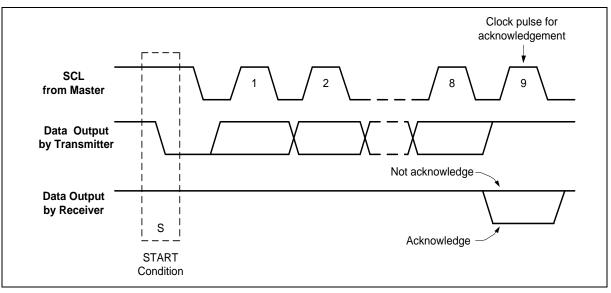

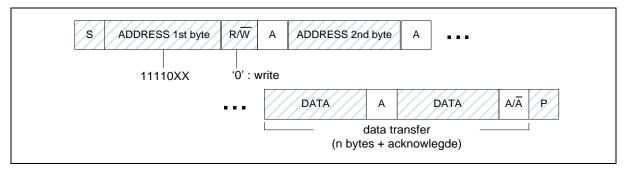

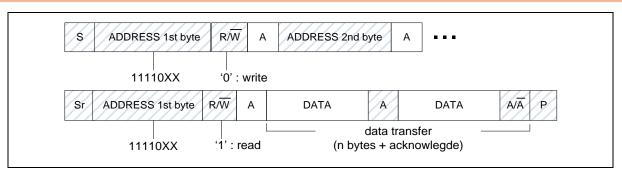

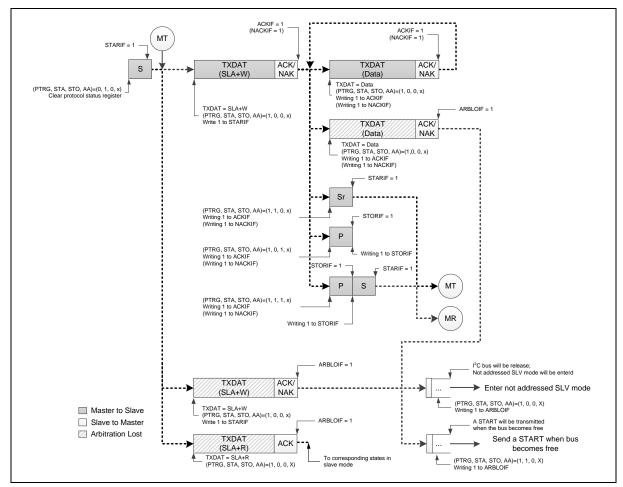

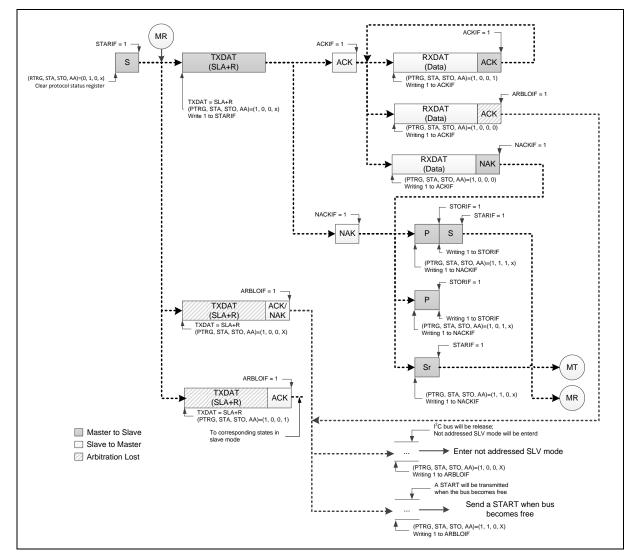

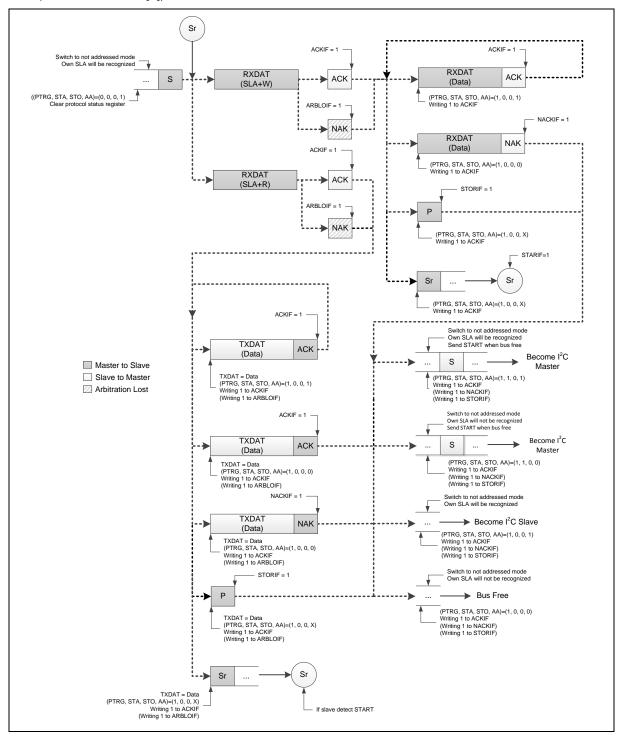

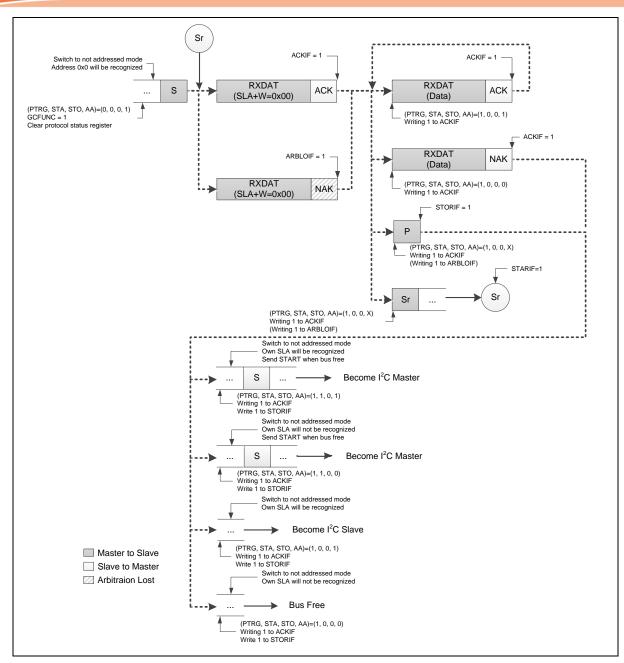

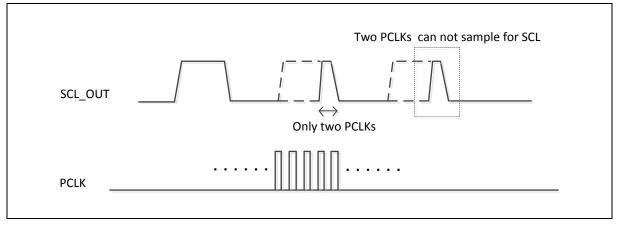

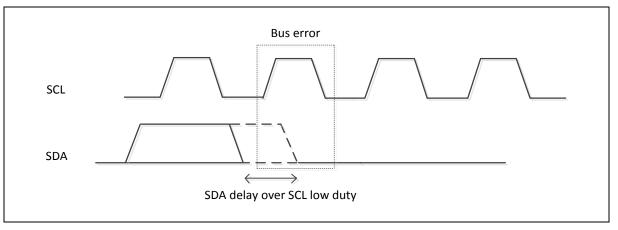

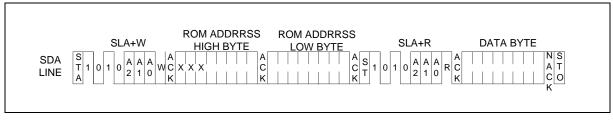

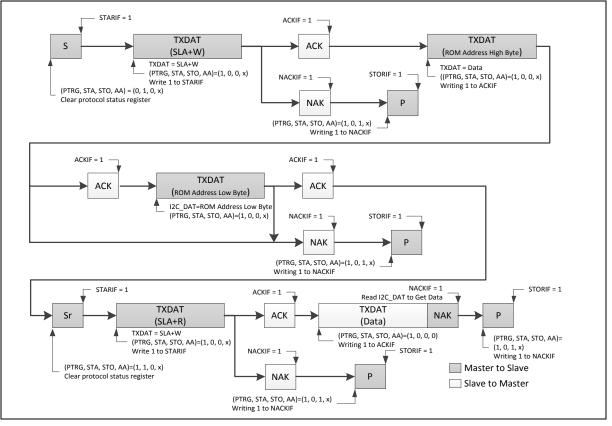

| 6.14 USCI – I <sup>2</sup> C Mode                         | 384 |

| 6.14.1 Overview                                           | 384 |

| 6.14.2 Features                                           | 384 |

| 6.14.3 Block Diagram                                      | 385 |

| 6.14.4 Basic Configuration                                |     |

| 6.14.5 Functional Description                             |     |

| 6.14.6 Register Map                                       |     |

| 6.14.7 Register Description                               |     |

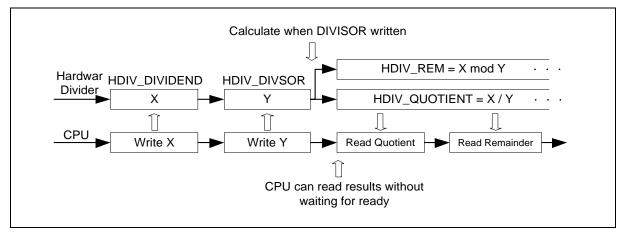

| 6.15 Hardware Divider (HDIV)                              |     |

| 6.15.1 Overview                                           |     |

| 6.15.2 Features                                           |     |

| 6.15.3 Basic Configuration                                |     |

| 6.15.4 Functional Description                             |     |

| 6.15.5 Register Map                                       | 424 |

### Mini57

|      |      | 6.15.6       | Register Description               | 425   |

|------|------|--------------|------------------------------------|-------|

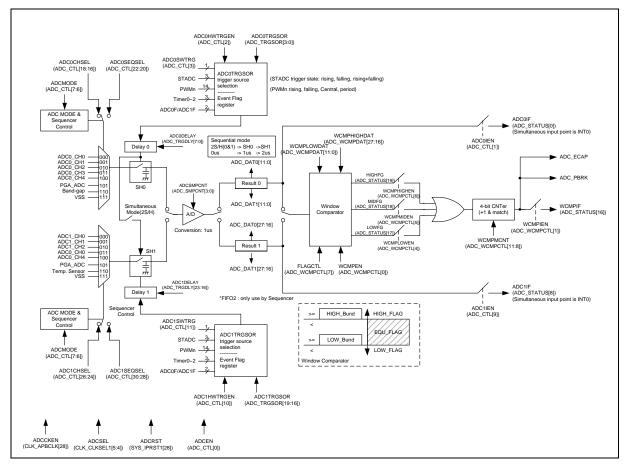

|      | 6.16 | Anal         | og to Digital Converter (ADC)      | . 430 |

|      |      | 1.1.1        | Overview                           | 430   |

|      |      | 1.1.2        | Features                           | 430   |

|      |      | 1.1.3        | Block Diagram                      | 430   |

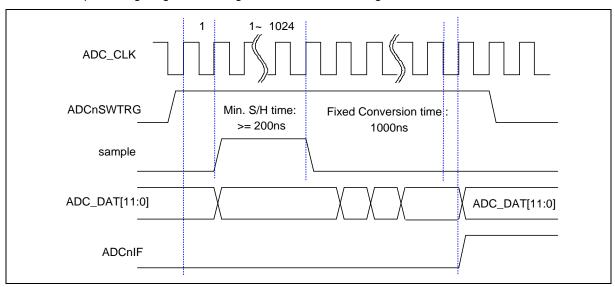

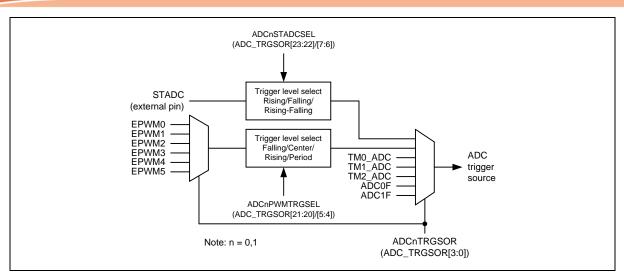

|      |      | 6.16.1       | Basic Configuration                | 431   |

|      |      | 6.16.2       | Functional Description             | 431   |

|      |      | 6.16.3       | Register Map                       | 435   |

|      |      | 6.16.4       | Register Description               | 436   |

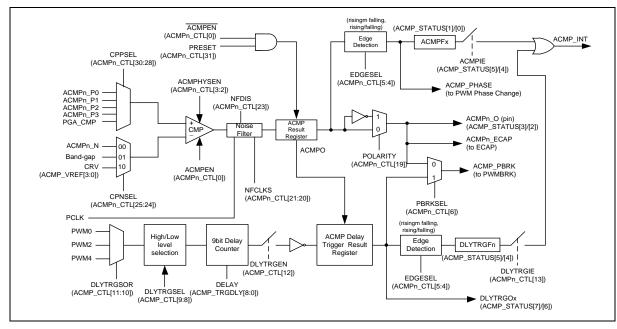

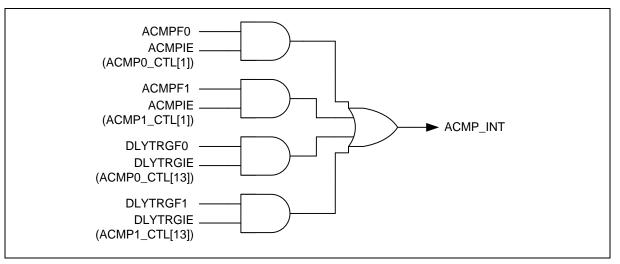

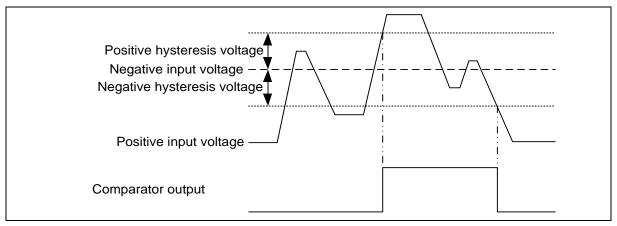

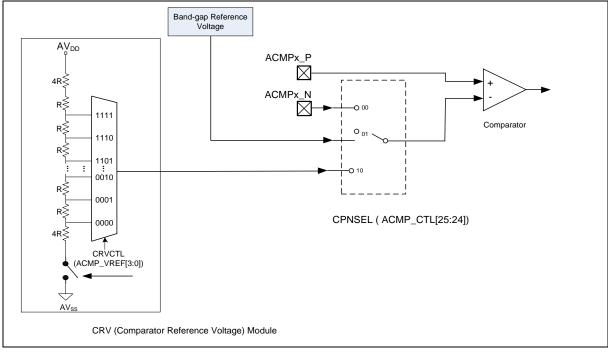

|      | 6.17 | Anal         | og Comparator (ACMP)               | . 452 |

|      |      | 6.17.1       | Overview                           | 452   |

|      |      | 6.17.2       | Features                           | 452   |

|      |      | 6.17.3       | Block Diagram                      | 453   |

|      |      |              | Basic Configuration                |       |

|      |      |              | Functional Description             |       |

|      |      |              | Comparator Reference Voltage (CRV) |       |

|      |      |              | Register Map                       |       |

|      |      |              | Register Description               |       |

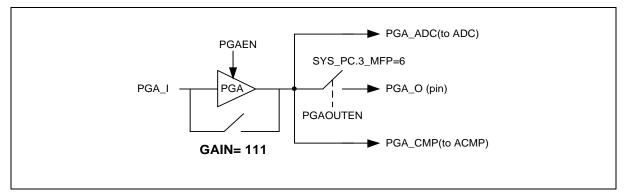

|      | 6.18 | 0            | rammable Gain Amplifier (PGA)      |       |

|      |      | 6.18.1       | Overview                           |       |

|      |      | 1.1.4        | Features                           |       |

|      |      | 1.1.5        | Block Diagram                      |       |

|      |      | 1.1.6        | Register Map                       |       |

|      |      |              | Register Description               |       |

|      |      |              | ON CIRCUIT                         |       |

| 8 EL | -EC1 | <b>TRICA</b> | L CHARACTERISTICS                  | 470   |

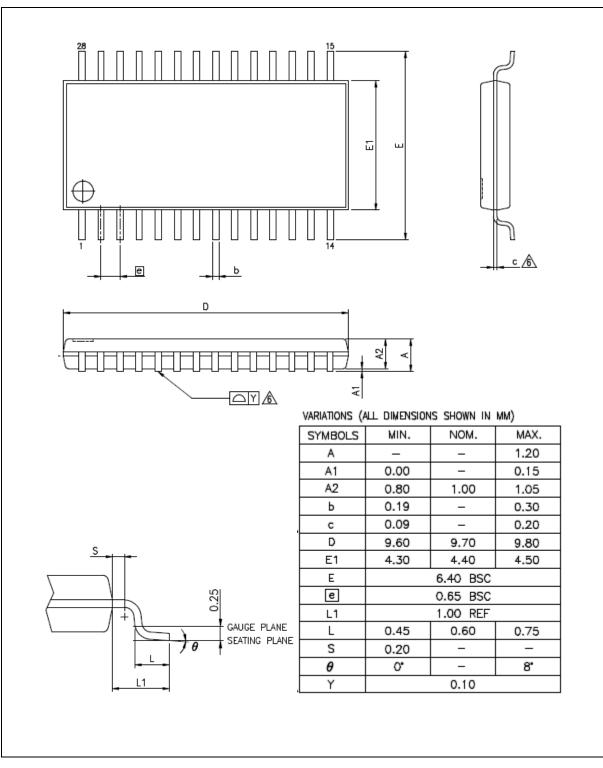

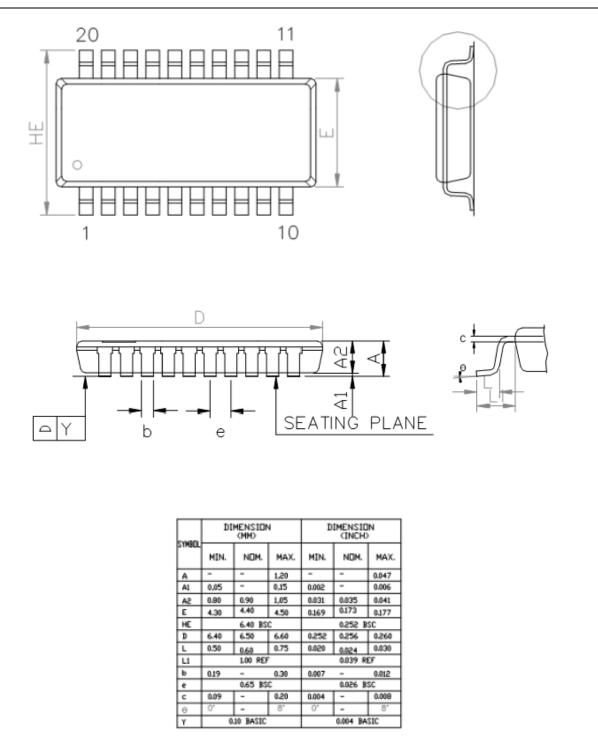

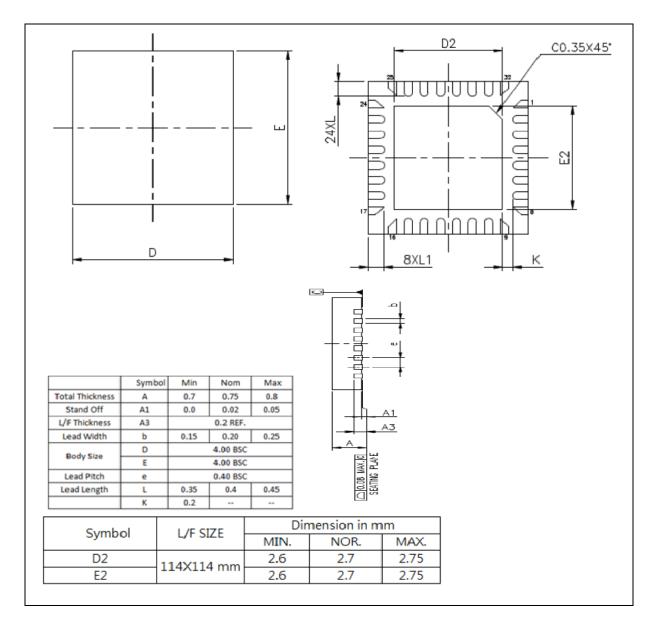

| 9P/  | ACK  | AGE [        | DIMENSIONS                         | 471   |

|      | 1.2  | 28-P         | in TSSOP (4.4x9.7x1.0 mm)          | . 471 |

|      | 1.3  | 20-P         | in TSSOP (4.4x6.5x0.9 mm)          | . 472 |

|      | 9.1  | 33-pi        | in *QFN33 (4x4x0.8 mm)             | . 473 |

| 10   | RE   | VISIO        | N HISTORY                          | 474   |

### List of Figures

| Figure 4.3-1 NuMicro® Mini57 Series TSSOP 28-pin Diagram       20         Figure 4.3-2 NuMicro® Mini57 Series TSSOP 28-pin Multi-function Diagram       20         Figure 4.3-3 NuMicro® Mini57 Series TSSOP 20-pin Diagram       21         Figure 4.3-4 NuMicro® Mini57 Series TSSOP 20-pin Multi-function Diagram       21         Figure 4.3-5 NuMicro® Mini57 Series QFN 33-pin Diagram       22         Figure 4.3-6 NuMicro® Mini57 Series QFN 33-pin Diagram       23         Figure 5.1-1 NuMicro® Mini57 Block Diagram       39         Figure 6.1-1 Functional Block Diagram       40         Figure 6.2-2 NRESET Reset Resources       43         Figure 6.2-3 Power-on Reset (POR) Waveform       45         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       46         Figure 6.2-5 Brown-out Detector (BOD) Waveform       47         Figure 6.2-6 Power Mode State Machine       48         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       51         Figure 6.3-8 NuMicro® Mini57 Flash, Security and Configuration Map       55         Figure 6.3-1 Clock Generator Block Diagram       113         Figure 6.3-2 System Clock Block Diagram       114         Figure 6.3-4 SysTick Clock Control Block Diagram       115         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       117         Figure 6.3-6 Clock Source of Frequency Di                                                             | Figure 4.3-2 NuMicro® Mini57 Series TSSOP 28-pin Multi-function Diagram       2         Figure 4.3-3 NuMicro® Mini57 Series TSSOP 20-pin Diagram       2         Figure 4.3-4 NuMicro® Mini57 Series TSSOP 20-pin Multi-function Diagram       2         Figure 4.3-5 NuMicro® Mini57 Series QFN 33-pin Diagram       2         Figure 5.1-1 NuMicro® Mini57 Series QFN 33-pin Multi-function Diagram       2         Figure 5.1-1 NuMicro® Mini57 Block Diagram       3         Figure 6.1-1 Functional Block Diagram       4         Figure 6.2-1 System Reset Resources       4         Figure 6.2-2 nRESET Reset Waveform       4         Figure 6.2-3 Power-on Reset (POR) Waveform       4         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       5         Figure 6.3-8 NuMicro® Mini57 Series Power Architecture Diagram       5         Figure 6.3-2 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Block Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 Suprick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11     <                                                                        | Figure 4.1-1 NuMicro <sup>®</sup> Mini57 Series Selection Code                      | 18  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|

| Figure 4.3-3 NuMicro® Mini57 Series TSSOP 20-pin Diagram       21         Figure 4.3-4 NuMicro® Mini57 Series TSSOP 20-pin Multi-function Diagram       21         Figure 4.3-5 NuMicro® Mini57 Series QFN 33-pin Diagram       22         Figure 4.3-6 NuMicro® Mini57 Series QFN 33-pin Multi-function Diagram       23         Figure 5.1-1 NuMicro® Mini57 Block Diagram       39         Figure 6.1-1 Functional Block Diagram       40         Figure 6.2-1 System Reset Resources       43         Figure 6.2-3 Power-on Reset (POR) Waveform       45         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       46         Figure 6.2-5 Brown-out Detector (BOD) Waveform       47         Figure 6.2-6 Power Mode State Machine       48         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       51         Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map       55         Figure 6.3-1 Clock Generator Block Diagram       113         Figure 6.3-2 Clock Generator Global View Diagram       114         Figure 6.3-3 System Clock Block Diagram       116         Figure 6.3-4 SysTick Clock Control Block Diagram       116         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       117         Figure 6.3-7 Block Diagram of Frequency Divider       119         Figure 6.4-4 SpROM Security Mode       139                                                                           | Figure 4.3-3 NuMicro® Mini57 Series TSSOP 20-pin Diagram       2         Figure 4.3-4 NuMicro® Mini57 Series TSSOP 20-pin Multi-function Diagram       2         Figure 4.3-5 NuMicro® Mini57 Series QFN 33-pin Diagram       2         Figure 4.3-6 NuMicro® Mini57 Series QFN 33-pin Multi-function Diagram       2         Figure 5.1-1 NuMicro® Mini57 Block Diagram       3         Figure 6.1-1 Functional Block Diagram       4         Figure 6.2-1 System Reset Resources       4         Figure 6.2-2 nRESET Reset Waveform       4         Figure 6.2-3 Power-on Reset (POR) Waveform       4         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       5         Figure 6.2-9 SRAM Block Diagram       5         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.3-6 Clock Source of Frequency Divider       11         Figure 6.4-1 Flash Memory Organization       13         Figure 6.4-2 Flash Memory Organizat                                                                                             | Figure 4.3-1 NuMicro <sup>®</sup> Mini57 Series TSSOP 28-pin Diagram                | 20  |

| Figure 4.3-4 NuMicro <sup>®</sup> Mini57 Series TSSOP 20-pin Multi-function Diagram       21         Figure 4.3-5 NuMicro <sup>®</sup> Mini57 Series QFN 33-pin Diagram       22         Figure 4.3-6 NuMicro <sup>®</sup> Mini57 Series QFN 33-pin Multi-function Diagram       23         Figure 5.1-1 NuMicro <sup>®</sup> Mini57 Series QFN 33-pin Multi-function Diagram       23         Figure 6.1-1 Functional Block Diagram       39         Figure 6.1-1 Functional Block Diagram       40         Figure 6.2-1 System Reset Resources       43         Figure 6.2-2 nRESET Reset Waveform       45         Figure 6.2-3 Power-on Reset (POR) Waveform       46         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       46         Figure 6.2-5 Brown-out Detector (BOD) Waveform       47         Figure 6.2-6 Power Mode State Machine       48         Figure 6.2-7 NuMicro <sup>®</sup> Mini57 Series Power Architecture Diagram       51         Figure 6.2-8 NuMicro <sup>®</sup> Mini57 Flash, Security and Configuration Map       55         Figure 6.3-1 Clock Generator Global View Diagram       113         Figure 6.3-2 Clock Generator Global View Diagram       114         Figure 6.3-3 System Clock Block Diagram       115         Figure 6.3-4 SysTick Clock Control Block Diagram       116         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       117         Figure 6.3-7 Block Diagram of Frequency Divi | Figure 4.3-4 NuMicro® Mini57 Series TSSOP 20-pin Multi-function Diagram       2         Figure 4.3-5 NuMicro® Mini57 Series QFN 33-pin Diagram       2         Figure 4.3-6 NuMicro® Mini57 Series QFN 33-pin Multi-function Diagram       2         Figure 5.1-1 NuMicro® Mini57 Block Diagram       3         Figure 6.1-1 Functional Block Diagram       4         Figure 6.2-1 System Reset Resources       4         Figure 6.2-2 nRESET Reset Waveform       4         Figure 6.2-3 Power-on Reset (POR) Waveform       4         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro® Mini57 Flash, Security and Configuration Map       5         Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map       5         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Global View Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.4-1 Flash Memory Organization       13         Figure 6.4-2 Flash Memory Organization       13         Figure 6.4-                                                                                             | Figure 4.3-2 NuMicro <sup>®</sup> Mini57 Series TSSOP 28-pin Multi-function Diagram | 20  |

| Figure 4.3-5 NuMicro <sup>®</sup> Mini57 Series QFN 33-pin Diagram       22         Figure 4.3-6 NuMicro <sup>®</sup> Mini57 Series QFN 33-pin Multi-function Diagram       23         Figure 5.1-1 NuMicro <sup>®</sup> Mini57 Block Diagram       39         Figure 6.1-1 Functional Block Diagram       40         Figure 6.2-1 System Reset Resources       43         Figure 6.2-2 nRESET Reset Waveform       45         Figure 6.2-3 Power-on Reset (POR) Waveform       45         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       46         Figure 6.2-5 Brown-out Detector (BOD) Waveform       47         Figure 6.2-6 Power Mode State Machine       48         Figure 6.2-7 NuMicro <sup>®</sup> Mini57 Series Power Architecture Diagram       51         Figure 6.2-8 NuMicro <sup>®</sup> Mini57 Flash, Security and Configuration Map       55         Figure 6.3-1 Clock Generator Block Diagram       113         Figure 6.3-2 Clock Generator Global View Diagram       114         Figure 6.3-3 System Clock Block Diagram       115         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       117         Figure 6.3-6 Clock Source of Frequency Divider       119         Figure 6.3-7 Block Diagram of Frequency Divider       119         Figure 6.3-7 Block Diagram of Frequency Divider       119         Figure 6.4-1 Flash Memory Organization       136         F                                              | Figure 4.3-5 NuMicro® Mini57 Series QFN 33-pin Diagram       2         Figure 4.3-6 NuMicro® Mini57 Series QFN 33-pin Multi-function Diagram       2         Figure 5.1-1 NuMicro® Mini57 Block Diagram       3         Figure 6.1-1 Functional Block Diagram       4         Figure 6.2-1 System Reset Resources       4         Figure 6.2-2 nRESET Reset Waveform       4         Figure 6.2-3 Power-on Reset (POR) Waveform       4         Figure 6.2-3 Power-on Reset (POR) Waveform       4         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro® Mini57 Flash, Security and Configuration Map       5         Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map       5         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Global View Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SuysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.3-6 Clock Source of Frequency Divider       11         Figure 6.4-1 Flash Memory Organization       13         Figure 6.4-2 Flash Memory Organ                                                                                             | Figure 4.3-3 NuMicro <sup>®</sup> Mini57 Series TSSOP 20-pin Diagram                | 21  |

| Figure 4.3-6 NuMicro® Mini57 Series QFN 33-pin Multi-function Diagram       23         Figure 5.1-1 NuMicro® Mini57 Block Diagram       39         Figure 6.1-1 Functional Block Diagram       40         Figure 6.2-1 System Reset Resources       43         Figure 6.2-2 nRESET Reset Waveform       45         Figure 6.2-3 Power-on Reset (POR) Waveform       45         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       46         Figure 6.2-5 Brown-out Detector (BOD) Waveform       47         Figure 6.2-6 Power Mode State Machine       48         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       51         Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map       55         Figure 6.3-1 Clock Generator Block Diagram       113         Figure 6.3-2 Clock Generator Global View Diagram       114         Figure 6.3-3 System Clock Block Diagram       115         Figure 6.3-4 SysTick Clock Control Block Diagram       116         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       117         Figure 6.3-7 Block Diagram of Frequency Divider       119         Figure 6.4-4 Spred Mamory Organization       136         Figure 6.3-5 Reset Namery Organization       136         Figure 6.4-4 SPROM Security Mode       139         Figure 6.4-5 Boot Select (BS) for Power                                                                                                | Figure 4.3-6 NuMicro® Mini57 Series QFN 33-pin Multi-function Diagram       2         Figure 5.1-1 NuMicro® Mini57 Block Diagram       3         Figure 6.1-1 Functional Block Diagram       4         Figure 6.2-1 System Reset Resources       4         Figure 6.2-2 nRESET Reset Waveform       4         Figure 6.2-3 Power-on Reset (POR) Waveform       4         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       5         Figure 6.2-8 NuMicro® Mini57 Series Power Architecture Diagram       5         Figure 6.2-9 SRAM Block Diagram       5         Figure 6.2-9 SRAM Block Diagram       11         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Global View Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.3-7 Block Diagram of Frequency Divider       11         Figure 6.4-2 Flash Memory Control Block Diagram       13         Figure 6.4-3 Data Flash Shared with APROM       13 <td>Figure 4.3-4 NuMicro<sup>®</sup> Mini57 Series TSSOP 20-pin Multi-function Diagram</td> <td> 21</td> | Figure 4.3-4 NuMicro <sup>®</sup> Mini57 Series TSSOP 20-pin Multi-function Diagram | 21  |

| Figure 5.1-1 NuMicro® Mini57 Block Diagram       39         Figure 6.1-1 Functional Block Diagram       40         Figure 6.2-1 System Reset Resources       43         Figure 6.2-2 nRESET Reset Waveform       45         Figure 6.2-3 Power-on Reset (POR) Waveform       45         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       46         Figure 6.2-5 Brown-out Detector (BOD) Waveform       47         Figure 6.2-6 Power Mode State Machine       48         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       51         Figure 6.2-9 SRAM Block Diagram       55         Figure 6.2-9 SRAM Block Diagram       57         Figure 6.3-1 Clock Generator Block Diagram       113         Figure 6.3-2 Clock Generator Block Diagram       114         Figure 6.3-3 System Clock Block Diagram       115         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       117         Figure 6.3-6 Clock Source of Frequency Divider       119         Figure 6.4-1 Flash Memory Control Block Diagram       134         Figure 6.4-2 Flash Memory Organization       136         Figure 6.4-2 Flash Memory Organization       137         Figure 6.4-4 SPROM Security Mode       139         Figure 6.4-5 Boot Select (BS) for Power-on Action       144                                                                                                                                                             | Figure 5.1-1 NuMicro® Mini57 Block Diagram       3         Figure 6.1-1 Functional Block Diagram       4         Figure 6.2-1 System Reset Resources       4         Figure 6.2-2 nRESET Reset Waveform       4         Figure 6.2-3 Power-on Reset (POR) Waveform       4         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       5         Figure 6.2-8 NuMicro® Mini57 Series Power Architecture Diagram       5         Figure 6.2-9 SRAM Block Diagram       5         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Global View Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.3-7 Block Diagram of Frequency Divider       11         Figure 6.4-1 Flash Memory Organization       13         Figure 6.4-2 Flash Memory Organization       13         Figure 6.4-3 Data Flash Shared with APROM       13         Figure 6.4-4 SPROM Security Mode       13         Figure                                                                                                                                 | Figure 4.3-5 NuMicro <sup>®</sup> Mini57 Series QFN 33-pin Diagram                  | 22  |

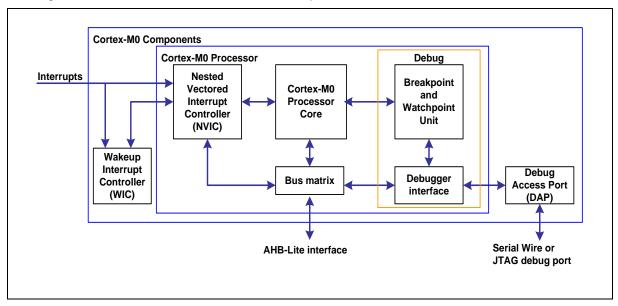

| Figure 6.1-1 Functional Block Diagram.       40         Figure 6.2-1 System Reset Resources       43         Figure 6.2-2 nRESET Reset Waveform       45         Figure 6.2-3 Power-on Reset (POR) Waveform       45         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       46         Figure 6.2-5 Brown-out Detector (BOD) Waveform       47         Figure 6.2-6 Power Mode State Machine       48         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       51         Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map       55         Figure 6.2-9 SRAM Block Diagram       57         Figure 6.3-1 Clock Generator Block Diagram       113         Figure 6.3-2 Clock Generator Block Diagram       114         Figure 6.3-3 System Clock Block Diagram       115         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       117         Figure 6.3-6 Clock Source of Frequency Divider       119         Figure 6.4-1 Flash Memory Control Block Diagram       134         Figure 6.4-2 Flash Memory Organization       136         Figure 6.4-3 Data Flash Shared with APROM       137         Figure 6.4-4 SPROM Security Mode       139         Figure 6.4-5 Boot Select (BS) for Power-on Action       144                                                                                                                                                                                  | Figure 6.1-1 Functional Block Diagram.       4         Figure 6.2-1 System Reset Resources       4         Figure 6.2-2 nRESET Reset Waveform       4         Figure 6.2-3 Power-on Reset (POR) Waveform       4         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro <sup>®</sup> Mini57 Series Power Architecture Diagram       5         Figure 6.2-8 NuMicro <sup>®</sup> Mini57 Flash, Security and Configuration Map       5         Figure 6.2-9 SRAM Block Diagram       5         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Global View Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.3-7 Block Diagram of Frequency Divider       11         Figure 6.4-1 Flash Memory Control Block Diagram       13         Figure 6.4-2 Flash Memory Organization       13         Figure 6.4-3 Data Flash Shared with APROM       13         Figure 6.4-4 SPROM Security Mode       13         Figure 6.4-5 Boot Select (BS) for Power-on Action       14                                                                                                  | Figure 4.3-6 NuMicro <sup>®</sup> Mini57 Series QFN 33-pin Multi-function Diagram   | 23  |

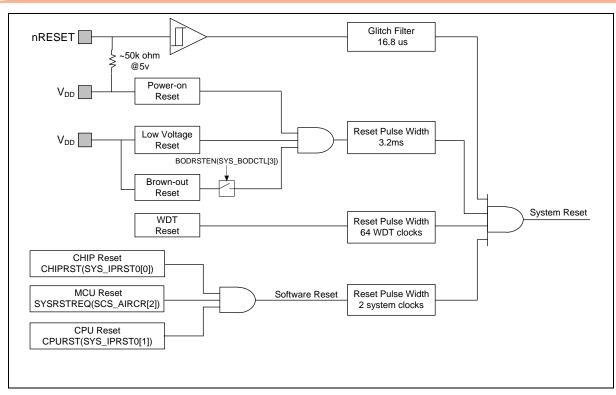

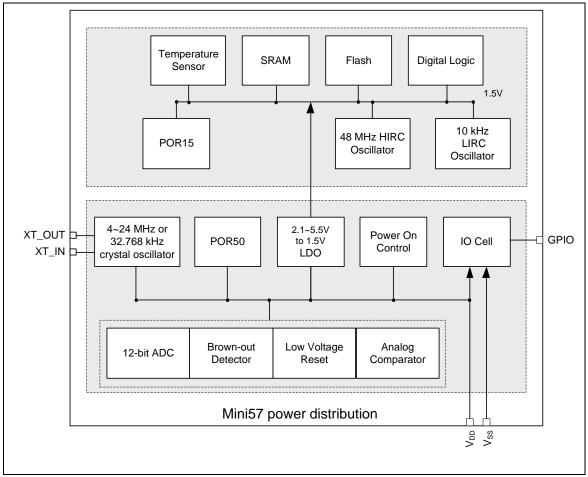

| Figure 6.2-1 System Reset Resources       43         Figure 6.2-2 nRESET Reset Waveform       45         Figure 6.2-3 Power-on Reset (POR) Waveform       45         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       46         Figure 6.2-5 Brown-out Detector (BOD) Waveform       47         Figure 6.2-6 Power Mode State Machine       48         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       51         Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map       55         Figure 6.2-9 SRAM Block Diagram       57         Figure 6.3-1 Clock Generator Block Diagram       113         Figure 6.3-2 Clock Generator Global View Diagram       114         Figure 6.3-3 System Clock Block Diagram       115         Figure 6.3-4 SysTick Clock Control Block Diagram       116         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       117         Figure 6.3-7 Block Diagram of Frequency Divider       119         Figure 6.4-1 Flash Memory Control Block Diagram       134         Figure 6.4-2 Flash Memory Organization       136         Figure 6.4-3 Data Flash Shared with APROM       137         Figure 6.4-4 SPROM Security Mode       139         Figure 6.4-5 Boot Select (BS) for Power-on Action       144                                                                                                                                                                | Figure 6.2-1 System Reset Resources       4         Figure 6.2-2 nRESET Reset Waveform       4         Figure 6.2-3 Power-on Reset (POR) Waveform       4         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       5         Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map       5         Figure 6.2-9 SRAM Block Diagram       5         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Global View Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.3-7 Block Diagram of Frequency Divider       11         Figure 6.4-1 Flash Memory Organization       13         Figure 6.4-2 Flash Memory Organization       13         Figure 6.4-3 Data Flash Shared with APROM       13         Figure 6.4-4 SPROM Security Mode       13         Figure 6.4-5 Boot Select (BS) for Power-on Action       14      <                                                                                                                    | Figure 5.1-1 NuMicro <sup>®</sup> Mini57 Block Diagram                              | 39  |

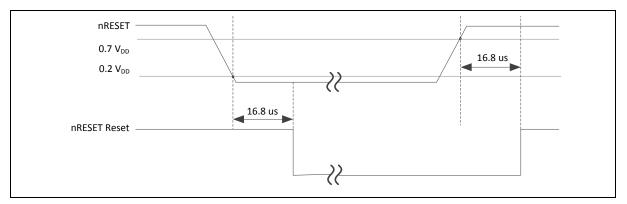

| Figure 6.2-2 nRESET Reset Waveform45Figure 6.2-3 Power-on Reset (POR) Waveform45Figure 6.2-4 Low Voltage Reset (LVR) Waveform46Figure 6.2-5 Brown-out Detector (BOD) Waveform47Figure 6.2-6 Power Mode State Machine48Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram51Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map55Figure 6.2-9 SRAM Block Diagram57Figure 6.3-1 Clock Generator Block Diagram113Figure 6.3-2 Clock Generator Global View Diagram114Figure 6.3-3 System Clock Block Diagram115Figure 6.3-4 SysTick Clock Control Block Diagram116Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK117Figure 6.3-7 Block Diagram of Frequency Divider119Figure 6.4-1 Flash Memory Control Block Diagram134Figure 6.4-2 Flash Memory Organization136Figure 6.4-3 Data Flash Shared with APROM137Figure 6.4-4 SPROM Security Mode139Figure 6.4-5 Boot Select (BS) for Power-on Action144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 6.2-2 nRESET Reset Waveform       4         Figure 6.2-3 Power-on Reset (POR) Waveform       4         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       5         Figure 6.2-7 NuMicro® Mini57 Flash, Security and Configuration Map       5         Figure 6.2-9 SRAM Block Diagram       5         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Global View Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.3-7 Block Diagram of Frequency Divider       11         Figure 6.4-1 Flash Memory Control Block Diagram       13         Figure 6.4-2 Flash Memory Organization       13         Figure 6.4-4 SPROM Security Mode       13         Figure 6.4-5 Boot Select (BS) for Power-on Action       14         Figure 6.4-6 Flash Memory Mapping of CBS in CONFIG0       14         Figure 6.4-7 Executable Range of Code with IAP Function Enabled       14                                                                                                                                          | Figure 6.1-1 Functional Block Diagram                                               | 40  |

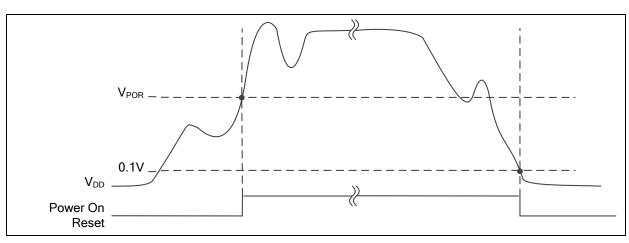

| Figure 6.2-3 Power-on Reset (POR) Waveform45Figure 6.2-4 Low Voltage Reset (LVR) Waveform46Figure 6.2-5 Brown-out Detector (BOD) Waveform47Figure 6.2-6 Power Mode State Machine48Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram51Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map55Figure 6.2-9 SRAM Block Diagram57Figure 6.3-1 Clock Generator Block Diagram113Figure 6.3-2 Clock Generator Global View Diagram114Figure 6.3-3 System Clock Block Diagram115Figure 6.3-4 SysTick Clock Control Block Diagram116Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK117Figure 6.3-7 Block Diagram of Frequency Divider119Figure 6.4-1 Flash Memory Control Block Diagram134Figure 6.4-2 Flash Memory Organization136Figure 6.4-3 Data Flash Shared with APROM137Figure 6.4-4 SPROM Security Mode139Figure 6.4-5 Boot Select (BS) for Power-on Action144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 6.2-3 Power-on Reset (POR) Waveform       4         Figure 6.2-4 Low Voltage Reset (LVR) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro <sup>®</sup> Mini57 Series Power Architecture Diagram       5         Figure 6.2-8 NuMicro <sup>®</sup> Mini57 Flash, Security and Configuration Map       5         Figure 6.2-9 SRAM Block Diagram       5         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Global View Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.3-7 Block Diagram of Frequency Divider       11         Figure 6.4-1 Flash Memory Control Block Diagram       13         Figure 6.4-2 Flash Memory Organization       13         Figure 6.4-3 Data Flash Shared with APROM       13         Figure 6.4-4 SPROM Security Mode       13         Figure 6.4-5 Boot Select (BS) for Power-on Action       14         Figure 6.4-6 Flash Memory Mapping of CBS in CONFIGO       14         Figure 6.4-7 Executable Range of Code with IAP Func                                                                         | Figure 6.2-1 System Reset Resources                                                 | 43  |

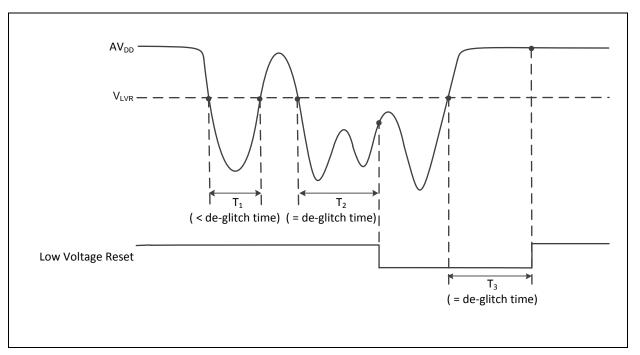

| Figure 6.2-4 Low Voltage Reset (LVR) Waveform.46Figure 6.2-5 Brown-out Detector (BOD) Waveform47Figure 6.2-6 Power Mode State Machine48Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram51Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map55Figure 6.2-9 SRAM Block Diagram57Figure 6.3-1 Clock Generator Block Diagram113Figure 6.3-2 Clock Generator Global View Diagram114Figure 6.3-3 System Clock Block Diagram115Figure 6.3-4 SysTick Clock Control Block Diagram116Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK117Figure 6.3-7 Block Diagram of Frequency Divider119Figure 6.4-1 Flash Memory Control Block Diagram134Figure 6.4-2 Flash Memory Organization136Figure 6.4-3 Data Flash Shared with APROM137Figure 6.4-4 SPROM Security Mode139Figure 6.4-5 Boot Select (BS) for Power-on Action144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 6.2-4 Low Voltage Reset (LVR) Waveform       4         Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro <sup>®</sup> Mini57 Series Power Architecture Diagram       5         Figure 6.2-8 NuMicro <sup>®</sup> Mini57 Flash, Security and Configuration Map       5         Figure 6.2-9 SRAM Block Diagram       5         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Global View Diagram       11         Figure 6.3-2 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Control Block Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.3-7 Block Diagram of Frequency Divider       11         Figure 6.4-1 Flash Memory Control Block Diagram       13         Figure 6.4-2 Flash Memory Organization       13         Figure 6.4-3 Data Flash Shared with APROM       13         Figure 6.4-5 Boot Select (BS) for Power-on Action       14         Figure 6.4-6 Flash Memory Mapping of CBS in CONFIG0       14         Figure 6.4-7 Executable Range of Code with                                                                         | Figure 6.2-2 nRESET Reset Waveform                                                  | 45  |

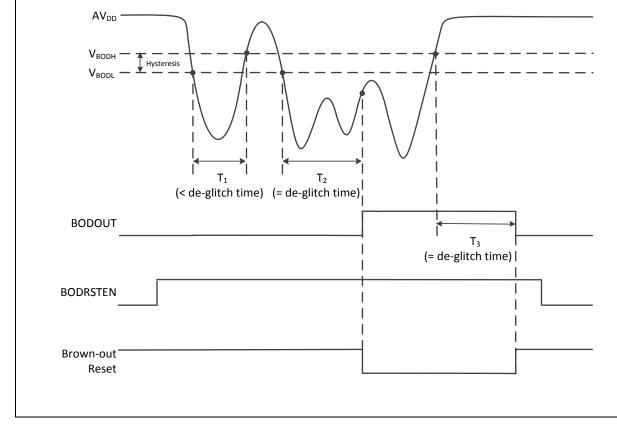

| Figure 6.2-5 Brown-out Detector (BOD) Waveform47Figure 6.2-6 Power Mode State Machine48Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram51Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map55Figure 6.2-9 SRAM Block Diagram57Figure 6.3-1 Clock Generator Block Diagram113Figure 6.3-2 Clock Generator Global View Diagram114Figure 6.3-2 Clock Generator Global View Diagram115Figure 6.3-3 System Clock Block Diagram116Figure 6.3-4 SysTick Clock Control Block Diagram116Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK117Figure 6.3-6 Clock Source of Frequency Divider119Figure 6.3-7 Block Diagram of Frequency Divider119Figure 6.4-1 Flash Memory Organization136Figure 6.4-2 Flash Memory Organization137Figure 6.4-3 Data Flash Shared with APROM137Figure 6.4-4 SPROM Security Mode139Figure 6.4-5 Boot Select (BS) for Power-on Action144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 6.2-5 Brown-out Detector (BOD) Waveform       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-6 Power Mode State Machine       4         Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       5         Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map       5         Figure 6.2-9 SRAM Block Diagram       5         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Global View Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.3-6 Clock Source of Frequency Divider       11         Figure 6.3-7 Block Diagram of Frequency Divider       11         Figure 6.4-1 Flash Memory Control Block Diagram       13         Figure 6.4-2 Flash Memory Organization       13         Figure 6.4-3 Data Flash Shared with APROM       13         Figure 6.4-5 Boot Select (BS) for Power-on Action       14         Figure 6.4-6 Flash Memory Mapping of CBS in CONFIG0       14         Figure 6.4-7 Executable Range of Code with IAP Function Enabled       14                                                                                                                                                                                       | Figure 6.2-3 Power-on Reset (POR) Waveform                                          | 45  |

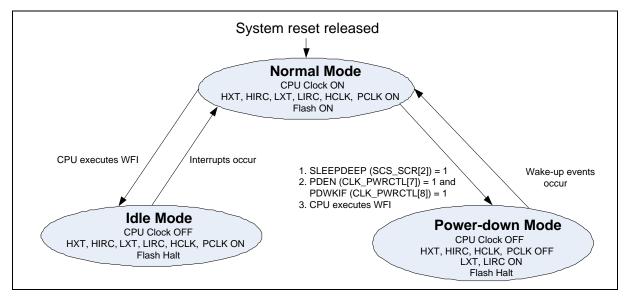

| Figure 6.2-6 Power Mode State Machine48Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram51Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map55Figure 6.2-9 SRAM Block Diagram57Figure 6.3-1 Clock Generator Block Diagram113Figure 6.3-2 Clock Generator Global View Diagram114Figure 6.3-3 System Clock Block Diagram115Figure 6.3-4 SysTick Clock Control Block Diagram116Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK117Figure 6.3-6 Clock Source of Frequency Divider119Figure 6.4-1 Flash Memory Control Block Diagram134Figure 6.4-2 Flash Memory Organization136Figure 6.4-3 Data Flash Shared with APROM137Figure 6.4-5 Boot Select (BS) for Power-on Action144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 6.2-6 Power Mode State Machine4Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram5Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map5Figure 6.2-9 SRAM Block Diagram5Figure 6.3-1 Clock Generator Block Diagram11Figure 6.3-2 Clock Generator Global View Diagram11Figure 6.3-3 System Clock Block Diagram11Figure 6.3-4 SysTick Clock Control Block Diagram11Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK11Figure 6.3-6 Clock Source of Frequency Divider11Figure 6.4-1 Flash Memory Control Block Diagram13Figure 6.4-2 Flash Memory Organization13Figure 6.4-3 Data Flash Shared with APROM13Figure 6.4-4 SPROM Security Mode13Figure 6.4-5 Boot Select (BS) for Power-on Action14Figure 6.4-6 Flash Memory Mapping of CBS in CONFIG014Figure 6.4-7 Executable Range of Code with IAP Function Enabled14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 6.2-4 Low Voltage Reset (LVR) Waveform                                       | 46  |

| Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       51         Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map       55         Figure 6.2-9 SRAM Block Diagram       57         Figure 6.3-1 Clock Generator Block Diagram       113         Figure 6.3-2 Clock Generator Global View Diagram       114         Figure 6.3-2 Clock Generator Global View Diagram       115         Figure 6.3-3 System Clock Block Diagram       116         Figure 6.3-4 SysTick Clock Control Block Diagram       116         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       117         Figure 6.3-6 Clock Source of Frequency Divider       119         Figure 6.3-7 Block Diagram of Frequency Divider       119         Figure 6.4-1 Flash Memory Control Block Diagram       134         Figure 6.4-2 Flash Memory Organization       136         Figure 6.4-3 Data Flash Shared with APROM       137         Figure 6.4-4 SPROM Security Mode       139         Figure 6.4-5 Boot Select (BS) for Power-on Action       144                                                                                                                                                                                                                                                                                                                                                                                       | Figure 6.2-7 NuMicro® Mini57 Series Power Architecture Diagram       5         Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map       5         Figure 6.2-9 SRAM Block Diagram       5         Figure 6.3-1 Clock Generator Block Diagram       11         Figure 6.3-2 Clock Generator Global View Diagram       11         Figure 6.3-3 System Clock Block Diagram       11         Figure 6.3-4 SysTick Clock Control Block Diagram       11         Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK       11         Figure 6.3-6 Clock Source of Frequency Divider       11         Figure 6.3-7 Block Diagram of Frequency Divider       11         Figure 6.4-1 Flash Memory Control Block Diagram       13         Figure 6.4-2 Flash Memory Organization       13         Figure 6.4-3 Data Flash Shared with APROM       13         Figure 6.4-5 Boot Select (BS) for Power-on Action       14         Figure 6.4-6 Flash Memory Mapping of CBS in CONFIG0       14         Figure 6.4-7 Executable Range of Code with IAP Function Enabled       14                                                                                                                                                                                                                                                                                                                                                                  | Figure 6.2-5 Brown-out Detector (BOD) Waveform                                      | 47  |

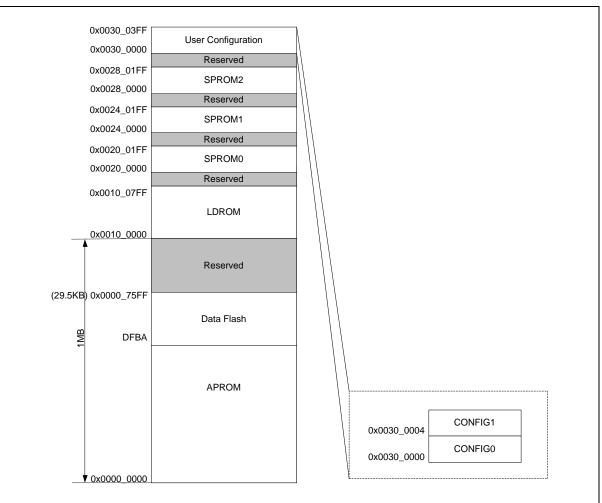

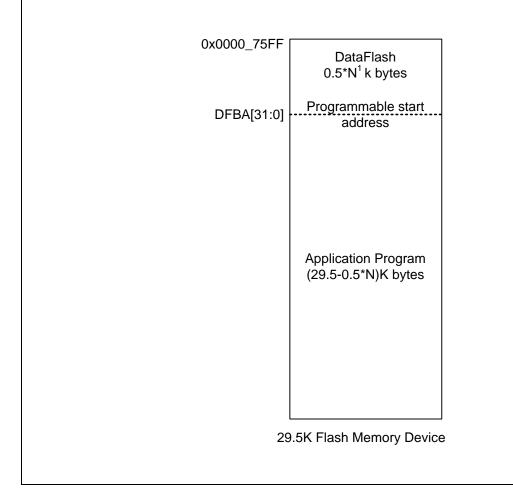

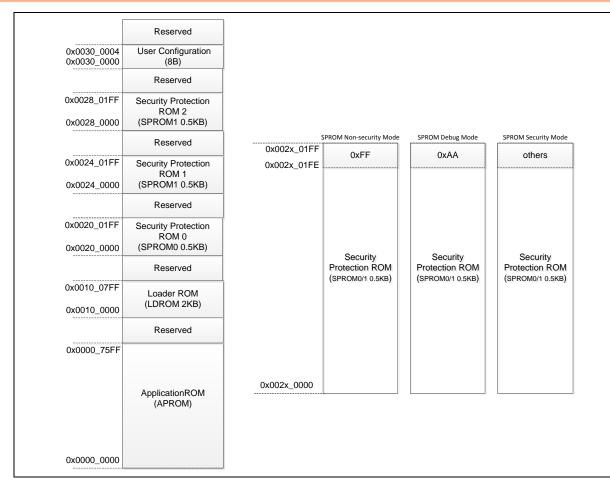

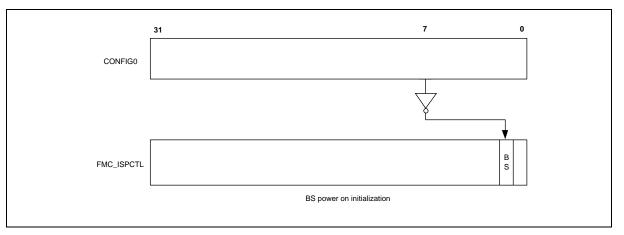

| Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map55Figure 6.2-9 SRAM Block Diagram57Figure 6.3-1 Clock Generator Block Diagram113Figure 6.3-2 Clock Generator Global View Diagram114Figure 6.3-3 System Clock Block Diagram115Figure 6.3-4 SysTick Clock Control Block Diagram116Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK117Figure 6.3-6 Clock Source of Frequency Divider119Figure 6.3-7 Block Diagram of Frequency Divider119Figure 6.4-1 Flash Memory Control Block Diagram134Figure 6.4-2 Flash Memory Organization136Figure 6.4-3 Data Flash Shared with APROM137Figure 6.4-5 Boot Select (BS) for Power-on Action144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 6.2-8 NuMicro® Mini57 Flash, Security and Configuration Map5Figure 6.2-9 SRAM Block Diagram5Figure 6.3-1 Clock Generator Block Diagram11Figure 6.3-2 Clock Generator Global View Diagram11Figure 6.3-3 System Clock Block Diagram11Figure 6.3-4 SysTick Clock Control Block Diagram11Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK11Figure 6.3-6 Clock Source of Frequency Divider11Figure 6.3-7 Block Diagram of Frequency Divider11Figure 6.4-1 Flash Memory Control Block Diagram13Figure 6.4-2 Flash Memory Organization13Figure 6.4-3 Data Flash Shared with APROM13Figure 6.4-4 SPROM Security Mode13Figure 6.4-5 Boot Select (BS) for Power-on Action14Figure 6.4-6 Flash Memory Mapping of CBS in CONFIG014Figure 6.4-7 Executable Range of Code with IAP Function Enabled14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 6.2-6 Power Mode State Machine                                               | 48  |

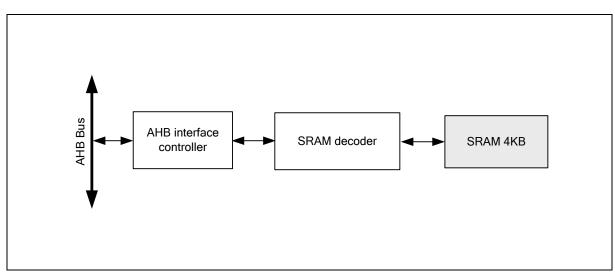

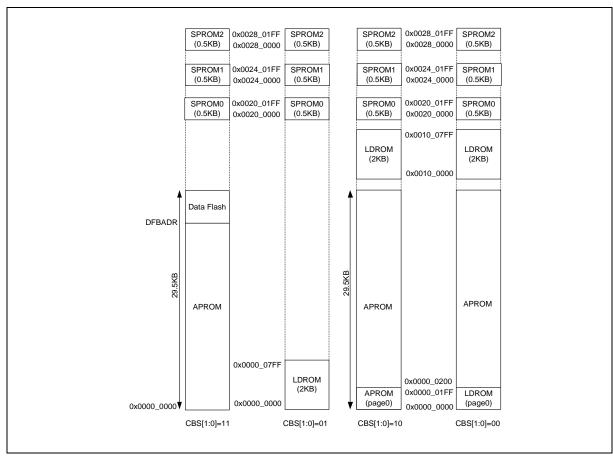

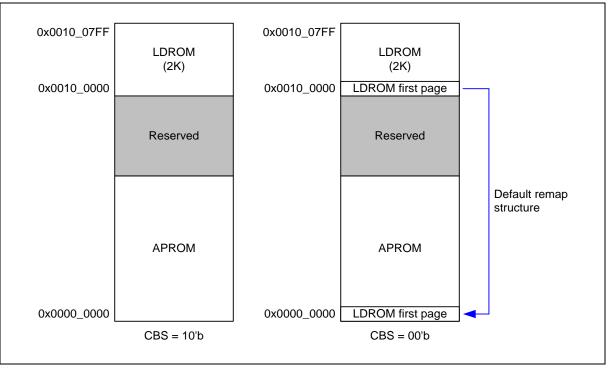

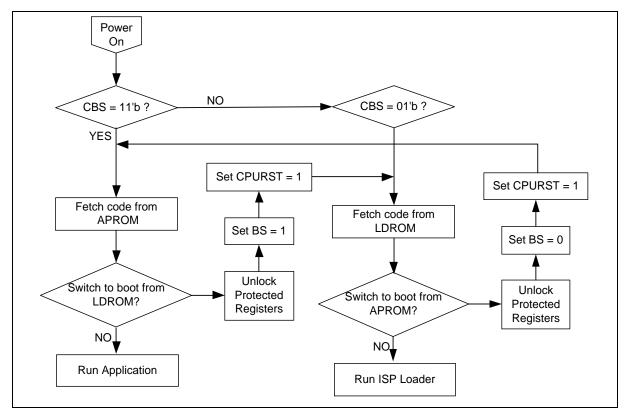

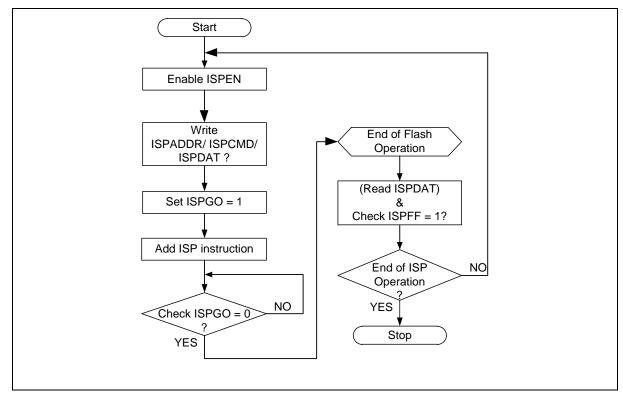

| Figure 6.2-9 SRAM Block Diagram57Figure 6.3-1 Clock Generator Block Diagram113Figure 6.3-2 Clock Generator Global View Diagram114Figure 6.3-3 System Clock Block Diagram115Figure 6.3-4 SysTick Clock Control Block Diagram116Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK117Figure 6.3-6 Clock Source of Frequency Divider119Figure 6.3-7 Block Diagram of Frequency Divider119Figure 6.4-1 Flash Memory Control Block Diagram134Figure 6.4-2 Flash Memory Organization136Figure 6.4-3 Data Flash Shared with APROM137Figure 6.4-4 SPROM Security Mode139Figure 6.4-5 Boot Select (BS) for Power-on Action144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 6.2-9 SRAM Block Diagram5Figure 6.3-1 Clock Generator Block Diagram11Figure 6.3-2 Clock Generator Global View Diagram11Figure 6.3-3 System Clock Block Diagram11Figure 6.3-4 SysTick Clock Control Block Diagram11Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK11Figure 6.3-6 Clock Source of Frequency Divider11Figure 6.3-7 Block Diagram of Frequency Divider11Figure 6.4-1 Flash Memory Control Block Diagram13Figure 6.4-2 Flash Memory Organization13Figure 6.4-3 Data Flash Shared with APROM13Figure 6.4-5 Boot Select (BS) for Power-on Action14Figure 6.4-6 Flash Memory Mapping of CBS in CONFIGO14Figure 6.4-7 Executable Range of Code with IAP Function Enabled14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 6.2-7 NuMicro <sup>®</sup> Mini57 Series Power Architecture Diagram          | 51  |

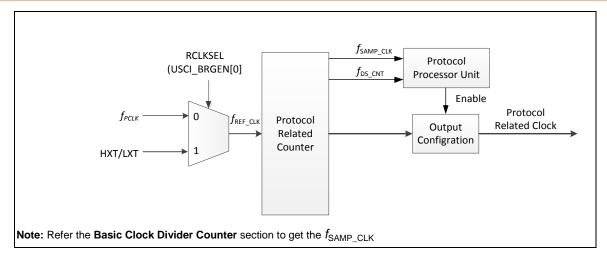

| Figure 6.3-1 Clock Generator Block Diagram113Figure 6.3-2 Clock Generator Global View Diagram114Figure 6.3-3 System Clock Block Diagram115Figure 6.3-4 SysTick Clock Control Block Diagram116Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK117Figure 6.3-6 Clock Source of Frequency Divider119Figure 6.3-7 Block Diagram of Frequency Divider119Figure 6.4-1 Flash Memory Control Block Diagram134Figure 6.4-2 Flash Memory Organization136Figure 6.4-3 Data Flash Shared with APROM137Figure 6.4-4 SPROM Security Mode139Figure 6.4-5 Boot Select (BS) for Power-on Action144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 6.3-1 Clock Generator Block Diagram11Figure 6.3-2 Clock Generator Global View Diagram11Figure 6.3-3 System Clock Block Diagram11Figure 6.3-4 SysTick Clock Control Block Diagram11Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK11Figure 6.3-6 Clock Source of Frequency Divider11Figure 6.3-7 Block Diagram of Frequency Divider11Figure 6.4-1 Flash Memory Control Block Diagram13Figure 6.4-2 Flash Memory Organization13Figure 6.4-3 Data Flash Shared with APROM13Figure 6.4-5 Boot Select (BS) for Power-on Action14Figure 6.4-6 Flash Memory Mapping of CBS in CONFIGO14Figure 6.4-7 Executable Range of Code with IAP Function Enabled14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 6.2-8 NuMicro <sup>®</sup> Mini57 Flash, Security and Configuration Map      | 55  |

| Figure 6.3-2 Clock Generator Global View Diagram114Figure 6.3-3 System Clock Block Diagram115Figure 6.3-4 SysTick Clock Control Block Diagram116Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK117Figure 6.3-6 Clock Source of Frequency Divider119Figure 6.3-7 Block Diagram of Frequency Divider119Figure 6.4-1 Flash Memory Control Block Diagram134Figure 6.4-2 Flash Memory Organization136Figure 6.4-3 Data Flash Shared with APROM137Figure 6.4-4 SPROM Security Mode139Figure 6.4-5 Boot Select (BS) for Power-on Action144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 6.3-2 Clock Generator Global View Diagram.11Figure 6.3-3 System Clock Block Diagram11Figure 6.3-4 SysTick Clock Control Block Diagram11Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK11Figure 6.3-6 Clock Source of Frequency Divider11Figure 6.3-7 Block Diagram of Frequency Divider11Figure 6.4-1 Flash Memory Control Block Diagram13Figure 6.4-2 Flash Memory Organization13Figure 6.4-3 Data Flash Shared with APROM13Figure 6.4-4 SPROM Security Mode13Figure 6.4-5 Boot Select (BS) for Power-on Action14Figure 6.4-6 Flash Memory Mapping of CBS in CONFIGO14Figure 6.4-7 Executable Range of Code with IAP Function Enabled14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 6.2-9 SRAM Block Diagram                                                     | 57  |

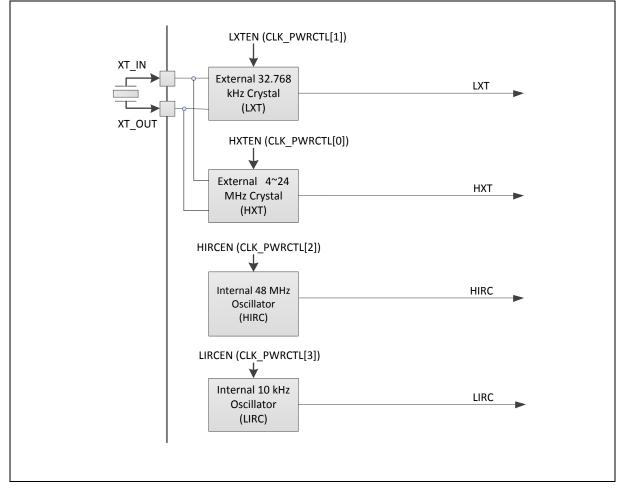

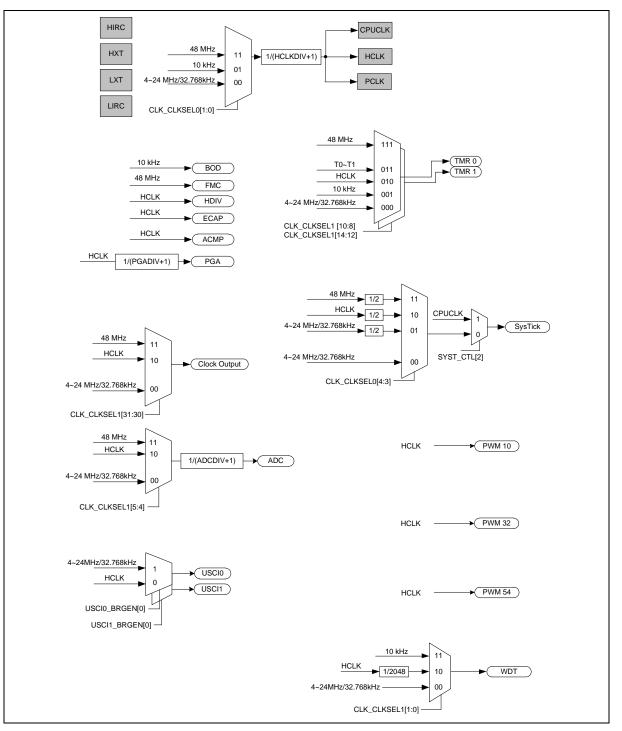

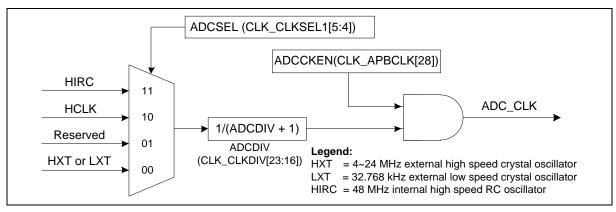

| Figure 6.3-3 System Clock Block Diagram115Figure 6.3-4 SysTick Clock Control Block Diagram116Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK117Figure 6.3-6 Clock Source of Frequency Divider119Figure 6.3-7 Block Diagram of Frequency Divider119Figure 6.4-1 Flash Memory Control Block Diagram134Figure 6.4-2 Flash Memory Organization136Figure 6.4-3 Data Flash Shared with APROM137Figure 6.4-4 SPROM Security Mode139Figure 6.4-5 Boot Select (BS) for Power-on Action144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 6.3-3 System Clock Block Diagram11Figure 6.3-4 SysTick Clock Control Block Diagram11Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK11Figure 6.3-6 Clock Source of Frequency Divider11Figure 6.3-7 Block Diagram of Frequency Divider11Figure 6.4-1 Flash Memory Control Block Diagram13Figure 6.4-2 Flash Memory Organization13Figure 6.4-3 Data Flash Shared with APROM13Figure 6.4-4 SPROM Security Mode13Figure 6.4-5 Boot Select (BS) for Power-on Action14Figure 6.4-6 Flash Memory Mapping of CBS in CONFIGO14Figure 6.4-7 Executable Range of Code with IAP Function Enabled14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 6.3-1 Clock Generator Block Diagram                                          | 113 |

| Figure 6.3-4 SysTick Clock Control Block Diagram116Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK117Figure 6.3-6 Clock Source of Frequency Divider119Figure 6.3-7 Block Diagram of Frequency Divider119Figure 6.4-1 Flash Memory Control Block Diagram134Figure 6.4-2 Flash Memory Organization136Figure 6.4-3 Data Flash Shared with APROM137Figure 6.4-4 SPROM Security Mode139Figure 6.4-5 Boot Select (BS) for Power-on Action144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 6.3-4 SysTick Clock Control Block Diagram11Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK11Figure 6.3-6 Clock Source of Frequency Divider11Figure 6.3-7 Block Diagram of Frequency Divider11Figure 6.4-1 Flash Memory Control Block Diagram13Figure 6.4-2 Flash Memory Organization13Figure 6.4-3 Data Flash Shared with APROM13Figure 6.4-4 SPROM Security Mode13Figure 6.4-5 Boot Select (BS) for Power-on Action14Figure 6.4-6 Flash Memory Mapping of CBS in CONFIGO14Figure 6.4-7 Executable Range of Code with IAP Function Enabled14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 6.3-2 Clock Generator Global View Diagram                                    | 114 |