# L9907

### Automotive FET driver for 3 phase BLDC motor

### Features

- AEC-Q100 qualified

- Supply voltage from 4.2V to 54 V for working in single (12 V systems), double (24 V systems) and 48 V battery applications

- The device can withstand -7 V to 90 V at the FET high-side Driver pins

- Low standby current consumption

- 3.3 V internal regulator supplied by Vcc pin

- Boost regulator for full Rdson down to 6 V and over voltage protection

- 3 low-side + 3 high-side drivers

- PWM operation up to 20 kHz

- Gate driver current adjustable via SPI in 4 steps. Range set via external resistor.

Maximum gate controlled current 600 mA

- Source connection to each MOSFET

- Input pin for each gate driver

- 2-differential current sense amplifiers:

- Output offset selectable via SPI (0.2\*V<sub>cc</sub> offset for ground shunt resistors connection, 0.5\*V<sub>cc</sub> offset for phase shunt resistors connection)

- All the amplifier gain factors are programmable (10, 30, 50, 100)

#### 8 MHz, 16-bit SPI

• Full diagnostic

#### Datasheet - production data

- Programmable parameters:

- Cross conduction dead time with a fixed minimum value

- 4 current steps driving the PowerMOS gates (25%, 50%, 75%, 100%)

- Phase or ground selection of current sense amplifier

- Gain values for the current sense amplifiers

- Zero current output voltage (offset) for the current sense amplifiers

- Over voltage threshold selection for single or double battery operation

- Short circuit detection thresholds for the low-side and the high-side MOSFETs (drain to source voltage monitor).

#### **Protection and diagnostic**

- FET driver:

- FET driver supply Undervoltage (UV) diagnostic;

- Gate to source output voltage limit;

- Gate to source passive switch off.

- Power supply pins V<sub>B</sub> and V<sub>CC</sub>:

- Overvoltage (OV), Undervoltage (UV) diagnostic and protection

- All logic pins withstand 35 V

- Power MOSFET drain to source voltage drop measurement for overcurrent protection

- Over-temperature diagnostic and shutdown

- Fault status flag output

#### Table 1. Device summary

| Order code | Package        | Packing     |

|------------|----------------|-------------|

| L9907      | TQFP64         | Tray        |

| L9907TR    | (10x10x1.0 mm) | Tape & reel |

This is information on a product in full production.

# Contents

| 1 | Des  | cription               |                                                                           | 6  |  |  |

|---|------|------------------------|---------------------------------------------------------------------------|----|--|--|

| 2 | Bloc | k diagra               | am and pin description                                                    | 7  |  |  |

|   | 2.1  | Block                  | diagram                                                                   | 7  |  |  |

|   | 2.2  | Pin de                 | scription                                                                 | 8  |  |  |

| 3 | Fun  | Functional description |                                                                           |    |  |  |

|   | 3.1  | Power                  | supply VB, VCC                                                            | 11 |  |  |

|   | 3.2  | Voltage                | e regulator VDD                                                           | 11 |  |  |

|   | 3.3  | EN1 a                  | nd EN2 pins (ENABLE)                                                      | 11 |  |  |

|   | 3.4  | Boost                  | converter                                                                 | 12 |  |  |

|   |      | 3.4.1                  | BstDis (boost disable) function                                           | 13 |  |  |

|   | 3.5  | MOSF                   | ET drivers                                                                | 14 |  |  |

|   |      | 3.5.1                  | GCR pin                                                                   | 14 |  |  |

|   |      | 3.5.2                  | Shoot through protection                                                  | 14 |  |  |

|   |      | 3.5.3                  | Drain source monitoring                                                   | 15 |  |  |

|   | 3.6  | Curren                 | nt sense amplifier (CSA)                                                  | 15 |  |  |

|   | 3.7  | Genera                 | al SPI usage                                                              | 15 |  |  |

|   | 3.8  | Device                 | e and FET fault handling                                                  | 15 |  |  |

|   |      | 3.8.1                  | SPI and PWM faults                                                        | 16 |  |  |

| 4 | Elec | trical sp              | pecifications                                                             | 17 |  |  |

|   | 4.1  | Maxim                  | num operating ranges                                                      | 17 |  |  |

|   | 4.2  | Absolu                 | ute maximum ratings                                                       | 17 |  |  |

|   | 4.3  | ESD p                  | protection                                                                | 18 |  |  |

|   | 4.4  | Tempe                  | erature ranges and thermal data                                           | 19 |  |  |

|   | 4.5  | Electri                | cal characteristics                                                       | 19 |  |  |

|   |      | 4.5.1                  | Supply                                                                    |    |  |  |

|   |      | 4.5.2                  | Voltage regulator VDD                                                     | 20 |  |  |

|   |      | 4.5.3                  | Logic input pins (PWM_H1 to 3, PWM_L1 to 3, SCK, CS, SDI, BS EN1 and EN2) |    |  |  |

|   |      | 4.5.4                  | Logic output pins (FS_FLAG, SDO, TO3)                                     | 21 |  |  |

|   |      | 4.5.5                  | Boost converter                                                           | 21 |  |  |

|   |      |                        |                                                                           |    |  |  |

|   |      | 4.5.6    | MOSFET drivers                                          | 22 |

|---|------|----------|---------------------------------------------------------|----|

|   |      | 4.5.7    | Current sense amplifier                                 | 24 |

| 5 | SPI  | operatio | on                                                      | 28 |

|   | 5.1  | SPI bit  | s mapping                                               | 29 |

|   |      | 5.1.1    | SDO                                                     | 36 |

| 6 | Appl | lication | circuit                                                 | 40 |

| 7 | Pack | age inf  | ormation                                                | 41 |

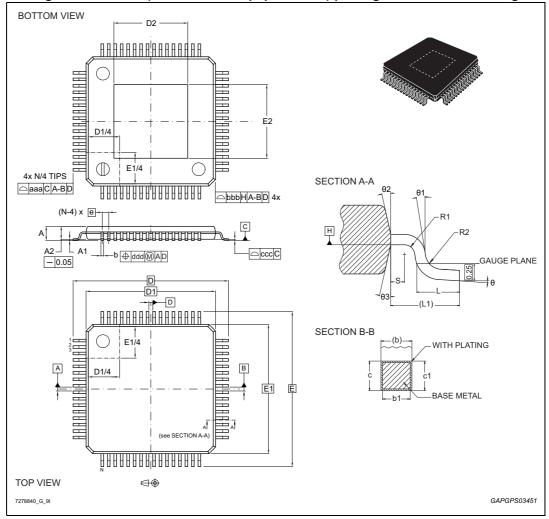

|   | 7.1  | TQFP6    | 64 (10x10x1 mm exp. pad down) package mechanical data . | 41 |

|   |      | 7.1.1    | TQFP64 exposed pad dimensions for L9907                 | 43 |

| 8 | Revi | sion his | story                                                   | 44 |

# List of tables

| Table 1.  | Device summary                                                     |

|-----------|--------------------------------------------------------------------|

| Table 2.  | Pin function                                                       |

| Table 3.  | Device and FET fault handling                                      |

| Table 4.  | SPI and PWM faults                                                 |

| Table 5.  | Maximum operating conditions                                       |

| Table 6.  | Absolute maximum ratings                                           |

| Table 7.  | ESD protection                                                     |

| Table 8.  | Temperature ranges and thermal data                                |

| Table 9.  | Supply electrical characteristics                                  |

| Table 10. | Voltage regulator VDD                                              |

| Table 11. | Logic I/O pins electrical characteristics                          |

| Table 12. | Logic output pins (FS_FLAG, SDO, TO3) electrical characteristics   |

| Table 13. | Boost converter electrical characteristics                         |

| Table 14. | MOSFET drivers electrical characteristics                          |

| Table 15. | PowerMOS overcurrent drop voltage sense                            |

| Table 16. | Gate voltage monitoring                                            |

| Table 17. | Phase current sense amplifier (SPI select: Offx=1, where x=1,2)    |

| Table 18. | Ground current sense amplifier                                     |

| Table 19. | SPI timing specifications                                          |

| Table 20. | SDI bit map definition                                             |

| Table 21. | SDI frame structure                                                |

| Table 22. | Dead time parameter                                                |

| Table 23. | Turn on/off current                                                |

| Table 24. | Current sense amplifier 2 gain                                     |

| Table 25. | Current sense amplifier 1 gain                                     |

| Table 26. | Short circuit detection threshold for low-side PowerMOS            |

| Table 27. | Short circuit detection threshold for low-side PowerMOS            |

| Table 28. | VB over voltage threshold for single or double battery application |

| Table 29. | CMD1 SDI SPI bits vs. enabled fault                                |

| Table 30. | VCC over voltage threshold                                         |

| Table 31. | Current sense amplifier input offset calibration                   |

| Table 32. | CMD4 SDI SPI bits vs. enabled fault                                |

| Table 33. | SDO bit map definition                                             |

| Table 34. | TQFP64 (10x10x1 mm exp. pad down) package mechanical data          |

| Table 35. | TQFP64 exposed pad dimensions for L9907                            |

| Table 36. | Document revision history                                          |

# List of figures

| Figure 1. | Block diagram                                                | 7  |

|-----------|--------------------------------------------------------------|----|

| Figure 2. | Pin connection diagram                                       | 8  |

| Figure 3. | MOSFET drivers supply structure 1                            | 2  |

| Figure 4. | Case of T_BOOST_OFF < T_BOOST_OFF_MAX 1                      | 3  |

| Figure 5. | Case of T_BOOST_OFF > T_BOOST_OFF_MAX1                       | 3  |

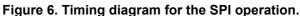

| Figure 6. | Timing diagram for the SPI operation                         | 28 |

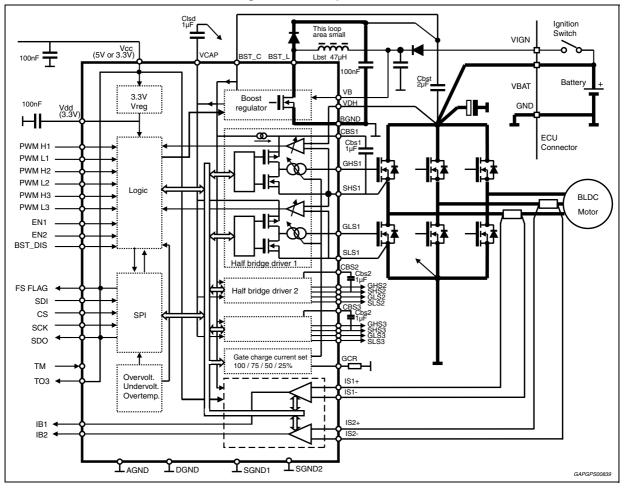

| Figure 7. | Three-phase motor control                                    | 0  |

| Figure 8. | TQFP64 (10x10x1 mm exp. pad down) package mechanical drawing | 1  |

### 1 Description

L9907 is a smart power device realized in STMicroelectronics advanced BCD-6s technology. It is able to drive all PowerMOS transistors for 3-phase BLDC motor applications. The circuit is suitable to operate in environments with high supply voltage such as double battery. Supply related pins are capable of withstanding up to 90 V.

Moreover, the device is able to control the six pre-driver channels independently. In this way it is possible to implement all kinds of electric motor control strategy.

The integrated boost regulator provides sufficient gate charge for all PowerMOS down to a battery voltage of 6 V. All pre-drivers have dedicated connections with the MOSFET sources. The device offers programmability for a base gate output current via an external resistor. Moreover, via SPI, it is possible to select among 4 gate output current levels even while the application is running. All channels are protected against short circuit and the device is protected against overtemperature conditions. Moreover, the boost converter implements an over voltage protection to allow safe functionality of pre-drivers in all battery voltage conditions. During over voltage conditions, BST\_C voltage is limited by temporarily switching off the boost regulator and pre-drivers are allowed to operate. Boost will be self reenabled as soon as the output voltage decreases to an acceptable value.

The device is equipped with 2 current sense amplifiers. Both have SPI selectable amplifier gain (10, 30, 50 and 100) and output offset voltage level in order to allow max flexibility for phase or ground current sense strategy. All I/O pins are 35 V compatible. Full diagnostic is available through SPI. The device is available in TQFP64.

The device is protected against Shoot Through events.

# 2 Block diagram and pin description

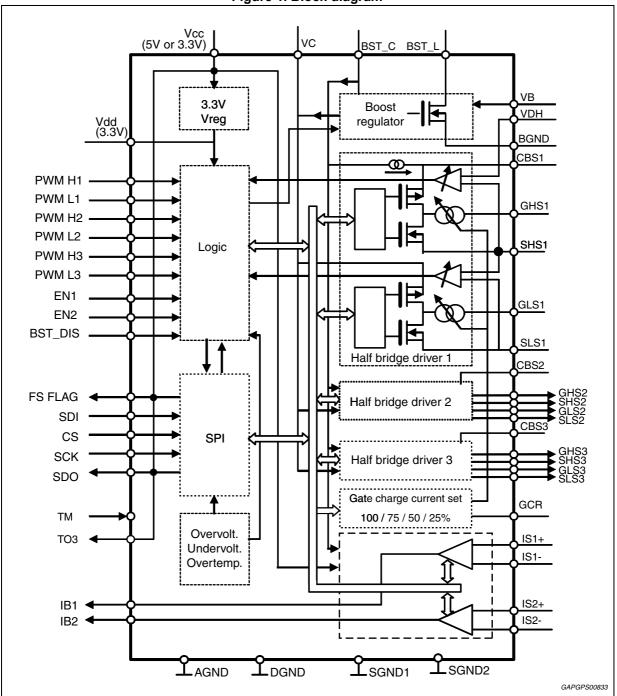

### 2.1 Block diagram

Figure 1. Block diagram

DS11800 Rev 4

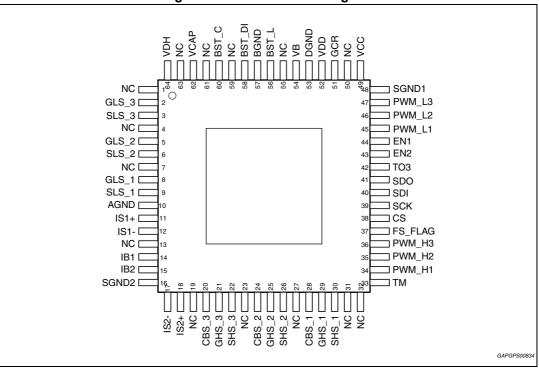

### 2.2 Pin description

#### Figure 2. Pin connection diagram

#### Table 2. Pin function

| Pin # | Pin name | Description                                                        |     |

|-------|----------|--------------------------------------------------------------------|-----|

| 1     | NC       | NC                                                                 | -   |

| 2     | GLS_3    | Gate connection for low-side MOSFET, phase 3                       | 0   |

| 3     | SLS_3    | Source connection for low-side MOSFET, phase 3                     | I   |

| 4     | NC       | NC                                                                 | -   |

| 5     | GLS_2    | Gate connection for low-side MOSFET, phase 2                       | 0   |

| 6     | SLS_2    | Source connection for low-side MOSFET, phase 2                     | I   |

| 7     | NC       | NC                                                                 | -   |

| 8     | GLS_1    | Gate connection for low-side MOSFET, phase 1                       | 0   |

| 9     | SLS_1    | Source connection for low-side MOSFET, phase 1                     | I   |

| 10    | AGND     | Analog ground                                                      | GND |

| 11    | IS1+     | Positive input for current sense amplifier 1                       | I   |

| 12    | IS1-     | Negative input for current sense amplifier 1                       | I   |

| 13    | NC       | NC                                                                 | -   |

| 14    | IB1      | Output for current sense amplifier 1 (Test mode digital output #1) | 0   |

| 15    | IB2      | Output for current sense amplifier 2 (Test mode digital output #2) | 0   |

| 16    | SGND2    | Substrate (and ESD_GND) connection 2                               | GND |

Table 2. Pin function (continued)

| Pin # | Pin name          | Description                                                      |     |

|-------|-------------------|------------------------------------------------------------------|-----|

| 17    | IS2-              | Negative input for current sense amplifier 2                     |     |

| 18    | IS2+              | Positive input for current sense amplifier 2                     | i   |

| 19    | NC                | NC                                                               | -   |

| 20    | CBS_3             | Bootstrap capacitor for high-side MOSFET, phase 3                | I   |

| 21    | GHS_3             | Gate connection for high-side MOSFET, phase 3                    | 0   |

| 22    | SHS_3             | Source connection for high-side MOSFET, phase 3                  | I   |

| 23    | NC                | NC                                                               | -   |

| 24    | CBS_2             | Bootstrap capacitor for high-side MOSFET, phase 2                | I   |

| 25    | GHS_2             | Gate connection for high-side MOSFET, phase 2                    | 0   |

| 26    | SHS_2             | Source connection for high-side MOSFET, phase 2                  | I   |

| 27    | NC                | NC                                                               | -   |

| 28    | CBS_1             | Bootstrap capacitor for high-side MOSFET, phase 1                | I   |

| 29    | GHS_1             | Gate connection for high-side MOSFET, phase 1                    | 0   |

| 30    | SHS_1             | Source connection for high-side MOSFET, phase 1                  | I   |

| 31    | NC                | NC                                                               | -   |

| 32    | NC                | NC                                                               | -   |

| 33    | TM <sup>(1)</sup> | Test mode enable input                                           | I   |

| 34    | PWM_H1            | PWM command input for high-side phase 1                          | I   |

| 35    | PWM_H2            | PWM command input for high-side phase 2                          | I   |

| 36    | PWM_H3            | PWM command input for high-side phase 3                          | I   |

| 37    | FS_FLAG           | Fault status flag output                                         | 0   |

| 38    | CS                | SPI chip select input                                            | I   |

| 39    | SCK               | SPI serial clock input                                           | I   |

| 40    | SDI               | SPI Serial data input                                            | I   |

| 41    | SDO               | SPI serial data output                                           | 0   |

| 42    | TO3               | Test output                                                      | 0   |

| 43    | EN2               | Enable Input 2 (ANDed with EN1 to enable any gate drive output). | I   |

| 44    | EN1               | Enable Input 1 (ANDed with EN2 to enable any gate drive output). | I   |

| 45    | PWM_L1            | PWM command input for low-side phase 1                           | I   |

| 46    | PWM_L2            | PWM command input for low-side phase 2                           | I   |

| 47    | PWM_L3            | PWM command input for low-side phase 3                           | I   |

| 48    | SGND1             | Substrate (and ESD_GND) connection 1                             | GND |

| 49    | Vcc               | 5 V / 3.3 V power supply input                                   | I   |

| 50    | NC                | NC                                                               | -   |

| 51    | GCR               | Connection to resistor for current selection of gate driver      | 0   |

| Pin # | Pin name | Description                                               |     |

|-------|----------|-----------------------------------------------------------|-----|

| 52    | Vdd      | 3.3 V power supply output (for IC internal purpose only)  | 0   |

| 53    | DGND     | Digital ground                                            | GND |

| 54    | VB       | Protected battery monitor                                 | I   |

| 55    | NC       | NC                                                        | -   |

| 56    | BST_L    | Boost regulator inductance connection                     | 0   |

| 57    | BGND     | Boost ground                                              | GND |

| 58    | BST_DIS  | Boost disable                                             | I   |

| 59    | NC       | NC                                                        | -   |

| 60    | BST_C    | Boost regulator capacitance connection                    | I   |

| 61    | NC       | NC                                                        | -   |

| 62    | VCAP     | Decoupling capacitor for power supply of low-side drivers | I   |

| 63    | NC       | NC                                                        | -   |

| 64    | VDH      | High-side drain voltage sense                             | I   |

Table 2. Pin function (continued)

1. TM pin has to be connected to ground in the application.

## 3 Functional description

### 3.1 Power supply VB, VCC

Voltage present at VB and VCC pins is monitored in order to inhibit driver and/or boost functionality in case of under/over voltage detection. A VCC over voltage self test is embedded for safety integrity check: VCC over voltage threshold can be reduced on purpose to a level that is always triggered with nominal values on VCC rail. The device is self protected in case of ground disconnections versus both SGNDx pins. SGND1 and SGND2 pins are internally shorted and connected to substrate: at least one of these pins must be connected to board ground. In case of AGND loss, a dedicated comparator will lead to a POR state for logic, where boost regulator and MOSFET drivers are disabled. This fault doesn't set any SPI error bit. In case of DGND loss the device is automatically disabled: MOSFET drivers go in tri-state condition and external FETs are kept off using integrate passive pull down. In case of BGND ground loss the boost regulator cannot work properly: the effect is an undervoltage on HS and/or LS side gate voltage monitor.

The ground reference for all the voltages and thresholds available in the device is AGND. The Exposed Pad (EP) is mainly used for thermal dissipation. It should be grounded and connected together with SGNDx pins.

### 3.2 Voltage regulator VDD

The internal 3.3 V voltage regulator is used to supply the internal logic and all internal blocks. For stability reasons a 100 nF capacitor has to be connected to VDD pin. This regulator is to be intended for IC internal use only. Suggested limits for external capacitor are min = 100 nF -20% ma x= 220 nF +20%. All tests are performed with a 100 nF capacitor, unless otherwise specified.

### 3.3 EN1 and EN2 pins (ENABLE)

To enable the gate driver functionality EN1 and EN2 have to be pulled high. These pins are by default internally logically ANDed. In case REGOFF\_EN bit in CMD4 SPI frame is set to 1 (refer to SPI mapping, *Table 20*), EN1 and EN2 have different meanings: EN2 stays the same as a gate driver functionality enabler, while EN1 will also become an enabler for all the regulators supplying the pre-driver circuitries. In this way, EN1 becomes a safety control pin that implements an additional switch-off path.

These pins are also used to enable the SPI write to CMD1 and CMD4. These registers contain gate driver sensitive to failure management bits which just can be written when at least one of the ENx pins is pulled low (gate driver disabled).

Nevertheless the pins are used as well to reactivate the gate driver in case of device internal switch off. Therefore a low cycle of at least  $3\mu$ s has to be applied after fault condition is removed to one or both of the ENx pins.

On both pins internal pull down currents are implemented.

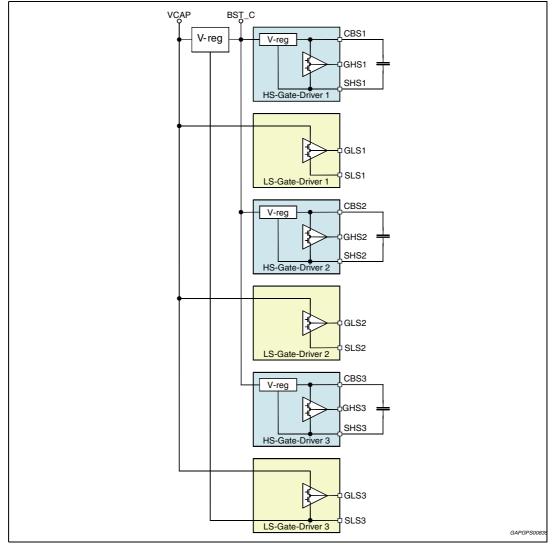

### 3.4 Boost converter

The purpose of the Boost converter is to generate a voltage around 10 V higher than the one present at VDH monitor pin. This voltage is used to supply HS drivers (through dedicated regulators) and LS drivers (through VCAP regulator). The regulated voltage is present at BST\_C pin. BST\_L pin is the drain of an integrated NDMOS switch. VCAP regulator is a current limited voltage regulator, fed by Boost and referred to SLS3 voltage, used to supply LS drivers. Each HS driver has a current limited voltage regulator that is fed by Boost, referred to SHSx pins and with regulated voltage present at CBSx pins. These regulators limit VGS of the external FETs. Overvoltage at BST\_C pin (e.g. due to low current demand) is limited by skipping turn on pulses until over voltage condition is removed. A fixed voltage threshold on BST\_C is implemented, in order to avoid the boost voltage exceeding a safety level in case of high voltage on VDH monitor pin. In case the user would not need this over voltage protection (e.g. for applications where high voltage is present on the VDH rail), L9907 provides a disabling bit in CMD3 SPI command (DIS\_BST<sub>ov</sub>). The Boost converter is disabled in case of validated Fault (see *Table 3*) and reactivated by fault removal and cleared after SPI reading.

Figure 3. MOSFET drivers supply structure

In case Boost converter is disabled, but voltage at BST\_C pin is present, Current Sense Amplifiers are active but with degraded performances at least in common mode dynamic range. In order to improve EMC behaviour an external RC series snubber can be added between BST\_L and BGND pins. RC~1/(6.28\*fSW\_BST).

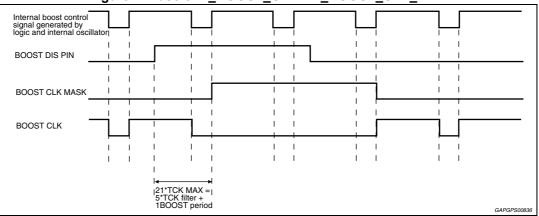

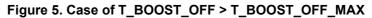

#### 3.4.1 BstDis (boost disable) function

In case noise-free CSA measuring is needed, a special functionality that temporarily disables Boost regulator is implemented, with the purpose to reduce PCB coupling between CSA output and boost PCB metal stripes that can act as antennas. Once BST\_DIS pin is asserted, boost regulator is disabled starting from the next complete boost cycle (maximum delay T\_BOOST\_OFF\_FILT).

Boost is re-enabled in two ways:

- internal timer expired (T\_BOOST\_OFF\_MAX time is reached)

- BstDis pin deasserted

In both cases boost starts working again from the beginning of the next complete boost cycle.

$T_BOOST_OFF_MAX = 6^{T}_{BOOS}T = 96^{T}_{CK}$

T\_BOOST\_OFF\_FILT = 3\*T<sub>CK</sub> min, 21\*T<sub>CK</sub> max

#### Figure 4. Case of T\_BOOST\_OFF < T\_BOOST\_OFF\_MAX

When BST\_DIS\_EN bit of CMD2 SPI frame is set to 1 (refer to SPI mapping, *Table 20*), BST\_DIS becomes a full-time control of the boost operation: the boost will be disabled as long as the BST\_DIS pin is high. This implements a boost permanent disabler that can be used for different reasons, e.g. to allow more precise and less noisy measurements, to decrease power dissipation or current load on battery in all conditions when the boost is not strictly necessary.

### 3.5 MOSFET drivers

MOSFET drivers are programmable current mirrors used to limit gate charge/discharge current without gate series resistors (which can be used anyway). Programmability has got two degrees of freedom: SPI programmability (25, 50, 75, 100% of max. available current IG) for MOSFET gate current adjustment during running application and via external resistor at GCR pin to adjust the gate current among different applications. External MOSFETs are protected against over current in on-state monitoring their Vds voltage. Maximum Vgs of external MOSFETs is limited using VCAP regulator for LS drivers and dedicated floating regulators referred to sources for HS drivers.

#### 3.5.1 GCR pin

At GCR pin a resistor has to be connected which defines in combination with the IGx SPI bits the gate current for charge and discharge.

Minimum value for GCR resistor is GCR(min) = 1 k $\Omega$  - 10% (maximum allowable gate current), maximum is GCR(max) = 22 k $\Omega$  +10% (minimum allowable gate current), but with degraded precision performances with GCR > 6 k $\Omega$  + 10%. Tested values are GCR = 1 k $\Omega$  and GCR = 6 k $\Omega$

GCR pin circuitry implements a open/short protection in case of a too high/low resistive load connected to it. If one of the above conditions occurs, the device switches to an internally generated current, equivalent to approximately 15 k $\Omega$ . The current reference can be switched to the internal reference by using the GCR\_INT\_I bit of CMD2 frame (refer to SPI mapping, *Table 20*); this can be used when a reduced power dissipation is needed.

#### 3.5.2 Shoot through protection

Shoot through protection's aim is to avoid destructive cross current conduction between high-side and low-side FETs of same phase in case of unwanted condition when PWM Hx and PWM Lx signals are set to logic '1' at the same time (e.g. because of a controller fault). With every activation of either PWM Hx or PWM Lx the cross current protection time is activated and switches off the corresponding half bridge for the programmed Dead time. The shoot through condition is validated via an up-down counter which is proportional to the programmed dead time. With this feature, continuous activation of HS and LS and also high frequency oscillations of the PWMx input signals (HS and LS) are detected and the shoot through failure state is set. If the fault condition is validated, all external FETs are switched OFF and FS FLAG is asserted low. No SPI SDO diagnostic bit is set, since hypothesis is that the controller is not able to work properly. In case the SHT PH bit of CMD2 SPI frame would be set to 1 (refer to SPI mapping, Table 20), the device allows the switching off of the only phase for which the shoot through occurred. The phase that experienced the fault is reported on DIAG2 SPI frame (SDO bits B<2:0>). In order to re-enable FET pre-drivers, at least one Enable signals EN1 or EN2 must be toggled. In order to unlatch also FS FLAG status a SPI communication with diagnostic frame must be performed.

#### 3.5.3 Drain source monitoring

To monitor the external MOSFET a Drain Source monitoring for all HS and LS is implemented. In case the drain source voltage exceeds a certain threshold (e.g. MOSFET short) during gate ON mode, all drivers will be disabled and the fail will be reported via FS\_FLAG and SPI. In case the ShortPH bit of CMD2 SPI frame would be set to 1 (refer to SPI mapping, *Table 20*), the device allows the switching off of the only phase for which the drain-source short occurred.

### 3.6 Current sense amplifier (CSA)

Current Sense Amplifier converts and amplifies (with a 4-step programmable gain) current information through external shunt in a voltage signal. Each CSA can be configured for one side ("Ground") or both sides ("Phase") current flow through the shunt. Indeed the shunt can be referred to ground or floating. Current Sense Amplifier is active if IC is active (VCC and VDD present and within spec range), despite of EN status. In case Boost converter is disabled, but voltage at BST\_C pin is present, Current Sense Amplifiers work but with degraded performances at least in common mode dynamic range.

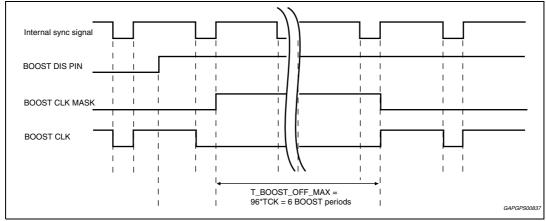

### 3.7 General SPI usage

For device programmability a four-wire SPI is used. The device acts as SPI slave. Data will be latched on the negative clock edge and shifted out on the positive edge ( $\mu$ C setting: CPHA =1; CPOL = 0).

To perform an SPI write the WE bit has to be set and a correct ODD parity bit has to be written.

A data read out is always performed on the following SPI frame (after power-up CMD0 is read). That means sending data to a certain register will lead to shift out the content of the addressed register in the following SPI frame. In case of wrong SPI communication (e.g. due to stuck at 0 or at 1 of SDI) the current command is rejected and an error message (0xB001) is presented as SDO response at the following SPI cycle.

### 3.8 Device and FET fault handling

All internal fault events are filtered to achieve noise immunity. After filter-time they are latched in the corresponding SPI register and the FS\_FLAG (active low) becomes low. In case the related driver-disable-bit (EN\_x) is set, additionally the gate driver will be disabled and actively discharged (see: Fault Effect enabling; *Table 32* and *29*). In case EN\_x is disabled the  $\mu$ C takes fully response to react on any errors immediately indicated by the FS\_FLAG. Neither the boost nor the FET drivers will be disabled on deselected faults.

| Fault                           | Diagnosis                                                          | Device action when<br>EN_x enabled             | Exit from fault condition                                                                                                                                                                         |

|---------------------------------|--------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overtemperature                 | FS_FLAG = low;<br>THSD SPI bit set                                 | FET driver functionality disabled              | <ul> <li>Remove fault =&gt; auto recovery</li> <li>SPI read clears the Fault Flags and<br/>sets FS_FLAG to high</li> </ul>                                                                        |

| VB or VCC over- or undervoltage | FS_FLAG = low;<br>VBOV or VBUV or<br>VCCOV or VCCUV SPI<br>bit set | FET driver functionality<br>and Boost disabled | <ul> <li>Remove fault =&gt; auto recovery of<br/>Boost</li> <li>EN cycling toggle reactivates the FET<br/>driver</li> <li>SPI read clears the Fault Flags and<br/>sets FS_FLAG to high</li> </ul> |

| Boost HS or LS<br>undervoltage  | FS_FLAG = low;<br>UV_HS or UV_LS SPI<br>bit set                    | FET driver functionality disabled              | <ul> <li>Remove fault</li> <li>EN cycling toggle reactivates the FET driver</li> <li>SPI read clears the Fault Flags and sets FS_FLAG to high</li> </ul>                                          |

| VSC_HSx<br>overcurrent          | FS_FLAG = low;<br>VSC_HSx SPI bit set                              | FET driver functionality<br>disabled           | <ul> <li>Remove fault</li> <li>EN cycling toggle reactivates the FET driver</li> <li>SPI read clears the Fault Flags and sets FS_FLAG to high</li> </ul>                                          |

| VSC_LSx<br>overcurrent          | FS_FLAG = low;<br>VSC_LSx SPI bit set                              | FET driver functionality<br>disabled           | <ul> <li>Remove fault</li> <li>EN cycling toggle reactivates the FET driver</li> <li>SPI read clears the Fault Flags and sets FS_FLAG to high</li> </ul>                                          |

### 3.8.1 SPI and PWM faults

#### Table 4. SPI and PWM faults

| Fault                                                                    | Diagnosis                                 | Device Action                     | Exit from Fault Condition                                                                                                     |

|--------------------------------------------------------------------------|-------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| SPI Error (wrong<br>address access;<br>parity error; SCK<br>count error) | SPI_Error bit set and 0xB001 return frame | Faulty SPI frame is ignored       | -                                                                                                                             |

| PWM_Hx and<br>PWM_Lx shoot<br>through protection                         | FS_FLAG = low;                            | FET driver functionality disabled | <ul> <li>Remove fault</li> <li>EN cycling toggle reactivates the FET driver</li> <li>SPI read sets FS_FLAG to high</li> </ul> |

# 4 Electrical specifications

### 4.1 Maximum operating ranges

The device may not operate properly if maximum operating condition is exceeded.

| Symbol          | Parameter                                 | Value                                   | Unit |

|-----------------|-------------------------------------------|-----------------------------------------|------|

| V <sub>B</sub>  | Protected battery monitor voltage         | 4.2 to 54 <sup>(1)</sup>                | V    |

| V <sub>CC</sub> | 5 V / 3.3 V power supply                  | 3 to 5.5                                | V    |

| V <sub>DH</sub> | High-side drain voltage sense             | 4.2 to 54 <sup>(1) (2)</sup>            | V    |

| SHS_1 to 3      | High-side source voltage                  | -7 to 54 <sup>(1) (3)</sup>             | V    |

| ISxx            | Current sense amplifier input pin voltage | -2 to V <sub>DH</sub> +4 <sup>(4)</sup> | V    |

Table 5. Maximum operating conditions

1. Maximum operating voltage is 75 V in dynamic conditions.

2. V<sub>DH</sub> maximum operating voltage range is limited by V(BST\_C)-15 V.

3. SHS maximum operating voltage range is limited by V(CBSxmax)-15 V.

4. Maximum operating voltage is  $V_{DH}$  +20 V in dynamic conditions.

### 4.2 Absolute maximum ratings

Maximum ratings are absolute ratings; exceeding any one of these values may cause permanent damage to the integrated circuit.

| Parameter                                | Condition                                                        | Min  | Мах               | Unit |  |

|------------------------------------------|------------------------------------------------------------------|------|-------------------|------|--|

| Monitor oundly pin                       | Pin VB                                                           | -0.3 | 75                | V    |  |

| Monitor supply pin                       |                                                                  | -10  | +10               | mA   |  |

|                                          | PST C                                                            | -0.3 | 90                | V    |  |

|                                          | BST_C                                                            | -100 | 100               | mA   |  |

| Devene evente eine                       |                                                                  | -0.3 | 90                | V    |  |

|                                          | Pin: BST_L                                                       | -100 | 100               | mA   |  |

|                                          |                                                                  | -0.3 | 35                | V    |  |

| Power supply pins                        | Pin Vcc                                                          | -10  | 25                | mA   |  |

|                                          | Pin Vdd                                                          | -0.3 | 4.6               | V    |  |

|                                          |                                                                  | -10  | 15                | mA   |  |

|                                          | Pin VCAP                                                         | -0.3 | 20                | V    |  |

|                                          |                                                                  | -100 | 100               | mA   |  |

|                                          | PWM_H1 to 3, PWM_L1 to 3, IB1,                                   | -0.3 | 35 <sup>(1)</sup> | V    |  |

| Miscellaneous Analog/Digital I/O<br>pins | IB2, EN1, EN2, FS_FLAG,<br>BST_DIS,TM, CS, SCK, SDI,<br>SDO, TO3 | -10  | 10                | mA   |  |

| Table 6. Absolute m | naximum ratings |

|---------------------|-----------------|

|---------------------|-----------------|

|                                                                                                       |                                                                                   | ,    |     |      |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|-----|------|

| Parameter                                                                                             | Condition                                                                         | Min  | Мах | Unit |

| Gate current selection pin                                                                            | Pin GCR                                                                           | -0.3 | 4.6 | V    |

| Gate current selection pin                                                                            | FINGER                                                                            | -10  | +10 | mA   |

| Current sense amplifier pins                                                                          | IS1+,IS1-,IS2+,IS2-                                                               | -7   | 75  | V    |

| Current sense ampliner pins                                                                           | 1317,131-,1327,132-                                                               | -10  | 10  | mA   |

| Differential voltage between ISx +/-                                                                  | Abs  ISx+ - ISx-                                                                  | -    | 15  | V    |

| High side drain conce                                                                                 | Pin VDH                                                                           | -4   | 75  | V    |

| High-side drain sense                                                                                 |                                                                                   | -10  | 10  | mA   |

|                                                                                                       | HS Bootstrap Cap pins: CBS_1 to 3                                                 | -0.3 | 90  | V    |

| FET-driver pins                                                                                       | Differential gate to source HS pins:<br>V(GHS_x) - V(SHS_x), $x = 1$ to $3^{(2)}$ | -0.3 | 20  | V    |

|                                                                                                       | Source HS pins: SHS_1 to 3                                                        | -7   | 75  | V    |

|                                                                                                       | Source LS pins: SLS_1 to 3                                                        | -7   | 10  | V    |

| FET driver pinsDifferential gate to source LS pins:<br>V(GLS_x) - V(SLS_x), x = 1 to 3 <sup>(2)</sup> |                                                                                   | -0.3 | 20  | V    |

| Current sense amplifier differential<br>voltage BST_C-ISxx                                            |                                                                                   | -0.3 | 90  | V    |

|                                                                                                       | Pins BGND and DGND                                                                | -0.3 | 4.6 | V    |

| GND pins                                                                                              | Pin AGND and EP                                                                   | -0.3 | 0.3 | V    |

Table 6. Absolute maximum ratings (continued)

In standard battery level application (12 V systems) the I/O pins and Vcc pin can stand a short to battery up to 35 V. A short to 35 V battery on any I/O pin also forces the Vcc to approximately 35 V. Care must be taken in order to avoid that under such conditions the Vcc pin is strongly pulled down to 5 V (or 3.3 V) with a current exceeding the absolute maximum ratings level.

2. Negative AMR is -0.3 V or -20 mA.

### 4.3 ESD protection

| Parameter                | Condition           | Min  | Мах | Unit |

|--------------------------|---------------------|------|-----|------|

| Logic and power pins     | Human body model    | -2   | 2   | kV   |

| FET driver pins          | Human body model    | -2   | 2   | kV   |

| All pins but corner pins | Charge device model | -250 | 250 | V    |

| Corner pins              | Charge device model | -750 | 750 | V    |

#### Table 7. ESD protection

HBM according to MIL 883C, Method 3015.7 or EIA/JESD22-A114\_A. HBM with all unzapped pins grounded.

### 4.4 Temperature ranges and thermal data

Table 8. Temperature ranges and thermal data

| Symbol                                                                      | Symbol Parameter                                           |     | Max | Unit |

|-----------------------------------------------------------------------------|------------------------------------------------------------|-----|-----|------|

| т                                                                           | Operating junction temperature                             | -40 | 150 | °C   |

| lj                                                                          | 100 hours over lifetime temperature <sup>(1)</sup>         | -   | 175 | °C   |

| T <sub>stg</sub>                                                            | T <sub>stg</sub> Storage temperature                       |     | 150 | °C   |

| T <sub>ot</sub>                                                             | T <sub>ot</sub> Thermal shutdown temperature               |     | 205 | °C   |

| T <sub>hys</sub>                                                            | Thermal shutdown temperature hysteresis <sup>(2)</sup>     |     | -   | °C   |

| R <sub>th j-amb</sub> Thermal resistance junction-to-ambient <sup>(3)</sup> |                                                            | -   | 23  | °C/W |

| R <sub>th j-case</sub>                                                      | R <sub>th j-case</sub> Thermal resistance junction-to-case |     |     | °C/W |

1. Functionality is guaranteed, the specified limits may be exceeded.

- 2. Guaranteed by design.

- 3. IC soldered on 2s2p PCB thermally enhanced.

### 4.5 Electrical characteristics

All voltages referred to ground (SGNDx ground) and currents are assumed to be positive when current flows into the pin.

#### 4.5.1 Supply

The device is operated in the specified operating range, unless otherwise specified (V<sub>CC</sub> = 3.20 V to 5.25 V, VB = 4.2 V to 54 V, T<sub>i</sub> = -40 °C to 150 °C).

| Symbol               | Parameter                                                     | Test condition                                        | Min  | Тур | Max  | Unit |

|----------------------|---------------------------------------------------------------|-------------------------------------------------------|------|-----|------|------|

| V <sub>B</sub>       | Operating supply voltage range                                | -                                                     | 4.2  | -   | 54   | V    |

| VB OV_1              | Overvoltage threshold for double battery applications (L9907) | VB <sub>OV2</sub> ,VB <sub>OV1</sub> = 01             | 36   | -   | 42   | V    |

| VB OV_2              | Overvoltage threshold for single battery application          | VB <sub>OV2</sub> ,VB <sub>OV1</sub> = 10             | 27.5 | 31  | 34.5 | V    |

| Td VB                | Overvoltage time delay for noise rejection                    | (guaranteed through scan)                             | 30   | -   | 80   | μs   |

| VB UV                | Undervoltage disable threshold                                | -                                                     | 4.2  | 4.6 | 5    | V    |

| Td <sub>UV</sub>     | Undervoltage time delay for noise rejection                   | (guaranteed through scan)                             | 30   | -   | 80   | μs   |

| I <sub>VB(dis)</sub> | Supply current                                                | VB= 13V, V <sub>cc</sub> < 0.5 V, room<br>temperature | -    | 1   | 10   | μA   |

| Symbol             | Parameter                                                   | Test condition                                                 | Min  | Тур  | Мах  | Unit |

|--------------------|-------------------------------------------------------------|----------------------------------------------------------------|------|------|------|------|

| Cynibol            |                                                             |                                                                |      | קעי  | max  | onic |

| $I_{VB}$           | VB supply current <sup>(1) (2)</sup>                        | VB= 13V, Vcc= 3.3V, open<br>outputs, fPWM =0                   | -    | -    | 10   | mA   |

| I <sub>BST_C</sub> |                                                             | VB = 13 V, drivers off, boost off                              | -    | -    | 10   | mA   |

| V <sub>CC</sub>    | Operating supply voltage range                              | -                                                              | 3.20 | -    | 5.25 | V    |

| lcc                | Vee DC cupply current                                       | VB= 13 V, Vcc = 3.3 V                                          | -    | -    | 20   | mA   |

| ICC                | Vcc DC supply current                                       | VB= 13 V, Vcc = 5 V                                            | -    | -    | 25   | mA   |

| Vcc UV             | Vcc undervoltage monitor                                    | -                                                              | 2.9  | 3.05 | 3.2  | V    |

| VCC OV<br>3.3V     | Vcc overvoltage monitor for 3.3V supply system              | VCC <sub>OV2</sub> ,VCC <sub>OV1</sub> =10,<br>Default on 3.3V | 3.4  | 3.55 | 3.7  | V    |

| VCC OV<br>5V       | Vcc overvoltage monitor for 5V supply system                | VCC <sub>OV2</sub> ,VCC <sub>OV1</sub> =01                     | 5.45 | 5.75 | 6.0  | V    |

| VCC OV<br>test     | Vcc overvoltage monitor for safety integrity check          | VOV <sub>TST</sub> = 1 (CMD2, B6)                              | 2.6  | 2.8  | 3.0  | V    |

| Td Vcc             | Overvoltage and undervoltage time delay for noise rejection | (guaranteed through scan)                                      | 30   | -    | 80   | μs   |

| Vdd uv             | VDD undervoltage monitor and reset                          | -                                                              | 2.5  | 2.7  | 2.8  | V    |

| AGNDloss           | AGND loss threshold                                         | Ramp AGND starting from 0 V                                    | 150  | 220  | 290  | mV   |

Table 9. Supply electrical characteristics (continued)

The following is the estimated V<sub>B</sub> supply current (I<sub>VB</sub>) given power supply voltage level (V<sub>B</sub>), PWM frequency (f<sub>PWM</sub>) and gate charge (Q) for each MOSFET (It represents the current that flows through external inductor to recharge Clsd and highside Cbs capacitors):

$$I_{VB} = 7.2 \text{ Q } f_{PWM} \left(1 + \frac{V_{boost} - V_B}{V_B}\right) + 6 \frac{2.81}{GCR} \left(1.5 + \frac{V_{boost}}{0.85 V_B}\right) + I_{BST_C}$$

The following is the estimated VB Power Dissipation (P<sub>diss</sub>, it cannot be calculated as VB times IVB) given power supply voltage level (VB), PWM frequency (f<sub>PWM</sub>) and gate charge (Q) for each MOSFET:

Pdiss = 3.6 Q  $f_{PWM}$  (V<sub>B</sub> + 20V) + V<sub>B</sub> 10mA (\*)

(\*) P<sub>diss</sub> formula is valid in case VB = VDH. In case VDH and VB are different, please consider that VB + 20 V = V(BST\_C,max). For the calculation, it is possible to change (VB + 20 V) in (VDH + 20 V) or BST\_C voltage have to be measured directly.

#### 4.5.2 Voltage regulator VDD

The device is operated in the specified operating range, unless otherwise specified (V<sub>CC</sub> = 3.20 V to 5.25 V, VB = 4.2 V to 54 V, T<sub>j</sub> = -40 °C to 150 °C).

| Symbol            | Parameter                  | Test condition                                                                                   | Min | Тур | Max | Unit |

|-------------------|----------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| VDD               | -                          | No external current load                                                                         | 3.0 | 3.3 | 3.6 | V    |

| T <sub>wuae</sub> | Wake up time (design info) | Time from $V_{CC}$ to steady state to $V_{dd}$ power on reset release (with 100 nF on $V_{dd}$ ) | -   | -   | 100 | μs   |

# 4.5.3 Logic input pins (PWM\_H1 to 3, PWM\_L1 to 3, SCK, CS, SDI, BST\_DIS, EN1 and EN2)

The device is operated in the specified operating range, unless otherwise specified (V<sub>CC</sub> = 3.20 V to 5.25 V, VB = 4.2 V to 54 V, T<sub>j</sub> = -40 °C to 150 °C).

| Symbol                             | Parameter                                              | Test condition                                                                                                  | Min  | Мах | Unit |

|------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|-----|------|

| Vin(HL)                            | High level input voltage                               | -                                                                                                               | 1.9  | -   | V    |

| Vin(LL)                            | Low level input voltage                                | -                                                                                                               | -    | 0.8 | V    |

| Vhin                               | Input voltage hysteresis                               | -                                                                                                               | 0.1  | -   | V    |

| Twuae                              | Wake up time (design info)                             | Time from $V_{CC}$ to<br>steady state to $V_{dd}$<br>power on reset<br>release (with 100 nF<br>on $V_{dd}$ )    | -    | 100 | μs   |

| I <sub>in(PD)</sub> <sup>(1)</sup> | PWM_H1 to 3, PWM_L1 to 3, SDI,<br>BST_DIS, EN1 and EN2 | V <sub>in</sub> = 0.8 V                                                                                         | 15   | 45  | μA   |

| I <sub>in(PU)</sub> <sup>(1)</sup> | Input pins pull up current at CS pin                   | V <sub>in</sub> = 2 V                                                                                           | -45  | -15 | μA   |

| td_EN                              | EN1, EN2 falling edge deglitch time                    | Delay time from<br>EN=(EN1 AND EN2)<br>falling edge to gate<br>drive switch off<br>(guaranteed through<br>scan) | 1.36 | 3   | μs   |

| Table 11 | . Loaic I/C | ) pins | electrical | characteristics |

|----------|-------------|--------|------------|-----------------|

|          |             |        | 010001100  |                 |

1. No PU/PD current at SCK pin.

### 4.5.4 Logic output pins (FS\_FLAG, SDO, TO3)

The device is operated in the specified operating range, unless otherwise specified (V<sub>CC</sub> = 3.20 V to 5.25 V, VB = 4.2 V to 54 V,  $T_j$  = -40 °C to 150 °C).

| Table 12. Logic output pins (FS_FL | AG, SDO, TO3) electrical characteristics |

|------------------------------------|------------------------------------------|

|------------------------------------|------------------------------------------|

| Symbol   | Parameter                 | Test condition             | Min       | Мах | Unit |

|----------|---------------------------|----------------------------|-----------|-----|------|

| Vout(HL) | High level output voltage | I <sub>sink</sub> = -1 mA  | Vcc-300mV | -   | mV   |

| Vout(LL) | Low level output voltage  | I <sub>source</sub> = 1 mA | -         | 300 | mV   |

#### 4.5.5 Boost converter

The device is operated in the specified operating range, unless otherwise specified (V<sub>CC</sub> = 3.20 V to 5.25 V, VB = 4.2 V to 54 V, T<sub>j</sub> = -40 °C to 150 °C).

| Symbol           | Parameter                      | Test condition           | Min     | Тур    | Мах    | Unit |

|------------------|--------------------------------|--------------------------|---------|--------|--------|------|

| V <sub>bst</sub> | Boost regulator output voltage | I <sub>bst</sub> = 50 mA | VDH+8.5 | VDH+10 | VDH+15 | V    |

| I <sub>bst</sub> | Boost regulator output current | V <sub>B</sub> = 14 V    | -       | 50     | 70     | mA   |

Table 13. Boost converter electrical characteristics

| Symbol              | Parameter                                           | Test condition                   | Min             | Тур | Max            | Unit |

|---------------------|-----------------------------------------------------|----------------------------------|-----------------|-----|----------------|------|

| I <sub>LIM</sub>    | Boost switch current limit                          | -                                | 250             | -   | 500            | mA   |

| Lbst                | Boost regulator inductance                          | -                                | -               | 47  | -              | μH   |

| Cbst                | Boost regulator capacitance                         | -                                | -               | 2   | -              | μF   |

| f <sub>SW_BST</sub> | Boost regulator switching frequency                 | -                                | 280             | 350 | 420            | kHz  |

| BST_HOV             | Boost over voltage threshold                        | -                                | 63              | -   | 73             | V    |

| BST_HOV<br>_HYST    | Boost over voltage hysteresis                       | -                                | 8               | -   | 10             | V    |

| T <sub>bst</sub>    | Boost regulator start-up time (design info)         | C <sub>bst</sub> = 2 µF          | -               | 1   | -              | ms   |

| VCAP                | Supply voltage for the LS gate driver               | I <sub>CAP</sub> = 25 mA         | V(SLS3)<br>+8.5 | -   | V(SLS3)<br>+15 | V    |

| I <sub>CAP</sub>    | Output current for the voltage regulator for the LS | V <sub>B</sub> = 14 V            | -65             | -   | -20            | mA   |

| V <sub>CBSX</sub>   | Bootstrap capacitor voltage<br>V(CBSx)-V(SHSx)      | V(SHSx) = 14 V,<br>ICBSX = -6 mA | 8.5             | -   | 15             | V    |

| I <sub>CBSX</sub>   | Bootstrap capacitor charge current at pin CBSx      | -                                | 6               | -   | 18             | mA   |

Table 13. Boost converter electrical characteristics (continued)

#### 4.5.6 MOSFET drivers

The device is operated in the specified operating range, unless otherwise specified (V<sub>CC</sub> = 3.20 V to 5.25 V, VB = 4.2 V to 54 V, T<sub>j</sub> = -40 °C to 150 °C).

| Symbol                           | Parameter                            | Test condition                                                      | Min | Тур | Max | Unit |

|----------------------------------|--------------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>GS</sub> (L)              | Low level output voltage             | VGx-VSx @ I= 50 mA                                                  | -   | 100 | 250 | mV   |

| V <sub>GS</sub> (H)              | High level output voltage            | VGx-VSx @ I= -5 mA                                                  | 7.5 | -   | 15  | V    |

|                                  |                                      | IG_1,IG_0 = 11 100% Imax                                            | 450 | 600 | 750 | mA   |

|                                  | Turn-on/off current with GCR = 1     | IG_1,IG_0 = 10 75% Imax                                             | 337 | 450 | 563 | mA   |

| $I_{Gxx_1}$ $k\Omega^{(1)}$      | IG_1,IG_0 = 01 50% Imax              | 225                                                                 | 300 | 375 | mA  |      |

|                                  |                                      | IG_1,IG_0 = 00 25% Imax                                             | 112 | 150 | 188 | mA   |

|                                  |                                      | IG_1,IG_0 = 11 100% Imax                                            | 75  | 100 | 125 | mA   |

|                                  | Turn-on/off current with GCR = 6     | IG_1,IG_0 = 10 75% Imax                                             | 56  | 75  | 94  | mA   |

| I <sub>Gxx_2</sub>               | kΩ                                   | IG_1,IG_0 = 01 50% Imax                                             | 37  | 50  | 63  | mA   |

|                                  |                                      | IG_1,IG_0 = 00 25% Imax                                             | 18  | 25  | 32  | mA   |

| I <sub>SLSx</sub> <sup>(2)</sup> | Low-side driver SLS output current   | GCR = 1 k $\Omega$ , PWM signals low                                | -   | -   | 3.3 | mA   |

| I <sub>SHSx</sub> <sup>(2)</sup> | High-side driver SHS output current  | GCR = 1 k $\Omega$ , PWM signals low                                | -   | -   | 3.3 | mA   |

| GCR_STG                          | Gate driver over current protection  | -                                                                   | -   | -   | 880 | Ω    |

| GCR_OL                           | Gate driver under current protection | -                                                                   | 22  | -   | -   | kΩ   |

| RGxxON                           | ON-resistance of SINK stage          | GCR = 1 k $\Omega$ , IG_1,IG_0=11, I = 25 mA injected into Gate pin | -   | -   | 5   | Ω    |

Table 14. MOSFET drivers electrical characteristics

| r               |                                          |                         |      |     |      |      |

|-----------------|------------------------------------------|-------------------------|------|-----|------|------|

| Symbol          | Parameter                                | Test condition          | Min  | Тур | Мах  | Unit |

| RGxx            | Gate source passive discharge resistance | -                       | 100  | 200 | 500  | kΩ   |

| tGHxlh          | Propagation delay time low to high       | VB = 13.5 V, Cg = 22 nF | -    | -   | 300  | ns   |

| tGLxlh          | Propagation delay time low to high       | VB = 13.5 V, Cg = 22 nF | -    | -   | 300  | ns   |

| tGHxhl          | Propagation delay time high to low       | VB = 13.5 V, Cg = 22 nF | -    | -   | 300  | ns   |

| tGLxhl          | Propagation delay time high to low       | VB = 13.5 V, Cg = 22 nF | -    | -   | 300  | ns   |

| fpwm            | PWM Switching frequency                  | -                       | -    | -   | 20   | kHz  |

| Q               | Drivable gate charge <sup>(3)</sup>      | VGS = 10 V, 20 kHz      | 300  | -   | 900  | nC   |

|                 |                                          | DT1, DT0 = 00 (default) | 100  | -   | 200  | ns   |

| t               | Dead time (adjustable in 4 steps via     | DT1, DT0 = 01           | 300  | -   | 500  | ns   |

| t <sub>DT</sub> | 2-bit SPI Register)                      | DT1, DT0 = 10           | 700  | -   | 1000 | ns   |

|                 |                                          | DT1, DT0 = 11           | 1000 | -   | 1500 | ns   |

Table 14. MOSFET drivers electrical characteristics (continued)

1. Only for turn-on currents with GCR = 1 kW: parameter is tested at hot temperature only; other temperatures are granted by design.

2. I = 400 μA + 2.81/GCR.

3. Design information. The IC does not provide any active internal Gate Charge limit.

| Table 15. PowerMOS overcurrent drop voltage sense | Table 15. | PowerMOS | overcurrent | drop | voltage | sense |

|---------------------------------------------------|-----------|----------|-------------|------|---------|-------|

|---------------------------------------------------|-----------|----------|-------------|------|---------|-------|

| Symbol                 | Parameter                                                                                         | Test condition <sup>(1)</sup>    | Min  | Тур                                     | Max               | Unit |

|------------------------|---------------------------------------------------------------------------------------------------|----------------------------------|------|-----------------------------------------|-------------------|------|

| eysei                  | - diameter                                                                                        |                                  |      | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | max               | •    |

| Chart sins it data sti | Short aircuit dataction thrashold low                                                             | SC_LS1, SC_LS0 = 00<br>(default) | 0.4  | 0.5                                     | 0.6               | V    |

| Vsc_ls                 | Short circuit detection threshold low-<br>side (adjustable in 4 steps via 2 bits<br>SPI register) | SC_LS1, SC_LS0 = 01              | 0.7  | 0.8                                     | 0.9               | V    |

|                        |                                                                                                   | SC_LS1, SC_LS0 = 10              | 0.9  | 1                                       | 1.1               | V    |

|                        |                                                                                                   | SC_LS1, SC_LS0 = 11              | 1.17 | 1.3                                     | 1.43              | V    |

|                        | Short Circuit detection threshold high-<br>Vsc_Hs side (adjustable in 4 steps via 2 bits          | SC_HS1, SC_HS0 = 00<br>(default) | 0.4  | 0.5                                     | 0.6               | V    |

| Vsc_нs                 |                                                                                                   | SC_HS1, SC_HS0 = 01              | 0.7  | 0.8                                     | 0.9               | V    |

|                        | SPI register)                                                                                     | SC_HS1, SC_HS0 = 10              | 0.9  | 1                                       | 1.1               | V    |

|                        |                                                                                                   | SC_HS1, SC_HS0 = 11              | 1.17 | 1.3                                     | 1.43              | V    |

| TSCoff                 | Short Circuit shut down delay (the<br>circuit shuts down by short circuit                         | Masking time at switch<br>ON     | 9    | 12                                      | 14 <sup>(2)</sup> | μs   |

| 13001                  | ISCOII longer than TSCoff; guaranteed through scan)                                               | Filter Time in normal operation  | 1    | -                                       | 2                 | μs   |

| VSC TEST               | Test functions for short circuit detection level $(SCDL)^{(3)}$                                   | VSC <sub>TST</sub> =1 (CMD2, B7) | -0.7 | -0.5                                    | -0.3              | V    |

1. The accuracy of SC detection thresholds for HS and LS is guaranteed for VB  $\ge$  6 V. In case VB < 6 V the accuracy for each configuration, both for HS and LS, is 22.5%.

2. The PWM ON time must be longer than this Short Circuit shutdown delay, else the short circuit condition cannot be detected.

3. Security Level test function. If this function is selected via SPI, the short circuit detection threshold is set to the specified negative level. In this way a short circuit is detected even if the current in the external MOSFET is zero, that is Vds=0.

| Symbol               | Parameter                                                                                                                                                                     | Test condition               | Min | Тур | Мах | Unit |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|-----|-----|------|

| V <sub>G UV HS</sub> | Undervoltage threshold for<br>HS gate driver. It monitors the<br>voltage difference between<br>boost output pin BST_C and<br>HS FET drain connection<br>VDH                   | V(BST_C)-V(VDH)              | 4.6 | -   | 6.8 | V    |

| V <sub>G UV LS</sub> | Undervoltage threshold for<br>LS gate driver. It monitors the<br>voltage difference between<br>low-side gate driver supply<br>pin VCAP and LS FET 3<br>source connection SLS3 | V(VCAP)-V(SLS3)              | 7.4 | 8.2 | 9.0 | V    |

| t <sub>UV VG</sub>   | Undervoltage filter time                                                                                                                                                      | (guaranteed through<br>scan) | 3.5 | 5   | 7   | μs   |

Table 16. Gate voltage monitoring

#### 4.5.7 Current sense amplifier

The device is operated in the specified operating range, unless otherwise specified (V<sub>CC</sub> = 3.20 V to 5.25 V, VB = 4.2 V to 54 V, T<sub>i</sub> = -40 °C to 150 °C).

*Note:* Table 17 is referred to bidirectional current measurement (shunt resistors on the phase of the motor).

| Symbol                          | Parameter                                                                  | Test condition                             | Min                                         | Тур                 | Max                                         | Unit  |

|---------------------------------|----------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------|---------------------|---------------------------------------------|-------|

| Vin_off                         | Differential input offset<br>voltage                                       | -                                          | -5                                          | -                   | 5                                           | mV    |

| Vio_step                        | Calibration step of<br>Differential input offset<br>voltage <sup>(1)</sup> | -                                          | 0.5                                         | 1                   | 1.5                                         | mV    |

| VICM                            | Common mode input                                                          | Operating                                  | -2                                          | -                   | VB+4                                        | V     |

| VICINI                          | voltage range                                                              | Transient (t < 1 µs)                       | -7                                          | -                   | VB+20                                       | V     |

| V <sub>obias</sub>              | Output bias voltage                                                        | V(Isx+) -V(Isx-) = 0                       | 0.5*V <sub>cc</sub> -<br>0.5 <sup>(2)</sup> | 0.5*V <sub>cc</sub> | 0.5*V <sub>cc</sub> +<br>0.5 <sup>(3)</sup> | V     |

| IOD                             | Input offset drift <sup>(3)</sup>                                          | Vcc = 5V                                   | -                                           | 7                   | 14                                          | µV/°C |

| CMRR                            | Input common mode<br>rejection ratio                                       | -                                          | 70                                          | 86                  | -                                           | dB    |

| I <sub>SX+</sub> <sup>(4)</sup> | Positive input pin current                                                 | Gain = 10 to 100,<br>V <sub>CC</sub> = 5 V | -200                                        | -                   | -                                           | μA    |

| I <sub>SX-</sub> <sup>(4)</sup> | Negative input pin current                                                 | Gain = 10 to 100,<br>V <sub>CC</sub> = 5 V | -1                                          | -                   | -                                           | mA    |

| BST_C PSRR                      | Rejection ratio for Boost<br>output power supply to<br>amplifier Input     | V(BST_C) / V(IBx)<br>f=350KHz              | 40 <sup>(5)</sup>                           | -                   | -                                           | dB    |

Table 17. Phase current sense amplifier (SPI select: Offx=1, where x=1,2)

| Symbol                | Parameter                                             | Test condition                                                                                  | Min                        | Тур | Max | Unit       |

|-----------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------|-----|-----|------------|

|                       |                                                       | Gx1,Gx0 = 11 (x = 1,2)                                                                          | -2%                        | 100 | +2% | -          |

| Gain                  | Gain<br>Gain<br>Gain temperature drift <sup>(3)</sup> | Gx1,Gx0 = 10 (x = 1,2)                                                                          | -2%                        | 50  | +2% | -          |

|                       |                                                       | Gx1,Gx0 = 01 (x = 1,2)                                                                          | -2%                        | 30  | +2% | -          |

|                       |                                                       | Gx1,Gx0 = 00 (x = 1,2)<br>(default)                                                             | -2%                        | 10  | +2% | -          |

|                       |                                                       | -                                                                                               | -                          | -   | 100 | ppm/<br>°C |

| M                     | IBx output voltage high<br>level                      | V(lsx+) -V(lsx-) > 500mV,<br>l <sub>out</sub> = 100 µA, V <sub>CC</sub> = 3.3 V                 | V <sub>cc</sub> -<br>0.12V | -   | -   | -          |

| V <sub>oh</sub>       |                                                       | V(lsx+) -V(lsx-) > 500mV,<br>l <sub>out</sub> = 100 µA, V <sub>CC</sub> = 5V                    | V <sub>cc</sub> -<br>0.15V | -   | -   | -          |

| V <sub>ol</sub>       | IBx output voltage low level                          | V(lsx+) -V(lsx-) <<br>-500mV, l <sub>out</sub> = 100 µA                                         | -                          | -   | 100 | mV         |

| SRCSO                 | CSO slew rate                                         | RL = 1 kOhm, CL = 20 pF                                                                         | 0.5                        | 2   | -   | V/µs       |

| <sup>t</sup> SETTLING | Output settling time                                  | Gain = 10,30, 50 and 100,<br>from 10% to 90%<br>R <sub>L</sub> = 1 kOhm, C <sub>L</sub> = 20 pF | -                          | -   | 5.0 | μs         |

Table 17. Phase current sense amplifier (SPI select: Offx=1, where x=1.2)

1. 30 calibration steps (15 for positive and 15 for negative direction) are available through SPI command for offset calibration.

- 2. Worst case, if gain = 100 is selected.

- 3. Guaranteed by design.

4.

$$I_{SxHI} = -\left(\frac{0.8 \cdot V_{CC}}{2000 \cdot Gnom} + I(trim, HI)\right) \cdot \frac{[2 + (3 \cdot Phase)]}{8} + 10 \mu A$$

$$I_{SxLO} = -\left(\frac{0.8 \cdot V_{CC}}{2000 \cdot Gnom} + I(trim, LO)\right) \cdot \frac{2}{8} + 10\mu A + I(rail)$$

Where:

Where:  $I_{SXHI}$  is current flowing out from ISxHI pin  $I_{SXLO}$  is current flowing out from ISxLO pin Vcc = reference supply [5 V or 3.3 V] Gnom = nominal programmed gain [10, 30, 50, 100] I(trim,HI/LO) = offset trimming current (w.c. ±8 µA see expression below) Phase = programmed phase configuration [1 if selected, otherwise 0] I(trial) = current from auxiliary rail (used for floating OpAmp) [typ ~145 µA±35% T+Models] : -- l= +-

$$I(\text{trim, HI}) = \pm \frac{Vbg}{15} \cdot \frac{\left[ \text{trimming bit} \frac{\text{weight}}{2} \right]}{10300 \cdot [5 + (3 \cdot \text{Ground})]} \cdot \frac{[2 + (3 \cdot \text{Phase})]}{8}$$

$$I(\text{trim, LO}) = \pm \frac{Vbg}{15} \cdot \frac{\left[ \text{trimming bit} \frac{\text{weight}}{2} \right]}{10300 \cdot [5 + (3 \cdot \text{Ground})]} \cdot \frac{2}{8}$$

Where: