## **Description**

The F2950 is a high power, reflective  $50\Omega$ , single-pole double-throw (SP2T) RF switch. This device covers a 100MHz to 8GHz frequency range to support a wide variety of applications including WLAN 802.11.

The F2950 uses a single positive supply voltage and is compatible with both 1.8V and 3.3V control logic.

## **Competitive Advantage**

The F2950 provides extremely low insertion loss across a very broad bandwidth while providing high linearity performance across its operating range.

- Optimized for Wi-Fi applications

- Wide bandwidth

- Low insertion loss

- Excellent linearity

- High power handling for large peak-to-average applications

- Fast switching

- No external matching required

- Minimal footprint

## **Typical Applications**

- 802.11 Wi-Fi

- Wireless Access Points, Gateways and Router Applications

- LTE and 4G Communication Systems

- 2-Way Radios

- General Purpose

#### **Features**

- Low insertion loss: 0.58dB at 2.5GHz

- High isolation: 44dB at 2.5GHz

- Excellent linearity:

- IIP3 +69dBm at 2.4GHz and 5.9GHz

- IIP2 +115dBm at 2.4GHz

- IIP2 +117dBm at 5.9GHz

- Second Harmonic: -93dBc at 5.9GHz

- Third Harmonic: -85dBc at 5.9GHz

- Typical switching speed: 170ns

- Supply voltage: +2.7V to +5.5V

- 1.8V and 3.3V compatible control logic

- -40°C to +105°C operating temperature range

- 1.5mm x 1.5mm, 6-pin DFN package

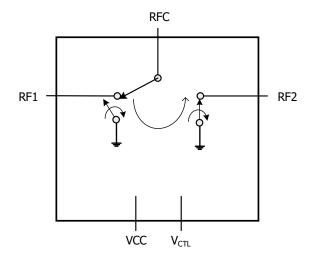

### **Block Diagram**

#### Figure 1. Block Diagram

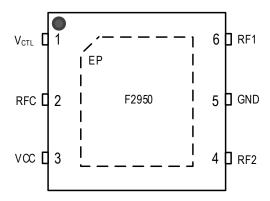

# **Pin Assignments**

Figure 2. Pin Assignments for 1.5mm x 1.5mm x 0.55mm DFN, NEG6 – Top View

## **Pin Descriptions**

Table 1. Pin Descriptions

| Pin | Name      | Function                                                                                                                                                                                                                                                                   |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | $V_{CTL}$ | Logic control pin. See Table 7 for logic control states.                                                                                                                                                                                                                   |

| 2   | RFC       | RF common port. Matched to $50\Omega$ in the insertion loss state only. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                        |

| 3   | Vcc       | Power supply. Bypass to GND with capacitors as close as possible to the pin.                                                                                                                                                                                               |

| 4   | RF2       | RF2 port. Matched to $50\Omega$ in the insertion loss state only. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                              |

| 5   | GND       | Ground. Ground this pin as close to the device as possible.                                                                                                                                                                                                                |

| 6   | RF1       | RF1 port. Matched to $50\Omega$ in the insertion loss state only. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                              |

|     | EP        | Exposed pad. Internally connected to GND. Solder this exposed pad to a PCB pad that uses multiple ground vias to provide heat transfer out of the device into the PCB ground planes. These multiple ground vias are also required to achieve the specified RF performance. |

## **Absolute Maximum Ratings**

Stresses beyond those listed below may cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Table 2. Absolute Maximum Ratings**

| Paramete                                                              | er                             | Symbol              | Minimum            | Maximum                               | Units |

|-----------------------------------------------------------------------|--------------------------------|---------------------|--------------------|---------------------------------------|-------|

| V <sub>CC</sub> to GND                                                |                                | V <sub>CC</sub>     | -0.3               | +6.0                                  | V     |

| V <sub>CTL</sub> to GND                                               |                                | V <sub>LOGIC</sub>  | -0.3               | Lower of (V <sub>CC</sub> + 0.3, 3.9) | V     |

| RF1, RF2, RFC to GND                                                  |                                | $V_{RF}$            | -0.3               | +0.3                                  | V     |

|                                                                       | $100MHz \le f_{RF} \le 200MHz$ | P <sub>ABSCW1</sub> |                    | 28                                    |       |

| Maximum Input CW Power,                                               | $200MHz < f_{RF} \le 500MHz$   | P <sub>ABSCW2</sub> |                    | 29                                    |       |

| $Z_S = Z_L = 50\Omega$ ,<br>$T_{EP} = 25^{\circ}C$ , $V_{CC} = 5.25V$ | $500MHz < f_{RF} \le 1GHz$     | P <sub>ABSCW3</sub> |                    | 30                                    | dBm   |

| (any port, insertion loss state) [a]                                  | $1GHz < f_{RF} \le 6GHz$       | P <sub>ABSCW4</sub> |                    | 31                                    |       |

| ,                                                                     | f <sub>RF</sub> > 6GHz         | P <sub>ABSCW5</sub> |                    | 30                                    |       |

|                                                                       | $100MHz \le f_{RF} \le 200MHz$ | P <sub>ABSPK1</sub> |                    | 35                                    |       |

| Maximum Peak Power,                                                   | $200MHz < f_{RF} \le 500MHz$   | P <sub>ABSPK2</sub> |                    | 36                                    |       |

| $Z_S = Z_L = 50\Omega$ ,<br>$T_{EP} = 25^{\circ}C$ , $V_{CC} = 5.25V$ | $500MHz < f_{RF} \le 1GHz$     | P <sub>ABSPK3</sub> |                    | 37                                    | dBm   |

| (any port, insertion loss state) [a], [b]                             | 1GHz < f <sub>RF</sub> ≤ 6GHz  | P <sub>ABSPK4</sub> |                    | 38                                    |       |

|                                                                       | f <sub>RF</sub> > 6GHz         | P <sub>ABSPK5</sub> |                    | 37                                    |       |

| Maximum Junction Temperature                                          |                                | $T_{JMAX}$          |                    | +140                                  | °C    |

| Storage Temperature Range                                             |                                | T <sub>STOR</sub>   | -65                | +150                                  | °C    |

| Lead Temperature (soldering, 10s)                                     |                                | $T_LEAD$            |                    | +260                                  | °C    |

| Electrostatic Discharge – HBM (JEDEC/ESDA JS-001-2012)                | V <sub>ESDHBM</sub>            |                     | 2000<br>(Class C2) | V                                     |       |

| Electrostatic Discharge – CDM (JEDEC 22-C101F)                        |                                | V <sub>ESDCDM</sub> |                    | 500<br>(Class C2)                     | V     |

<sup>[</sup>a]  $T_{EP}$  is the temperature of the exposed paddle.

<sup>[</sup>b] 5% duty cycle of 4.6ms period in a  $50\Omega$  environment.

## **Recommended Operating Conditions**

**Table 3. Recommended Operating Conditions**

| Parameter                    | Symbol                | Conditions                                          | Min          | Тур | Max  | Units |

|------------------------------|-----------------------|-----------------------------------------------------|--------------|-----|------|-------|

| Power Supply Voltage         | $V_{CC}$              |                                                     | 2.7 [a]      | 3.3 | 5.5  | V     |

| Operating Temperature Range  | $T_{EP}$              | Exposed paddle                                      | -40          | +25 | +105 | °C    |

| RF Frequency Range           | $f_{RF}$              |                                                     | 0.1          |     | 8    | GHz   |

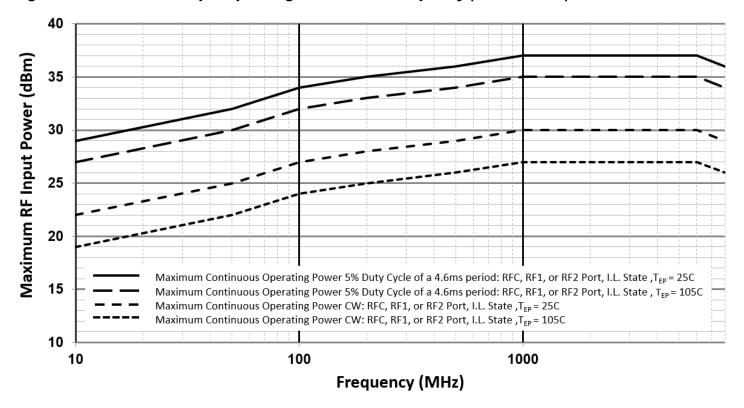

|                              | $P_{RF\_CW}$          | CW, insertion loss state                            | See Figure 3 |     |      |       |

| RF Input Power [b]           | P <sub>RF_PULSE</sub> | 5% duty cycle of 4.6ms period, insertion loss state | See Figure 3 |     | dBm  |       |

| RFC, RF1, RF2 Port Impedance | $Z_{RF}$              |                                                     |              | 50  |      | Ω     |

<sup>[</sup>a] Functional with reduced performance for  $2.3V \le V_{CC} < 2.7V$ .

Figure 3. Maximum RF Input Operating Power vs. RF Frequency ( $Z_S = Z_L = 50\Omega$ )

<sup>[</sup>b] Levels based on:  $V_{CC}$  = 2.7V to 5.5V, 100MHz  $\leq$  f<sub>RF</sub>  $\leq$  8GHz,  $Z_S$  =  $Z_L$  = 50 $\Omega$ . See Figure 3 for power handling derating vs. RF frequency.

#### **Electrical Characteristics**

#### Table 4. Electrical Characteristics

See F2950 Typical Application Circuit. Specifications apply when operated with  $V_{CC}$  = +3.3V,  $T_{EP}$  = +25°C,  $P_{IN}$  = 0dBm,  $Z_S$  =  $Z_L$  = 50 $\Omega$ , single tone and two tone signals applied at RF1 or RF2 and measured at RFC when in the ON state, PCB board trace and connector losses are deembedded, unless otherwise noted.

| Parameter                               | Symbol                           | Conditions                              | Min                | Тур  | Max                              | Units |  |

|-----------------------------------------|----------------------------------|-----------------------------------------|--------------------|------|----------------------------------|-------|--|

| Logic Input High Threshold              | V <sub>IH</sub>                  | V <sub>CTL</sub> pin                    | 1.1 <sup>[b]</sup> |      | Lower of (V <sub>CC</sub> , 3.6) | V     |  |

| Logic Input Low Threshold               | $V_{IL}$                         | V <sub>CTL</sub> pin                    | -0.3               |      | 0.6                              | V     |  |

| Logic Current                           | I <sub>IH,</sub> I <sub>IL</sub> | V <sub>CTL</sub> pin                    | -1                 |      | +1                               | μΑ    |  |

| DC Current                              | Icc                              |                                         |                    | 170  | <b>250</b> [a]                   | μΑ    |  |

|                                         |                                  | $f_{RF}$ = 100MHz to 900MHz             |                    | 0.54 | 0.74                             |       |  |

|                                         |                                  | f <sub>RF</sub> = 900MHz to 2500MHz [c] |                    | 0.58 | 0.79                             |       |  |

| Insertion Loss (RF1 or RF2 to RFC)      | IL                               | $f_{RF} = 2500MHz$ to 3700MHz           |                    | 0.61 | 0.83                             | dB    |  |

| Insertion coss (Ki 1 of Ki 2 to Ki C)   | -                                | $f_{RF} = 3700MHz$ to $4900MHz$         |                    | 0.64 | 0.88                             | uБ    |  |

|                                         |                                  | $f_{RF} = 4900MHz$ to $6000MHz$         |                    | 0.67 | 0.90                             |       |  |

|                                         |                                  | $f_{RF} = 6000MHz$ to $8000MHz$         |                    | 0.73 |                                  |       |  |

|                                         |                                  | $f_{RF} = 100MHz$ to $900MHz$           | 48                 | 53   |                                  | dB    |  |

|                                         | ISO1                             | $f_{RF} = 900MHz$ to 2500MHz            | 39                 | 44   |                                  |       |  |

| Isolation (RF1 or RF2 to RFC)           |                                  | $f_{RF} = 2500MHz$ to 3700MHz           | 35                 | 40   |                                  |       |  |

| Isolation (NT 1 of NT 2 to NT 0)        |                                  | $f_{RF} = 3700MHz$ to $4900MHz$         | 32                 | 37   |                                  |       |  |

|                                         |                                  | $f_{RF} = 4900MHz$ to $6000MHz$         |                    | 34   |                                  |       |  |

|                                         |                                  | $f_{RF} = 6000MHz$ to $8000MHz$         |                    | 31   |                                  |       |  |

|                                         |                                  | $f_{RF} = 100MHz$ to $900MHz$           | 50                 | 54   |                                  |       |  |

|                                         |                                  | $f_{RF} = 900MHz$ to 2500MHz            | 40                 | 44   |                                  | ]     |  |

| Isolation (RF1 to RF2, RF2 to RF1)      | ISO2                             | $f_{RF} = 2500MHz$ to $3700MHz$         | 35                 | 40   |                                  | dB    |  |

| lisolation (Ni T to Ni Z, Ni Z to Ni T) | 1002                             | $f_{RF} = 3700MHz$ to $4900MHz$         | 32                 | 37   |                                  | UD    |  |

|                                         |                                  | $f_{RF} = 4900MHz$ to $6000MHz$         |                    | 34   |                                  |       |  |

|                                         |                                  | $f_{RF} = 6000MHz$ to $8000MHz$         |                    | 30   |                                  |       |  |

|                                         |                                  | $f_{RF} = 100MHz$ to $900MHz$           |                    | 25   |                                  |       |  |

|                                         |                                  | $f_{RF}$ = 900MHz to 2500MHz            |                    | 23   |                                  | dB    |  |

| Return Loss (RFC, RF1, RF2)             | RL                               | f <sub>RF</sub> = 2500MHz to 3700MHz    |                    | 22   |                                  |       |  |

| 110001112000 (111 0, 111 1, 111 2)      | I RL                             | $f_{RF}$ = 3700MHz to 4900MHz           |                    | 21   |                                  |       |  |

|                                         |                                  | $f_{RF}$ = 4900MHz to 6000MHz           |                    | 20   |                                  |       |  |

|                                         |                                  | $f_{RF} = 6000MHz$ to $8000MHz$         |                    | 20   |                                  |       |  |

<sup>[</sup>a] Items in min/max columns in bold italics are guaranteed by test.

<sup>[</sup>b] Items in min/max columns that are not bold italics are guaranteed by design characterization.

<sup>[</sup>c] Minimum or maximum specification guaranteed by test at 2.5GHz and by design characterization over the whole frequency range.

#### **Electrical Characteristics**

#### Table 5. Electrical Characteristics

See F2950 Typical Application Circuit. Specifications apply when operated with  $V_{CC}$  = +3.3V,  $T_{EP}$  = +25°C,  $P_{IN}$  = 0dBm,  $Z_S$  =  $Z_L$  = 50 $\Omega$ , single tone and two tone signals applied at RF1 or RF2 and measured at RFC when in the ON state, PCB board trace and connector losses are deembedded, unless otherwise noted.

| Parameter                  | Symbol             | Conditions                                                                            |      | Min | Тур  | Max | Units  |  |

|----------------------------|--------------------|---------------------------------------------------------------------------------------|------|-----|------|-----|--------|--|

| Input ID2                  | IIP3               | $f_{RF}$ = 2.4GHz at $P_{IN}$ = +24dBm/ton<br>100MHz tone spacing                     | е    |     | 69   |     | dDm    |  |

| Input IP3                  | IIPS               | $f_{RF}$ = 5.9GHz at $P_{IN}$ = +24dBm/ton<br>100MHz tone spacing                     | е    |     | 69   |     | dBm    |  |

| Inc. 4 ID2                 | IIP2               | $f_1 = 700$ MHz, $f_2 = 1.7$ GHz<br>$P_{IN} = +24$ dBm/tone<br>Measure 2.4GHz product |      |     | 115  | dBm |        |  |

| Input IP2                  | IIPZ               | $f_1$ = 2.4GHz, $f_2$ = 3.5GHz<br>$P_{IN}$ = +24dBm/tone<br>Measure 5.9GHz product    |      |     | 117  |     |        |  |

| Cocond Harmonia            | H2                 | f <sub>RF</sub> = 2.4GHz, P <sub>IN</sub> = +30dBm<br>Measure 4.8GHz product          |      |     | 104  |     | dDa    |  |

| Second Harmonic            | П2                 | f <sub>RF</sub> = 5.9GHz, P <sub>IN</sub> = +30dBm<br>Measure 11.8GHz product         |      |     | 93   |     | dBc    |  |

| Third Harmonic             | H3                 | f <sub>RF</sub> = 2.4GHz, P <sub>IN</sub> = +30dBm<br>Measure 7.2GHz product          |      |     | 85   |     | dBc    |  |

| Tillia Haimonic            | нз                 | f <sub>RF</sub> = 5.9GHz, P <sub>IN</sub> = +30dBm<br>Measure 17.7GHz product         |      |     | 85   |     | dbc    |  |

|                            |                    | $f_{RF} = 2.4GHz$                                                                     |      |     | 40   |     |        |  |

| Input 1dB compression [c]  | P1dB               | $f_{RF} = 6GHz$                                                                       |      |     | 40   |     | dBm    |  |

|                            |                    | f <sub>RF</sub> = 8GHz                                                                |      |     | 39   |     |        |  |

| Spurious Output [d]        | Pspur1             | f <sub>OUT</sub> > 5MHz<br>All ports terminated, RBW = 100H                           | z    |     | -97  |     | dBm    |  |

| Spurious Output 1-3        | Pspur2             | f <sub>OUT</sub> ≤ 5MHz<br>All ports terminated, RBW = 100H                           | z    |     | -125 |     | dDill  |  |

| Maximum Video Feed-Through | VID <sub>FT</sub>  | Peak transient during switching. Measured with 20ns rise time,                        | Rise |     | 10   |     | m\/nn  |  |

| on RF Ports                | VID <sub>FT</sub>  | 0V to 3.3V (3.3V to 0V) control pulse applied to V <sub>CTL</sub> .                   | Fall |     | 21   |     | - mVpp |  |

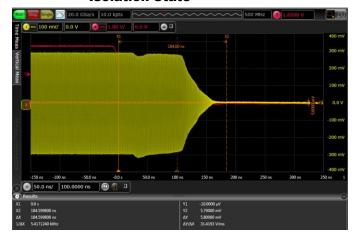

|                            |                    | 50% V <sub>CTL</sub> to 90% RF                                                        |      |     | 170  | 230 |        |  |

| Switching Time [e]         | SW <sub>TIME</sub> | 50% V <sub>CTL</sub> to 10% RF                                                        |      |     | 170  | 230 | ns     |  |

| Ownorling Time 53          | O V V I IIVIE      | 50% V <sub>CTL</sub> to 99% RF                                                        |      |     | 190  | 270 | 110    |  |

|                            |                    | 50% V <sub>CTL</sub> to 1% RF                                                         |      |     | 190  | 270 |        |  |

| Maximum Switching Rate     | SW <sub>RATE</sub> |                                                                                       |      |     | 125  |     | kHz    |  |

- [a] Items in min/max columns in **bold italics** are guaranteed by test.

- [b] Items in min/max columns that are not bold italics are guaranteed by design characterization.

- [c] The input 1dB compression point is a linearity figure of merit. Refer to the "Absolute Maximum Ratings" section and Figure 3 for the maximum RF input power.

- [d] Spurious due to on-chip negative voltage generator. Spurious fundamental is approximately 5.7MHz.

- [e]  $f_{RF} = 1$ GHz. Rise and fall time of  $V_{CTL} = 20$ ns.

## **Thermal Characteristics**

#### **Table 6. Package Thermal Characteristics**

| Parameter                                                                   | Symbol                    | Value | Units |

|-----------------------------------------------------------------------------|---------------------------|-------|-------|

| Junction to Ambient Thermal Resistance                                      | $\theta_{JA}$             | 200   | °C/W  |

| Junction to Case Thermal Resistance (Case is defined as the exposed paddle) | $	heta_{	extsf{JC\_BOT}}$ | 132   | °C/W  |

| Moisture Sensitivity Rating (Per J-STD-020)                                 |                           | MSL 1 |       |

# **Typical Operating Conditions (TOCs)**

Unless otherwise noted:

- $V_{CC} = +3.3V$

- T<sub>EP</sub> = 25°C

- $Z_S = Z_L = 50\Omega$

- f<sub>RF</sub> = 1GHz

- Small signal tests done at 0dBm input power

- All temperatures are referenced to the exposed paddle

- Evaluation Kit traces and connector losses are de-embedded

# **Typical Performance Characteristics [1]**

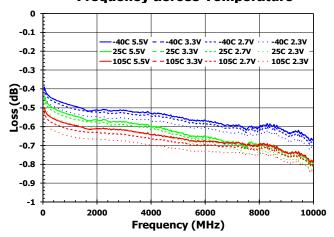

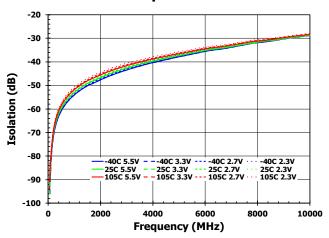

Figure 4. RF1 to RFC Insertion Loss vs.

Frequency across Temperature

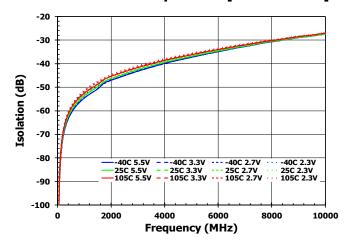

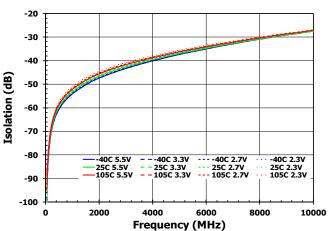

Figure 6. RF1 to RFC Isolation vs. Frequency across Temperature

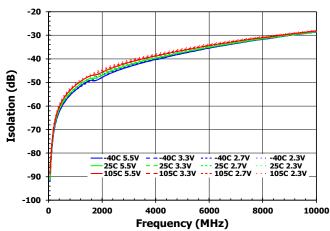

Figure 8. RF1 to RF2 Isolation vs. Frequency across Temperature [RF1 Selected]

Figure 5. RF2 to RFC Insertion Loss vs.

Frequency across Temperature

Figure 7. RF2 to RFC Isolation vs. Frequency across Temperature

Figure 9. RF2 to RF1 Isolation vs. Frequency across Temperature [RF2 Selected]

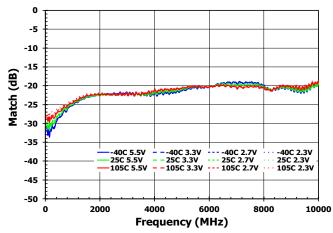

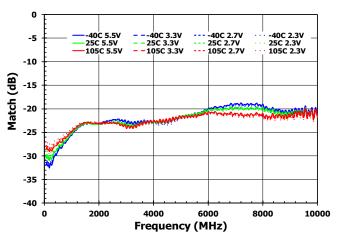

## **Typical Performance Characteristics [2]**

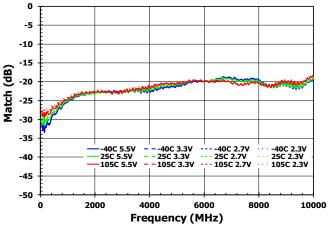

Figure 10. RF1 Return Loss vs. Frequency across Temperature [RF1 Selected]

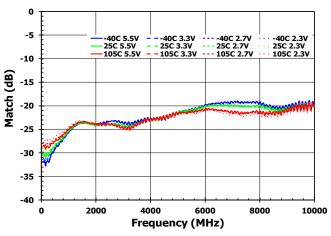

Figure 12. RFC Return Loss vs. Frequency across Temperature [RF1 Selected]

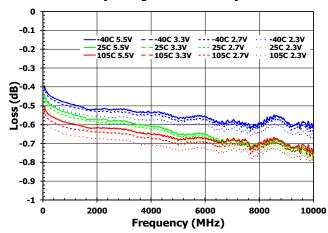

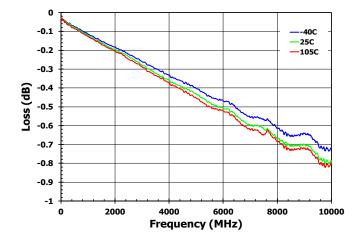

Figure 14. EVKit PCB and Connector Thru Loss vs. Frequency across Temperature

Figure 11. RF2 Return Loss vs. Frequency across Temperature [RF2 Selected]

Figure 13. RFC Return Loss vs. Frequency across Temperature [RF2 Selected]

# **Typical Performance Characteristics [3]**

Figure 15. Switching Time Isolation to Insertion Loss State

Figure 16. Switching Time Insertion Loss to Isolation State

#### **Control Mode**

Table 7. Switch Control Truth Table

| V <sub>CTL</sub> | RFC to RF1 | RFC to RF2 |

|------------------|------------|------------|

| LOW              | OFF        | ON         |

| HIGH             | ON         | OFF        |

## **Application Information**

#### **Default Start-up**

The V<sub>CTL</sub> control pin includes no internal pull-down resistors to logic LOW or pull-up resistors to logic HIGH.

### **Power Supplies**

A common  $V_{CC}$  power supply should be used for all pins requiring DC power. All supply pins should be bypassed with external capacitors to minimize noise and fast transients. Supply noise can degrade noise figure and fast transients can trigger ESD clamps and cause them to fail. Supply voltage change or transients should have a slew rate slower than  $1V / 20\mu s$ . In addition, all control pins should remain at  $0V (\pm 0.3V)$  while the supply voltage ramps up or while it returns to zero.

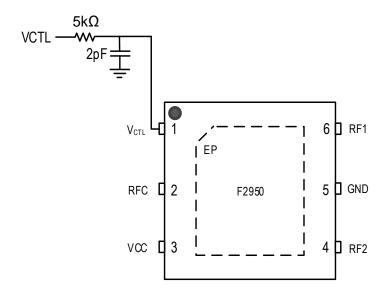

#### **Control Pin Interface**

If a clean control signal cannot be guaranteed due to overshoot, undershoot, ringing, etc., the following circuit at the input of the control pin is recommended.

Figure 17. Control Pin Signal Integrity Improvement Circuit

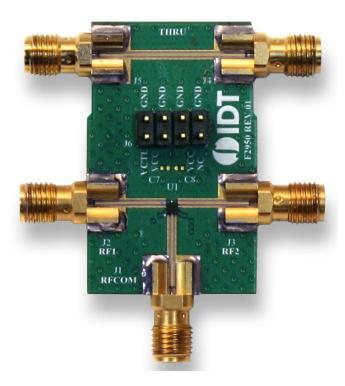

## **Evaluation Kit Picture**

## Figure 18. Top View

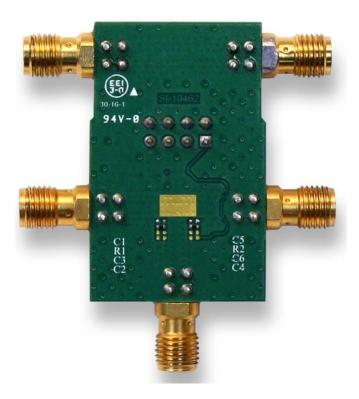

Figure 19. Bottom View

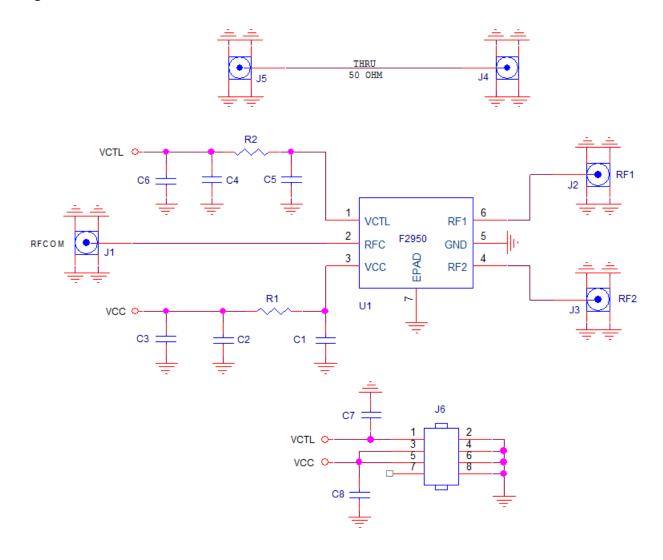

# **Evaluation Kit / Applications Circuit**

Figure 20. Electrical Schematic

Table 8. Bill of Material (BOM)

| Part Reference | QTY | Description                                    | Manufacturer Part # | Manufacturer       |

|----------------|-----|------------------------------------------------|---------------------|--------------------|

| C1             | 1   | 0.1µF ±10%, 16V, X7R, Ceramic Capacitor (0402) | GRM155R71C104K      | Murata             |

| C2 – C8        | 0   | Not Installed (0402)                           |                     |                    |

| R1, R2         | 2   | 0Ω, 1/10W, Jumper (0402)                       | ERJ-2GE0R00X        | Panasonic          |

| J1 – J5        | 5   | 50Ω Edge SMA Connector                         | 142-0761-881        | Cinch Connectivity |

| J6             | 1   | Conn Header Vert 4x2 Pos Gold                  | 67997-108HLF        | Amphenol FCI       |

| U1             | 1   | SP2T Switch 1.5mm x 1.5mm 6-pin NEG6 DFN       | F2950NEGK6          | IDT                |

|                | 1   | Printed Circuit Board                          | F2950 EVKit         | IDT                |

## **Evaluation Kit (EVKit) Operation**

### **External Supply Setup**

Set up a V<sub>CC</sub> power supply in the voltage range of 2.7V to 5.5V with the power supply output disabled.

Connect the disabled V<sub>CC</sub> supply connection to J6 pin 3 or 5 and GND to J6 pin 2, 4, 6, or 8.

### **Logic Control Setup**

With the logic control line disabled, set the logic HIGH and LOW levels to satisfy the levels stated in the electrical specifications table.

Connect the disabled logic control line to VCTL (pin 1 of J6) and GND to J6 pin 2, 4, 6, or 8.

#### **Turn On Procedure**

Set up the supplies and EVKit as noted in the "External Supply Setup" and "Logic Control Setup" sections above.

Enable the V<sub>CC</sub> supply.

Enable the logic control signal.

Set the VCTL logic setting to achieve the desired Table 7 configuration. Note that the VCTL control logic should not be applied without V<sub>CC</sub> being present.

Enable any RF signal.

#### **Turn Off Procedure**

Disable any applied RF signal.

Set VCTL to GND.

Disable the V<sub>CC</sub> supply.

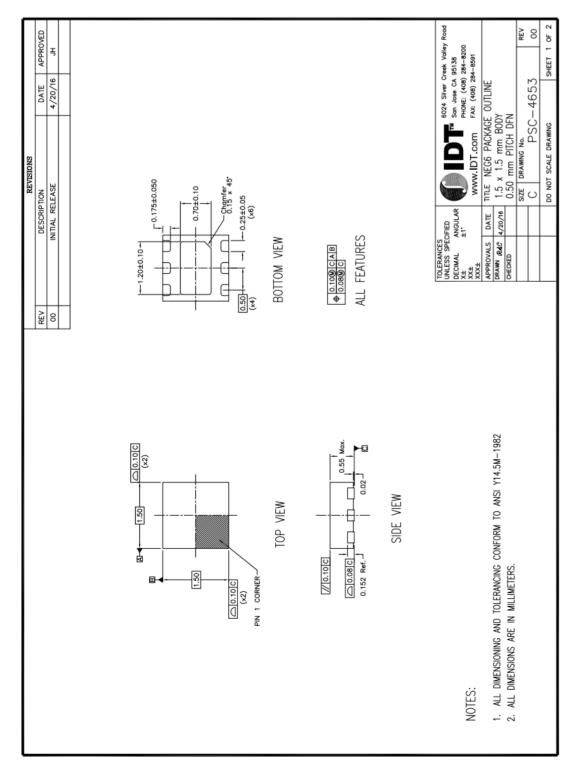

## **Package Drawings**

Figure 21. Package Outline Drawing - NEG6 Package

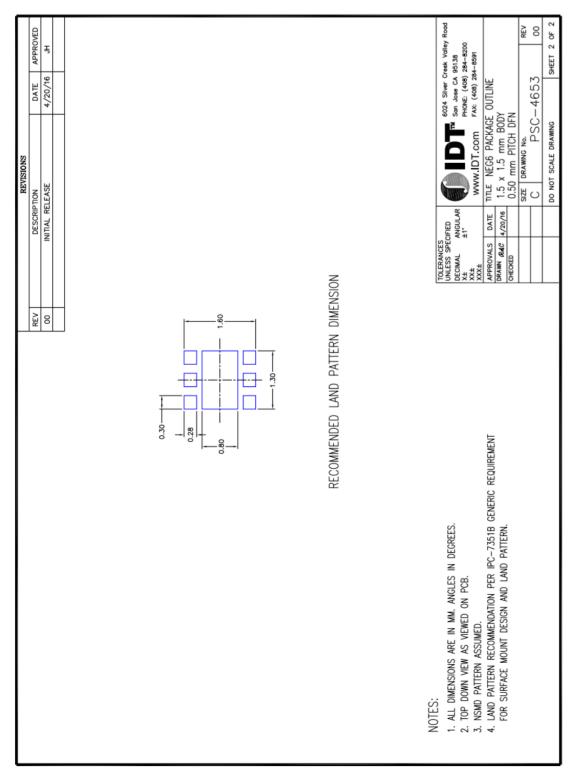

## **Recommended Land Pattern**

Figure 22. Recommended Land Pattern - NEG6 Package

# **Marking Diagram**

- 1. Line 1: Y = last digit of the year, BA = sequential letters for traceability purposes

- 2. Line 2: Pin 1 dot, 2 = F2950 part number code

# **Ordering Information**

| Orderable Part Number | Package                         | MSL Rating | Shipping Packaging | Temperature     |

|-----------------------|---------------------------------|------------|--------------------|-----------------|

| F2950NEGK             | 1.5mm x 1.5mm x 0.55mm NEG6 DFN | MSL1       | Cut Tape           | -40°C to +105°C |

| F2950NEGK8            | 1.5mm x 1.5mm x 0.55mm NEG6 DFN | MSL1       | Reel               | -40°C to +105°C |

| F2950EVBI             | Evaluation Board                |            |                    |                 |

# **Revision History**

| Revision | Revision Date  | Description of Change |

|----------|----------------|-----------------------|

| Rev O    | August 8, 2017 | Initial Release       |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/