## 32 Bit RISC Microcontroller TX00 Series

TMPM066/067/068FW

**TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

\*\*

Arm, Cortex and Thumb are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved.

arm

#### General precautions on the use of Toshiba MCUs

This Page explains general precautions on the use of Toshiba MCUs.

Note that if there is a difference between the general precautions and the description in the body of the document, the description in the body of document has higher priority.

1. The MCUs' operation at power-on

At power-on, internal state of the MCUs is unstable. Therefore, state of the pins is undefined until reset operation is completed.

When a reset is performed by an external reset pin, pins of the MCUs that use the reset pin are undefined until reset operation by the external pin is completed.

Also, when a reset is performed by the internal power-on reset, pins of the MCUs that use the internal power-on reset are undefined until power supply voltage reaches the voltage at which power-on reset is valid.

#### 2. Unused pins

Unused input/output ports of the MCUs are prohibited to use. The pins are high-impedance.

Generally, if MCUs operate while the high-impedance pins left open, electrostatic damage or latch-up may occur in the internal LSI due to induced voltage influenced from external noise.

Toshiba recommend that each unused pin should be connected to the power supply pins or GND pins via resistors.

#### 3. Clock oscillation stability

A reset state must be released after the clock oscillation becomes stable. If the clock is changed to another clock while the program is in progress, wait until the clock is stable.

#### Introduction: Notes on the description of SFR (Special Function Register) under this specification

An SFR (Special Function Register) is a control register for peripheral circuits (IP).

The SFR addresses of IPs are described in the chapter on memory map, and the details of SFR are given in the chapter of each IP.

Definition of SFR used in this specification is in accordance with the following rules.

- a. SFR table of each IP as an example

- SFR tables in each chapter of IP provides register names, addresses and brief descriptions.

- All registers have a 32-bit unique address and the addresses of the registers are defined as follows, with some exceptions: "Base address + (Unique) address"

|                  |       | Base Address = 0x0000_0000 |

|------------------|-------|----------------------------|

| Register name    |       | Address(Base+)             |

| Control register | SAMCR | 0x0004                     |

|                  |       | 0x000C                     |

Note) SAMCR register address is 32 bits wide from the address 0x0000\_0004 (Base Address (0x00000000) + unique address (0x0004)).

Note) The register shown above is an example for explanation purpose and not for demonstration purpose. This register does not exist in this microcontroller.

- b. SFR (register)

- Each register basically consists of a 32-bit register (some exceptions).

- The description of each register provides bits, bit symbols, types, initial values after reset and functions.

|             | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|-------------|----|----|----|----|----|----|----|----|

| bit symbol  | -  | -  | -  | -  | -  | -  | -  | -  |

| After reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|             | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| bit symbol  | -  | -  | -  | -  | -  | -  | -  | -  |

| After reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|             | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| bit symbol  | -  | -  | -  | -  | -  | -  | МС | DE |

| After reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 7           | 0  | 0  | Ŭ  | 0  | 0  | 0  | •  | ő  |

|             | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| bit symbol  |    | -  | -  |    |    |    | 1  | -  |

1.2.2 SAMCR(Control register)

TOSHIBA

| Bit   | Bit Symbol | Туре | Function                                      |

|-------|------------|------|-----------------------------------------------|

| 31-10 | -          | R    | "0" can be read.                              |

| 9-7   | MODE[2:0]  | R/W  | Operation mode settings                       |

|       |            |      | 000 : Sample mode 0                           |

|       |            |      | 001 : Sample mode 1                           |

|       |            |      | 010 : Sample mode 2                           |

|       |            |      | 011 : Sample mode 3                           |

|       |            |      | The settings other than those above: Reserved |

| 6-0   | TDATA[6:0] | W    | Transmitted data                              |

Note) The Type is divided into three as shown below.

| R / W | READ WRITE |

|-------|------------|

| R     | READ       |

| W     | WRITE      |

c. Data description

Meanings of symbols used in the SFR description are as shown below.

- x: channel numbers/ports

- n, m: bit numbers

- d. Register descriptions

Registers are described as shown below.

Register name <Bit Symbol>

Example: SAMCR<MODE>="000" or SAMCR<MODE[2:0]>="000"

<MODE[2:0]> indicates bit 2 to bit 0 in bit symbol mode (3bit width).

• Register name [Bit]

Example: SAMCR[9:7]="000"

It indicates bit 9 to bit 7 of the register SAMCR (32 bit width).

## **Revision History**

| Date      | Revision | Comment          |

|-----------|----------|------------------|

| 2016/6/27 | 1        | First Release    |

| 2018/9/21 | 2        | Contents Revised |

# **Table of Contents**

### General precautions on the use of Toshiba MCUs

#### TMPM066FWUG TMPM067FWQG TMPM068FWXBG

| 1.1 | Featu   | ires                                                                               | 1 |

|-----|---------|------------------------------------------------------------------------------------|---|

| 1.2 | Bloc    | k Diagram                                                                          | 5 |

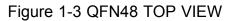

|     |         | Layout (Top view)                                                                  |   |

|     |         | names and Functions                                                                |   |

| 1.  | 4.1 Pin | names and Functions for each peripheral function, control pin and power supply pin | ) |

|     | 1.4.1.1 | Peripheral functions                                                               |   |

|     | 1.4.1.2 | Debug function                                                                     |   |

|     | 1.4.1.3 | Control function                                                                   |   |

|     | 1.4.1.4 | Power supply pins                                                                  |   |

| 1.  | 4.2 Pin | names and Function of TMPM066/067/068FW1                                           | l |

|     | 1.4.2.1 | The detail for pin names and function list                                         |   |

|     | 1.4.2.2 | PORT / Debug pin                                                                   |   |

|     | 1.4.2.3 | USB & Control pin                                                                  |   |

|     | 1.4.2.4 | Power Supply pin                                                                   |   |

|     |         |                                                                                    |   |

#### 2. Product Information

| 2.1 Information of Each Peripheral Function      |    |

|--------------------------------------------------|----|

| 2.1.1 DMA Controller (DMAC).                     |    |

| 2.1.1.1 DMA Request table                        |    |

| 2.1.2 16-bit Timer/Event Counter (TMRB)          |    |

| 2.1.3 16-bit Timer A (TMR16A)                    |    |

| 2.1.4 High Resolution 16-bit Timer (TMRD)        | 20 |

| 2.1.4.1 Clock setting for TMRD                   |    |

| 2.1.5 Serial Channel (SIO/UART)                  | 20 |

| 2.1.6 I2C Bus (I2C)                              | 21 |

| 2.1.7 Toshiba Serial Peripheral Interface (TSPI) |    |

| 2.1.8 Analog/Digital Converter (ADC)             | 21 |

| 2.1.9 USB Device (USBD)                          | 22 |

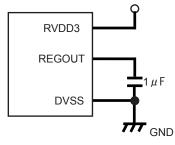

| 2.1.9.1 Reference Circuit                        |    |

| 2.1.10 Debug Interface                           | 22 |

#### 3. Processor Core

| 3.1   | Information on the processor core |    |

|-------|-----------------------------------|----|

| 3.2   | Configurable Options              | 23 |

|       | Exceptions/ Interruptions         |    |

|       | Number of Interrupt Inputs        |    |

|       | SysTick                           |    |

|       | SYSRESETREQ                       |    |

| 3.3.4 | LOCKUP                            |    |

| 3.4   | Events                            | 24 |

| 3.5   | Power Management                  | 24 |

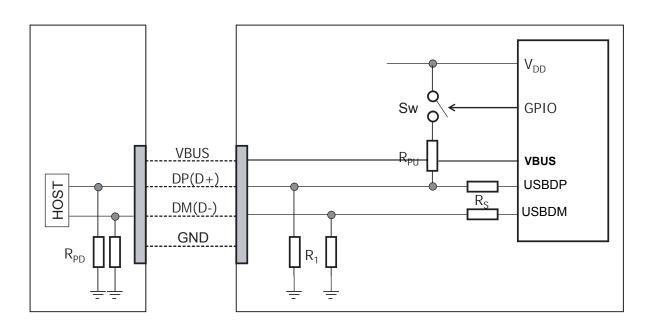

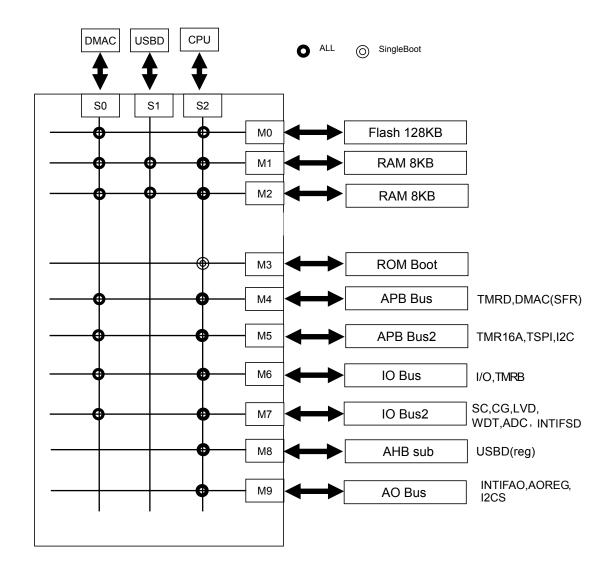

## 4. Memory Map

| 4.1  | Memory map                                                          | 27 |

|------|---------------------------------------------------------------------|----|

|      | Bus Matrix                                                          |    |

| 4.2. | 1 Structure                                                         | 30 |

| 4    | 1.2.1.1 Single chip mode, Single boot mode                          |    |

| 4.2. | 2 Connection table                                                  | 31 |

|      | 4.2.2.1     Code area / SRAM area       4.2.2.2     Peripheral area |    |

|      | 3 Address lists of peripheral functions                             | 33 |

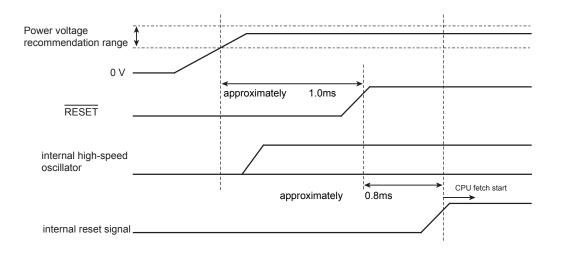

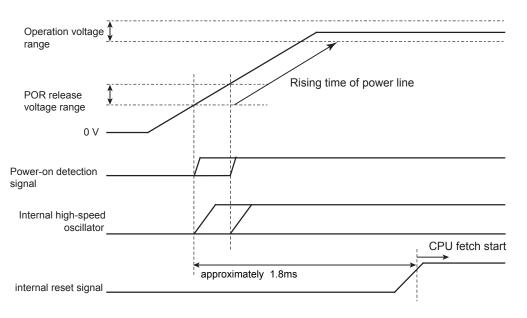

## 5. Reset Operation

| 5.1 | Cold Reset                               | 36 |

|-----|------------------------------------------|----|

|     | Cold Reset by RESET pin                  |    |

|     | 2 Cold Reset with power-on-reset circuit |    |

| 5.2 | Warm Reset                               | 37 |

| 5.3 | After reset                              | 37 |

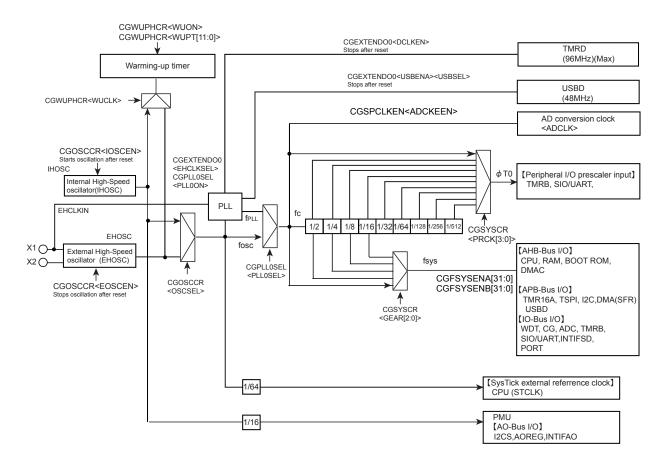

### 6. Clock/Mode control

| 6.1            | Features                                                      |           |

|----------------|---------------------------------------------------------------|-----------|

| 6.2            | Registers                                                     | 40        |

| 6.2.1          | 8                                                             |           |

| 6.2.2          |                                                               |           |

| 6.2.3          |                                                               |           |

| 6.2.4          |                                                               |           |

| 6.2.5          |                                                               |           |

| 6.2.6          |                                                               |           |

| 6.2.7          |                                                               |           |

| 6.2.8          | 3 CGFSYSENA (fsys Clock on/off register A)                    |           |

| 6.2.9          | CGFSYSENB (fsys Clock on/off register B)                      |           |

| 6.2.1          | 10 CGSPCLKEN (ADC Clock on/off register)                      |           |

| 6.2.1          | 11 CGEXTENDO0 (Optional function setting register)            |           |

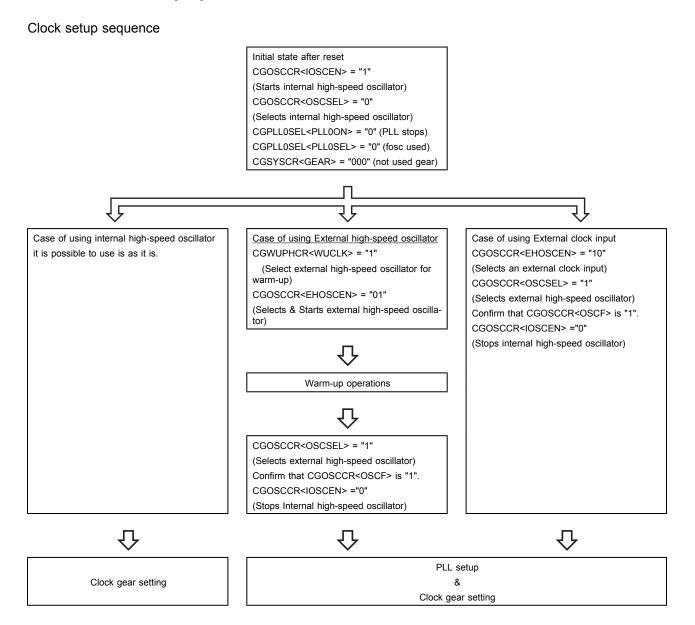

| 6.3            | Clock control                                                 |           |

| 6.3.1          |                                                               |           |

| 6.3.2          | 51                                                            |           |

| 6.3.3          |                                                               |           |

| 6.3.4          |                                                               |           |

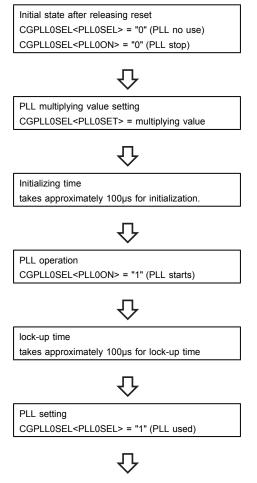

| 6.             | 3.4.1 Operation start                                         |           |

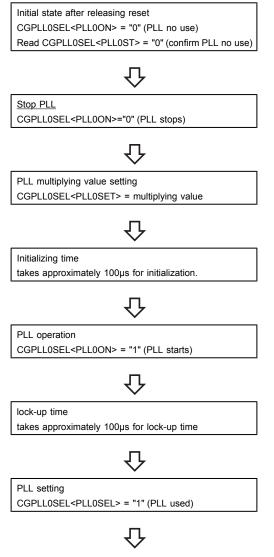

|                | 3.4.2 Changed the multiplication                              |           |

|                | 3.4.3 The sequence of PLL setting                             |           |

|                | 3.4.4 The sequence of PLL setting (Changed multiplying value) | <b>57</b> |

| 6.3.5<br>6.3.6 |                                                               |           |

| 6.3.7          |                                                               |           |

|                | e                                                             |           |

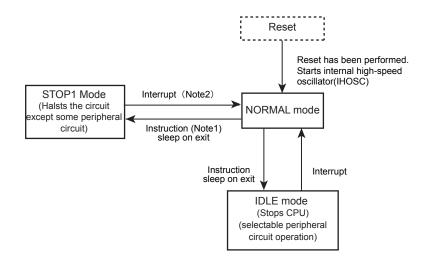

|                | Modes and Mode Transitions                                    |           |

| 6.4.1          |                                                               |           |

| 6.4.2          |                                                               |           |

| 6.5            | Operation mode                                                | 61        |

| 6.5.1          | NORMAL mode                                                   | 61        |

| 6.6            | Low Power Consumption Modes                                   | 61        |

| 6.6.1          |                                                               |           |

| 6.6.2          |                                                               |           |

| 6.6.3          |                                                               |           |

| 6.6.4          | 4 Operational Status in Each Mode                             |           |

| 6.6.5          | Releasing the Low Power Consumption Mode                      |           |

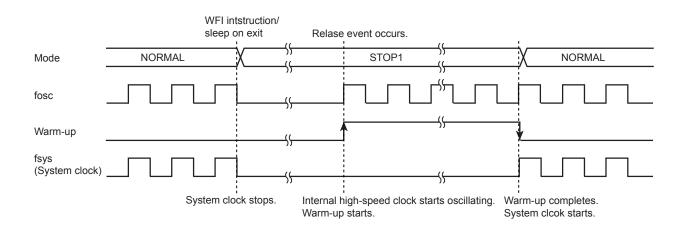

| 6. | 6.6 | Warm-up                                                                            |

|----|-----|------------------------------------------------------------------------------------|

|    |     | Clock Operations in Mode Transition                                                |

|    |     | 7.1 Transition of operation modes: NORMAL $\rightarrow$ STOP1 $\rightarrow$ NORMAL |

## 7. Exceptions

| 7.1 Overview                                                                              |                                                   | 69  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------|-----|

| 7.1.1 Exception Types                                                                     |                                                   | 69  |

| 1 51                                                                                      |                                                   |     |

| 7.1.2.1 Exception Request and Detection                                                   |                                                   |     |

| 7.1.2.2 Exception Handling and Branch to the                                              | he Interrupt Service Routine (Pre-emption)        |     |

| 7.1.2.3 Executing an ISR                                                                  |                                                   |     |

| 7.1.2.4 Exception exit                                                                    |                                                   |     |

| 7.2 Reset Exceptions                                                                      |                                                   | 75  |

| 7.3 Non-Maskable Interrupts (NM                                                           | MI)                                               | 76  |

| 7.4 SysTick                                                                               | · · · ·                                           | 76  |

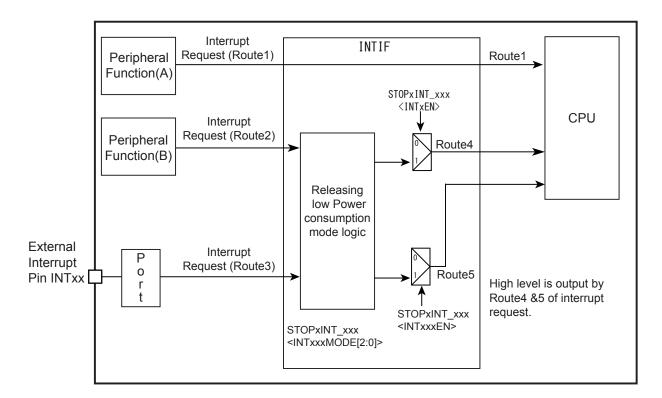

| 7.5 Interrupts                                                                            |                                                   |     |

| <b>A</b>                                                                                  |                                                   |     |

| 7.5.1.1 Interrupt Route                                                                   |                                                   |     |

| 7.5.1.2 Generation                                                                        |                                                   |     |

| 7.5.1.3 Transmission                                                                      |                                                   |     |

| 7.5.1.4 Precautions when using external inter                                             | errupt pins                                       |     |

| 7.5.1.5 List of Interrupt Sources                                                         |                                                   |     |

| 7.5.1.6 Active level                                                                      |                                                   |     |

| 7.5.1.7 Precautions on Clearing Low-power                                                 | Consumption Mode                                  |     |

| 7.5.1.8 Interrupt management numbers                                                      |                                                   |     |

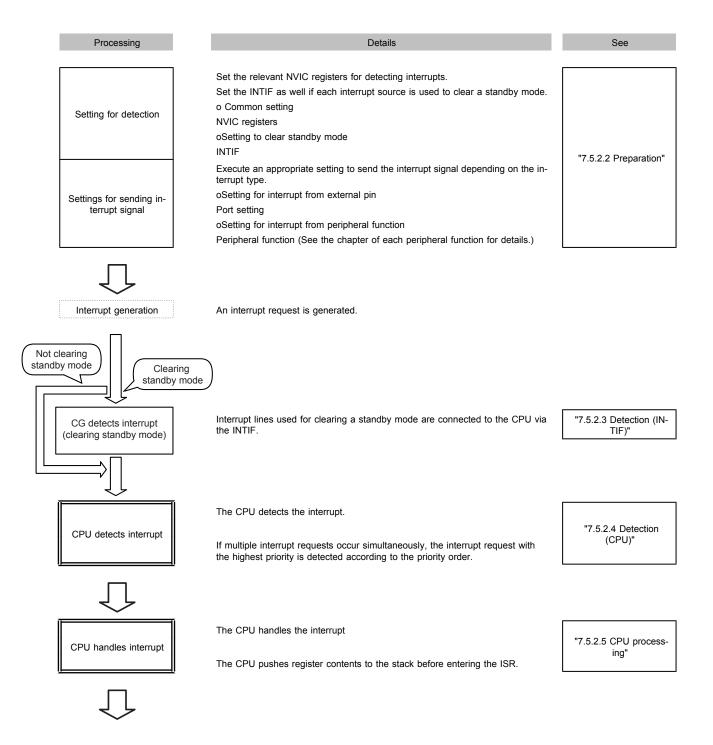

|                                                                                           |                                                   | 84  |

| 7.5.2.1 Flowchart                                                                         |                                                   |     |

| 7.5.2.2 Preparation                                                                       |                                                   |     |

| 7.5.2.3 Detection (INTIF)                                                                 |                                                   |     |

| 7.5.2.4 Detection (CPU)                                                                   |                                                   |     |

| 7.5.2.5 CPU processing                                                                    |                                                   |     |

| 7.5.2.6 Interrupt Service Routine (ISR)                                                   |                                                   |     |

|                                                                                           | Registers                                         |     |

|                                                                                           | -                                                 |     |

| 7.6.2 NVIC registers                                                                      |                                                   | 91  |

| 7.6.2.1 SysTick Control and Status Register                                               |                                                   |     |

| 7.6.2.2 SysTick Reload Value Register                                                     |                                                   |     |

| 7.6.2.3 SysTick Correct Value Register                                                    |                                                   |     |

| 7.6.2.4 SysTick Calibration Value Register                                                |                                                   |     |

| 7.6.2.5 Interrupt Set-Enable Register 1                                                   |                                                   |     |

| 7.6.2.6 Interrupt Clear-Enable Register 1                                                 |                                                   |     |

| 7.6.2.7 Interrupt Set-Pending Register 1                                                  |                                                   |     |

| 7.6.2.8 Interrupt Clear-Pending Register 1                                                |                                                   |     |

| 7.6.2.9 Interrupt Priority Register<br>7.6.2.10 Application Interrupt and reset Com       | atral Pagistar                                    |     |

| 7.6.2.10 Application Interrupt and reset Con<br>7.6.2.11 System Handler Priority Register | inoi registei                                     |     |

| 7.6.2.11 System Handler Priority Register<br>7.6.2.12 System Handler Control and State F  | Register                                          |     |

|                                                                                           |                                                   | 102 |

|                                                                                           | for release from NMI, low-power consumption mode) | 102 |

| 7.6.3.2 RSTFLG (Reset flag register)                                                      | tor receise nom runn, tow-power consumption mode) |     |

| 7.6.3.3 INTFLAG (Interrupt monitor flag reg                                               | egister)                                          |     |

|                                                                                           | u /                                               |     |

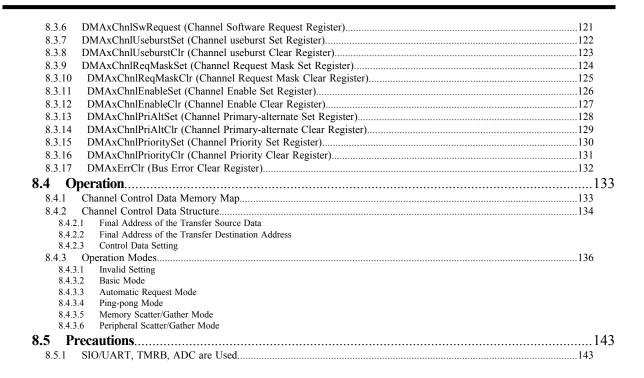

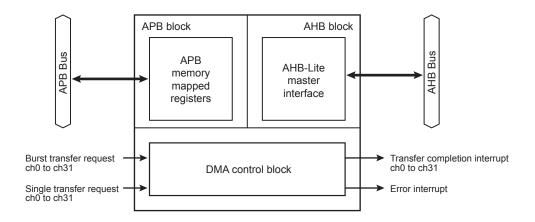

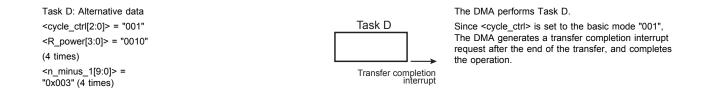

## 8. µDMA Controller (µDMAC)

| 8.1   | Overview                                                                    |  |

|-------|-----------------------------------------------------------------------------|--|

|       | Function List                                                               |  |

| 8.2   | Block Diagram                                                               |  |

|       | Registers                                                                   |  |

|       | Register List                                                               |  |

| 8.3.2 | 2 DMAxStatus (DMAC Status Register)                                         |  |

| 8.3.3 | 3 DMAxCfg (DMAC Configuration Register)                                     |  |

| 8.3.4 | DMAxCtrlBasePtr (Channel Control Data Base-pointer Register)                |  |

| 8.3.5 | 5 DMAxAltCtrlBasePtr (Channel Alternate Control Data Base-pointer Register) |  |

#### 9. Input/Output port

| 9.1 R | legisters                                       |  |

|-------|-------------------------------------------------|--|

| 9.1.1 | Register list                                   |  |

| 9.1.2 | Register list<br>Port function and setting list |  |

| 9.1.2 |                                                 |  |

| 9.1.2 | 2.2 PORT B                                      |  |

| 9.1.2 | 2.3 PORT C                                      |  |

| 9.1.2 | 2.4 PORT D                                      |  |

| 9.1.2 | 2.5 PORT E                                      |  |

| 9.1.2 | 2.6 PORT F                                      |  |

| 9.1.2 | 2.7 PORT G                                      |  |

| 9.1.2 | 2.8 PORT H                                      |  |

| 9.1.2 |                                                 |  |

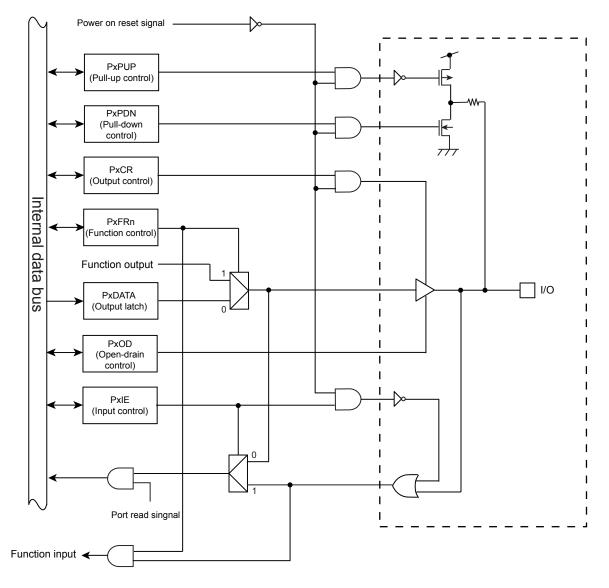

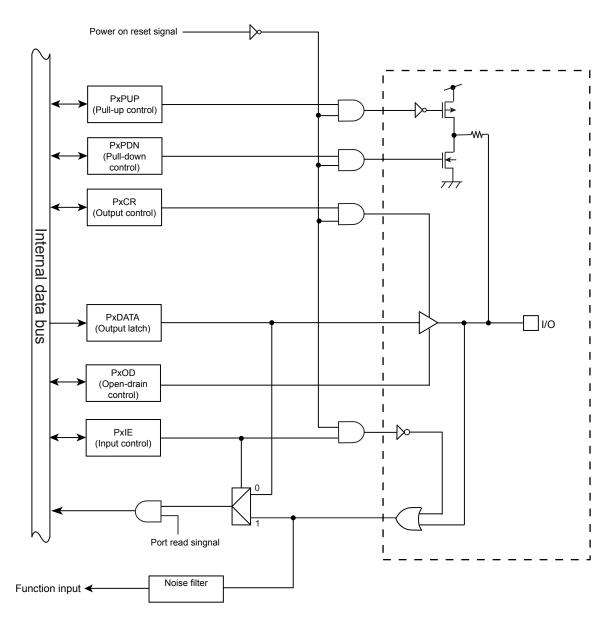

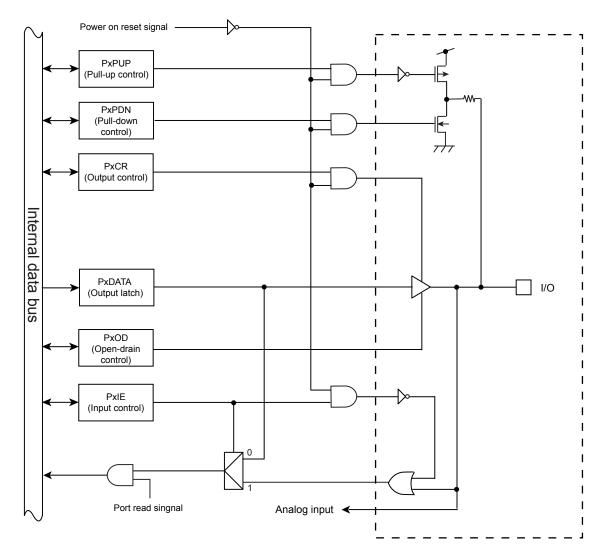

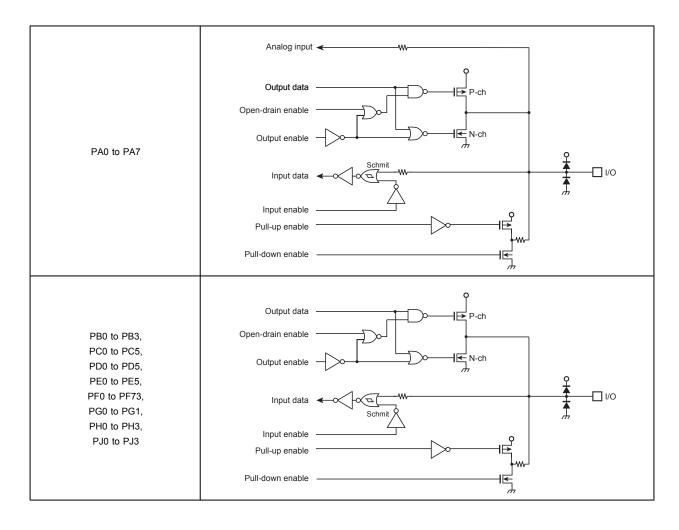

| 9.1.3 | Block Diagrams of Ports                         |  |

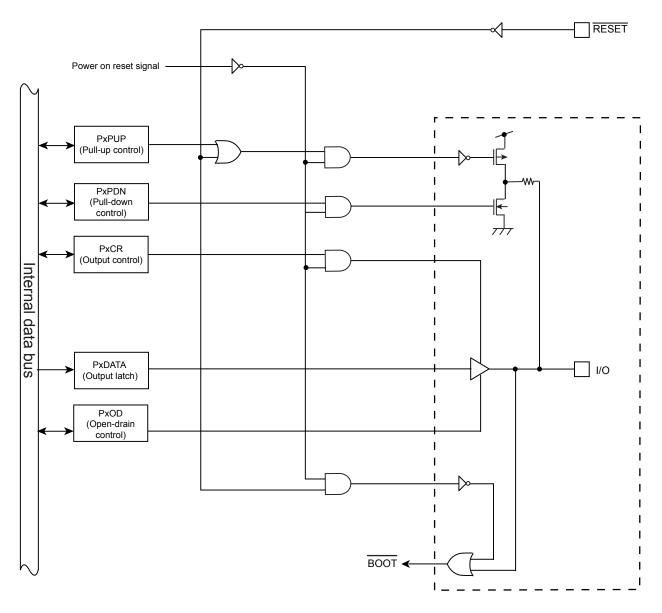

| 9.1.3 | 3.1 Port Type                                   |  |

| 9.1.3 | 3.2 Type FT1                                    |  |

| 9.1.3 | 3.3 Type FT4                                    |  |

| 9.1.3 | 3.4 Type FT5                                    |  |

| 9.1.3 | 3.5 Type FT6                                    |  |

#### 10. 16-bit Timer / Event Counters (TMRB)

| 10.1   | Outline                                                                         |     |

|--------|---------------------------------------------------------------------------------|-----|

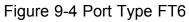

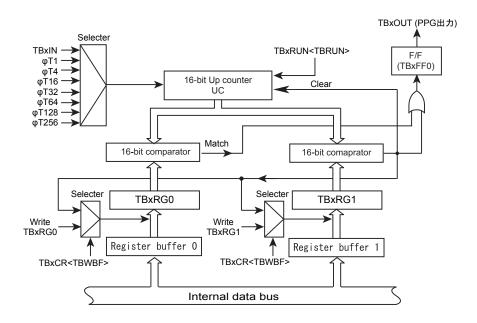

| 10.2   | Block Diagram                                                                   |     |

|        | Registers                                                                       |     |

| 10.3.1 | Register List                                                                   | 164 |

| 10.3.2 |                                                                                 | 165 |

| 10.3.3 | TBxRUN (RUN Register)                                                           |     |

| 10.3.4 |                                                                                 | 167 |

| 10.3.5 | TBxMOD (Mode Register)                                                          |     |

| 10.3.6 |                                                                                 | 170 |

| 10.3.7 | TBxST (Status Register)                                                         |     |

| 10.3.8 |                                                                                 | 172 |

| 10.3.9 | TBxUC (Up-counter Capture Register)                                             | 173 |

| 10.3.1 | TBxUC (Up-counter Capture Register).         0       TBxRG0 (Timer Register 0). | 174 |

| 10.3.11 | TBxRG1 (Timer Register 1)                                        |     |

|---------|------------------------------------------------------------------|-----|

| 10.3.12 | TBxCP0 (Capture register 0)                                      |     |

| 10.3.13 | TBxCP1 (Capture Register 1)                                      |     |

| 10.3.14 | TBxDMA(DMA request enable register)                              |     |

| 10.4 E  | Description of Operation                                         |     |

| 10.4.1  | Prescaler                                                        |     |

| 10.4.2  | Up-counter (UC)                                                  |     |

| 10.4.2  |                                                                  |     |

| 10.4.2  |                                                                  |     |

| 10.4.2  |                                                                  |     |

| 10.4.2  | op commence and a second                                         | 170 |

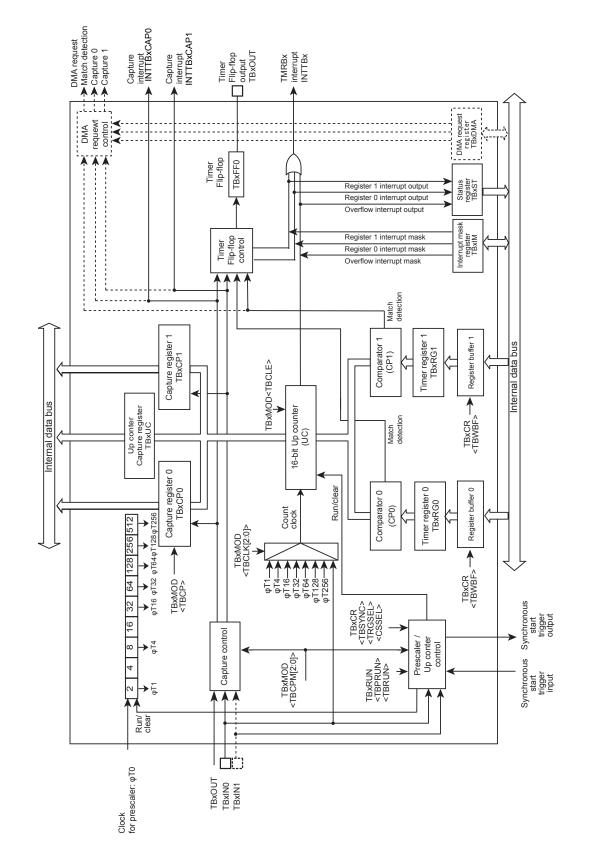

| 10.4.3  | Timer Registers (TBxRG0, TBxRG1)                                 |     |

| 10.4.4  | Capture Control                                                  |     |

| 10.4.5  | Capture Registers (TBxCP0, TBxCP1)                               |     |

| 10.4.6  | Up-Counter Capture Register (TBxUC)                              |     |

| 10.4.7  | Comparators (CP0, CP1)                                           |     |

| 10.4.8  | Timer Flip-Flop (TBxFF0)                                         |     |

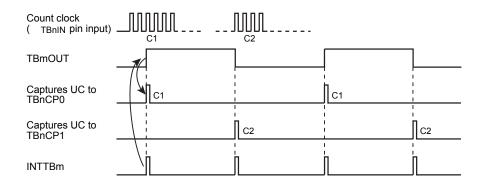

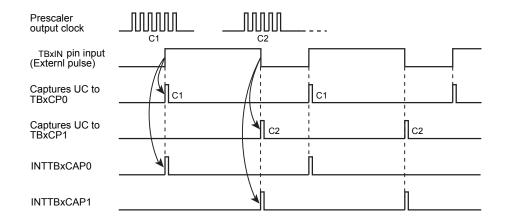

| 10.4.9  | Capture Interrupt (INTTBxCAP0, INTTBxCAP1)                       |     |

| 10.4.10 |                                                                  |     |

| 10.5 L  | escription of Operation for each mode                            |     |

| 10.5.1  | Interval Timer Mode                                              |     |

| 10.5.2  | Event Counter Mode                                               |     |

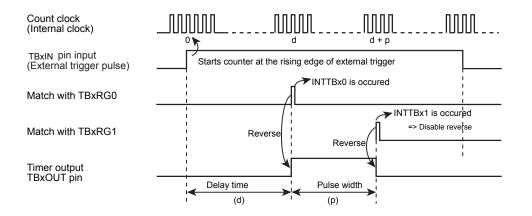

| 10.5.3  | Programmable Pulse Generation (PPG) Output Mode                  |     |

| 10.5.4  | Programmable Pulse Generation (PPG) External Trigger Output Mode |     |

| 10.6 A  | Applications Using Capture Function                              |     |

| 10.6.1  | Frequency Measurement                                            |     |

| 10.6.2  | Pulse Width Measurement                                          |     |

|         |                                                                  |     |

## 11. 16-Bit Timer A (TMR16A)

| 11.1 0  | utline                       |     |

|---------|------------------------------|-----|

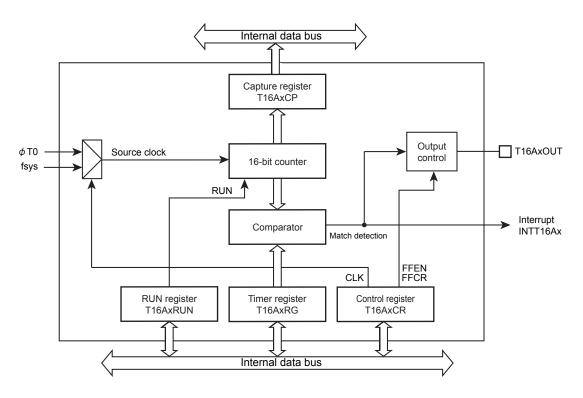

| 11.2 B  | lock Diagram                 |     |

|         | egisters                     |     |

| 11.3.1  | Register List                |     |

|         | 1 T16AxEN (Enable Register)  |     |

| 11.3.1. | 2 T16AxRUN (RUN Register)    |     |

| 11.3.1. | 3 T16AxCR (Control Register) |     |

| 11.3.1. | 4 T16AxRG (Timer Register)   |     |

|         | 5 T16AxCP (Capture Register) |     |

| 11.4 O  | peration Description         |     |

| 11.4.1  | Timer Operation              | 194 |

| 1142    | T16AxOUT Control             | 194 |

| 11.4.3  | Read Capture                 |     |

| 11.4.4  | Automatic Stop               |     |

## **12.** High Resolution 16-bit Timer (TMRD ver.C)

| 12.1 Outline                         |     |

|--------------------------------------|-----|

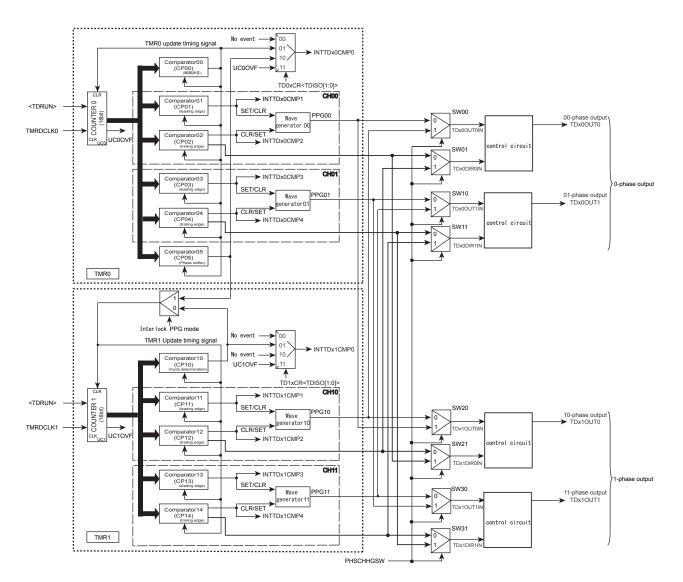

| 12.2 Configuration                   |     |

| 12.2.1 Timer Unit                    |     |

| 12.2.1.1 Block Diagram of Timer Unit |     |

| 12.3 Registers                       | 199 |

| 12.3.1 Register List                 |     |

| 12.3.1.1 Register List (TMRD)        |     |

| 12.4 Operation Description           |     |

| 12.4.1 Prescaler Clock               |     |

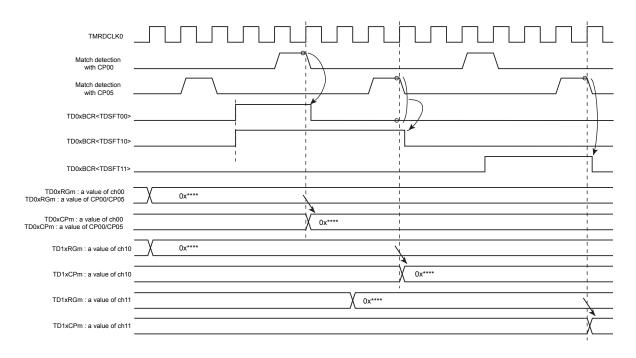

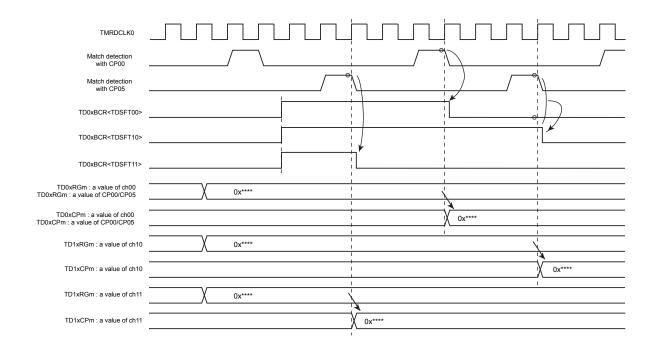

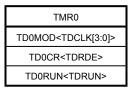

| 12.4.2 Timer Unit (TMR0, TMR1)       |     |

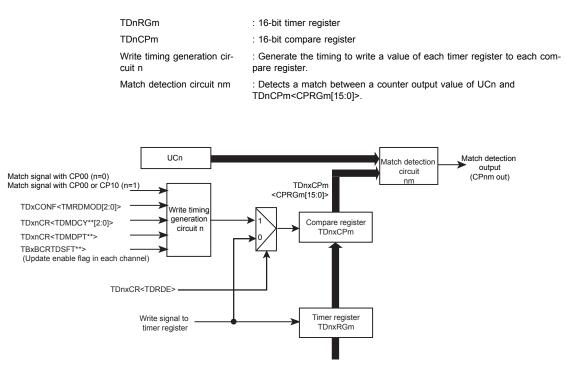

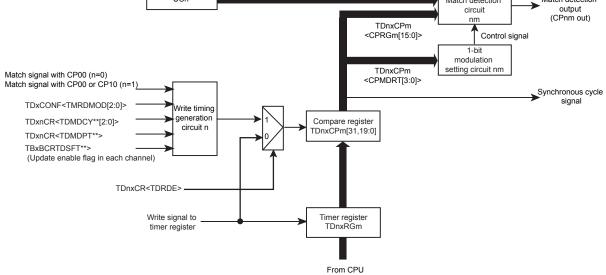

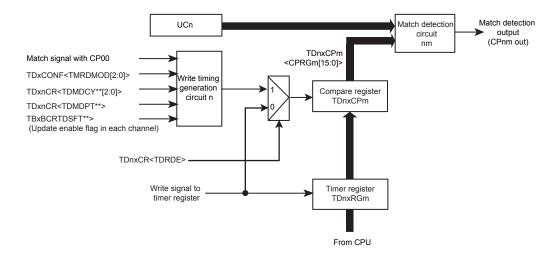

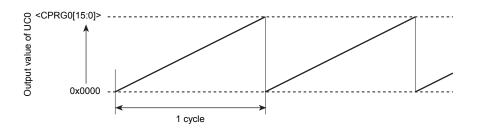

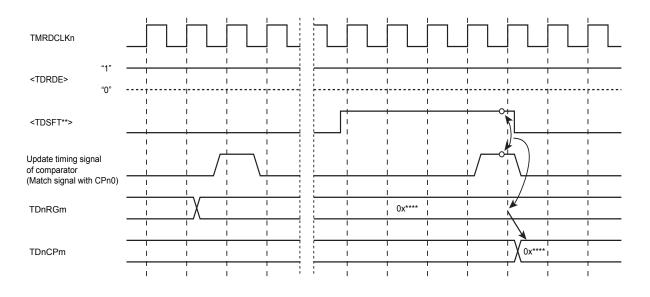

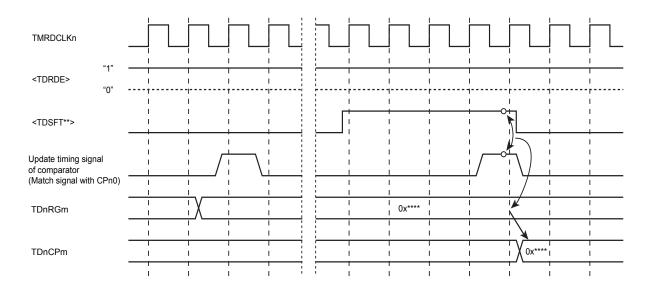

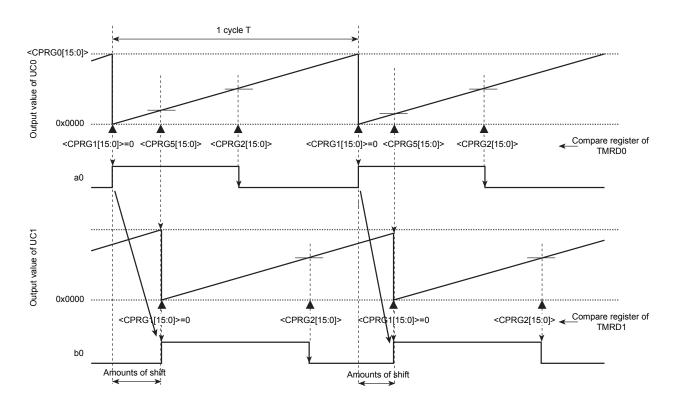

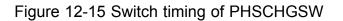

| 12.4.2.1 Counter (UCn)               |     |

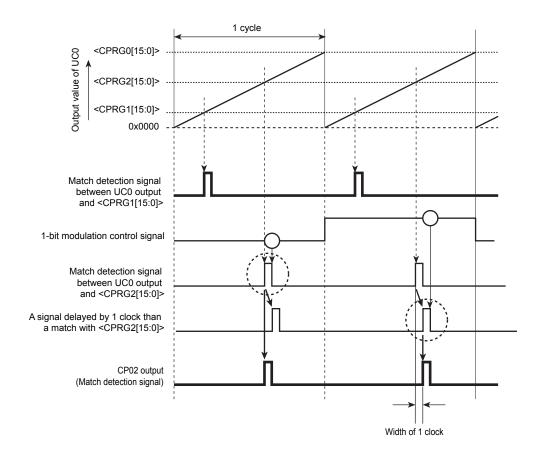

| 12.4.2.2 Comparator (CPnm)           |     |

| 12.4.2.3 Output Channel (CHn0, CHn1) |     |

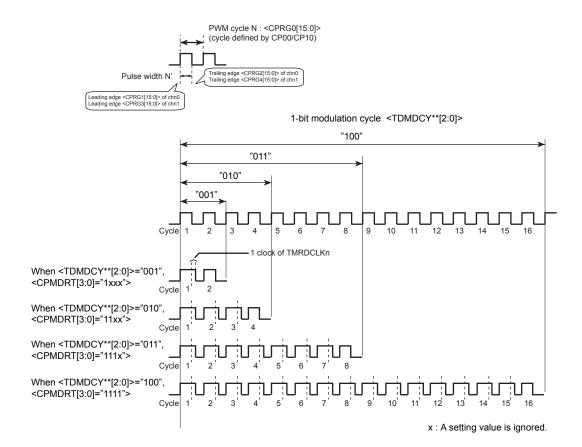

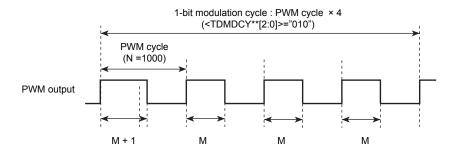

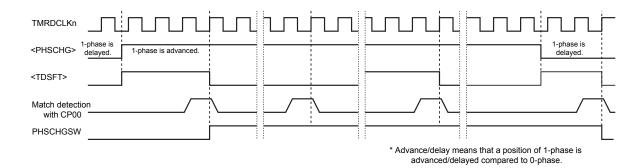

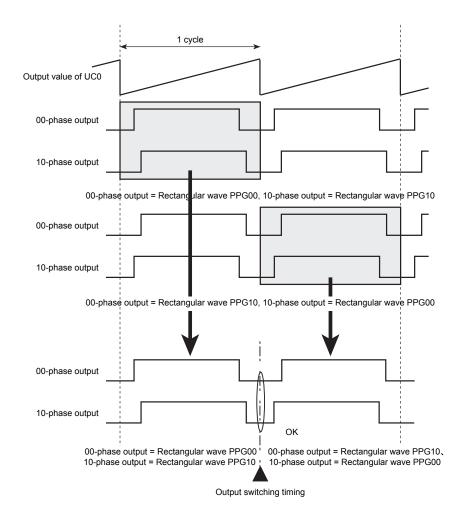

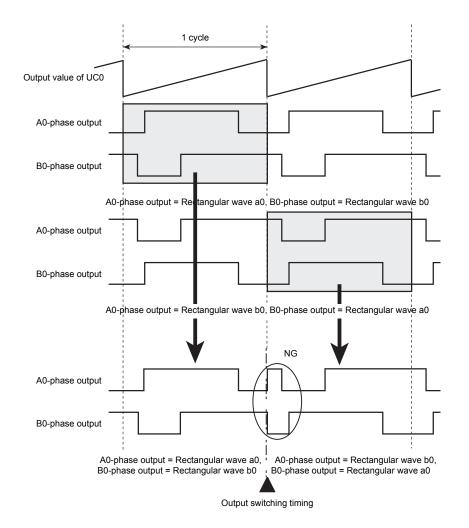

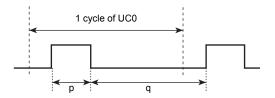

| 12.5 Each Operation Mode Description                      |     |

|-----------------------------------------------------------|-----|

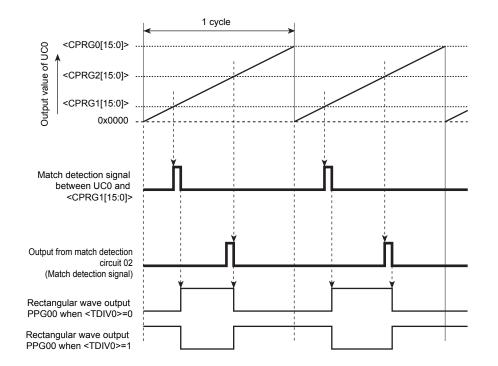

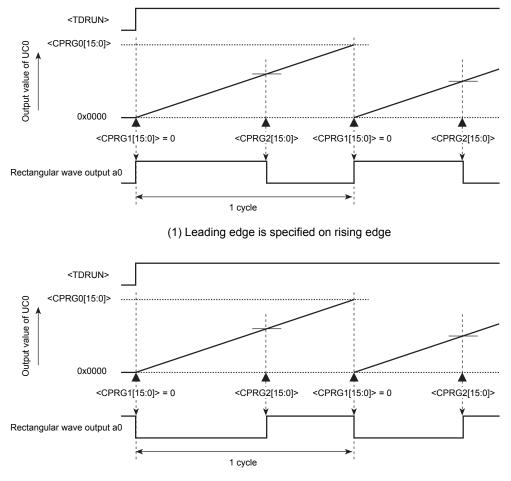

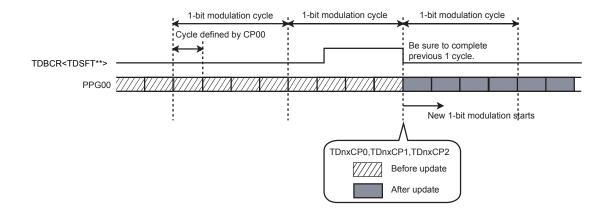

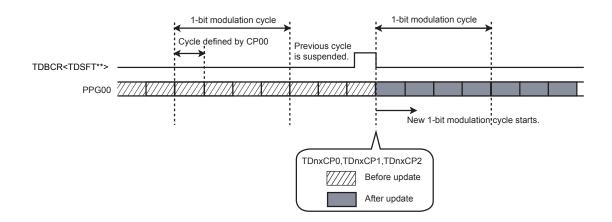

| 12.5.1 16-bit Programmable Rectangular Pulse Output (PPG) |     |

| 12.5.1.1 PPG mode                                         |     |

| 12.5.1.2 Interlock PPG Mode                               |     |

| 12.5.1.3 Setting Range of Compare Register                |     |

| 12.5.2 Each Operation Mode and Interrupts                 | 243 |

## 13. Serial Channel with 4bytes FIFO (SIO/UART)

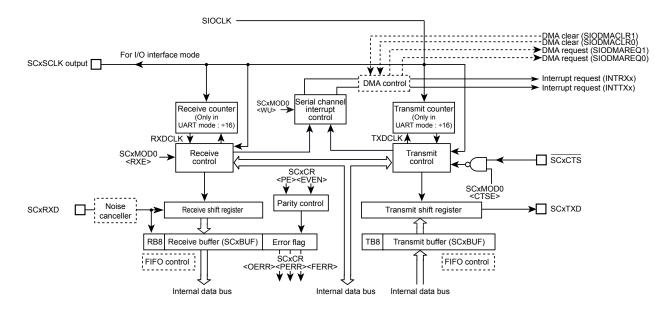

| 13.1 Overview                                                           |     |

|-------------------------------------------------------------------------|-----|

| 13.2 Configuration                                                      |     |

| 13.3 Registers Description.                                             |     |

| 13.3.1 Registers List                                                   |     |

| 13.3.2 SCxEN (Enable Register)                                          |     |

| 13.3.3 SCxBUF (Buffer Register)                                         |     |

| 13.3.4 SCxCR (Control Register)                                         |     |

| 13.3.5 SCxMOD0 (Mode Control Register 0)                                |     |

| 13.3.6 SCxMOD1 (Mode Control Register 1)                                |     |

| 13.3.7 SCxMOD2 (Mode Control Register 2)                                |     |

| 13.3.8 SCxBRCR (Baud Rate Generator Control Register)                   |     |

| 13.3.9 SCxBRADD (Baud Rate Generator Control Register 2)                |     |

| 13.3.10 SCxFCNF (FIFO Configuration Register)                           |     |

| 13.3.11 SCxRFC (Receive FIFO Configuration Register)                    |     |

| 13.3.12 SCxTFC (Transmit FIFO Configuration Register)                   |     |

| 13.3.13 SCxRST (Receive FIFO Status Register)                           |     |

| 13.3.14 SCxTST (Transmit FIFO Status Register)                          |     |

| 13.3.15 SCxDMA (DMA request enable register)                            |     |

| 13.4 Operation in Each Mode                                             |     |

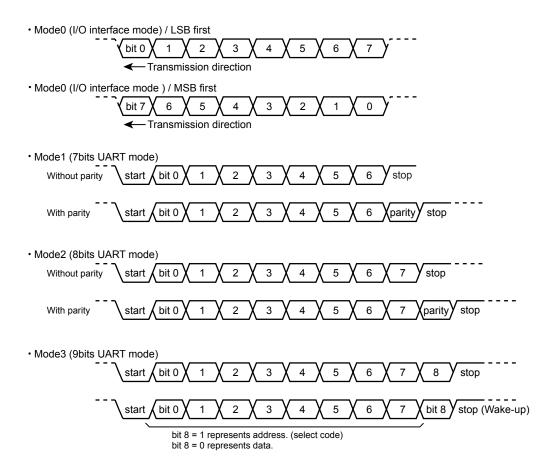

| 13.5 Data Format                                                        | 266 |

| 13.5.1 Data Format List                                                 |     |

| 13.5.2 Parity Control                                                   |     |

| 13.5.2.1 Transmission                                                   |     |

| 13.5.2.2 Receiption                                                     |     |

| 13.5.3 STOP Bit Length                                                  |     |

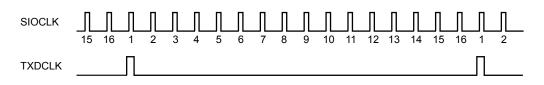

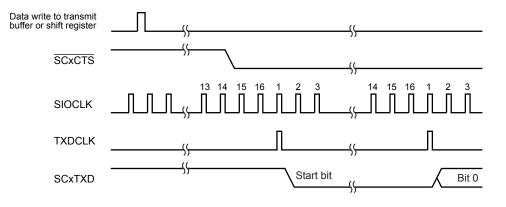

| 13.6 Clock Control                                                      |     |

| 13.6.1 Prescaler                                                        |     |

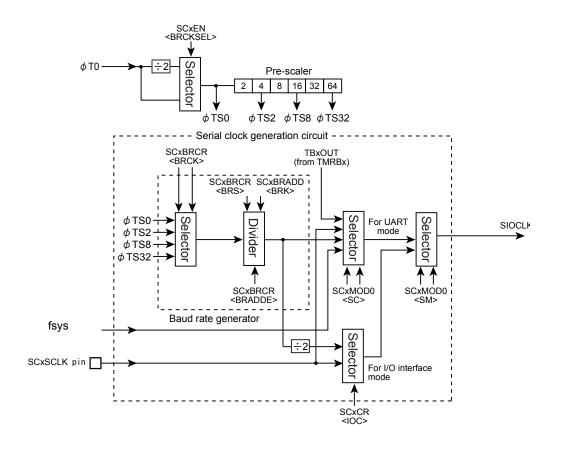

| 13.6.2 Serial Clock Generation Circuit                                  |     |

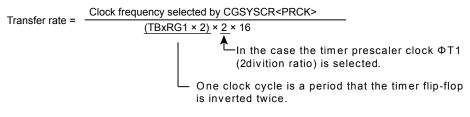

| 13.6.2.1 Baud Rate Generator                                            |     |

| 13.6.2.2 Clock Selection Circuit                                        |     |

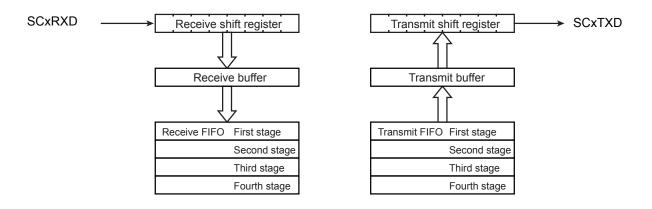

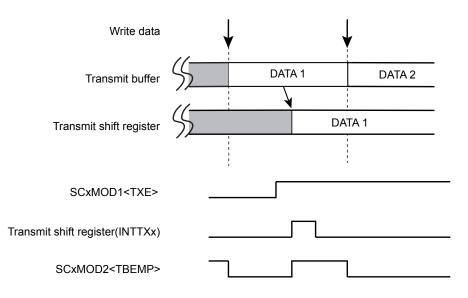

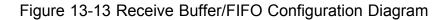

| 13.6.3 Transmit/Receive Buffer and FIFO                                 | 272 |

| 13.6.3.1 Configuration                                                  |     |

| 13.6.3.2 Transmit/Receive Buffer<br>13.6.3.3 Initialize Transmit Buffer |     |

| 13.6.3.4 FIFO                                                           |     |

| 13.7 Status Flag                                                        | 274 |

|                                                                         |     |

| 13.8 Error Flag                                                         |     |

| 13.8.1 OERR Flag                                                        |     |

| 13.8.2 PERR Flag                                                        |     |

| 13.8.3 FERR Flag                                                        |     |

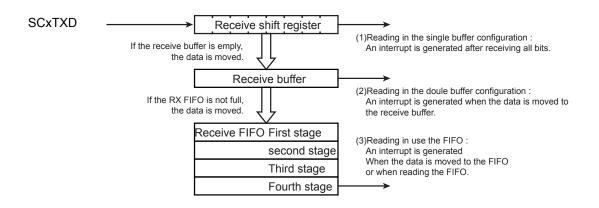

| 13.9 Receive                                                            |     |

| 13.9.1 Receive Counter                                                  |     |

| 13.9.2 Receive Control Unit                                             |     |

| 13.9.2.1 I/O interface mode                                             |     |

| 13.9.2.2 UART Mode<br>13.9.3 Receive Operation                          |     |

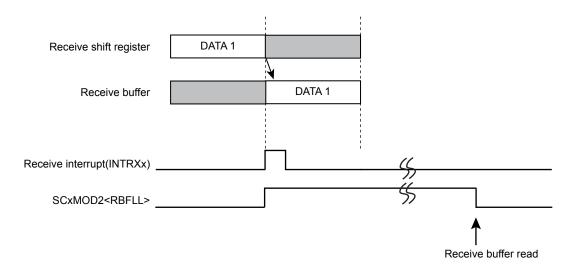

| 13.9.3 Receive Operation<br>13.9.3.1 Receive Buffer                     |     |

| 13.9.3.2 Receive FIFO Operation                                         |     |

| 13.9.3.3 I/O interface mode with clock output mode                      |     |

| 13.9.3.4 Read Received Data                                             |     |

| 13.9.3.5 Wake-up Function                                               |     |

| 13.9.3.6 Overrun Error                                                  |     |

| 13.10 Transmit                                                          |     |

| 13.10.1 Transmit Counter                                                |     |

| 13.10.2 Transmit Control                                                                              |     |

|-------------------------------------------------------------------------------------------------------|-----|

| 13.10.2.1 In I/O Interface Mode                                                                       |     |

| 13.10.2.2 In UART Mode                                                                                |     |

| 13.10.3 Transmit Operation                                                                            |     |

| 13.10.3.1 Operation of Transmit Buffer                                                                |     |

| 13.10.3.2 Transmit FIFO Operation                                                                     |     |

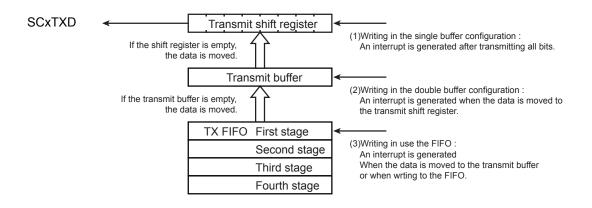

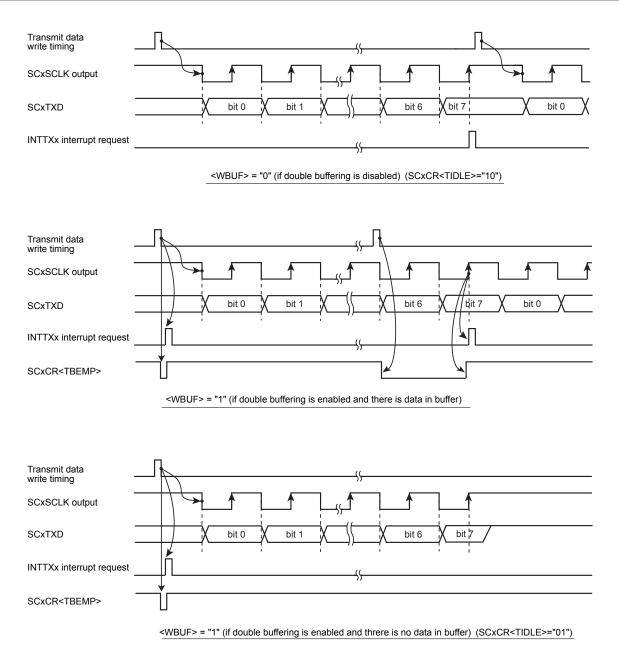

| 13.10.3.3 Transmit in I/O interface Mode with Clock Output Mode                                       |     |

| 13.10.3.4 Level of SCxTXD pin after the last bit is output in I/O interface mode                      |     |

| 13.10.3.5 Under-run error<br>13.10.3.6 Data Hold Time In the I/O interface mode with clock input mode |     |

| 1                                                                                                     | 005 |

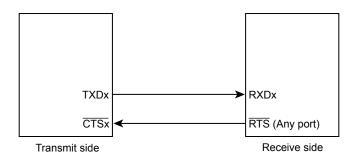

| 13.11 Handshake function                                                                              |     |

| 13.12 Interrupt/Error Generation Timing                                                               |     |

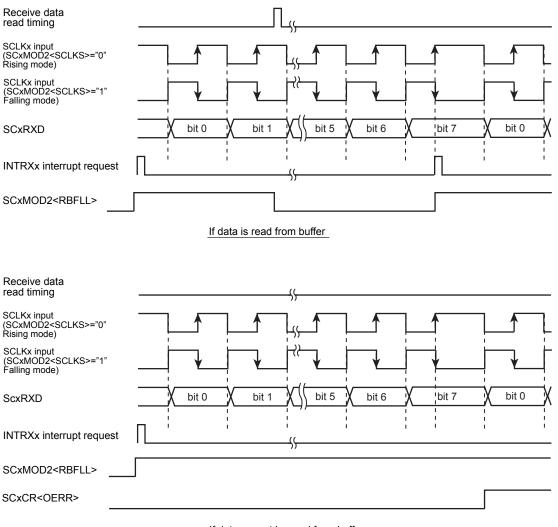

| 13.12.1 Receive Interrupts                                                                            |     |

| 13.12.1.1 Single Buffer / Double Buffer                                                               | 200 |

| 13.12.1.2 FIFO                                                                                        |     |

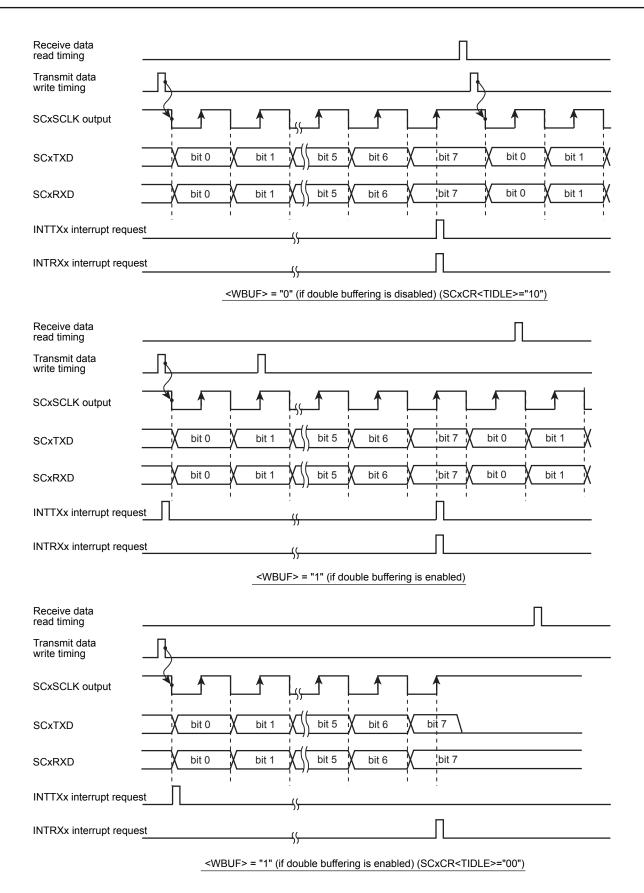

| 13.12.2 Transmit interrupts                                                                           |     |

| 13.12.2.1 Singe Buffer / Double Buffer                                                                |     |

| 13.12.2.2 FIFO                                                                                        |     |

| 13.12.3 Error Generation                                                                              |     |

| 13.12.3.1 UART Mode                                                                                   |     |

| 13.12.3.2 I/O Interface Mode                                                                          |     |

| 13.13 DMA Request                                                                                     |     |

| 13.14 Software Reset                                                                                  |     |

| 13.15 Operation in Each Mode                                                                          | 291 |

| 13.15.1 Mode 0 (I/O interface mode)                                                                   |     |

| 13.15.1 1 Transmit                                                                                    |     |

| 13 15 1.2 Receive                                                                                     |     |

| 13.15.1.3 Transmit and Receive (Full-duplex)                                                          |     |

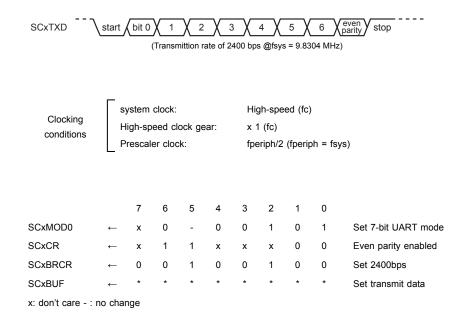

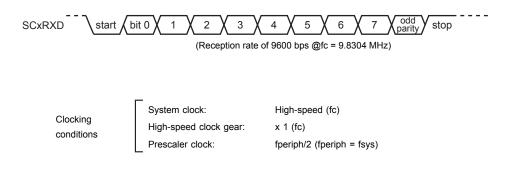

| 13.15.2 Mode 1 (7-bit UART mode)                                                                      | 302 |

| 13.15.3 Mode 2 (8-bit UART mode)                                                                      |     |

| 13.15.4 Mode 3 (9-bit UART mode)                                                                      |     |

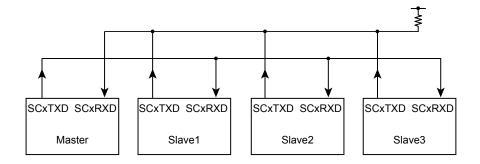

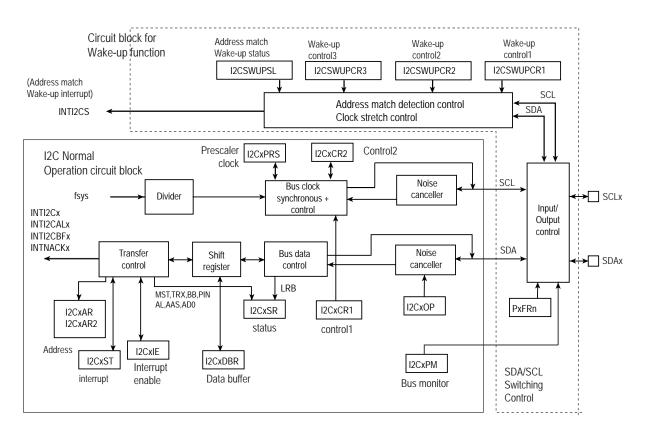

| 13.15.4.1 Wakeup function                                                                             |     |

| 13.15.4.2 Protocol                                                                                    |     |

|                                                                                                       |     |

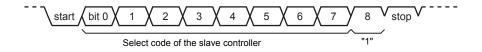

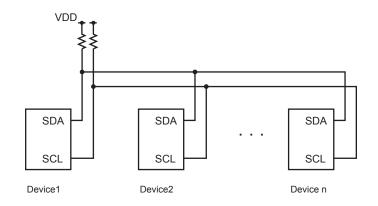

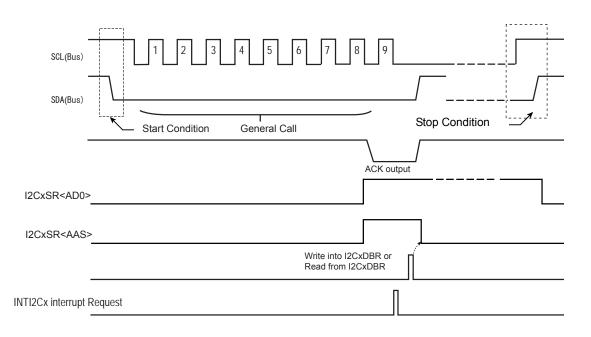

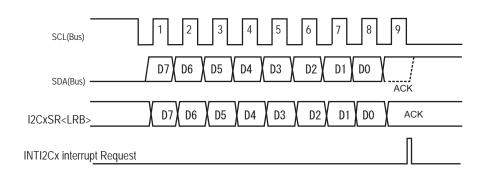

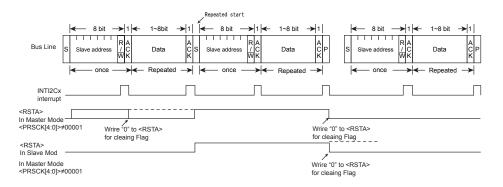

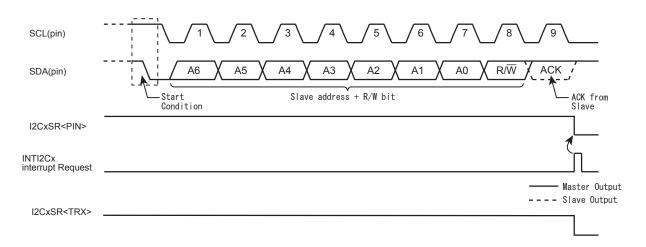

## 14. I2C Bus Interface

| 14.1 | Features                                                                |     |

|------|-------------------------------------------------------------------------|-----|

| 14.2 | Configuration                                                           |     |

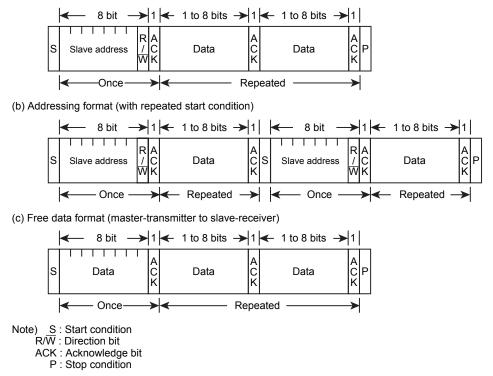

|      | .1 I2C Bus mode                                                         |     |

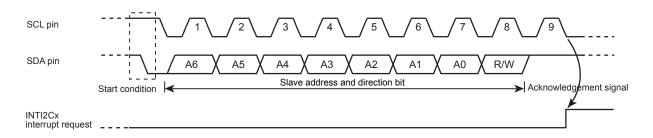

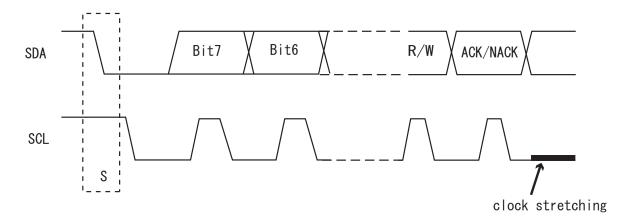

| 14   | 4.2.1.1 I2C Bus Mode Data Format                                        |     |

| 14.3 | Register                                                                |     |

| 14.3 | 0                                                                       |     |

| 14.3 | .2 I2CxCR1(Control register 1)                                          |     |

| 14.3 | .3 I2CxDBR (Serial bus interface data buffer register)                  |     |

| 14.3 |                                                                         |     |

| 14.3 | .5 I2CxCR2(Control register 2)                                          |     |

| 14.3 | .6 I2CxSR (Status Register)                                             |     |

| 14.3 | .7 I2CxPRS(Prescaler Clock setting register)                            |     |

| 14.3 | .8 I2CxIE(Interrupt Enable register)                                    |     |

| 14.3 | .9 I2CxST(I2C Interrupt status register)                                |     |

| 14.3 |                                                                         |     |

| 14.3 |                                                                         |     |

| 14.3 |                                                                         |     |

| 14.3 |                                                                         |     |

| 14.3 |                                                                         |     |

| 14.3 |                                                                         |     |

| 14.3 | .16 I2CSWUPSL(I2C status register)                                      |     |

| 14.4 | Function                                                                |     |

| 14.4 |                                                                         |     |

| 14.4 | .2 Setting the Number of Bits per Transfer and the Acknowledgement Mode |     |

| 14.4 |                                                                         |     |

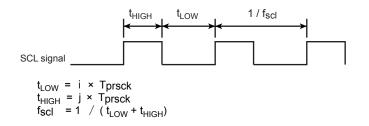

| •    | 4.4.3.1 Clock source                                                    |     |

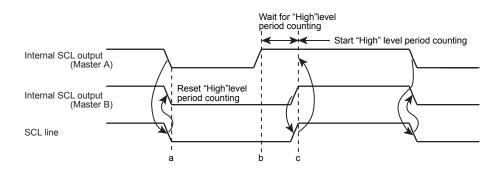

| -    | 4.4.3.2 Clock Synchronization                                           | 225 |

| 14.4 |                                                                         |     |

| 14.4 | .5 Configuring the I2C as a Transmitter or a Receiver                   |     |

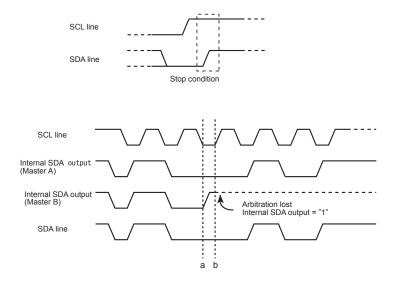

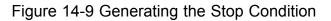

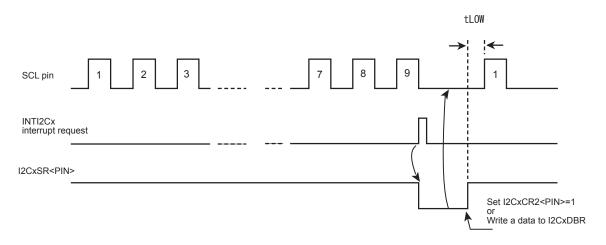

| 14.4.6  | Generating Start and Stop Conditions                     |  |

|---------|----------------------------------------------------------|--|

| 14.4.7  | Interrupt Service Request and Release                    |  |

| 14.4.8  | I2C Bus mode                                             |  |

| 14.4.9  | Software Reset                                           |  |

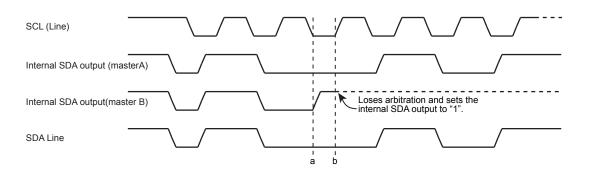

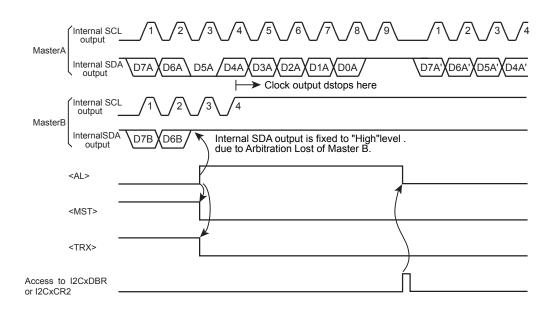

| 14.4.10 | Arbitration Lost Detection Monitor                       |  |

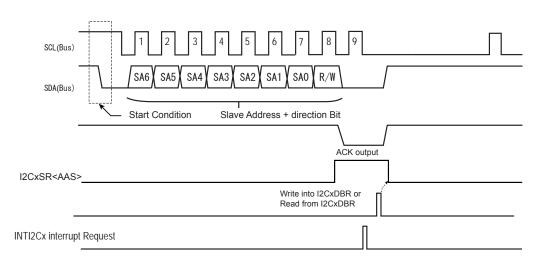

| 14.4.11 | Slave Address Match Detection Monitor                    |  |

| 14.4.12 | General-call Detection Monitor                           |  |

| 14.4.13 | Last Received Bit Monitor                                |  |

| 14.4.14 | Setting of Slave Addressing and Address Recognition Mode |  |

| 14.4.15 | Noise Cancellation                                       |  |

| 14.4.16 | Repeated START Detection                                 |  |

| 14.4.17 | DMA request output Control                               |  |

| 14.5 C  | ontrol in the I2C Bus Mode                               |  |

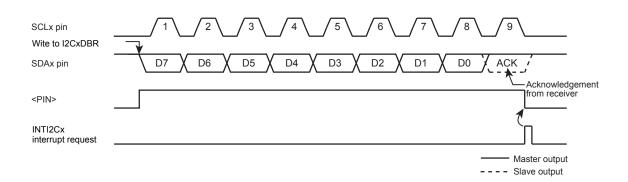

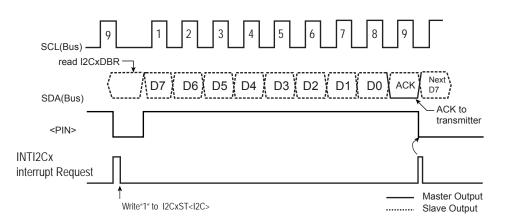

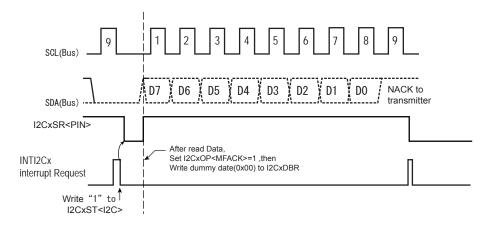

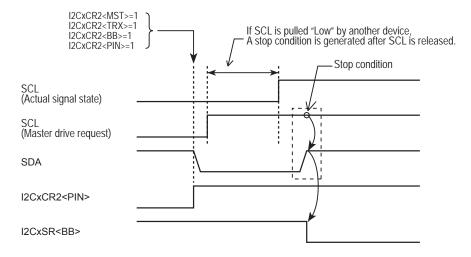

| 14.5.1  | Data Transfer Procedure in the I2C Bus Mode              |  |

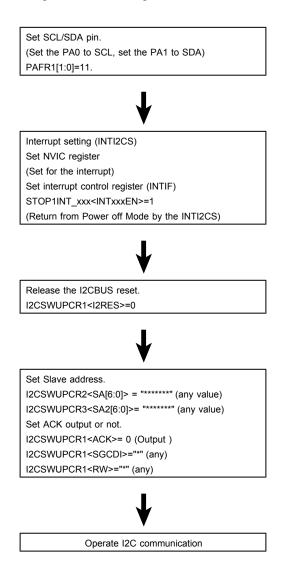

| 14.5.1. | 1 Device Initialization                                  |  |

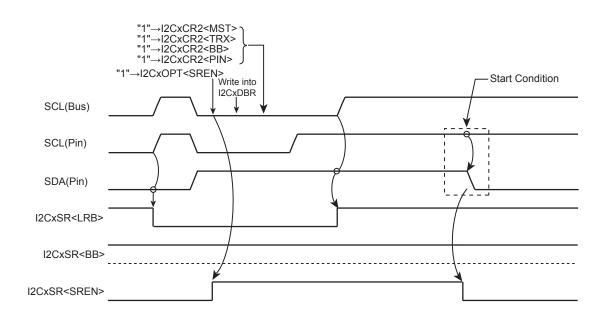

| 14.5.1. | 2 Generating the Start Condition and a Slave Address     |  |

| 14.5.1. |                                                          |  |

| 14.5.1. | Survey Survey Survey Street                              |  |

| 14.5.1. |                                                          |  |

| 14.5.1. |                                                          |  |

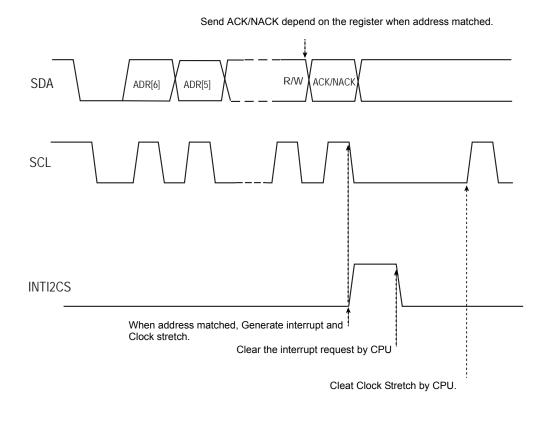

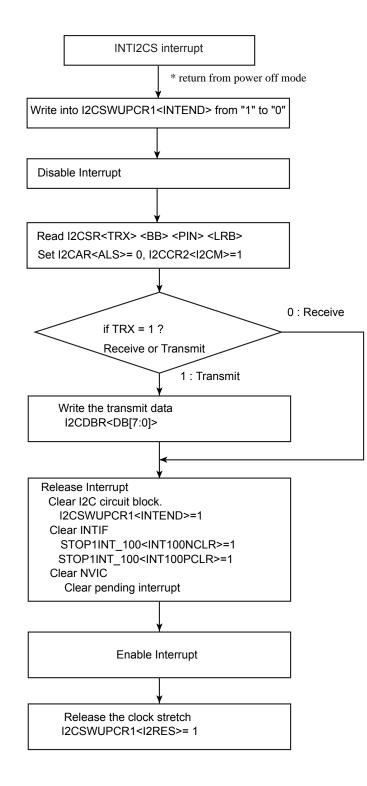

| 14.6 I2 | C Address Match Wake Up Function                         |  |

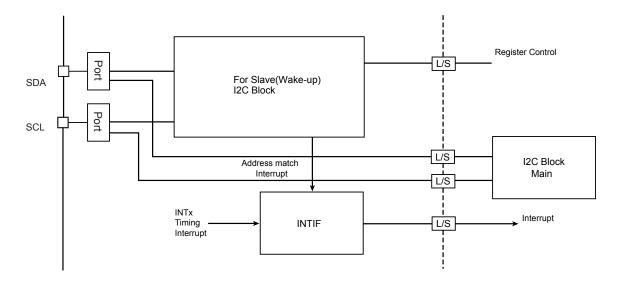

| 14.6.1  | Configuration                                            |  |

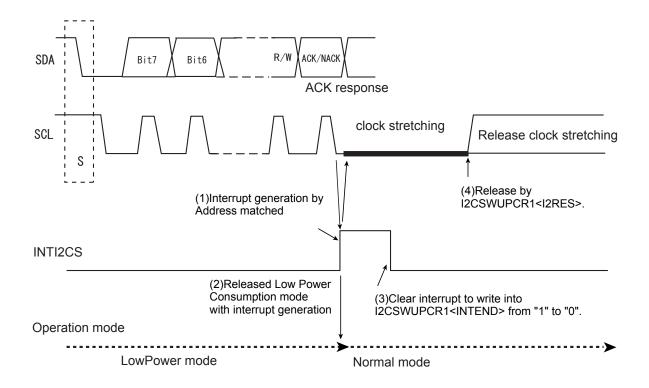

| 14.6.2  | Description of Operation                                 |  |

| 14.6.2. | 1 Clock Stretch Function                                 |  |

| 14.6.2. | - · · · · · · · · · · · · · · · · · · ·                  |  |

| 14.6.2. | 8                                                        |  |

| 14.6.2. | 4 Operation and setting flow (example)                   |  |

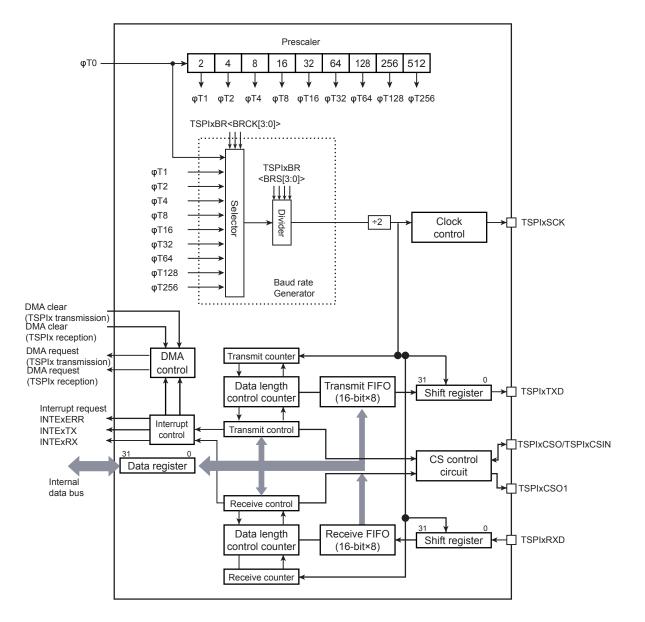

## 15. Toshiba Serial Peripheral Interface (TSPI)

| 15.1 Outline                                                                           |     |

|----------------------------------------------------------------------------------------|-----|

| 15.2 Block Diagram                                                                     |     |

| 15.3 Registers                                                                         |     |

| 15.3.1 Register List                                                                   |     |

| 15.3.2 TSPIxCR0 (TSPI Control Register 0)                                              |     |

| 15.3.3 TSPIXCR0 (TST1 Control Register 1)                                              |     |

| 15.3.4 TSPIxCR2 (TSPI Control Register 2)                                              |     |

| 15.3.5 TSPIxCR3 (TSPI Control Register 3)                                              |     |

| 15.3.6 TSPIxBR (TSPI Baud Rate Register)                                               |     |

| 15.3.7 TSPIxFMTR0 (TSPI Format Control Register 0)                                     |     |

| 15.3.8 TSPIXFMTR1 (TSPI Format Control Register 1)                                     |     |

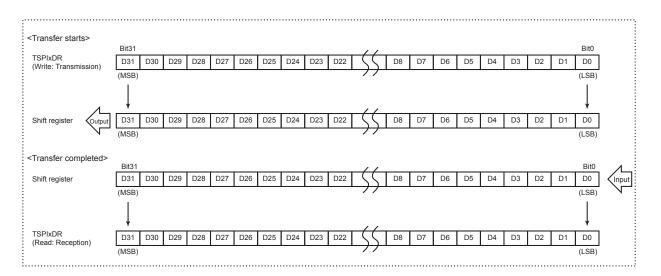

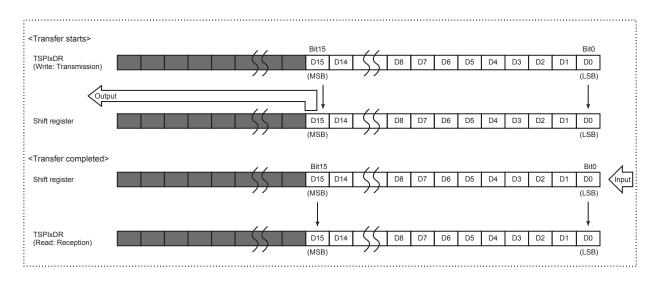

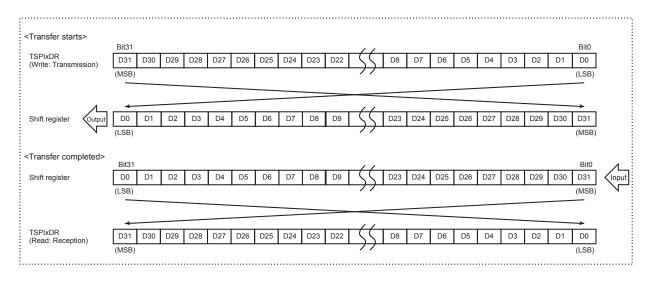

| 15.3.9 TSPIXDR (TSPI Data Register)                                                    |     |

| 15.3.10 TSPIxSR (TSPI Status Register)                                                 |     |

| 15.3.11 TSPIxERR (TSPI Error Flag Register)                                            |     |

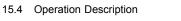

| 15.4 Operation Description                                                             |     |

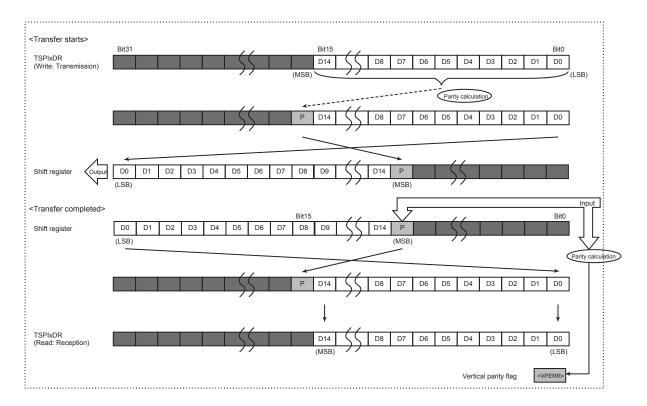

| 15.4.1 Data Format                                                                     |     |

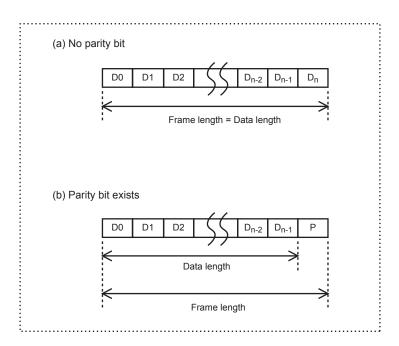

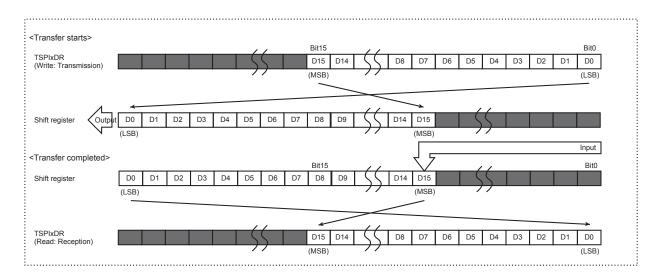

| 15.4.1.1 Data Format without Parity                                                    |     |

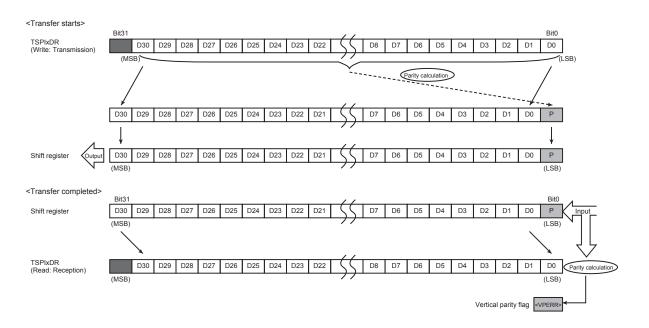

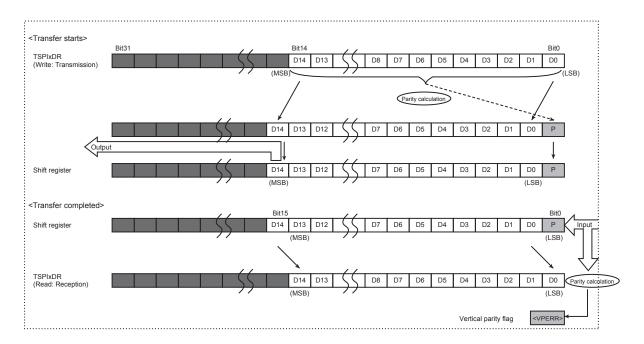

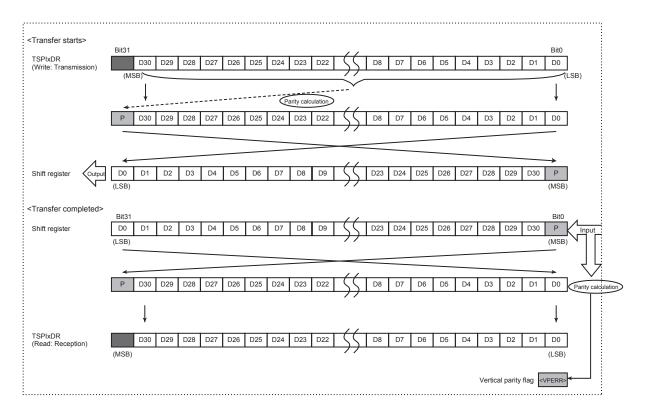

| 15.4.1.2 Data Format with a Parity Bit                                                 |     |

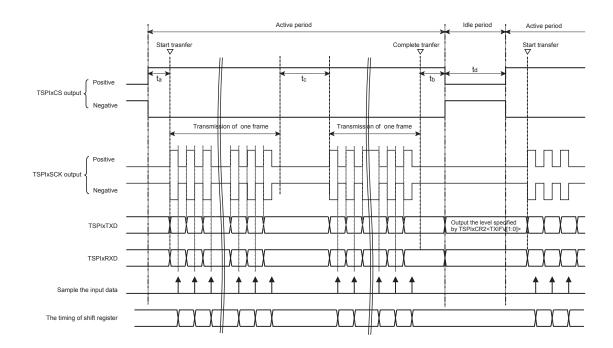

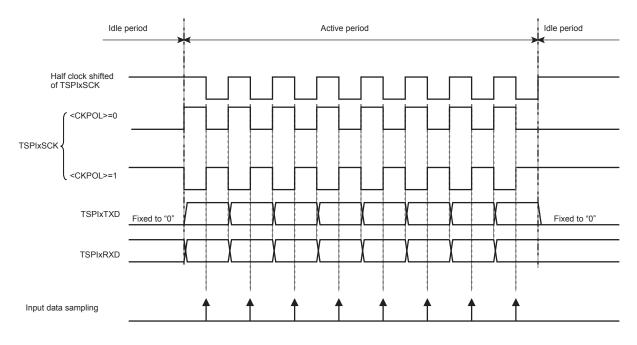

| 15.4.2 Transfer Format                                                                 | 381 |

| 15.4.2.1 Polarity of TSPIxCS Signal and Generation Timing                              |     |

| 15.4.2.2 Polarity of Clock                                                             |     |

| 15.4.2.3 TSPIxTXD Output during Idle                                                   |     |

| 15.4.3 Buffer Structure                                                                |     |

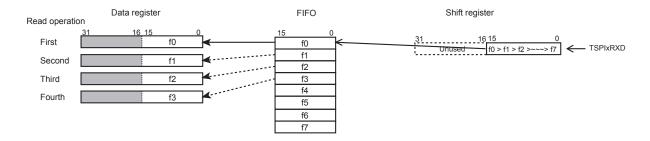

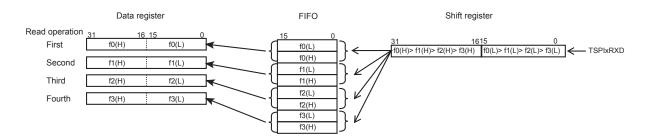

| 15.4.3.1 Data Length and FIFO Operation                                                |     |

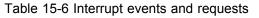

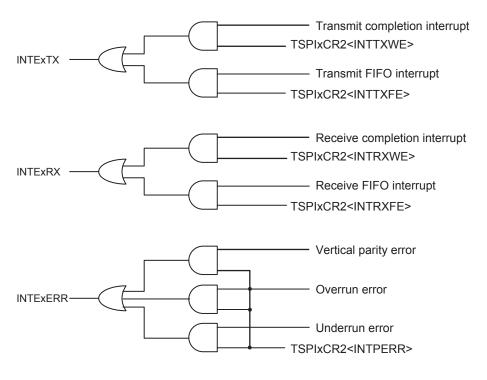

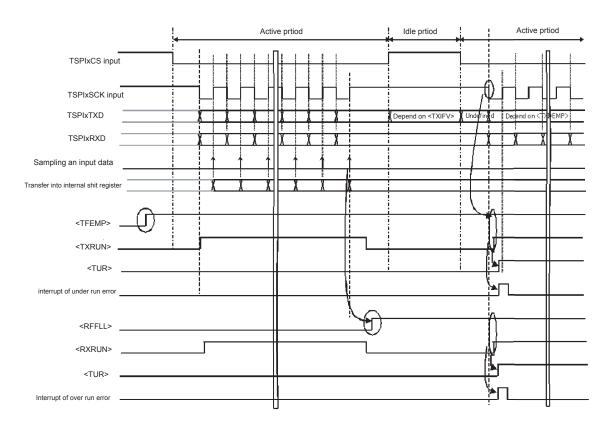

| 15.4.4 Interrupt Request                                                               |     |

| 15.4.4.1 Transmit Completion Interrupt/Receive Completion Interrupt                    |     |

| 15.4.4.2 Transmit FIFO Interrupt/Receive FIFO Interrupt<br>15.4.4.3 Error Interruption |     |

| 15.4.5 DMA Request                                                                     | 391 |

| 15.4.6 Transfer Mode                                                                   |     |

| 15.4.6.1 Single Transfer                                                               |     |

| 15.4.6.2 Burst Transfer                                                                |     |

| 15.4.7 SIO/SPI mode                                                                    |     |

| 15.4.7.1 SPI mode                                                                      |     |

| 15.4.7.2 SIO mode                                                                      |     |

| 15.4.8 Master / Slave                                                                  |     |

| 15.4.8.1 | 1 Operation as Slave in SPI mode  |  |

|----------|-----------------------------------|--|

| 15.4.8.2 | 2 Operation as Master in SPI mode |  |

| 15.4.8.3 | 3 Operation as Slave in SIO mode  |  |

| 15.4.8.4 | 4 Operation as Master in SIO mode |  |

| 15.5 TS  | SPI Control                       |  |

| 15.5.1   | Reset                             |  |

| 15.5.2   | Initial Setting of TSPI           |  |

| 15.5.3   | Start/Stop Transfer               |  |

| 15.6 Co  | ommunication Mode                 |  |

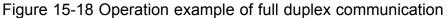

| 15.6.1   | Full Duplex Communication Mode    |  |

| 15.6.2   | Transmit Mode                     |  |

| 15.6.3   | Receive Mode                      |  |

## 16. USB Device Controller (USBD)

| 16.1 Ou              | tline                                                   |     |

|----------------------|---------------------------------------------------------|-----|

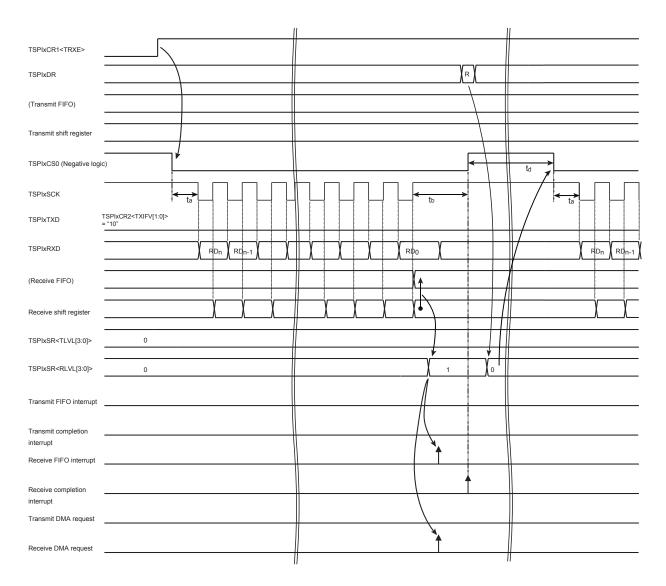

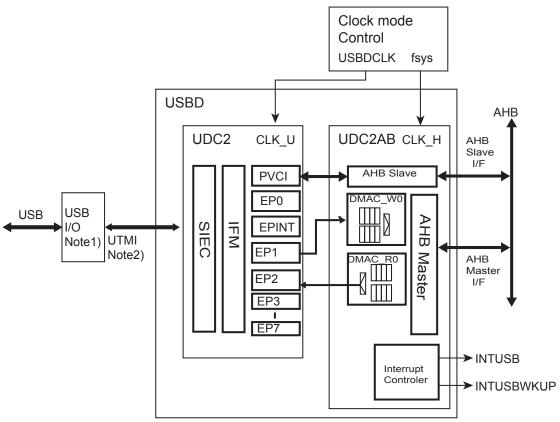

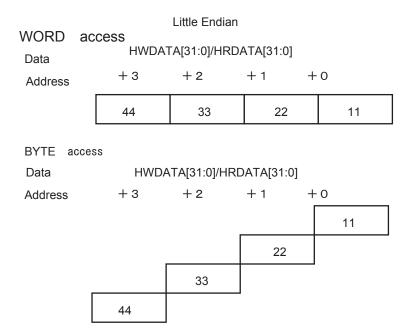

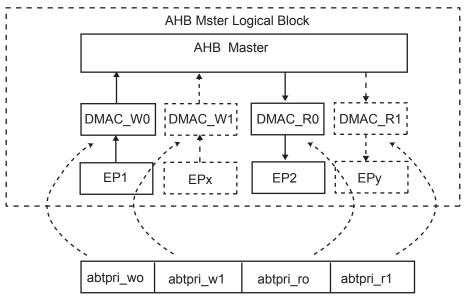

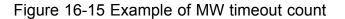

| 16.2 Svs             | tem Structure                                           | 402 |

| •                    | AB Bus Bridge (UDC2AB)                                  |     |

| 16.2.1 P             | Functions and Features                                  |     |

| 16.2.1.1             |                                                         |     |

| 16.2.1.2             | Configuration<br>Clock Domain                           |     |

|                      | Cock Domain Oshiba USB-Spec2.0 Device Controller (UDC2) | 109 |

|                      | Features and Functions                                  |     |

| 16.2.2.1<br>16.2.2.2 |                                                         |     |

| 16.2.2.2             | Specifications of Flags<br>Commands to EP               |     |

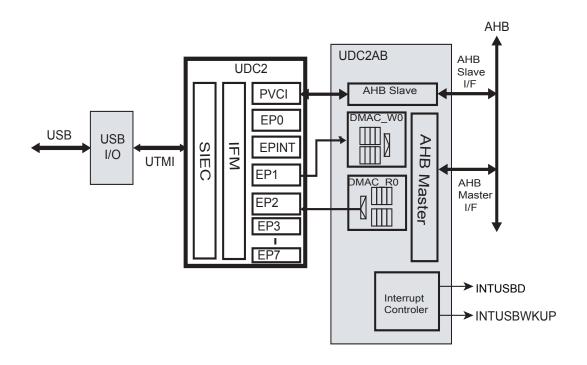

|                      |                                                         | 415 |

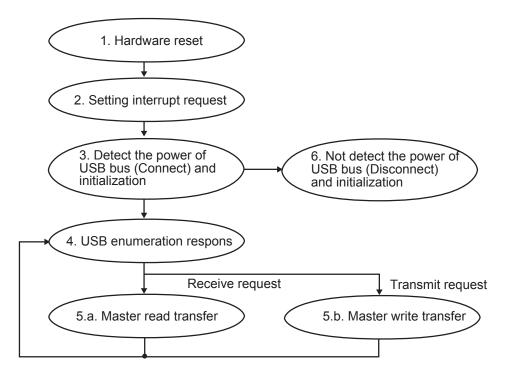

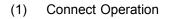

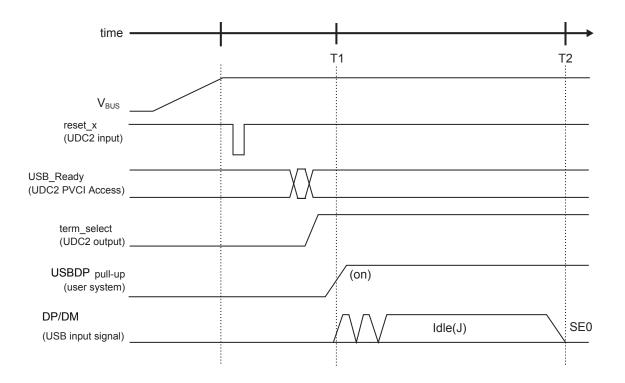

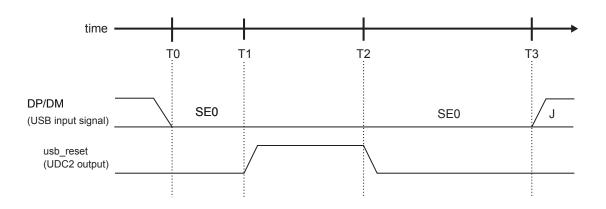

|                      | w to connect with the USB bus                           |     |

| 16.4 Reg             | gisters                                                 |     |

| 16.4.1 U             | DC2AB Register                                          |     |

| 16.4.1.1             | UDC2AB Register list                                    |     |

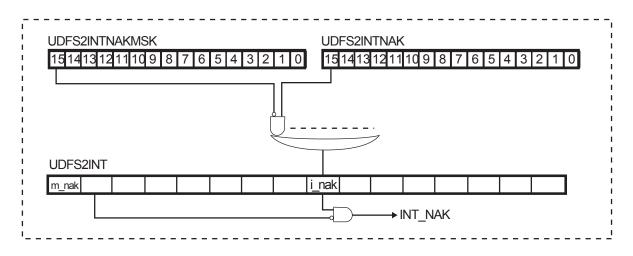

| 16.4.1.2             | UDFSINTSTS (Interrupt Status Register)                  |     |

| 16.4.1.3             | UDFSINTENB(Interrupt Enable Register)                   |     |

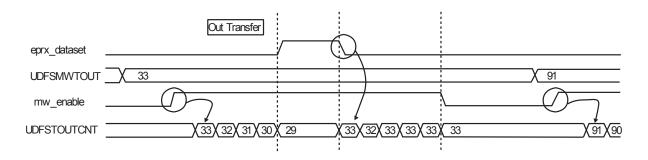

| 16.4.1.4             | UDFSMWTOUT(Master Write Timeout Register)               |     |

| 16.4.1.5             | UDFSC2STSET(UDC2 Setting Register)                      |     |

| 16.4.1.6             | UDFSMSTSET(DMAC Setting Register)                       |     |

| 16.4.1.7             | UDFSDMACRDREQ(DMAC Read Request Register)               |     |

| 16.4.1.8             | UDFSDMACRDVL(DMAC Read Value Register)                  |     |

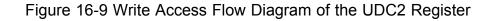

| 16.4.1.9             | UDFSUDC2RDREQ(UDC2 Read Request Register)               |     |

| 16.4.1.10            | UDFSUDC2RDVL(UDC2 Read Value Register)                  |     |

| 16.4.1.11            | UDFSARBTSET(Arbiter Setting Register)                   |     |

| 16.4.1.12            | 2 UDFSMWSADR(Master Write Start Address Register)       |     |

| 16.4.1.13            | UDFSMWEADR(Master Write End Address Register)           |     |

| 16.4.1.14            | UDFSMWCADR(Master Write Current Address Register)       |     |

| 16.4.1.15            | UDFSMWAHBADR(Master Write AHB Address Register)         |     |

| 16.4.1.16            | UDFSMRSADR(Master Read Start Address Register)          |     |

| 16.4.1.17            | UDFSMREADR(Master Read End Address Register)            |     |

| 16.4.1.18            | UDFSMRCADR(Master Read Current Address Register)        |     |

| 16.4.1.19            | UDFSMRAHBADR(Master Read AHB Address Register)          |     |

| 16.4.1.20            | UDFSPWCTL(Power Detect Control Register)                |     |

| 16.4.1.21            | 0 = 1 = 1 = ((((((((((((((((((((((((((((                |     |

| 16.4.1.22            |                                                         |     |

| 16.4.2 U             | JDC2 Register                                           |     |

| 16.4.2.1             | UDC2 Registers                                          |     |

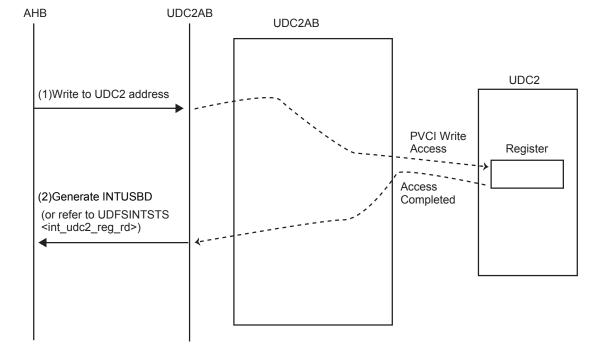

| 16.4.2.2             | How to access the UDC2 register                         |     |

| 16.4.2.3             | UDFS2ADR(Address-State register)                        |     |

| 16.4.2.4             | UDFS2FRM(Frame register)                                |     |

| 16.4.2.5             | UDFS2CMD(Command register)                              |     |

| 16.4.2.6             | UDFS2BRQ(bRequest-bmRequest Type register)              |     |

| 16.4.2.7             | UDFS2WVL(wValue register)                               |     |

| 16.4.2.8             | UDFS2WIDX(wIndex register)                              |     |

| 16.4.2.9             | UDFS2WLGTH(wLength register)                            |     |

| 16.4.2.10            |                                                         |     |

| 16.4.2.11            |                                                         |     |

| 16.4.2.12            |                                                         |     |

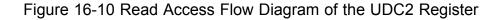

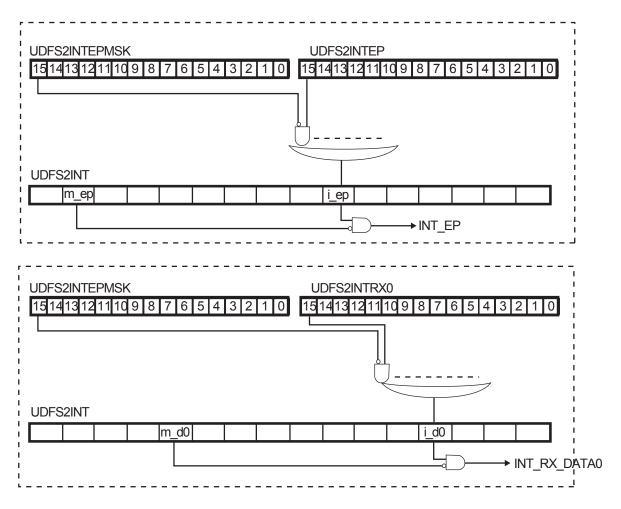

| 16.4.2.13            | UDFS2INTRX0(INT_RX_DATA0 register)                      |     |

| 16.4.2.14            |                                                         |     |

| 16.4.2.15            | UDFS2INTNAKMSK(INT_NAK_MASK register)                   |     |

| 16.4.2.16            | UDFS2EP0MSZ(EP0_MaxPacketSize register)                 |     |

| 16.4.2.17            | UDFS2EP0STS(EP0_Status register)                        |     |

| 16.4.2.18            | UDFS2EP0DSZ(EP0 Datasize register)                      |     |

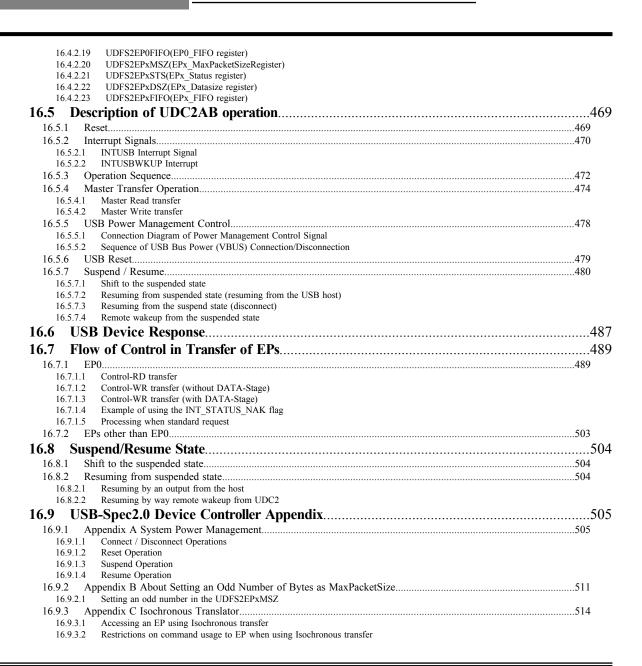

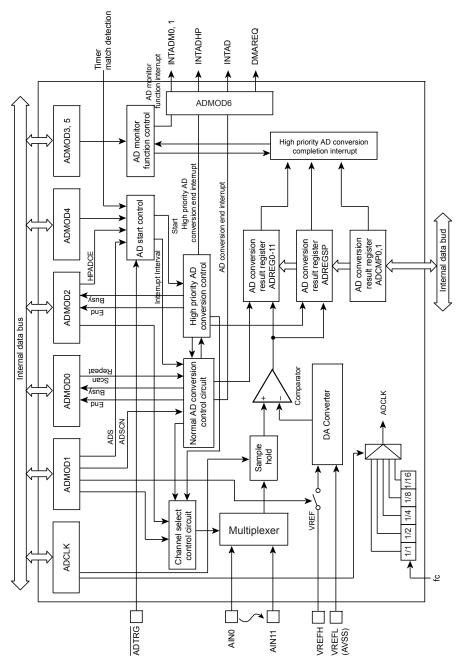

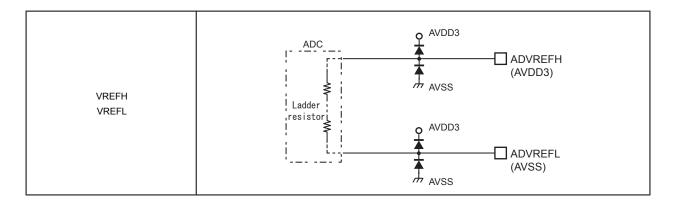

#### 17. 10-bit Analog/Digital Converter (ADC)

| 17.1    | Outline                                               |  |

|---------|-------------------------------------------------------|--|

|         | Configuration                                         |  |

| 17.3    | Registers                                             |  |

| 17.3.1  | Register list                                         |  |

| 17.3.2  | ADCLK (Conversion Clock Setting Register)             |  |

| 17.3.3  |                                                       |  |

| 17.3.4  | ADMOD1 (Mode Control Register 1)                      |  |

| 17.3.5  |                                                       |  |

| 17.3.6  |                                                       |  |

| 17.3.7  |                                                       |  |

| 17.3.8  | ADMOD5 (Mode Control Register 5)                      |  |

| 17.3.9  | ADMOD6 (Mode Control Register 6)                      |  |

| 17.3.10 | ADREGn (Conversion Result Register n: $n = 0$ to 11)  |  |

| 17.3.1  |                                                       |  |

| 17.3.12 | 2 ADCMP0 (AD Conversion Result Comparison Register 0) |  |

| 17.3.13 ADCMP1 (AD Conversion Result Comparison Register 1)                                                                              |   |

|------------------------------------------------------------------------------------------------------------------------------------------|---|

| 17.4 Description of Operations                                                                                                           | 5 |

| 17.4.1 Analog Reference Voltage                                                                                                          |   |

| 17.4.2 AD Conversion Mode                                                                                                                |   |

| 17.4.2.1 Normal AD conversion                                                                                                            |   |

| 17.4.2.2 Top-priority AD conversion                                                                                                      |   |

| 17.4.3 AD Monitor Function                                                                                                               |   |

| 17.4.4 Selecting the Input Channel                                                                                                       |   |

| 17.4.5 AD Conversion Details                                                                                                             |   |

| 17.4.5.1 Starting AD Conversion                                                                                                          |   |

| 17.4.5.2 AD Conversion                                                                                                                   |   |

| 17.4.5.3 Top-priority AD conversion during normal AD conversion                                                                          |   |

| 17.4.5.4 Stopping Repeat Conversion Mode                                                                                                 |   |

| 17.4.5.5 Reactivating normal AD conversion<br>17.4.5.6 Conversion completion                                                             |   |

| <ul><li>17.4.5.6 Conversion completion</li><li>17.4.5.7 Interrupt generation timings and AD conversion result storage register</li></ul> |   |

| 17.4.5.7 Interrupt generation timings and AD conversion result storage register                                                          |   |

- 17.4.5.8 DMA Request 17.4.5.9 Cautions

- 17.4.5.9 Caution

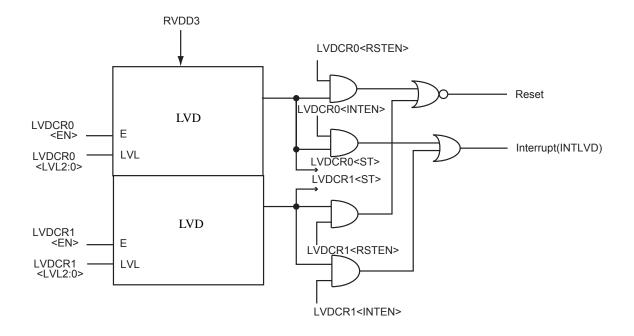

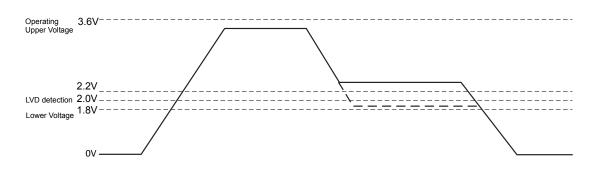

## **18.** Low Voltage detection circuit (LVD)

| 18.1 <b>(</b> | Configuration                                                        |  |

|---------------|----------------------------------------------------------------------|--|

|               | Registers                                                            |  |

|               | Register list                                                        |  |

|               | LVDCR0 (LVD detection control register 0)                            |  |

| 18.2.3        | LVDCR1 (LVD detection control register 1)                            |  |

| 18.3 (        | Dperation                                                            |  |

| 18.3.1        | Selecting detection voltage and enabling voltage detection operation |  |

| 18.3.2        | Reset by Detecting a supply voltage                                  |  |

| 18.3.3        | Interrupt by Detecting a supply voltage                              |  |

|               | Detecting Status                                                     |  |

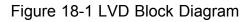

## **19. Watchdog Timer (WDT)**

| 19.1   | Configuration                                    |     |

|--------|--------------------------------------------------|-----|

| 19.2   | Register                                         |     |

| 19.2.1 | 8                                                |     |

| 19.2.2 | 2 WDMOD (Watchdog Timer Mode Register)           |     |

| 19.2.3 |                                                  |     |

| 19.2.4 |                                                  |     |

| 19.3   | Description of Operation                         |     |

| 19.3.1 | 1 Basic Operation                                |     |

| 19.3.2 | 1 Basic Operation<br>2 Operation Mode and Status |     |

| 19.3.3 |                                                  |     |

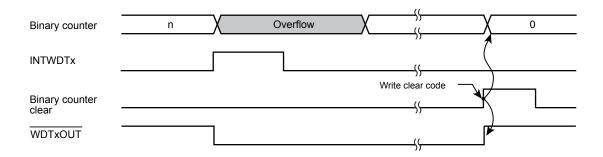

| 19.    | 3.3.1 INTWDT interrupt generation                |     |

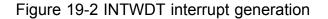

| 19.    | 3.3.2 Internal Reset Generation                  |     |

| 19.4   | Control of the watchdog timer                    | 549 |

| 19.4.1 | 1 Register access                                |     |

| 19.4.2 |                                                  |     |

| 19.4.3 | 3 Enable control                                 |     |

| 19.4.4 | 4 Watchdog timer clearing control                |     |

| 19.4.5 | 5 Detection time of watchdog timer               |     |

|        |                                                  |     |

## 20. Flash Memory Operation

| 20.1   | Features                      |  |

|--------|-------------------------------|--|

|        | Memory Size and Configuration |  |

|        | Function                      |  |

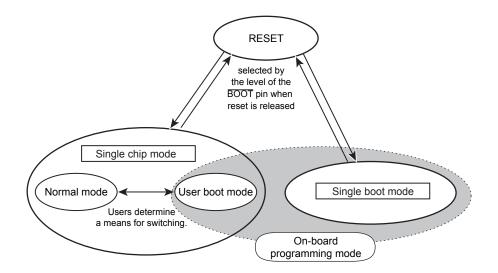

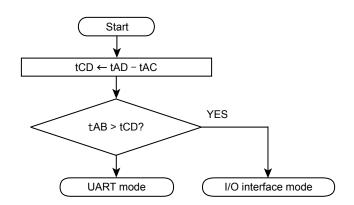

| 20.1.3 | Operation Mode                |  |

|        | *                             |  |

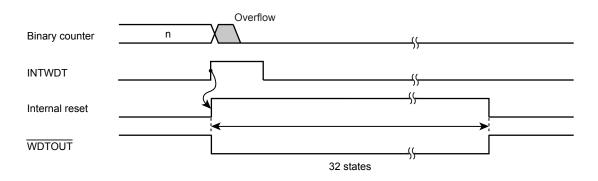

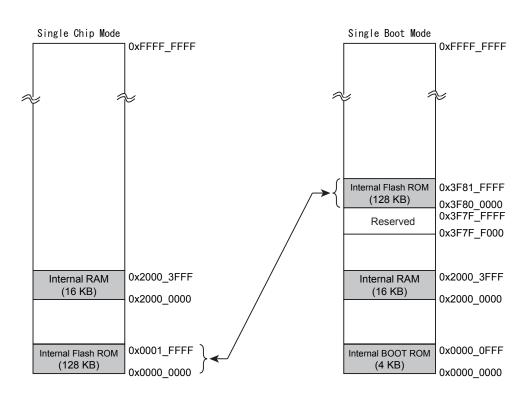

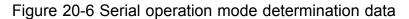

| 20.1.3.2 Mode Determination<br>20.1.4 Memory Map                                                                                 | 551 |

|----------------------------------------------------------------------------------------------------------------------------------|-----|

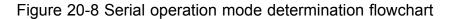

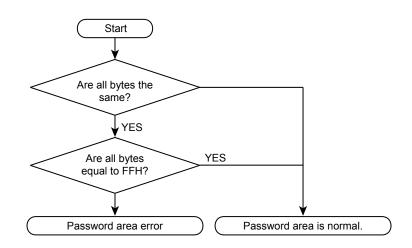

| 20.1.4     Memory Map       20.1.5     Protect/Security Function                                                                 |     |

| 20.1.5.1 Protect Function                                                                                                        |     |

| 20.1.5.2 Protect Bit Mask Function                                                                                               |     |

| 20.1.5.3 Security Function                                                                                                       |     |

| 20.1.6 Register                                                                                                                  | 557 |

| 20.1.6.1 Register List                                                                                                           |     |

| 20.1.6.2 FCSR (Flash status register)<br>20.1.6.2 FCSE(DIT (Security bit register)                                               |     |

| <ul> <li>20.1.6.3 FCSECBIT (Security bit register)</li> <li>20.1.6.4 FCPSRA (Flash protect status register)</li> </ul>           |     |

| 20.1.6.5 FCPMRA (Flash protect mask register)                                                                                    |     |

| 20.2 Detail of Flash Memory                                                                                                      | 560 |

| 20.2.1 Function                                                                                                                  |     |

| 20.2.1 Function                                                                                                                  |     |

| 20.2.2 Operation Mode of Flash Methofy                                                                                           |     |

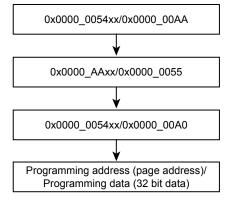

| 20.2.4 How to Execute Command                                                                                                    |     |

|                                                                                                                                  |     |

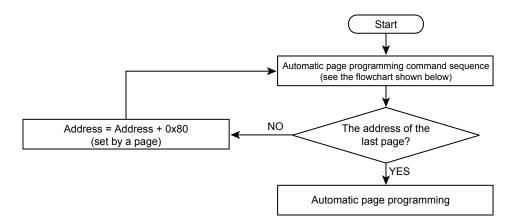

| 20.2.5 Command Description<br>20.2.5.1 Automatic Page Program                                                                    |     |

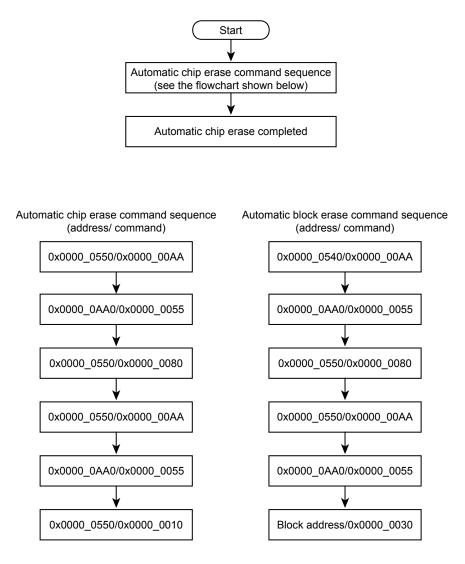

| 20.2.5.1       Automatic Page Program         20.2.5.2       Automatic Chip Erase                                                |     |

| 20.2.5.3 Automatic Block Erase                                                                                                   |     |

| 20.2.5.4 Automatic Protect Bit Program                                                                                           |     |

| 20.2.5.5 Auto Protect Bit Erase                                                                                                  |     |

| 20.2.5.6 ID-Read                                                                                                                 |     |

| 20.2.5.7 Read Command and Read/reset Command (Software Reset)                                                                    |     |

| 20.2.6 Command Sequence                                                                                                          | 565 |

| 20.2.6.1 Command Sequence List                                                                                                   |     |

| 20.2.6.2Address Bit Configuration in the Bus Cycle20.2.6.3Block Address (BA)                                                     |     |

| 20.2.6.4 How to Specify Protect Bit (PBA)                                                                                        |     |

| 20.2.6.5 ID-Read Code (IA, ID)                                                                                                   |     |

| 20.2.6.6 Example of Command Sequence                                                                                             |     |

| 20.2.7 Flowchart                                                                                                                 |     |

| 20.2.7.1 Automatic Program                                                                                                       |     |

| 20.2.7.2 Automatic Erase                                                                                                         |     |

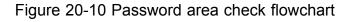

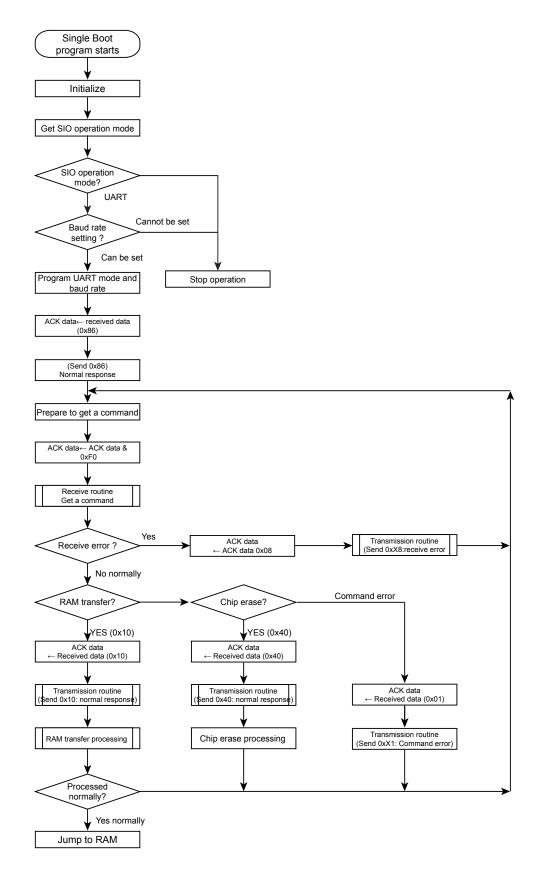

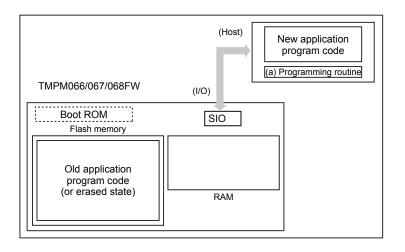

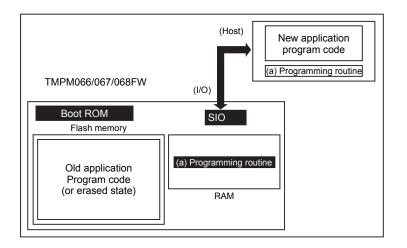

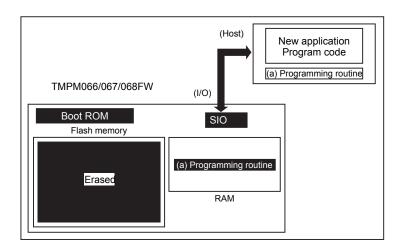

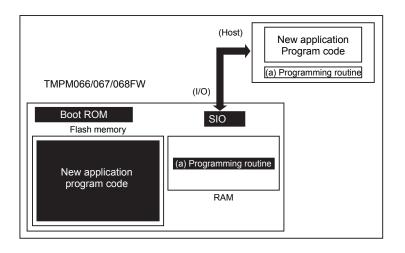

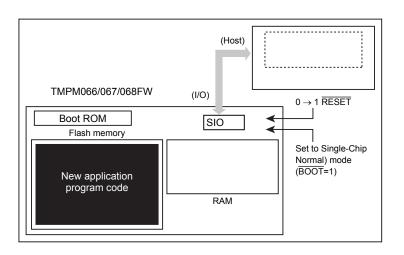

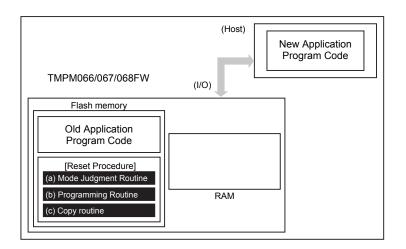

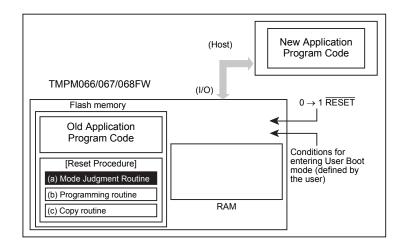

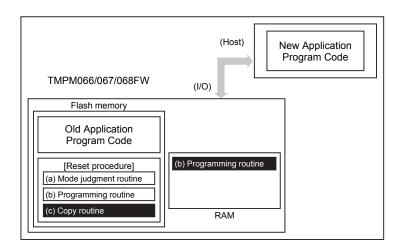

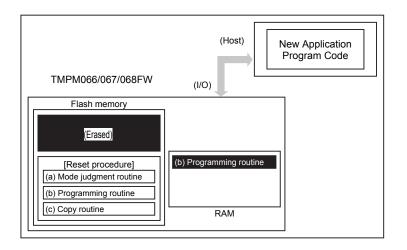

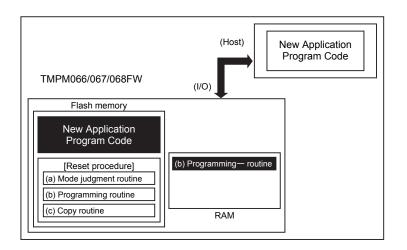

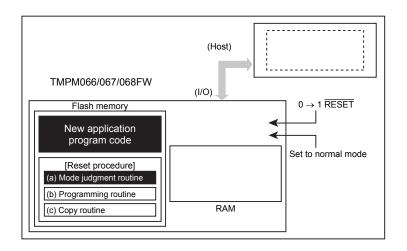

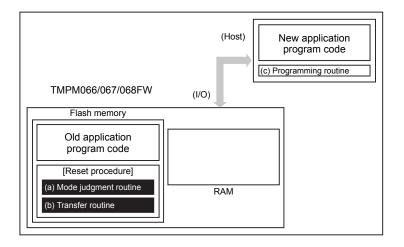

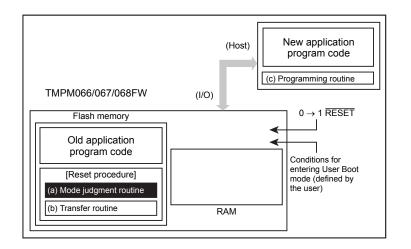

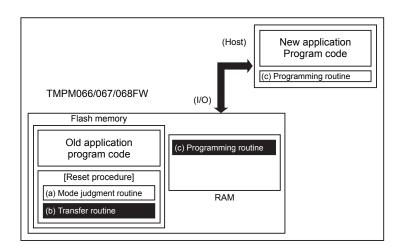

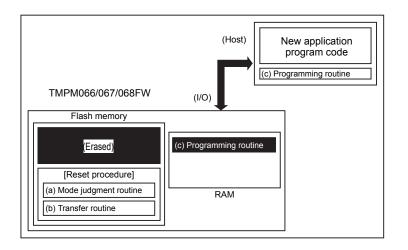

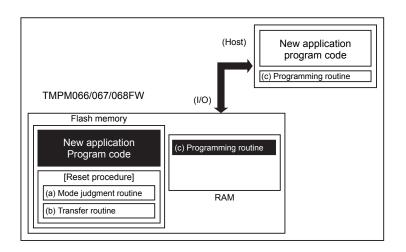

| 20.3 How to Reprogram Flash using Single Boot Mode                                                                               | 571 |

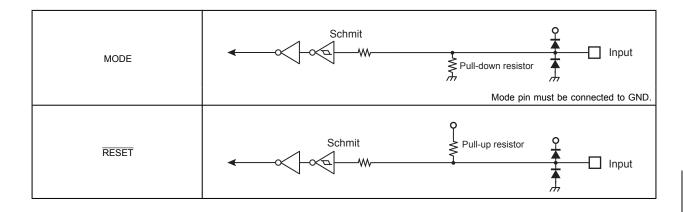

| 20.3.1 Mode Setting                                                                                                              |     |

| 20.3.2 Interface Specification                                                                                                   |     |

| 20.3.3 Restrictions on Internal Memories                                                                                         |     |

| 20.3.4 Operation Command                                                                                                         |     |

| 20.3.4.1 RAM Transfer                                                                                                            |     |

| 20.3.4.1 10/10/11/00/00                                                                                                          |     |

| 20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase                                                                           |     |

| 20.3.4.2       Flash Memory Chip Erase and Protect Bit Erase         20.3.5       Common Operation regardless of Command         |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| 20.3.4.2       Flash Memory Chip Erase and Protect Bit Erase         20.3.5       Common Operation regardless of Command         |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| 20.3.4.2       Flash Memory Chip Erase and Protect Bit Erase         20.3.5       Common Operation regardless of Command         |     |

| 20.3.4.2       Flash Memory Chip Erase and Protect Bit Erase         20.3.5       Common Operation regardless of Command         |     |

| <ul> <li>20.3.4.2 Flash Memory Chip Erase and Protect Bit Erase</li> <li>20.3.5 Common Operation regardless of Command</li></ul> |     |

| 20.3.4.2       Flash Memory Chip Erase and Protect Bit Erase         20.3.5       Common Operation regardless of Command         |     |

20.4.2.4

Step-5

20.4.2.5

Step-5

20.4.2.6 Step-6

### 21. Debug Interface

| 21.1 | Specification Overview                                                                                           |  |

|------|------------------------------------------------------------------------------------------------------------------|--|

|      | SWJ-DP                                                                                                           |  |

| 21.3 | Peripheral Functions in Halt Mode                                                                                |  |

| 21.4 | Connection with a Debug Tool                                                                                     |  |

|      | About connection with debug tool<br>Important points of using debug interface pins used as general-purpose ports |  |

## 22. Port Section Equivalent Circuit Schematic

| 22.1 | PORT pin    |  |

|------|-------------|--|

|      | Analog pin  |  |

|      | Control pin |  |

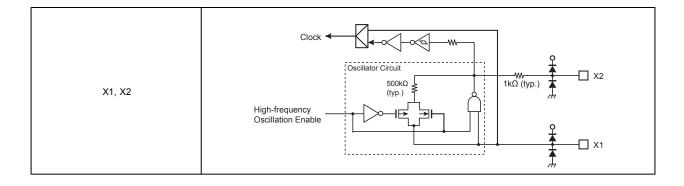

|      | Clock pin   |  |

## 23. Electrical Characteristics

| 23.1 Absolute Maximum Ratings                                                                    |     |

|--------------------------------------------------------------------------------------------------|-----|

| 23.2 DC Electrical Characteristics (1/2)                                                         |     |

| 23.3 DC Electrical Characteristics (2/2)                                                         |     |

| 23.4 10-bit AD Converter electrical Characteristics                                              |     |

| 23.5 AC Electrical Characteristics                                                               |     |

|                                                                                                  |     |

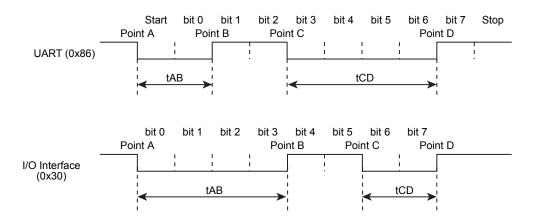

| 23.5.1 Serial channel (SIO/UART)                                                                 | 608 |

| 23.5.1.1 AC measurement Condition<br>23.5.1.2 AC Electrical Characteristics (I/O Interface Mode) |     |

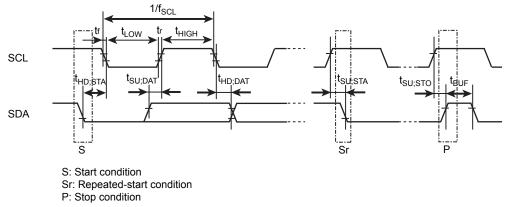

| 23.5.2 I2C interface (I2C)                                                                       | 610 |

| 23.5.2.1 AC measurement Condition                                                                |     |

| 23.5.2.2 AC Electrical Characteristics                                                           |     |

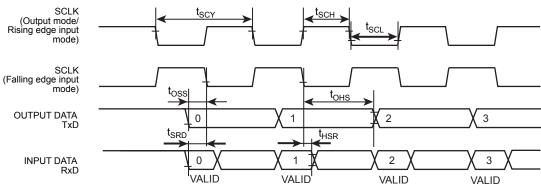

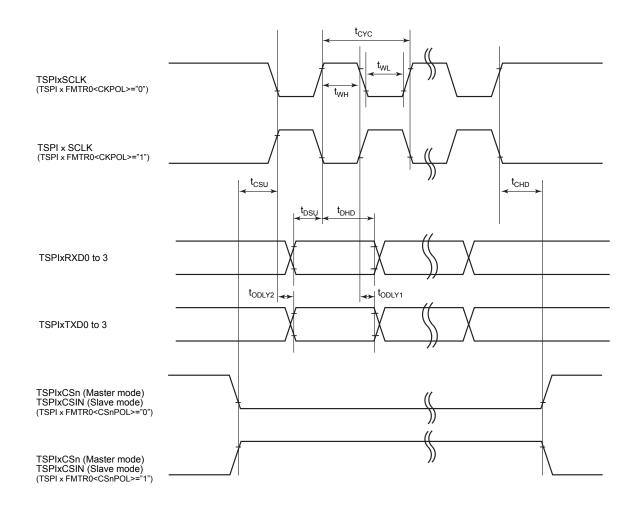

| 23.5.3 Toshiba serial peripheral interface (TSPI)                                                | 612 |

| 23.5.3.1 AC Measurement Condition                                                                |     |

| 23.5.4 USB Timing (Full-speed)                                                                   | 613 |

| 23.5.5 16-bit Timer / Event counter (TMRB)                                                       | 614 |

| 23.5.5.1 Event Counter                                                                           |     |

| 23.5.5.2 Capture                                                                                 |     |

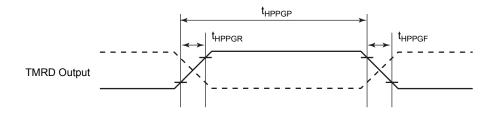

| 23.5.6 High Resolution 16-bit Timer (TMRD Ver.C) PPG output                                      | 615 |

| 23.5.6.1 AC Measurement Condition                                                                |     |

| 23.5.7 External Interrupt                                                                        | 616 |

| 23.5.7.1 AC Measurement Condition<br>23.5.7.2 AC Electrical Characteristics                      |     |

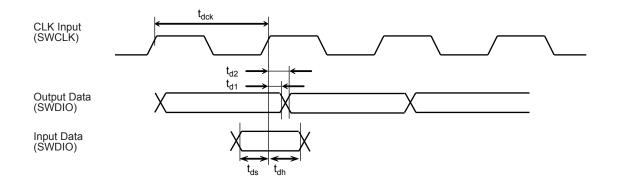

| 23.5.8 Debug Communication                                                                       | 617 |

| 23.5.8.1 AC Measurement Condition                                                                |     |

| 23.5.8.2 SWD interface                                                                           |     |

| 23.5.9 On-chip Oscillator Characteristic                                                         |     |

| 23.5.10 External Oscillator                                                                      |     |

| 23.5.11 External Clock Input                                                                     |     |

| 23.5.12 Flash Characteristic                                                                     |     |

| 23.5.13 Noise Filter Characteristic                                                              | 619 |

| 23.6 Recommended Oscillation Circuit                                                             | 620 |

| 23.6.1 Ceramic Oscillator                                                                        |     |

| 23.6.2 Crystal Oscillator                                                                        |     |

| 23.6.3 Precautions for designing printed circuit board.                                          |     |

| 23.7 Handling Precaution                                                                         |     |

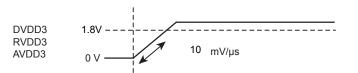

| 23.7.1 Voltage level of power supply at power-on                                                 |     |

|                                                                                                  |     |

| 23.7.2 Voltage drop during operations                                                            | 021 |

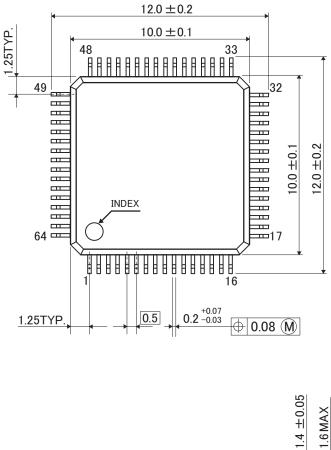

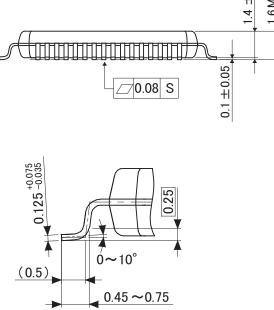

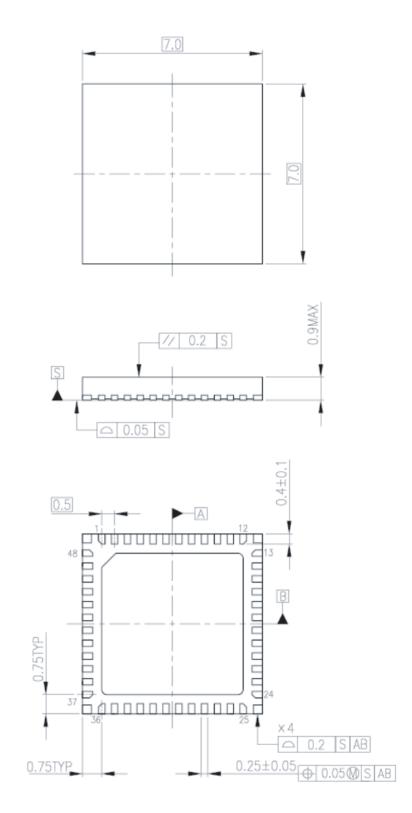

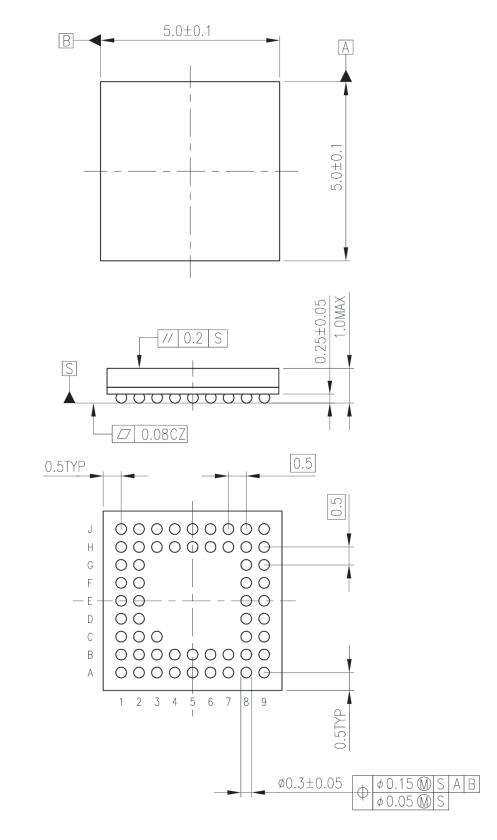

## 24. Package Dimensions

## CMOS 32-Bit Microcontroller

# TMPM066FWUG TMPM067FWQG TMPM068FWXBG

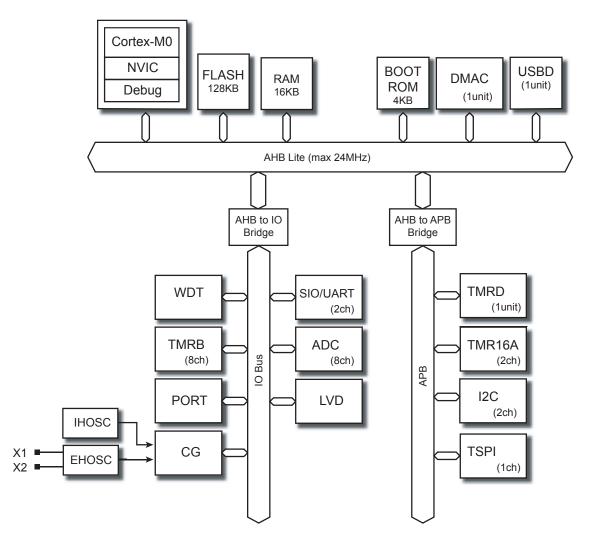

The TMPM066/067/068FW is a 32-bit RISC microprocessor series with an Arm®Cortex®-M0 microprocessor core.

Features of the TMPM066/067/068FW are as follows.

## 1.1 Features

- 1. Arm®Cortex®-M0 microprocessor core

- a. Improved code efficiency has been realized through the use of Thumb®-2 instruction.

- b. Both high performance and low power consumption have been achieved.

[High performance]

- A 32-bit multiplication (32 x 32=32 bit) can be executed with one clock.

[Low power consumptions]

- Optimized design using a low power consumption library

- Standby function that stops the operation of the micro controller core

- c. High-speed interrupt response suitable for real-time control

- An interruptible long instruction.

- Stack push automatically handled by hardware.

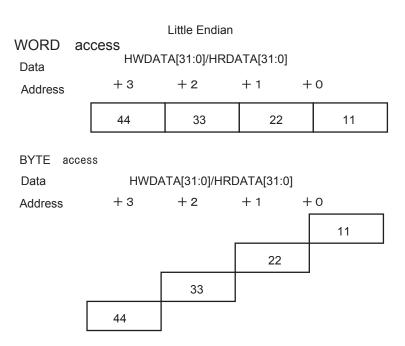

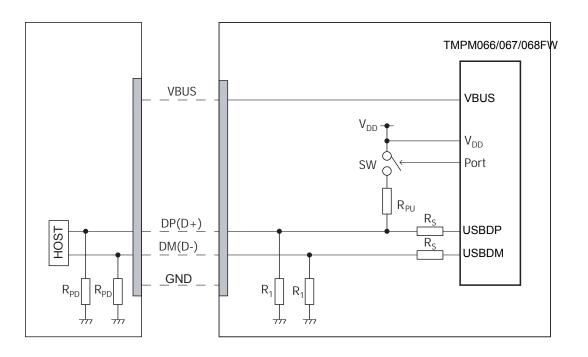

- 2. Endian: Little endian

- 3. On Chip program memory and data memory

- On chip Flash ROM: 128 Kbyte

- On chip RAM: 16 Kbyte

- 4. DMA controller (DMAC): 28 channels / 1 units

- Transfer mode: Built-in memory, peripheral function and external memory.

- 5. Clock generator (CG)

- External Clock input /external oscillation (8MHz to 16MHz)

- on Chip PLL (12x ,Max)

- Clock gear function: The high-speed clock can be divided into 1/1, 1/2, 1/4, 1/8, 1/16.

- 6. Standby mode

- IDLE, STOP1

- 7. Interrupt source: The order of priority can be set to 4 levels.

- Internal: 24 factors

- · External: 6 factors

8. Input/output ports (PORT):

|                  | TMPM066FWUG | TMPM067FWQG | TMPM068FWXBG |

|------------------|-------------|-------------|--------------|

| Input/Output pin | 48          | 32          | 40           |

| Input pin        | -           | -           | -            |

| Output pin       | -           | -           | -            |

- 9. 16-bit timer (TMRB): 8 channels

- 16-bit interval timer mode

- 16-bit event counter mode

- 16-bit PPG output (4 Phase Synchronous mode)

- Input capture function

- 10. 16-bit timer (TMR16A): 2 channels

- 11. 16-bit timer with high resolution PPG output (TMRD):1unit

- 4-channel synchronous PPG output

- Duty can be settable in the units of 96MHz (10.4ns).

- 12. Watchdog timer (WDT): 1 channel

Watchdog timer (WDT) generates a reset or a non-maskable interrupt (NMI).

- 13. General-purpose serial interface (SIO/UART): 2 channels

- Either UART mode or synchronous mode can be selected

- Transmit FIFO: 4-stage 8-bit width, receive FIFO: 4-stage 8-bit width

- 14. I2C bus interface (I2C): 2 channels

- Communication rate 100kbps / 400kbps / 1000kbps(Ch1 only)

- · Wake-up function by Slave Address match (Ch1 only)

- 15. Serial Peripheral interface (TSPI) : 1 channel

- · Supports 2 types of communications such as SPI mode and SIO mode