# RAIN® RFID single chip reader EPC Class1 Gen2 compatible

Datasheet - production data

#### **Features**

- Supply voltage range 3.0 to 3.6 V

- Limited operation possible down to 2.7 V

- Maximum PA supply voltage 4.3 V

- Peripheral I/O supply range 1.65 to 5.5 V

- Protocol support for:

- ISO 18000-6C (EPC Class1 Gen2)

- ISO 29143 (Air interface for mobile RFID)

- ISO 18000-6A/B through direct mode

- DRM: 250 kHz and 320 kHz filters for M4 and M8

- Integrated supply regulators

- Frequency hopping support

- ASK or PR-ASK modulation

- Automatic I/Q selection

- Phase bit for tag tracking with 8-bit linear RSSI

- Temperature range: -40 °C to 85 °C

- 48-pin QFN (7x7x0.9 mm) package

- Tag read rates of up to 700\* tags/s (16-bit tag EPC length)

# **Description**

The ST25RU3993 RAIN® (UHF) RFID reader device provides multi-protocol support for the 840-960 MHz UHF band compatible with ISO18000-62 & -63, ISO29143 and to GS1's EPC UHF Gen2 air interface protocol. It includes an on-chip VCO and a power amplifier, and offers a complete set of RFID features including dense reader mode (DRM) functionality and support for frequency-hopping, low-level transmission coding, low-level decode, data framing and CRC checking.

The ST25RU3993 operates at very low-power, making it suitable for use in portable and battery-powered equipment such as mobile phones.

Packaged in a 7x7 mm QFN, the ST25RU3993 is able to deliver very high sensitivity and provides high immunity against the effects of antenna reflection and self-jamming. This is critical in mobile and embedded applications, in which antenna design is often compromised by cost or size constraints. High sensitivity enables the end-products to achieve their required read range while using a simpler and cheaper antenna, thus reducing overall system cost.

Thanks to its high level of integration, the ST25RU3993 requires only an external 8-bit microcontroller to create a complete RFID reader system, thus eliminating the need for a complex RFID co-processor.

Contents ST25RU3993

# **Contents**

| 1 | Des  | cription |                                            | 9  |

|---|------|----------|--------------------------------------------|----|

|   | 1.1  | Block    | diagram                                    | 9  |

| 2 | Fund | ctional  | overview                                   | 10 |

|   | 2.1  | Power    | r supply                                   | 12 |

|   |      | 2.1.1    | Main regulators                            | 12 |

|   |      | 2.1.2    | Internal PA supply regulator               | 12 |

|   |      | 2.1.3    | Periphery communication supply             | 12 |

|   |      | 2.1.4    | Automatic power supply level setting       | 12 |

|   |      | 2.1.5    | Power modes                                | 13 |

|   | 2.2  | Host o   | communication                              | 14 |

|   |      | 2.2.1    | Writing to registers                       | 16 |

|   |      | 2.2.2    | Reading from registers                     | 17 |

|   |      | 2.2.3    | Direct commands                            | 18 |

|   |      | 2.2.4    | SPI interface timing                       | 22 |

|   |      | 2.2.5    | CLSYS output                               | 24 |

|   |      | 2.2.6    | IO signal level and output characteristics | 24 |

|   |      | 2.2.7    | OAD, OAD2 outputs                          | 25 |

|   | 2.3  | PLL a    | nd VCO section                             | 25 |

|   |      | 2.3.1    | Voltage controlled oscillator              | 26 |

|   |      | 2.3.2    | PLL prescaler and main divider             | 26 |

|   |      | 2.3.3    | PLL reference frequency                    | 27 |

|   |      | 2.3.4    | Reference frequency source                 | 27 |

|   |      | 2.3.5    | Phase-frequency detector and charge pump   | 27 |

|   |      | 2.3.6    | Loop filter                                | 27 |

|   |      | 2.3.7    | Frequency hopping commands                 | 27 |

|   |      | 2.3.8    | PLL start-up and frequency hopping         | 28 |

|   | 2.4  | Device   | e status control                           | 28 |

|   | 2.5  | Protoc   | col control                                | 28 |

|   | 2.6  | Transı   | mission section                            | 29 |

|   |      | 2.6.1    | Tx data handling and coding                |    |

|   |      | 2.6.2    | Tx shape circuitry                         |    |

|   |      | 2.6.3    | Local oscillator (LO) path                 |    |

|   |      | 2.6.4    | Modulator                                  |    |

|   | 2.7  | Tx outp  | outs                                                     | 30 |

|---|------|----------|----------------------------------------------------------|----|

|   | 2.8  | Тх оре   | ration modes                                             | 31 |

|   |      | 2.8.1    | TX normal mode                                           | 31 |

|   |      | 2.8.2    | TX direct mode                                           | 33 |

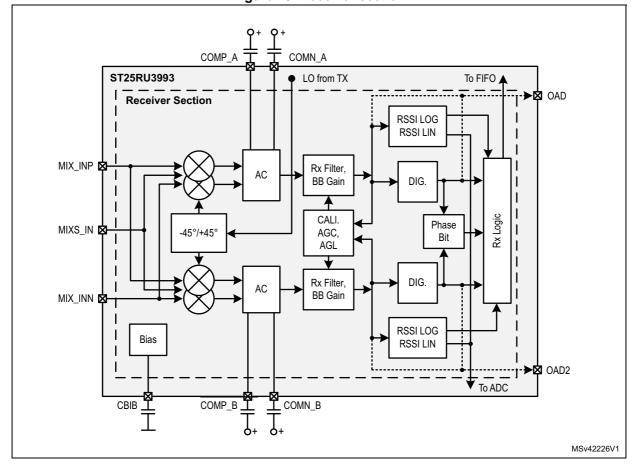

|   | 2.9  | Receiv   | er                                                       | 33 |

|   |      | 2.9.1    | Input mixers                                             | 34 |

|   |      | 2.9.2    | Local oscillator path                                    | 35 |

|   |      | 2.9.3    | Fast AC coupling                                         | 35 |

|   |      | 2.9.4    | Rx filter                                                | 35 |

|   |      | 2.9.5    | IQ selection                                             | 38 |

|   |      | 2.9.6    | Bit decoder                                              | 39 |

|   |      | 2.9.7    | Data framer                                              | 39 |

|   | 2.10 | Data re  | eception modes                                           | 39 |

|   |      | 2.10.1   | Rx normal mode                                           | 39 |

|   |      | 2.10.2   | Rx direct mode                                           | 42 |

|   |      | 2.10.3   | Modes supporting tuning of antenna or directivity device | 43 |

|   |      | 2.10.4   | Logarithmic RSSI                                         | 43 |

|   | 2.11 | A/D co   | nverter                                                  | 43 |

|   |      | 2.11.1   | External RF power detector                               | 43 |

|   |      | 2.11.2   | Reflected RF power indicator                             | 44 |

|   |      | 2.11.3   | Supply voltage measurement                               | 44 |

|   |      | 2.11.4   | Linear RSSI with sub-carrier phase bit                   | 44 |

|   |      | 2.11.5   | Internal signal level detectors                          | 45 |

|   | 2.12 | Interro  | gator anti-collision support                             | 45 |

| 3 | Regi | ster des | scription                                                | 46 |

|   | 3.1  | Main c   | ontrol registers                                         | 47 |

|   |      | 3.1.1    | Device status control register                           |    |

|   |      | 3.1.2    | Protocol selection register                              |    |

|   | 3.2  | Configu  | uration registers                                        |    |

|   |      | 3.2.1    | Tx options register                                      |    |

|   |      | 3.2.2    | Rx options register                                      |    |

|   |      | 3.2.3    | TRcal high register                                      |    |

|   |      | 3.2.4    | TRcal low register                                       |    |

|   |      | 3.2.5    | AutoACK wait time register                               |    |

|   |      | 3.2.6    | Rx no response time register                             |    |

|   |      |          |                                                          |    |

Contents ST25RU3993

|     | 3.2.7    | Rx wait time register                                                 | 52         |

|-----|----------|-----------------------------------------------------------------------|------------|

|     | 3.2.8    | Rx filter setting register                                            | 52         |

|     | 3.2.9    | Rx mixer and gain register                                            | 53         |

|     | 3.2.10   | Regulator and PA bias register                                        | 54         |

|     | 3.2.11   | RF output and LO control register                                     | 55         |

|     | 3.2.12   | Miscellaneous register 1                                              | 55         |

|     | 3.2.13   | Miscellaneous register 2                                              | 56         |

|     | 3.2.14   | Measurement control register                                          | 57         |

|     | 3.2.15   | VCO control register                                                  | 57         |

|     | 3.2.16   | CP control register                                                   | 58         |

|     | 3.2.17   | Modulator control register 1                                          | 59         |

|     | 3.2.18   | Modulator control register 2                                          | 59         |

|     | 3.2.19   | Modulator control register 3                                          | 30         |

|     | 3.2.20   | Modulator control register 4                                          | 31         |

|     | 3.2.21   | PLL main register 1                                                   | 31         |

|     | 3.2.22   | PLL main register 2                                                   | 32         |

|     | 3.2.23   | PLL main register 3                                                   | 33         |

|     | 3.2.24   | PLL auxiliary register 1                                              | 33         |

|     | 3.2.25   | PLL auxiliary register 2                                              | 34         |

|     | 3.2.26   | PLL auxiliary register 3                                              | 34         |

|     | 3.2.27   | Interrogator collision detection and IQ selection settings register 6 | 35         |

|     | 3.2.28   | Emitter-coupled mixer options register                                | 35         |

| 3.3 | Status r | egisters6                                                             | 36         |

|     | 3.3.1    | Status readout page setting register                                  | 36         |

|     | 3.3.2    | AGC and internal status display register                              | 36         |

|     | 3.3.3    | RSSI display register                                                 | 37         |

|     | 3.3.4    | AGL/VCO/F_CAL/PilotFreq status display register (r2Cpage[1:0] = 00) 6 | 37         |

|     | 3.3.5    | AGL/VCO/F_CAL/PilotFreq status register (r2Cpage[1:0] = 01) 6         | 38         |

|     | 3.3.6    | AGL/VCO/F_CAL/PilotFreq status register (r2Cpage[1:0] = 10) 6         | 86         |

|     | 3.3.7    | ADC readout/regulator setting display register (r2Dpage[1:0] = 00) 6  | 39         |

|     | 3.3.8    | ADC readout/regulator setting display register (r2Dpage[1:0] = 01) 6  | 39         |

|     | 3.3.9    | Command status display register                                       | 70         |

|     | 3.3.10   | Version register                                                      | 70         |

| 3.4 | Interrup | t registers                                                           | <b>7</b> 1 |

|     | 3.4.1    | Enable interrupt register 1                                           | 71         |

|     | 3.4.2    | Enable interrupt register 2                                           | 71         |

|     | 3.4.3    | Interrupt register 1                                                  | 72         |

|   |      | 3.4.4     | Interrupt register 2        |

|---|------|-----------|-----------------------------|

|   | 3.5  | Comm      | nunication registers        |

|   |      | 3.5.1     | FIFO status register        |

|   |      | 3.5.2     | Rx length register 1        |

|   |      | 3.5.3     | Rx length register 2        |

|   |      | 3.5.4     | Tx setting register         |

|   |      | 3.5.5     | Tx length register 170      |

|   |      | 3.5.6     | Tx length register 270      |

|   |      | 3.5.7     | FIFO I/O register           |

| 4 | Pino | uts and   | I pin description           |

| 5 | Elec | trical cl | naracteristics8°            |

|   | 5.1  | Absolu    | ute maximum ratings         |

|   | 5.2  | Opera     | ting conditions             |

|   | 5.3  | Typica    | l operating characteristics |

| 6 | Pack | kage inf  | formation                   |

|   | 6.1  | QFN4      | 8 package information       |

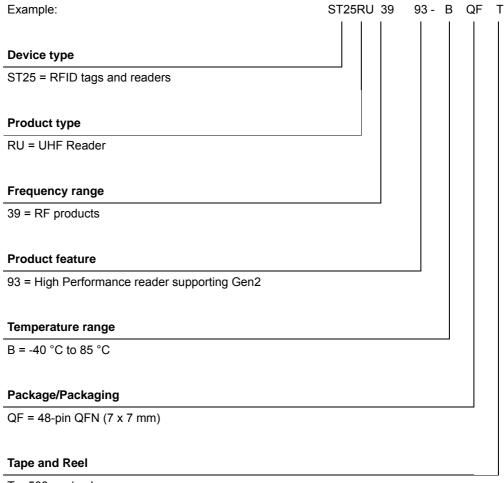

| 7 | Part | numbe     | ring 88                     |

| 8 | Revi | sion his  | story8                      |

List of tables ST25RU3993

# List of tables

| Table 1.  | Power modes overview                                                | 14 |

|-----------|---------------------------------------------------------------------|----|

| Table 1.  | Serial data interface (SPI interface) signal lines                  |    |

| Table 3.  | SPI operation modes                                                 |    |

| Table 4.  | List of direct commands                                             |    |

| Table 5.  | SPI timing parameters                                               |    |

| Table 6.  | I/O pin reassignment in direct mode                                 |    |

| Table 7.  | Rx filter characteristics (register 09h)                            |    |

| Table 8.  | Proposed Rx filter settings for supported link modes                |    |

| Table 9.  | Registers map                                                       |    |

| Table 10. | Device status control register                                      |    |

| Table 11. | Protocol selection register                                         |    |

| Table 11. | Tx options register                                                 |    |

| Table 13. | Rx options register                                                 |    |

| Table 14. | TRcal high register                                                 |    |

| Table 15. | TRcal low register                                                  |    |

| Table 15. | AutoACK wait time register                                          |    |

| Table 17. | Rx no response time register                                        |    |

| Table 17. | Rx wait time register                                               |    |

| Table 19. | Rx filter setting register                                          |    |

| Table 20. | Rx mixer and gain register                                          |    |

| Table 21. | Regulator and PA bias register                                      |    |

| Table 21. | RF output and LO control register                                   |    |

| Table 23. | Miscellaneous register 1                                            |    |

| Table 24. | Miscellaneous register 2                                            |    |

| Table 25. | Measurement control register                                        |    |

| Table 26. | VCO control register                                                |    |

| Table 27. | CP control register                                                 |    |

| Table 28. | Modulator control register 1                                        |    |

| Table 29. | Modulator control register 2                                        |    |

| Table 30. | Modulator control register 3                                        |    |

| Table 31. | Modulator control register 4                                        |    |

| Table 32. | PLL main register 1                                                 |    |

| Table 33. | PLL main register 2.                                                |    |

| Table 34. | PLL main register 3                                                 |    |

| Table 35. | PLL auxiliary register 1                                            |    |

| Table 36. | PLL auxiliary register 2                                            |    |

| Table 37. | PLL auxiliary register 3                                            |    |

| Table 38. | Interrogator collision detection and IQ selection settings register | 65 |

| Table 39. | Emitter-coupled mixer options register                              |    |

| Table 40. | Status readout page setting register                                |    |

| Table 41. | AGC and internal status display register                            |    |

| Table 42. | RSSI display register                                               |    |

| Table 43. | AGL/VCO/F_CAL/PilotFreq status display register (r2Cpage[1:0] = 00) |    |

| Table 44. | AGL/VCO/F_CAL/PilotFreq status register (r2Cpage[1:0] = 01)         |    |

| Table 45. | AGL/VCO/F_CAL/PilotFreq status register (r2Cpage[1:0] = 10)         |    |

| Table 46. | ADC readout/regulator setting display register (r2Dpage[1:0] = 00)  |    |

| Table 47. | ADC readout/regulator setting display register (r2Dpage[1:0] = 01)  |    |

| Table 48. | Command status display register                                     |    |

|           |                                                                     |    |

ST25RU3993 List of tables

| Table 49. | Version register                                     | 70 |

|-----------|------------------------------------------------------|----|

| Table 50. | Enable interrupt register 1                          | 71 |

| Table 51. | Enable interrupt register 2                          | 71 |

| Table 52. | Interrupt register 1                                 | 72 |

| Table 53. | Interrupt register 2                                 | 73 |

| Table 54. | FIFO status register                                 | 74 |

| Table 55. | Rx length register 1                                 | 74 |

| Table 56. | Rx length register 2                                 | 75 |

| Table 57. | Tx setting register                                  | 75 |

| Table 58. | Tx length register 1                                 | 76 |

| Table 59. | Tx length register 2                                 | 76 |

| Table 60. | FIFO I/O register                                    | 77 |

| Table 61. | ST25RU3993 pin definitions                           | 78 |

| Table 62. | Electrical parameters                                | 81 |

| Table 63. | Electrostatic discharge                              | 81 |

| Table 64. | Continuous power dissipation                         | 81 |

| Table 65. | Temperature ranges and storage conditions            | 82 |

| Table 66. | Operating conditions                                 | 82 |

| Table 67. | Differential mixer                                   | 83 |

| Table 68. | Single-ended mixer                                   | 84 |

| Table 69. | CMOS Input (valid for all CMOS inputs)               | 84 |

| Table 70. | CMOS output (valid for all CMOS ouputs)              | 85 |

| Table 71. | Typical operating characteristics                    | 85 |

| Table 72. | QFN48, 7x7 mm, 0.5 mm pitch, package mechanical data | 87 |

| Table 73. | Package codification                                 | 87 |

| Table 74. | Ordering information scheme                          | 88 |

| Table 75  | Document revision history                            | 90 |

List of figures ST25RU3993

# List of figures

| Figure 1.  | ST25RU3993 block diagram                               | 9    |

|------------|--------------------------------------------------------|------|

| Figure 2.  | Basic UHF reader system                                | . 10 |

| Figure 3.  | Possible SPI configurations                            | . 15 |

| Figure 4.  | Writing a single byte                                  | . 16 |

| Figure 5.  | Writing registers using address auto-incrementing      | . 17 |

| Figure 6.  | Reading a single byte                                  | . 17 |

| Figure 7.  | Reading from registers using address auto-incrementing | . 18 |

| Figure 8.  | Sending direct commands                                | . 22 |

| Figure 9.  | SPI Write timing                                       | . 23 |

| Figure 10. | SPI Read timing                                        | . 24 |

| Figure 11. | PLL and VCO section                                    | . 25 |

| Figure 12. | Transmission section                                   | . 29 |

| Figure 13. | Receiver section                                       | . 34 |

| Figure 14. | ST25RU3993 pinout                                      | . 78 |

| Figure 15  | OFN48 7x7 mm 0.5 mm pitch, package outline             | 86   |

ST25RU3993 **Description**

#### **Description** 1

The ST25RU3993 device is ideally suited for:

Embedded consumer/industrial applications with cost constraints such as beverage dispensing

- Hand-held readers

- Mobile UHF RFID readers

- Battery-powered stationary readers

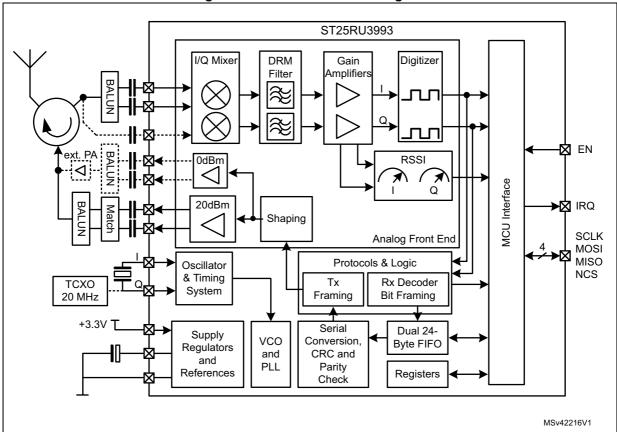

#### 1.1 **Block diagram**

The block diagram is shown in Figure 1.

Figure 1. ST25RU3993 block diagram

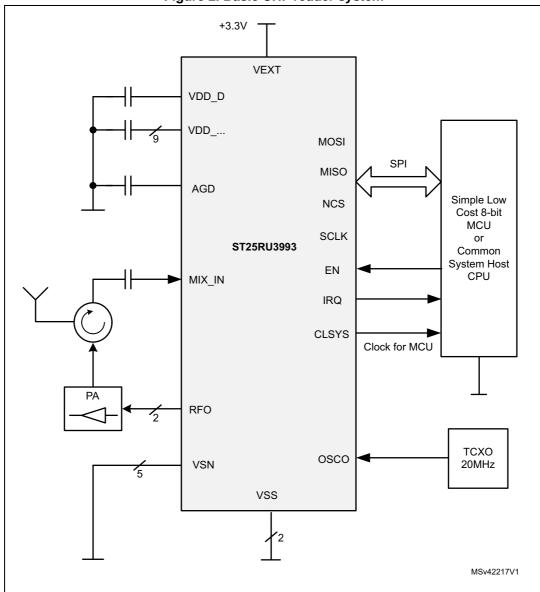

# 2 Functional overview

The ST25RU3993 UHF reader device is an integrated analog front end and protocol handling system for UHF RFID readers. The chip works on 3.3 V supply voltage and is therefore perfectly suited for low voltage, low-power applications.

It supports operation on DRM link frequencies used in ETSI and FCC regions (see Section 2.9.4: Rx filter for supported link modes). It complies with EPC Class1 Gen2 protocol (ISO 18000-6C) in normal mode and ISO 18000-6A/B in direct mode.

Figure 2. Basic UHF reader system

The RFID reader device features complete analog and digital functionality for the reader operation, including transmitter and receiver section with full EPC Class1 Gen2 (ISO18000-6C) digital protocol support.

577

The reader is enabled by setting the EN pin of the device to a positive logic level. A four-wire serial peripheral interface (SPI) is used for communication between the host system (MCU) and the reader device. The MCU is notified to service an IRQ by a logic high level on the IRQ pin. The device configuration and fine tuning of the reader performance is achieved through direct access to all control registers. The baseband data is transferred via a dual 24-byte FIFO buffer register to and from the reader device. The transmission system comprises a parallel/serial data conversion, low level data encoding and automatic generation of FrameSync, Preamble, and cyclic redundancy check (CRC).

Two transmitter output ports are available:

- One differential low-power, high linearity 0 dBm output that drives its power into a single ended 50 Ω load.

- One differential high power output that is amplified by the internal PA. The high power output delivers up to 20 dBm and requires a single ended 50 Ω load.

Both outputs are capable of amplitude shift keying (ASK) or phase reversal amplitude shift keying (PR-ASK) shaped modulation. The integrated supply voltage regulators ensure supply ripple rejection of the complete reader system.

The receiver system ensures both AM and PM demodulation, and comprises a proprietary automatic gain control system.

Selectable gain stages and signal bandwidth cover a wide range of input link frequencies and bit rate options. The signal strength of AM and PM modulation is measured and can be accessed through the *RSSI display register* (2Bh). The receiver output is selectable between digitized sub-carrier signals and internal sub-carrier decoder output. The internal decoder output delivers a bit stream and a data clock.

The receiver system comprises a framing system for the baseband data. It performs a CRC check and organizes the data in bytes that are then accessible to the host system through a 24-byte FIFO register.

To minimize the bill of materials (BOM), it also comprises an on-board PLL section with an integrated voltage controlled oscillator (VCO), partially integrated loop filter, supply section, ADC section and host interface section. To cover a wide range of applications the reader device has several possible configurations. The register section configures the operation and the behavior of all blocks.

The device needs to be supplied via VEXT and VEXT\_PA pins. The power supply connection is described in *Power supply*. At device power-up, the configuration registers are preset with their default values. The default values are described in the configuration register tables along with all option bits. The communication between the reader device and the transponder(s) follows the reader-talk-first method. After device power-up and register configuration, the host system (MCU) can start a communication with the transponder by turning the RF field ON and transmitting the first protocol command. Transmission and reception is possible in two modes:

- Normal mode

- Direct mode

In normal mode the base band data is transferred through the double FIFO buffer and all protocol data processing is done internally. In the direct mode the encoders and decoders are bypassed for transmission and reception and the data processing must be done by the MCU. In the direct mode the MCU can service the analog front-end in real time.

DS11840 Rev 9 11/90

# 2.1 Power supply

The device has its own power supply system to minimize the influence of external power supply noise and interferences and improves decoupling between different internal building blocks.

The positive supply pins are VEXT and VEXT\_PA. The negative supply pins are all VSN and VSS pins, including the exposed die pad. For optimal power supply rejection and device performance the supply voltage should be at least 3.3 V. A power supply voltage above 3.0 V enables operation with reduced power supply rejection. With lower supply voltages (down to 2.7 V) reduced device performance should be expected.

# 2.1.1 Main regulators

A set of adjustable regulators is used to supply the different internal building blocks of the device. The common input pin for most regulators is VEXT. The regulator outputs are the VDD\_A, VDD\_LF, VDD\_D, VDD\_MIX and VDD\_B pins. Each regulator output requires shunt capacitors to ground. Typical values are 2.2  $\mu$ F and 100 pF, ceramic capacitors of (at least) X5R class are recommended. VDD\_LFI and VDD\_TXPAB are supply input pins and should be connected to VDD\_MIX.

The regulated output voltage can be set in the range from 2.7 V up to 3.4 V in 0.1 V steps using option bits rvs[2:0] in the *Regulator and PA bias register* (0Bh). It is also possible to adjust the regulated output voltage automatically to approximately 300 mV below the supply voltage V<sub>EXT</sub> using the direct command automatic power supply level setting (A2h).

### 2.1.2 Internal PA supply regulator

The internal power amplifier has a dedicated voltage regulator. The input pin is VEXT\_PA, output is VDD\_PA. The regulator has an internal compensation circuit that requires a small external capacitance on VDD\_PA (typical 1 nF). Operation of this voltage regulator is allowed only in a loaded condition.

The regulated output voltage can be set in the range from 2.7 V up to 3.4 V in 0.1 V steps using option bits rvs\_rf[2:0] in the *Regulator and PA bias register* (0Bh). It is also possible to adjust the regulated output voltage automatically to approximately 300 mV below the supply voltage V<sub>EXT</sub> using the direct command automatic power supply level setting (A2h).

As the rvs\_rf[2:0] settings and the automatic power supply level adjustment generally can have different values, the system is designed to automatically select the lowest voltage level for the VDD PA.

#### 2.1.3 Periphery communication supply

The logic levels used for communication with the host system (MCU) can vary within a wide voltage range. The VDD\_IO input pin is used to define these logic levels between 1.65 V and 5.5 V. It is recommended to connect VDD\_IO to the host system power supply in order to avoid any voltage mismatch.

#### 2.1.4 Automatic power supply level setting

The power supply section comprises a system that automatically adjusts the regulators to approximately 300 mV below the  $V_{\text{EXT}}$  supply voltage, required to achieve good power supply rejection in the regulators.

The direct command automatic power supply level setting (A2h) activates the system. To switch back to manual power supply level adjustment, the direct command manual power supply level setting (A3h) should be sent.

Before the direct command (A2h) is issued it is necessary to set and lock the PLL within the allowed target frequency (840 MHz to 960 MHz).

At the beginning of the automatic adjustment, the device sets the regulators to 3.4 V and enables the RF field to simulate a normal power supply load. During the procedure the device decreases the regulated voltage in 100 mV steps, each 300  $\mu$ s long. The lowest voltage that the regulator can set is 2.7 V.

The procedure stops when the difference between the  $V_{EXT}$  and the regulated voltages is at least 300 mV, or reaches the last step. The device then disables the RF field and sends an IRQ request with Irq cmd bit (register 36h) set to high.

#### 2.1.5 Power modes

The device has four main power modes:

- Power down mode

- Standby mode

- Normal mode RF OFF

- Normal mode RF ON

#### Power down mode

By driving the EN pin to a logic low level the device enters the power-down mode. In this mode, the circuit is disabled.

#### Standby mode

The standby mode is entered from normal mode by setting the option bit stby high (register 00h). In the standby mode the voltage regulators, the reference voltage system and the crystal oscillator are operating in a low-power mode. The PLL, transmitter output stages and the receivers are switched off. All register settings are maintained while switching between standby and normal mode. The bias and reference voltages after stby = 0 typically stabilize within 12 ms. By then the device is ready to switch ON the RF field and start data transmission.

#### Normal mode - RF OFF

Setting the EN pin to a logic high level activates the normal mode. In this mode the following internal blocks are enabled:

- All supply regulators

- Reference voltage and bias system

- Crystal oscillator

- RF oscillator and PLL

When the EN pin is set to a logic high level the bias and reference voltages become stable after 12 ms (typical value). From then on the device is ready for interaction with the internal registers. After the reference frequency source stabilizes and the CLSYS clock becomes active, the device is ready to operate according to the configuration of its internal registers. If the crystal oscillator is used, the time the crystal stabilizes depends on the crystal type used. A typical time is 1.5 ms to 3 ms. By reading the *AGC and internal status display*

DS11840 Rev 9 13/90

*register* (2Ah), the MCU can check the crystal status. The status bit osc\_ok = 1 in this register indicates that the crystal oscillation is stable and that the device is ready to operate.

If a continuously running TCXO is used the settling of the internal clock is faster, as only the OSCO pin DC level needs to be set. The same test with the osc\_ok status bit as described above can be used.

After additional 500 ms (typ.) the device is ready to switch on the RF field and the transmission of inventory commands for transponder communication.

#### Normal mode - RF ON

By setting the rf\_on option bit in the *Device status control register* (00h) the device immediately starts with the field ramp-up. The ramp-up time and shape are defined by trfon[1:0] and lin\_mod option bits in the *Modulator control register 3* (15h). When the RF field ramp-up is finished the rf\_ok status bit (register 2Ah) is set to high. In addition an IRQ is generated, which is indicated by Irq ana status bit set to high (register 38h).

Setting the option bit rf\_on to low starts the field ramp-down. The RF field is decreased according to trfon[1:0] and lin\_mod bits (register 15h). When this step is completed, the rf\_ok status bit in *AGC and internal status display register* (2Ah) is set to low, and an IRQ is sent with the Irg\_ana status bit high.

*Table 1* summarizes the available power modes and the transitions times between them.

| Mode                    | EN<br>pin | Stby<br>option<br>bit | rf_on<br>option<br>bit | Current<br>consumption | Time to enter<br>the mode                       | Time from mode to active RF field               |

|-------------------------|-----------|-----------------------|------------------------|------------------------|-------------------------------------------------|-------------------------------------------------|

| Power<br>down           | L         | -                     | -                      | 1 μΑ                   | Immediately from normal mode                    | 12 - 17 ms (Crystal or TCXO start + bias start) |

| Standby                 | Н         | Н                     | L                      | 3 mA                   | Immediately from normal mode                    | 12 - 17 ms (Crystal or TCXO start + bias start) |

| Normal                  | Н         | L                     | L                      | 24 mA                  | 12 - 17 ms (Crystal or TCXO start + bias start) | 12.5 µs<br>(Field ramp-up)                      |

| Normal with RF field on | Н         | L                     | Н                      | 75 mA                  | 12.5 µs<br>(Field ramp-up)                      | NA                                              |

Table 1. Power modes overview

# 2.2 Host communication

A standard 4-wire serial interface (SPI) together with an interrupt request line (IRQ pin) is used to communicate with the device. An additional line (CLSYS) can be used as a system clock source for the MCU.

Table 2. Serial data interface (SPI interface) signal lines

| Name | Signal        | Signal level | Description             |

|------|---------------|--------------|-------------------------|

| NCS  | Digital input | CMOS         | SPI enable (active low) |

| SCLK | Digital input | CMOS         | Serial clock            |

| MOSI | Digital input | CMOS         | Serial data input       |

|       |                                   |      | (                        |

|-------|-----------------------------------|------|--------------------------|

| Name  | Signal Signal level               |      | Description              |

| MISO  | Digital output with tri-<br>state | CMOS | Serial data output       |

| IRQ   | Digital output                    | CMOS | Interrupt request output |

| CLSYS | Digital output                    | CMOS | MCU clock output         |

Table 2. Serial data interface (SPI interface) signal lines (continued)

By setting the NCS pin low the SPI interface is enabled. While NCS is high the SPI interface is deactivated. It is recommended to keep signal NCS high whenever the SPI interface is not used. MOSI is sampled at the falling edge of SCLK. The SPI communication is done in bytes. The first two bits of the first byte on the MOSI line (after NCS high-to-low) define the SPI operation mode. MSB bit is always transmitted first (valid for address and data).

The read and write modes support address auto incrementing for multi byte transfers. Only the first address needs to be sent and internally the address is incremented for consecutive reads or writes.

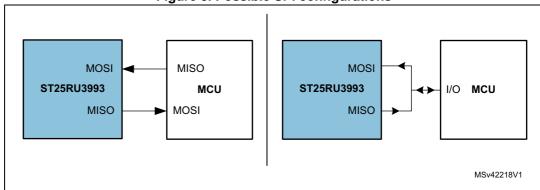

The MISO output is usually in tri-state and it is only driven when output data are available. This allows to short-circuit the MOSI and the MISO lines externally to create a bi-directional signal (see *Figure 3*).

During the time the MISO output is in high impedance it is possible to activate a 50 k $\Omega$  pull-down resistor by setting option bits miso\_pd1 and miso\_pd2 in *Miscellaneous register 1* (0Dh).

Figure 3 shows the possible SPI interconnection options.

Figure 3. Possible SPI configurations

|                | Mode pattern (MSB to LSB) |    |                               |    |    |    |    |    |                                                  |

|----------------|---------------------------|----|-------------------------------|----|----|----|----|----|--------------------------------------------------|

| Command type   | Mode                      |    | Register address / command ID |    |    |    |    |    | Mode related data                                |

|                | M1                        | МО | X5                            | X4 | Х3 | X2 | X1 | X0 |                                                  |

| Write          | 0                         | 0  | A5                            | A4 | А3 | A2 | A1 | A0 | Data byte (or more bytes if of autoincrementing) |

| Read           | 0                         | 1  | A5                            | A4 | А3 | A2 | A1 | A0 | Data byte (or more bytes if of autoincrementing) |

| Direct command | 1                         | 0  | C5                            | C4 | C3 | C2 | C1 | C0 | -                                                |

| RFU            | 1                         | 1  | х                             | х  | Х  | х  | Х  | х  | -                                                |

Table 3. SPI operation modes

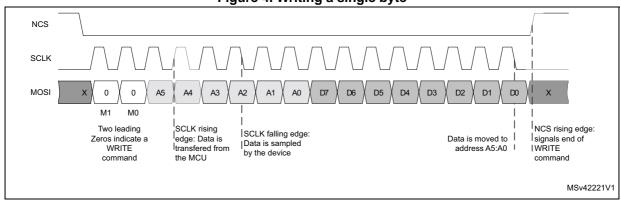

# 2.2.1 Writing to registers

Figure 4 show typical SPI Write communication examples for a single byte and for multiple bytes using address auto-incrementing. Following the SPI operation mode bits (M1 and M2) the address bits (A5: A1) of the target register are sent. Then one or more data bytes are sent depending on using auto-incrementing or not. The communication is terminated by putting NCS back to high. If this happens before a packet of 8 bits (one byte) is sent, writing to this register is not performed. If the register at the defined address does not exist or is a read only register the write command does not succeed either.

Figure 4 shows an example of a SPI write command signaling for a single byte.

Figure 4. Writing a single byte

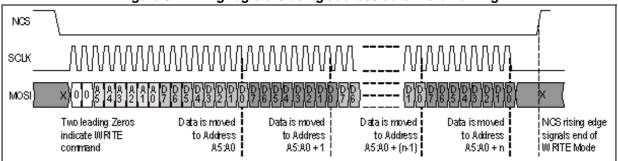

Figure 5 an example of a SPI write command signaling for multiple bytes.

Figure 5. Writing registers using address auto-incrementing

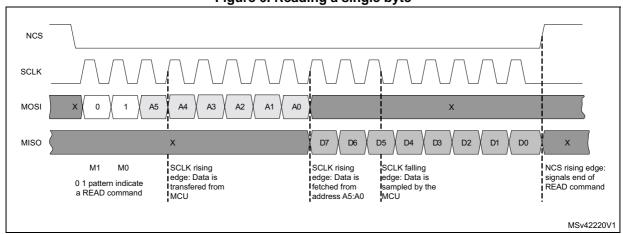

# 2.2.2 Reading from registers

After the SPI operation mode bits (M1 and M0) the target address is sent. Then one or more data bytes are transferred to the MISO output. MOSI is sampled at the falling edge of SCLK. Data to be read from the internal registers are transferred to the MISO pin on rising edge of SCLK and should be sampled by the MCU on the falling edge. If the register address does not exist all 0 data are sent to MISO.

Figure 6 shows an example for a typical SPI Read command for a single byte.

Figure 6. Reading a single byte

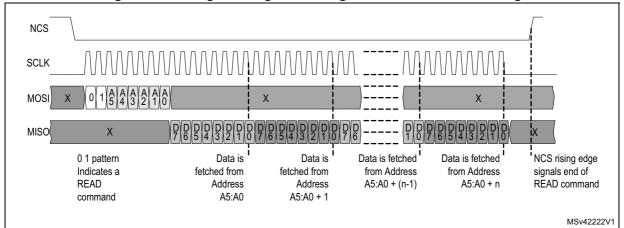

Figure 7 shows an example of an SPI read command signaling for multiple bytes.

Figure 7. Reading from registers using address auto-incrementing

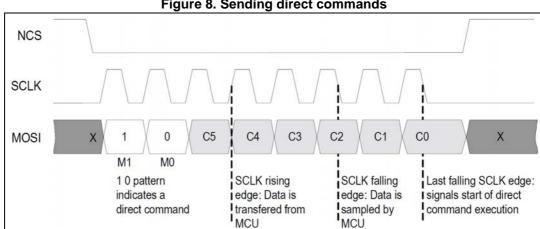

#### 2.2.3 Direct commands

Direct commands have no parameters, so only a single byte needs to be sent. The only exception is the Query command, which requires two parameter bytes (stored in FIFO) following the command byte. SPI operation mode bits M1 = 1 and M0 = 0 define a direct command. The following six bits define the direct command ID. The direct command is executed at the last falling edge of SCLK. Some direct commands are executed immediately while others start a process with certain duration (calibration, measurements...).

Caution:

During execution of such commands it is not recommended to start another activity on the SPI interface.

After the execution of a direct command an IRQ request with Irq\_cmd bit high (register 38h) is sent.

Table 4. List of direct commands

| Code (HEX) | Command                                     | Direct execution |

|------------|---------------------------------------------|------------------|

| 80h        | Idle                                        | Yes              |

| 81h        | Direct Mode                                 | Yes              |

| 83h        | Soft Init                                   | Yes              |

| 84h        | Hop to Main Frequency                       | Yes              |

| 85h        | Hop to Auxiliary Frequency                  | Yes              |

| 87h        | Trigger AD Conversion                       | No               |

| 88h        | Trigger Rx Filter Calibration               | No               |

| 89h        | Decrease Rx Filter Calibration Data         | Yes              |

| 8Ah        | Increase Rx Filter Calibration Data         | Yes              |

| 90h        | Transmission with CRC                       | Yes              |

| 91h        | Transmission with CRC Expecting Header Bit  | Yes              |

| 92h        | Transmission without CRC                    | Yes              |

| 96h        | Block Rx                                    | Yes              |

| 97h        | Enable Rx                                   | Yes              |

| 98h        | Query                                       | Yes              |

| 99h        | QueryRep                                    | Yes              |

| 9Ah        | QueryAdjustUp                               | Yes              |

| 9Bh        | QueryAdjustNic                              | Yes              |

| 9Ch        | QueryAdjustDown                             | Yes              |

| 9Dh        | ACK                                         | Yes              |

| 9Fh        | ReqRN                                       | Yes              |

| A2h        | Automatic power supply level setting        | No               |

| A3h        | Manual power supply level setting           | Yes              |

| A4h        | Automatic VCO range selection               | No               |

| A5h        | Manual VCO range selection                  | Yes              |

| A6h        | AGL On                                      | Yes              |

| A7h        | AGL Off                                     | Yes              |

| A8h        | Store RSSI                                  | Yes              |

| A9h        | Clear RSSI                                  | Yes              |

| AAh        | Interrogator anti-collision support enable  | Yes              |

| ABh        | Interrogator anti-collision support disable | Yes              |

|            |                                             |                  |

# **Direct command description**

The direct commands supported by the ST25RU3993 are detailed below. Values in parentheses show the related command byte.

- Direct mode (81h): device enters the direct mode.

- **Soft init** (83h): this command resets the configuration registers to their default values and terminates all functions that were triggered before.

- **Hop to main frequency** (84h): this command forces the PLL to use the frequency defined in the PLL Main Registers 1 3. The PLL main registers are used per default.

- **Hop to auxiliary frequency** (85h): This command forces the PLL to use the frequency setting defined in the *PLL auxiliary register 1*, *PLL auxiliary register 2* and *PLL auxiliary register 3*.

- **Trigger A/D conversion** (87h): this command triggers the analog to digital conversion using the internal 8-bit A/D converter. For further information, refer to the A/D Converter description.

- **Trigger Rx filter calibration** (88h): this command triggers the Rx filter calibration procedure. For further information, refer to the Rx filter calibration description.

- **Decrease Rx filter calibration data** (89h), Increase Rx filter calibration data (8Ah): these commands adjust the automatically acquired Rx filter calibration data. For further information, refer to the Rx filter calibration description.

- Transmission with CRC (90h): transmission commands are used to transmit data from the reader to transponders. First, the Tx length registers (3Dh, 3Eh) need to be set with the number of complete bytes for transmission, including the number of bits for the incomplete byte. Then transmission data can be loaded in the FIFO register (3Fh). Transmission starts when the first byte is loaded. CRC-16 is included in the transmitted sequence.

The optimal way to load all transmission data is to use the Continuous Write mode, starting with the address 3Dh.

Example Using Address Auto-Incrementing:

SPI data (MOSI): 90h - 3Dh - 00h - 30h - AAh - BBh - CCh operates as follows:

- 90h:Transmission with CRC

- Write 00h to 3Dh

- Write 30h to 3Eh (three bytes are going to be transmitted)

- Write AAh, BBh, CCh to address 3Fh (FIFO data which will be transmitted).

- Transmission with CRC expecting header bit (91h): same as the previous command, but it also informs Rx decoding logic that an header bit is expected in the response.

- Transmission without CRC (92h): same as direct command 'Transmission with CRC', but the CRC part is omitted.

- Block Rx (96h): the Block Rx command deactivates the digital part of receiver (bit decoder and framer). Turning OFF the receiver is useful if the system operates in a noisy environment, causing a constant switching of the sub-carrier input of the Rx digital part. The active receiver will try to detect a Preamble and if the noise pattern matches the expected signal pattern, an interrupt is generated. A constant flow of interrupt requests can be a problem for the MCU, Such situation can be avoided by deactivating the receive decoder using the block RX command. The receiver is automatically reactivated at the end of any data transmission after the Rx wait time elapses. To set the Rx wait time refer to the Rx wait timer section. A second possibility to stop block Rx is to send the enable Rx (97h) command.

- Enable Rx (97h): this command prepares analog and digital part of the receiver for reception. This command should be sent to trigger the reception manually. This

command should not be sent if reception is automatically triggered by a data transmission command.

• Query (98h): the Query command issues the EPC query, which starts the inventory round. The Query command requires additional two data bytes which should be written to the FIFO (3Fh):

The two bytes in the FIFO should contain: "00", DR, M, TRext, Sel, Session, Target, Q Since this adds-up to 15 applicable bits, the LSB bit is disregarded. The transmitter in the end sends:

- Preamble

- Command ID

- Tx data (two bytes from FIFO)

- CRC-5.

The received RN16 is stored in the internal RN16 register for further communication steps (ACK, RegRN). RN16 is also stored in the FIFO.

- QueryRep (99h): the QueryRep command issues the EPC Gen2 QueryRep command followed by two session bits. The session bits are taken from *Tx setting register* (3Ch). The received RN16 is stored in the internal RN16 register for further communications (ACK, RegRN). RN16 is also accessible in the FIFO.

- QueryAdjustUp (9Ah): the QueryAdjustUp direct command issues the EPC Gen2

QueryAdjust command followed by two session bits and 'up' parameter (increasing the

number of available slots). The session bits are taken from *Tx setting register* (3Ch).

The received RN16 is stored in the internal RN16 register for further communications

(ACK, RegRN). RN16 is also accessible in the FIFO.

- QueryAdjustNic (9Bh): the QueryAdjustNic command issues the EPC Gen2

QueryAdjust command followed by two session bits and 'no change' parameter. The

session bits are taken from Tx setting register (3Ch). The received RN16 is stored in

the internal RN16 register for further communications (ACK, ReqRN). RN16 is also

accessible in the FIFO.

- QueryAdjustDown (9Ch): the QueryAdjustUp command issues the EPC Gen2

QueryAdjust followed by two session bits and 'down' parameter (decreasing the

number of available slots). The session bits are taken from *Tx setting register*(3Ch).

The received RN16 is stored in the internal RN16 register for further communications

(ACK, RegRN). RN16 is also accessible in the FIFO.

- ACK (9Dh): the ACK command issues the EPC ACK followed by RN16 stored in the internal RN16 register during last successful Query command.

- NAK (9Eh): the NAK command issues the EPC Gen2 NAK command to tags.

- ReqRN (9Fh): the ReqRN command issues the EPC Request RN to the tag. The last received RN is used as a parameter and the received new RN16 (handle) is stored in the internal RN16 register for further communications (ACK, ReqRN). New RN16 is also stored in the FIFO.

- Automatic power supply level setting (A2h), manual power supply level setting

(A3h): these commands trigger the automatic adjustment of the on-board voltage

regulators, and switch back to the manual selection. See Periphery Communication

Supply description for more details.

- Automatic VCO range selection (A4h), manual VCO range selection (A5h): these

commands trigger the automatic VCO range selection and switch back to manual VCO

range selection. See PLL and VCO description for more details.

DS11840 Rev 9 21/90

> AGL on (A6h), AGL off (A7h): these commands trigger and disable the AGL action. See AGL description for more details.

- Store RSSI (A8h), Clear RSSI (A9h): these commands store and clear the received signal strength indicator (RSSI) data that can be used for IQ decision circuitry. See IQ Selection description for more details.

- Interrogator anti-collision support enable (AAh), interrogator anti-collision support disable (ABh): these commands enable or disable the interrogator anticollision support defined in ISO 29143.

## **Direct command chaining**

Direct commands with immediate execution can be followed by another SPI commands like Read or Write without deactivating the NCS signal in between.

Figure 8. Sending direct commands

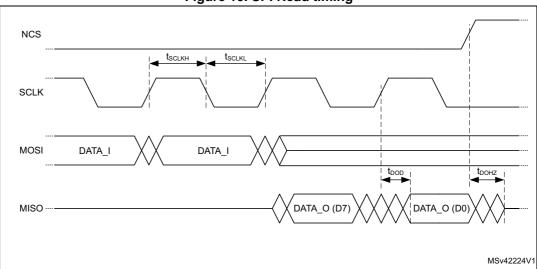

#### 2.2.4 **SPI** interface timing

**Table 5. SPI timing parameters**

| Symbol                                               | Parameter             | Note/Condition                                                              | Min | Тур | Max | Unit |

|------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------|-----|-----|-----|------|

| General (VDD_IO > 3 V, CLOAD < 50 pF, hs_output = 1) |                       |                                                                             |     |     |     |      |

| BR <sub>SPI</sub>                                    | Bit rate              | -                                                                           | -   | -   | 5   | Mbps |

| t <sub>SCLKH</sub>                                   | Clock high time       | -                                                                           | 70  | -   | -   | ns   |

| t <sub>SCLKL</sub>                                   | Clock low time        | -                                                                           | 70  | -   | -   | ns   |

| t <sub>NCSL</sub>                                    | NCS setup time        | Time between NCS<br>high-low transition to<br>first SCLK high<br>transition | 10  | -   | -   | ns   |

| t <sub>DIS</sub>                                     | Data-in setup<br>time | -                                                                           | 10  | -   | -   | ns   |

| t <sub>DIH</sub>                                     | Data-in hold time     | -                                                                           | 10  | -   | -   | ns   |

DS11840 Rev 9 22/90

Table 5. SPI timing parameters (continued)

| Symbol            | Parameter                        | Note/Condition                                                                                     | Min | Тур | Max | Unit |

|-------------------|----------------------------------|----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| <sup>t</sup> ncsh | NCS hold time<br>Read / Write    | Time between last<br>SCLK falling edge<br>and NCS low-high<br>transition after a<br>Read or Write  | 10  | -   | -   | ns   |

| tncsh             | NCS hold time direct command     | Time between last<br>SCLK falling edge<br>and NCS low-high<br>transition after a<br>direct command | 70  | -   | -   | ns   |

|                   | Read timing                      |                                                                                                    |     |     |     |      |

| t <sub>DOD</sub>  | Data out delay                   | $V_{DD\_IO} \ge 3 \text{ V},$ $C_{LOAD} = 50 \text{ pF},$ $hs\_output = 1$                         | -   | 30  | -   | ns   |

| t <sub>DOD</sub>  | Data out delay                   | $V_{DD\_IO} \ge 1.65 \text{ V},$ $C_{LOAD} = 50 \text{ pF},$ $hs\_output = 1$                      | -   | 60  | -   | ns   |

| t <sub>DOD</sub>  | Data out delay                   | $V_{DD\_IO} \ge 3 \text{ V},$ $C_{LOAD} = 50 \text{ pF},$ $hs\_output = 0$                         | -   | 90  | -   | ns   |

| t <sub>DOHZ</sub> | Data out to high impedance delay | Time for the SPI to release the MISO line                                                          | -   | 40  | -   | ns   |

Figure 9 shows the corresponding timing waveforms and parameters for the SPI write command.

Figure 9. SPI Write timing NCS tsclkh tsclkl tncsh **SCLK** t<sub>DIH</sub>  $t_{\text{DIS}}$ MOSI DATA\_I DATA\_I MISO MS50043V1

Figure 10 shows the corresponding timing waveforms and parameters for the SPI read command.

Figure 10. SPI Read timing

## 2.2.5 CLSYS output

The CLSYS output is intended to be used as a MCU clock source. Available frequencies are:

- 4 MHz

- 5 MHz

- 10 MHz

- 20 MHz

The CLSYS frequency is defined by clsys[2:0] option bits in the *Miscellaneous register 2* (0Eh).

#### 2.2.6 IO signal level and output characteristics

The logic high level for the host communication and CLSYS is defined by the supply voltage connected to VDD\_IO pin. The logic high level can be in the range between 1.65 V and 5.5 V. VDD\_IO should be connected to the host system periphery supply voltage to ensure matching communication levels.

The digital outputs are by default configured for high-speed operation. A 5 MHz SPI clock is possible with a 50 pF capacitive load on the MISO and IRQ outputs and a minimum VDD\_IO supply voltage of 3 V. A 3 MHz SPI clock is possible with a 50 pF load and a minimum  $V_{DD\ IO}$  supply voltage of 1.65V.

To decrease the harmonic content of the digital output signals, it is possible to configure the device outputs to provide weak, sloped output signals by setting the hs\_output option bit in the *Miscellaneous register 1* (0Dh) to low. In this configuration the possibility of interferences by the host system communication with other internal building blocks of the device is mitigated as well. Using this option a 2 MHz SPI clock is possible with maximum 50 pF capacitive load on MISO and IRQ and at least a  $V_{\rm DD\ IO}$  supply voltage of 3 V.

It is also possible to define open drain N-MOS outputs by setting the option bit open\_dr high (register 0Dh). This option reduces the harmonic content on the MISO, IRQ, and CLSYS signals further. It also decreases cross-coupling effects that could interfere with operation of other blocks of the device.

# 2.2.7 OAD, OAD2 outputs

The OAD and OAD2 outputs are analog and digital test outputs. When used as analog outputs, the received sub-carrier signals or mixer analog DC output levels are multiplexed at these pins. The signal is centered to AGD level. When used as digital output, the levels are configured with VDD\_IO. The OAD pins can be configured as high speed outputs by setting the option bit hs\_oad in the *Miscellaneous register 1* (0Dh). During normal operation it is not recommended to use hs\_oad, as higher harmonic content can increase the crosstalk to sensitive pins of the device.

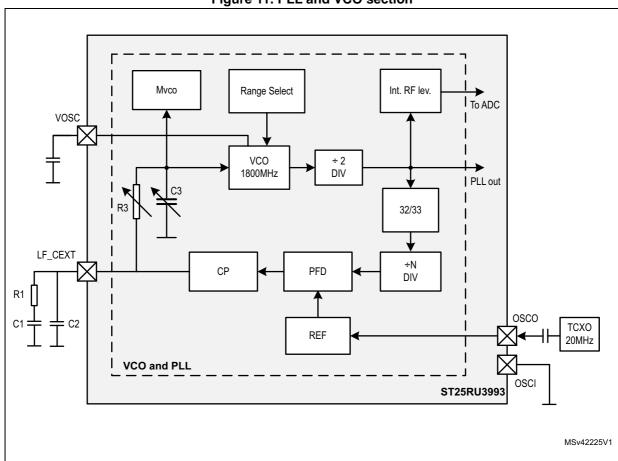

# 2.3 PLL and VCO section

The PLL section comprises a voltage controlled oscillator, a pre-scaler, main and reference dividers, a phase-frequency detector, a charge pump and a loop filter.

Figure 11 shows a detailed block diagram of the PLL and VCO section of the ST25RU3993 device.

Figure 11. PLL and VCO section

> All building blocks, except a section of the loop filter, are integrated in the ST25RU3993. The allowed frequency operation range is 840 MHz to 960 MHz.

#### 2.3.1 Voltage controlled oscillator

The VCO is entirely integrated, including the variable capacitor and inductor. The frequency control input pin is LF\_CEXT. The valid voltage range is between 0.5 V and  $V_{DD\ A}$  - 0.5 V. The option bits eosc[2:0] in the VCO control register (11h) are used for oscillator noise and current consumption optimization. Power supply decoupling is done via VOSC pin. The internal VCO frequency is set in the range of 1800 MHz, which is internally divided by two for decreased VCO pulling effect. The tuning curve of the 1800 MHz VCO is divided into 16 segments (ranges) to decrease the VCO gain and to attain lowest possible phase noise.

#### VCO tuning range selection

The selection of the VCO tuning range can be done manually by setting the option bits vco r[3:0] in the VCO control register(11h). An automatic selection can be started by using the direct command automatic VCO Range Selection (A4h). Reverting back to manual selection is possible by sending the direct command manual VCO range selection (A5h). The automaticautomatic VCO range selection (A4h) command starts a search algorithm that finds the appropriate VCO segment. When the algorithm is finished an IRQ request is sent with Irq\_cmd and autovco\_done status bit in the Command status display register (2Eh) set high.

#### Readout of VCO tuning range status

The result of the automatic segment search algorithm is represented by vco\_ri[7:4], which can be read out from the device via the AGL/VCO/F CAL/PilotFreg status register (r2Cpage[1:0] = 01) (2Ch) when option bits r2Cpage[1:0] = 01b (register 29h).

#### VCO control voltage measurement

It is possible to measure the VCO control voltage by setting option bit mvco in VCO control register (11h) to high. The 3 bits result vco\_ri[2:0] can be read from the AGL/VCO/F\_CAL/PilotFreq status register (r2Cpage[1:0] = 01) (2Ch) using r2Cpage[1:0] = 01b (register 29h). During normal operation, the mvco option bit in register 11h should remain low. Details on using the 1800 MHz VCO are described in a dedicated application note.

#### 2.3.2 PLL prescaler and main divider

The divide-by-32/33 prescaler is controlled by the N-divider. The divider ratio is defined by the PLL main register 1 and PLL main register 3 (17h-19h) or PLL auxiliary register 1 and PLL auxiliary register 3 (1Ah-1Ch). The lower ten bits of the three main (aux.) registers define the A value and the next upper ten bits define the B value. The A and B values define the main divider dividing ratio to:

$$N = B \cdot 32 + A \cdot 33$$

The two registers PLL main register 1 and PLL main register 3 and PLL auxiliary register 1 and PLL auxiliary register 3 are intended to support frequency hopping using the direct commands hop to main frequency (84h) and hop to auxiliary frequency (85h).

# 2.3.3 PLL reference frequency

The reference frequency is selected by the RefFreq[2:0] bits in the *PLL main register 1* (17h). Available values are:

- 125 kHz

- 100 kHz

- 50 kHz

- 25 kHz

# 2.3.4 Reference frequency source

For the reference frequency a frequency source of 20 MHz is required. It is possible to use an external oscillator (TCXO) or a quartz crystal. If a TCXO is used, it should be connected to the OSCO pin while the OSCI pin should be shorted to ground. The signal shape of the TCXO should be of a sinusoidal type and AC coupled. The level should be in the range between 0.8 Vpp and 3 Vpp. A low OSCO level is recommended to minimize the spectral signal components spaced by  $\pm 20$  MHz around the Tx carrier frequency. The OSCO input impedance in this mode is typically 9 k $\Omega$ , with 9 pF in parallel. A crystal should be connected between the OSCI and OSCO pins with appropriate load capacitors in shunt configuration to ground. Load capacitances in the range from 15 pF to 20 pF are recommended. The maximum series resistance in resonance should be 30  $\Omega$ . The crystal oscillator is started-up in fast mode in order to speed-up a stable crystal oscillation. The device then switches back to the power saving mode. The device operation typically uses the power saving mode. Option bits xosc[1:0] in the *Miscellaneous register 2* (0Eh) are available to manually control the crystal operation modes.

# 2.3.5 Phase-frequency detector and charge pump

The reference frequency and the divided RF frequency are compared in the phase-frequency detector that drives the charge pump connected to the LF\_CEXT pin. The charge pump current is selectable between 150  $\mu$ A and 2350  $\mu$ A using option bits cp[2:0] in the *CP control register* (12h).

#### 2.3.6 Loop filter

The loop filter is composed of an external and an internal portion. The first stage (series capacitor, series resistor and shunt capacitor) is external and is connected to the pin LF\_CEXT. The second stage (R3/C3 filter) is internally connected between the LF\_CEXT pin and the VCO control input.

The values for the internal part of the loop filter (R3 and C3) can be selected by option bits LF\_R3[7:6] and LF\_C3[5:3] both in the CP Control Register (12h). R3 can be set in a range from 30 k $\Omega$  to 100 k $\Omega$  and C3 can be set in a range from 20 pF to 200 pF.

# 2.3.7 Frequency hopping commands

Frequency hopping is possible by issuing the direct commands Hop to main frequency (84h) and hop to auxiliary frequency (85h) that set the main divider ratio either to the main or the auxiliary PLL register. The host system (MCU) is responsible to perform correct frequency hopping according to local regulations.

DS11840 Rev 9 27/90

#### 2.3.8 PLL start-up and frequency hopping

Before enabling the RF field, the host system needs to configure the PLL through the CP control register (12h) and the PLL main register 1, PLL main register 2 and PLL main register 3 (17h, 18h, 19h). The PLL should be locked using one of the above defined possibilities. Any time during operating at one frequency, the host system can fill the auxiliary PLL main registers. When the frequency hop needs to be performed only the appropriate frequency hopping direct command needs to be sent to the device.

#### 2.4 **Device status control**

In the Device status control register (00h), the main functionality of the device is controlled. By setting the option bit rf on, the internal transmitter and receiver blocks are enabled. The initial RF field ramp-up is defined by the Tari[2:0] option bits in the Tx options register (02h) and by option bits trfon[1:0] in the *Modulator control register 3*(15h).

The available values are:

- 100 us

- 200 µs

- 400 µs

- TARI determined

When finished, the rf ok bit in the AGC and internal status display register (2Ah) is set and an IRQ with Irq ana bit is sent. By setting the rf on bit low, the RF field is ramped-down similarly to the ramp-up transient and an IRQ with Irq ana bit set is sent. The rec on bit enables the receiver only. The agc on bit enables the AGC functionality. The stby bit puts the device into the standby mode.

#### 2.5 Protocol control

In the *Protocol selection register* (01h), the main protocol parameters are selected. The prot[2:0] option bits should be set to 000b for EPC Class1 Gen2 operation and to 001b for ISO18000-6A/B FM0 decoder operation. The AutoACK[1:0] bits enables the automatic inventory round sequencing and define its depth. There are three possible modes:

- No automatic

- Automatic ACK

- Automatic ACK + RegRN

The option bit RX\_crc\_n = 1 defines reception with no internal CRC check. The CRC is then just passed on to the FIFO like any other data bytes. In the EPC Gen 2 protocol this is a useful feature in case of a truncated EPC reply, where the stored CRC that a transponder transmits is not calculated over the actual transmitted data and is therefore an invalid CRC. The dir mode bit defines the type of output signals while operating in the direct mode. It also disables any decoding and signal sensing automatics during the reception. It is advised to set this bit high when continuous analog measurements are performed.

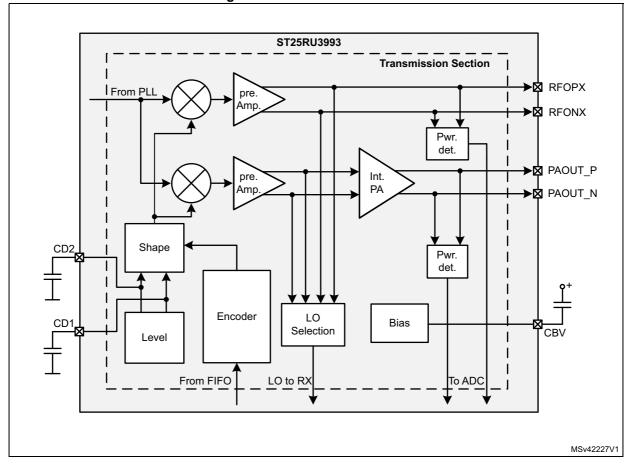

### 2.6 Transmission section

The transmitter section comprises a data handling, an encoding part, a shaping circuitry, a modulator and amplifier circuitry.

Figure 12. Transmission section

The RF carrier is modulated with a shaped representation of the transmit data and (pre-)amplified for transmission.

# 2.6.1 Tx data handling and coding

The data handling part takes the baseband data from the FIFO and encodes it according to the Gen2 protocol (PIE). It adds a preamble or a frame-sync and calculates the CRC. The digital modulation signals are fed to the shape circuitry.

# 2.6.2 Tx shape circuitry

The modulation shape is controlled by a double D/A converter. The first 5-bit logarithmic converter creates two voltages, which define minimum and maximum (Vpp) modulation signal level. The two voltages are filtered by two external capacitors connected to the CD1 and CD2 pins to minimize the noise level and are used as a reference for the shaping circuitry. The second 9-bit linear converter transforms the digital modulation signal into a sinusoidal or linear shaped analog modulation signal. The output of the shaping circuit is interpolated and connected to the modulator input.

57

DS11840 Rev 9 29/90

# 2.6.3 Local oscillator (LO) path

To improve the phase noise rejection, the local oscillator signal is derived from the output of the pre-amplifier stages. For optimal operation, the pre-amplifier levels should be close to nominal (set by TX\_lev[4:0] in register 15h). If lower levels are used, the LO signal can be increased by approximately 6 dB using option bit eTX[7]. The drawback is increased received noise.

#### 2.6.4 Modulator

The modulator modulates the RF carrier with the shaped representation of the digital modulation signal. The internal modulator is capable of ASK and PR-ASK modulation.

# Tx level and shape adjustments

The output level and modulation shape properties are controlled by the *Modulator control register 1* and *Modulator control register 4* (13h-16h). The level of the output signal is adjusted by option bits TX\_lev[4:0] in *Modulator control register 3*(15h). For good performance, it is advised to design the external circuit of the reader device to have the reader output power close to the ST25RU3993 nominal output power. If temporarily operation at decreased power is need the TX\_lev[4:0] option bits should be used.

Sinusoidal or linear shape is defined by the option bit lin\_mod in register (15h). PR-ASK modulation is selected by setting the pr\_ask option bit to high. If PR-ASK is selected, the del\_len[5:0] option bits are used to adjust the delimiter length in the range from 9.6  $\mu$ s to 15.9  $\mu$ s. For Tari = 25  $\mu$ s PR-ASK and ASK delimiter shapes are available. The ASK transient which gives more accurate timing can be selected by the ook\_ask option bit in register 15h. For Tari = 12.5  $\mu$ s and 6.25  $\mu$ s only the ASK delimiter shape is available.

ASK modulation is selected by setting the pr\_ask option bit to low. In ASK modulation it is possible to adjust the delimiter length by setting the option bit ook\_ask. In this case, ook\_ask defines 100% ASK modulation and the del\_len[5:0] bits are used for delimiter length setting as in the PR-ASK mode described above.

The rate of the modulation transient is automatically adjusted to the selected Tari setting and can be re-adjusted by the ask\_rate[1:0] option bits (register 13h). For smoother transitions of the modulation signal an optional low pass filter can be activated by the e\_lpf option bit in the *Modulator control register 1* (13h). Bits aux\_mod and main\_mod define whether the modulation signal will be connected to the low-power output or to the internal PA output path. If one of the outputs is enabled by the eTX[3:0] bits in *RF output and LO control register* (0Ch) and corresponding aux\_mod or main\_mod bit is low, the output is enabled but not modulated (the device would output only a continuous wave signal).

# 2.7 Tx outputs

Two Tx differential output ports are available:

- Differential low-power, high linear output (nom. 0 dBm)

- Differential high power output (nom. 20 dBm)

The low-power output can be used to drive an external PA to generate a high power RF signal. The internal high power output can be used to directly drive an antenna suitable for applications with low to medium read range requirements.

#### low-power output

The differential low-power, high linear RF outputs ( $\sim$ 0 dBm) are intended to be used to drive an external amplifier. The RF outputs composed of RFOPX and RFONX pins need external RF chokes connected to VDD\_B, decoupling capacitors and a Balun with 2:1 impedance ratio for optimal operation in a 50  $\Omega$  system. The output is enabled by eTX[1:0] bits in the *RF output and LO control register* (0Ch). By using these bits, it is possible to adjust current capability of the RF output pins.

### High power output

The differential high power output pins are the outputs of the internal power amplifier outputs PAOUT\_P and PAOUT\_N. They require external RF chokes, connected to VDD\_PA and an impedance matching circuit for operation in a 50  $\Omega$  system. The amplifier is enabled by the eTX[4] and eTX[3:2] option bits in register 0Ch. Bit eTX[3:2] also define the bias of the internal pre-amplifier stage. The PA supply regulator is automatically enabled when the internal PA is enabled. The bias current for the internal PA is defined by the option bits pa\_bias[1:0] in the *Regulator and PA bias register* (0Bh).

# 2.8 Tx operation modes

#### 2.8.1 TX normal mode

The baseband data is transferred to the 24 byte FIFO and the complete signal processing (protocol encoding, adding preamble or frame-sync, CRC, signal shaping, and modulation) is done internally. The data is then coded to the modulation pulse level and sent to the modulator. This means that the MCU has only to load the FIFO with data.

#### **Transmission start**

There are three possibilities to start data transmission in the normal mode.

The first one is data transmission that can be triggered by sending related direct commands:

- Transmission with CRC (90h)

- Transmission with CRC Expecting Header Bit (91h)

- Transmission without CRC (92h)

followed by information about the number of bytes that should be transmitted and the baseband data. The number of bytes that needs to be written into the *Tx length register 1* and *Tx length register 2* (3Dh, 3Eh) and the data itself should be put into the *FIFO I/O register* (3Fh). Both operations can be done with one continuous Write command. The transmission is started when the first data byte is completely written to the FIFO.

DS11840 Rev 9 31/90

The second possibility to trigger the transmission is with one of the direct commands related to the EPC Class1 Gen2 protocol:

- Inventory Commands:

- Query (98h)

- QueryRep (99h)

- QueryAdjustUp (9Ah)

- QueryAdjustNic (9Bh)

- QueryAdjustDown (9Ch)

- ACK (9Dh)

- RegRN (9Fh)

In this case, the transmission is started upon receiving the command.

The third possibility for data transmission is using one of the AutoACK modes. In this case the ACK or RegRn is sent automatically if the previous reception was successful.

During data transmission, the TX\_status bit in the *FIFO status register* (39h) is set. When the data transmission is finished, the reader device signals an IRQ request with Irq\_TX bit set high.

### **Protocol adjustments**

The EPC Class1 Gen 2 protocol allows the user to adjust transmission parameters. The three supported Tari values are selected by changing the Tari[1:0] option bits in the *Tx options register* (02h). The length of the high period of the (PIE encoded) logical one is selected by TXOne[1:0] option bits in the *Tx options register* (02h). The session parameters for the direct command Query (98h) are defined by the S1 and S0 option bits in the *Tx setting register* (3Ch). TRcal, which defines the backscatter link frequency, is incorporated in the Query command transmission. TRcal is defined by option bits TRcal[11:0] in the TRcal Registers (04h, 05h).

#### Caution:

The software designer needs to take care that bits TRcal[11:0], RX\_LF[3:0] and the DR bit in the transmission of the Query command follow the Gen2 protocol. A precise description can be found in the EPC Class1 Gen2 or ISO18000-6C protocol description. If TRcal data is required in normal transmission, it can be set by Force\_TRcal option bit in the *Tx setting register* (3Ch). The cyclic redundancy check can be changed to CRC-5 instead of CRC-16. This is done in normal transmission by setting TXCRC\_5 option bit in the *Tx setting register* (3Ch) to high.

#### **Transmission FIFO**

The reader device supports two fully separate 24-byte FIFO buffer registers, one for transmission and one for reception. They share the same address. By writing to FIFO address 3Fh the data will be passed to transmission FIFO, while reading from the register address 3Fh will fetch the values from the reception FIFO. This approach makes it possible to start a new transmission before the previously received data is read out by the MCU.

If the data bytes to transmit exceed the size of the FIFO buffer, the MCU should initially fill the FIFO register with 24 bytes. The reader device starts the transmission and sends an interrupt request, signaled by irq\_fifo in the *Interrupt register 1* (37h), when only 6 bytes are left in the FIFO. When the interrupt is received, the MCU needs to read from register 37h. By reading this register, the host system will know the cause for the interrupt and at the same time clear the interrupt bit. After this the MCU puts the remaining transmission data bytes to the FIFO considering the available FIFO size. If all transmission data bytes were

already sent to the FIFO, the host system waits until the last data byte has been sent. The end of the transmission is signaled to the MCU by the IRQ request irq\_TX in register 37h. The two *Tx length register 1* and *Tx length register 2* (3Dh, 3Eh) support incomplete byte transmission. The MCU needs to define the number of complete bytes and the number of the remaining bits that should be transmitted.

#### 2.8.2 TX direct mode

Direct mode is chosen when using only analog functions, bypassing all the protocol handling support of the reader device.

## Entering and terminating the direct mode

To enter the direct mode the direct command direct mode (81h) should be sent followed by a NCS low-to-high transition. The direct mode remains active as long as NCS is kept high. To terminate the direct mode the direct command block Rx (96h) needs to be sent immediately after the NCS high-to-low transition. During the same or consecutive NCS low periods normal communication via the SPI interface is possible again.

#### **Direct Mode Signals**

The *Table 6* shows the re-assignments of the I/O pins during the direct mode. The different reception outputs options are related to the dir\_mode option bit in the *Protocol selection register* (01h).

| Pin Name | Bit Stream and Bit Clock Output<br>(dir_mode = 0) | Sub Carrier Output<br>(dir_mode = 1) |  |  |

|----------|---------------------------------------------------|--------------------------------------|--|--|

| MOSI     | Tx data input                                     | Tx data input                        |  |  |

| SCLK     | Enable Rx input                                   | Enable Rx input                      |  |  |

| MISO     | Rx data output                                    | I-Channel subcarrier output          |  |  |

| IRQ      | Rx bit clock output                               | Q-Channel subcarrier output          |  |  |

Table 6. I/O pin reassignment in direct mode