# DESCRIPTION

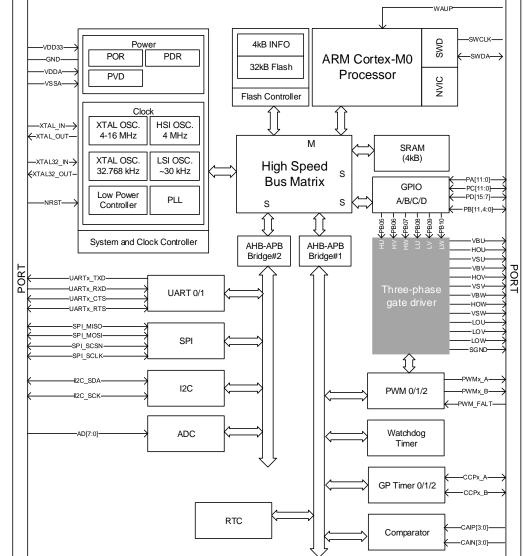

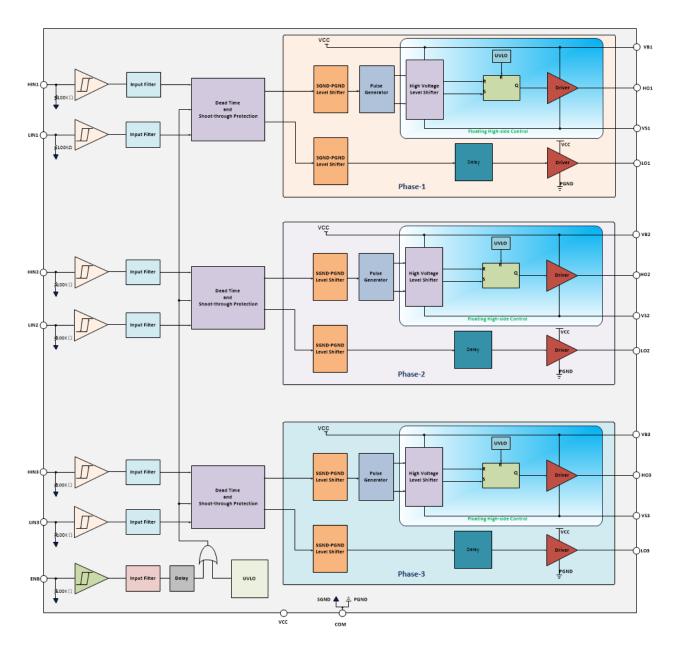

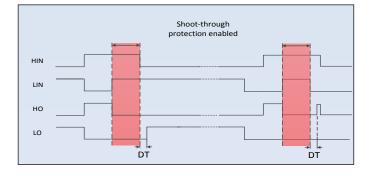

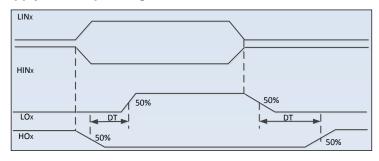

The PT32M625 is a SiP (System in Package) with mcu PT32U301 and a motor gate driver PT5619. The PT32M625 microcontroller is a series of low-power microcontroller incorporating a high-performance ARM CortexTM-M0 32-bit RISC core. It operates at a maximum 48Mhz frequency and features up to 32Kbytes of Flash and up to 4Kbytes of SRAM. The PT5619 is a high-speed 3-phase gate driver for power MOSFET and IGBT devices with three independent high and low side referenced output channels. Built-in dead time protection and shoot-through protection prevent damage to the half-bridge.

# FEATURES

- ARM Cortex M0 Processor

- Performance up to 48 MHz

- Flash Memory 32K-Byte

- System SRAM 4K-Byte

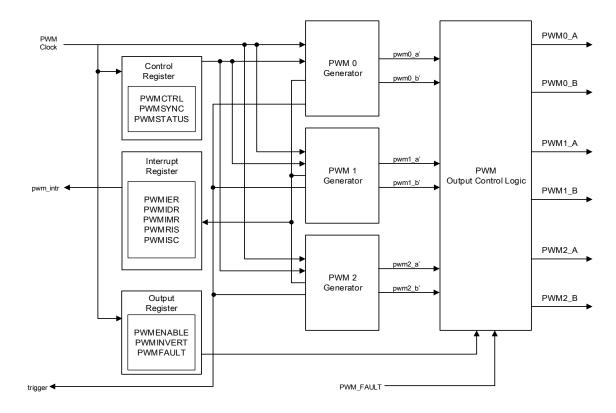

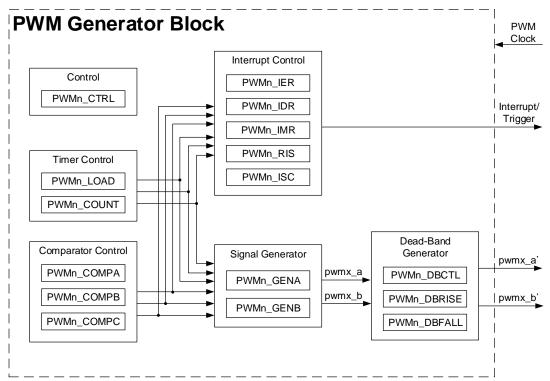

- PWM Mode control logic

- PT5619

- 90V half-bridge high side driver

- Driver up to 3-phase half-bridge gates

- Built-in dead time control 0.5µs (typ.)

- Shoot-through protection

- Common-mode dV/dt noise cancellation circuit

- Tolerant of negative transient voltage

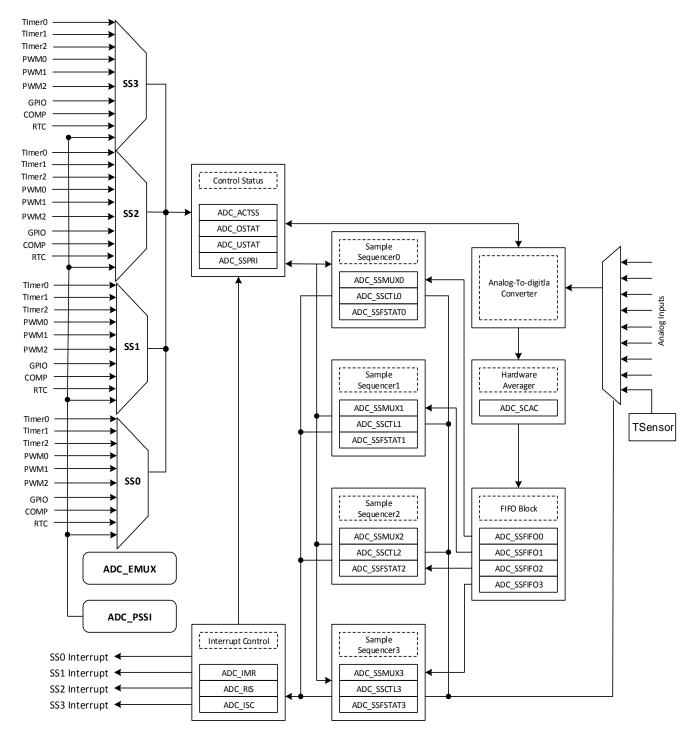

# BLOCK DIAGRAM

## CONTENT

| 2. PIN CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1 MULTIPLEXING PINS FUNCTION SELECTION53.2 SIGNAL DESCRIPTION74. FUNCTIONAL DESCRIPTION84.1 SYSTEM AND MEMORY OVERVIEW84.2 ARM ® CORTEX™-M0 CORE114.3 SYSTEM CONTROL (SC)344.4 FLASH CONTROLLER (FC)674.5 GENERAL PURPOSE I/O (GPIO)714.6 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER (UART)844.7 PULSE WIDTH MODULATION (PWM)1104.8 ANALOG TO DIGITAL CONVERTER (ADC)1454.9 GENERAL PURPOSE TIMERS (GPT)1784.10 ANALOG COMPARATOR (AC)2044.11 WATCH DOG TIMER (WDT)214                                                                                                                                       |

| 3.2 SIGNAL DESCRIPTION74. FUNCTIONAL DESCRIPTION84.1 SYSTEM AND MEMORY OVERVIEW84.2 ARM ® CORTEX™-M0 CORE114.3 SYSTEM CONTROL (SC)344.4 FLASH CONTROLLER (FC)674.5 GENERAL PURPOSE I/O (GPIO)714.6 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER (UART)844.7 PULSE WIDTH MODULATION (PWM)1104.8 ANALOG TO DIGITAL CONVERTER (ADC)1454.9 GENERAL PURPOSE TIMERS (GPT)1784.10 ANALOG COMPARATOR (AC)2044.11 WATCH DOG TIMER (WDT)214                                                                                                                                                                                |

| 4. FUNCTIONAL DESCRIPTION.       .8         4.1 SYSTEM AND MEMORY OVERVIEW.       .8         4.2 ARM ® CORTEX™-M0 CORE       .11         4.3 SYSTEM CONTROL (SC)       .34         4.4 FLASH CONTROLLER (FC).       .67         4.5 GENERAL PURPOSE I/O (GPIO)       .71         4.6 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER (UART)       .84         4.7 PULSE WIDTH MODULATION (PWM)       .110         4.8 ANALOG TO DIGITAL CONVERTER (ADC)       .145         4.9 GENERAL PURPOSE TIMERS (GPT)       .178         4.10 ANALOG COMPARATOR (AC)       .204         4.11 WATCH DOG TIMER (WDT)       .214 |

| 4.1 SYSTEM AND MEMORY OVERVIEW       .8         4.2 ARM ® CORTEX™-M0 CORE       .11         4.3 SYSTEM CONTROL (SC)       .34         4.4 FLASH CONTROLLER (FC)       .67         4.5 GENERAL PURPOSE I/O (GPIO)       .71         4.6 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER (UART)       .84         4.7 PULSE WIDTH MODULATION (PWM)       .110         4.8 ANALOG TO DIGITAL CONVERTER (ADC)       .145         4.9 GENERAL PURPOSE TIMERS (GPT)       .178         4.10 ANALOG COMPARATOR (AC)       .204         4.11 WATCH DOG TIMER (WDT)       .214                                               |

| 4.2 ARM ® CORTEX™-M0 CORE       11         4.3 SYSTEM CONTROL (SC)       34         4.4 FLASH CONTROLLER (FC)       67         4.5 GENERAL PURPOSE I/O (GPIO)       71         4.6 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER (UART)       84         4.7 PULSE WIDTH MODULATION (PWM)       110         4.8 ANALOG TO DIGITAL CONVERTER (ADC)       145         4.9 GENERAL PURPOSE TIMERS (GPT)       178         4.10 ANALOG COMPARATOR (AC)       204         4.11 WATCH DOG TIMER (WDT)       214                                                                                                         |

| 4.3 SYSTEM CONTROL (SC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.4 FLASH CONTROLLER (FC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.5 GENERAL PURPOSE I/O (GPIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

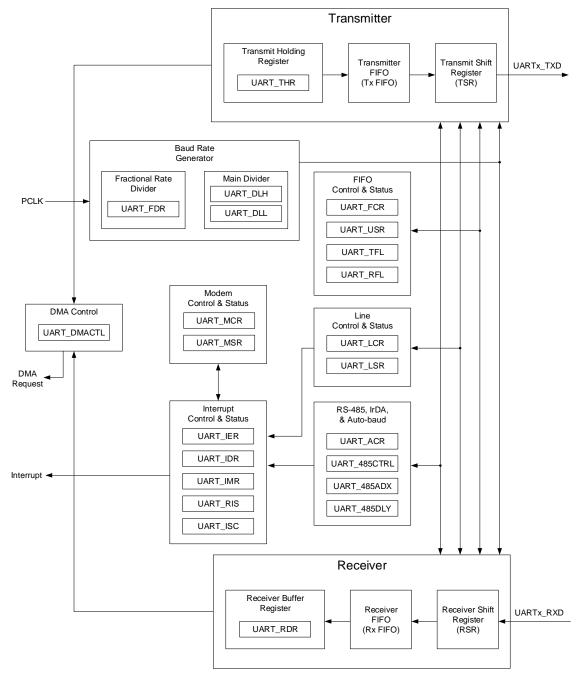

| 4.6       UNIVERSAL ASYNCHRONOUŚ RECEIVER/TRANSMITTER (UART)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.7 PULSE WIDTH MODULATION (PWM)       110         4.8 ANALOG TO DIGITAL CONVERTER (ADC)       145         4.9 GENERAL PURPOSE TIMERS (GPT)       178         4.10 ANALOG COMPARATOR (AC)       204         4.11 WATCH DOG TIMER (WDT)       214                                                                                                                                                                                                                                                                                                                                                                |

| 4.8 ANALOG TO DIGITAL CONVERTER (ADC)       145         4.9 GENERAL PURPOSE TIMERS (GPT)       178         4.10 ANALOG COMPARATOR (AC)       204         4.11 WATCH DOG TIMER (WDT)       214                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.9 GENERAL PURPOSE TIMERS (GPT)       178         4.10 ANALOG COMPARATOR (AC)       204         4.11 WATCH DOG TIMER (WDT)       214                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

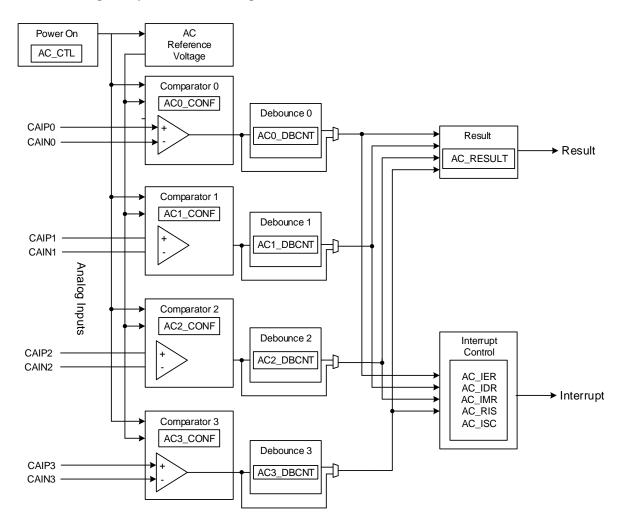

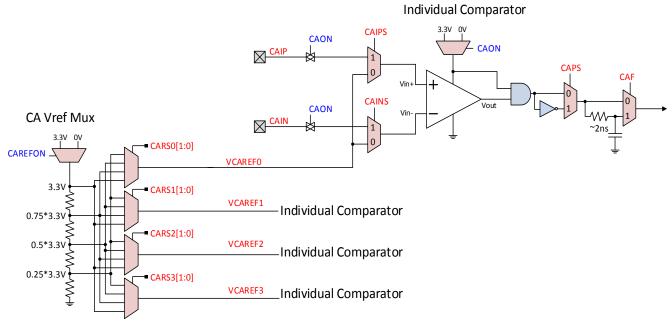

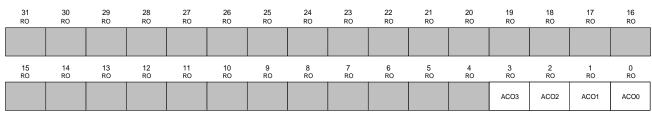

| 4.10 ANALOG COMPARATOR (AC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

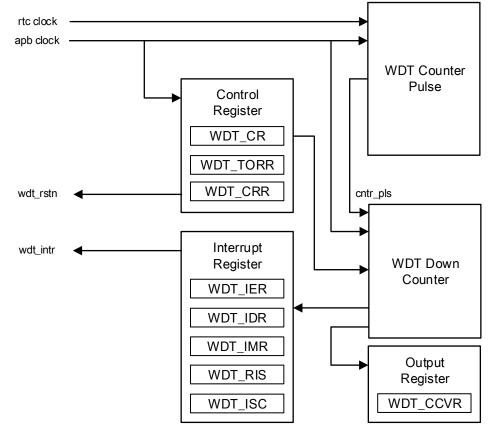

| 4.11 WATCH DOG TIMER (WDT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.12 REAL TIME CLOCK (RTC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

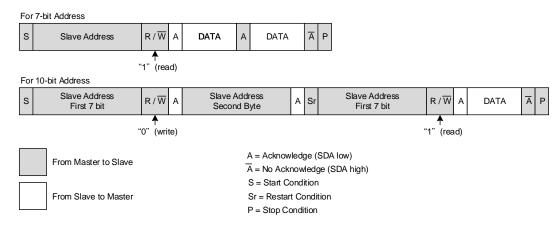

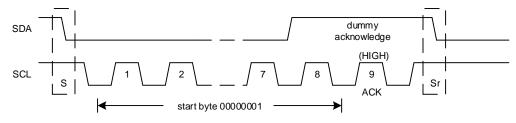

| 4.13 INTER INTEGRATED CIRCUIT (I2C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

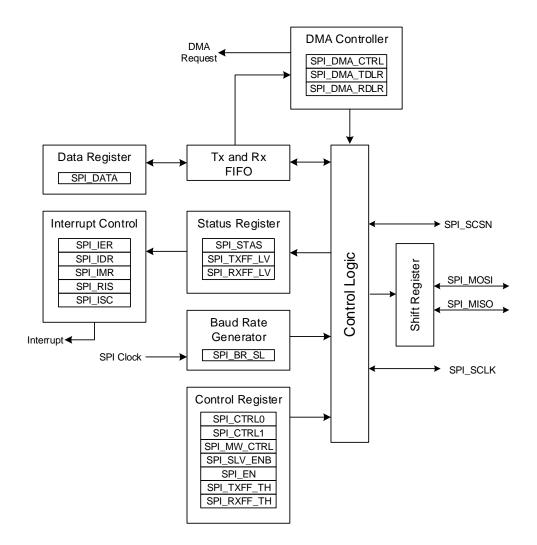

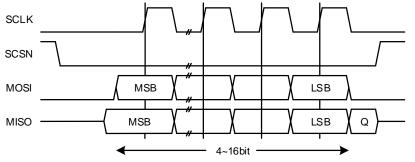

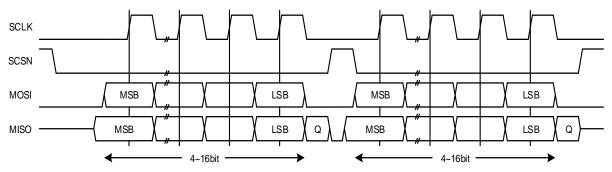

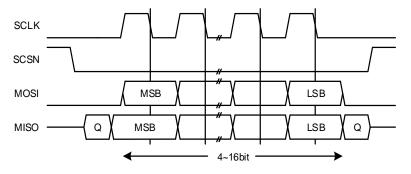

| 4.14 SERIAL PERIPHERAL INTERFACE (SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.15 PT5619 FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5. PT32U301 ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.1 MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.2 OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.3 I/O PIN CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.4 ON-CHIP LOW DROP-OUT(LDO) REGULATOR CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.5 PHASE LOCKED LOOP CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.6 POWER-ON RESET CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.7 NRST CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.8 8 MHZ XTAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.9 4 MHZ RCOSC CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.10 32 KHZ XTAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.11 TEMPERATURE SENSOR CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

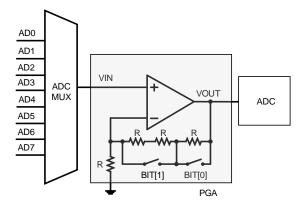

| 5.12 ADC+ PGA CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.13 COMPARATOR CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.14 RCOSC_32K CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.15 POWER CONSUMPTION TABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6 PT5619 ELECTRICAL CHARACTERISTIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.1 ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.2 RECOMMENDED OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.2 RECOMMENDED OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.2       RECOMMENDED OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.2 RECOMMENDED OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# **1. ORDER INFORMATION**

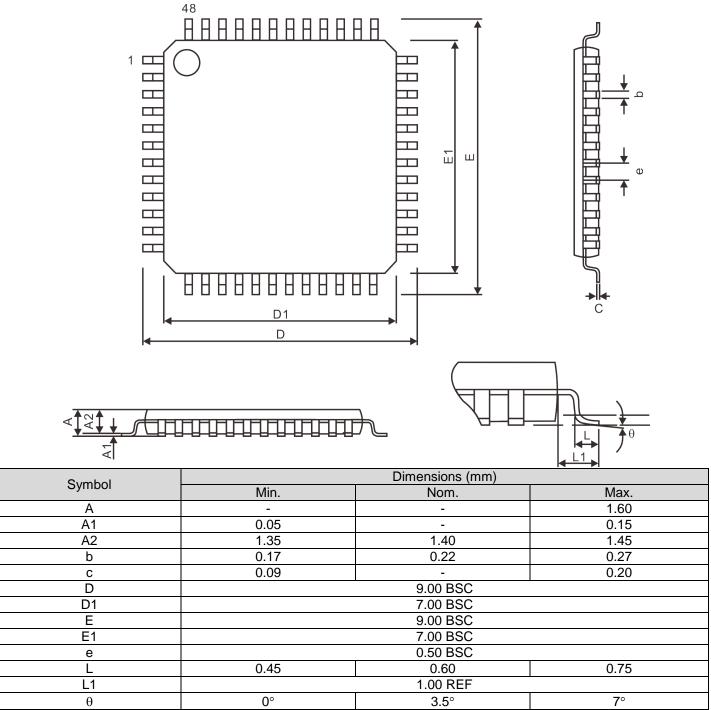

| Valid Part Number | Package Type | Top Code    |

|-------------------|--------------|-------------|

| PT32M625-LQ       | LQFP 48      | PT32M625-LQ |

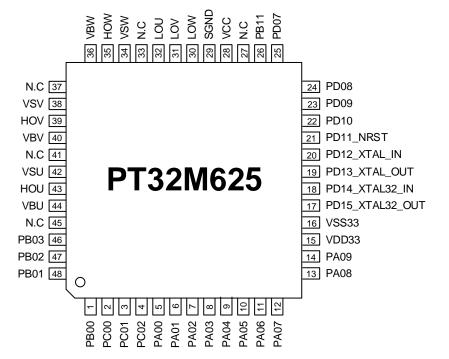

# **2. PIN CONFIGURATION**

# **3. PIN DESCRIPTION**

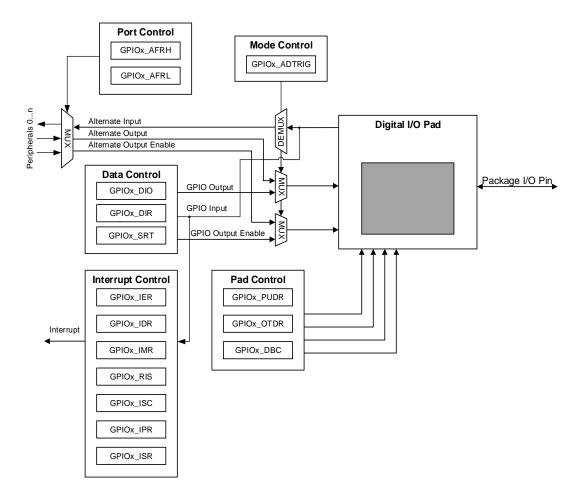

Each GPIO line can be assigned to one of the peripheral functions. The following table lists out the pin name of all packages and its respective available alternate function.

| Pin Name        | Pin Type | Description                                             | Pin No.            |

|-----------------|----------|---------------------------------------------------------|--------------------|

| PB00            | I/O      | General Purpose Digital I/O Pin                         | 1                  |

| PC00            | I/O      | General Purpose Digital I/O Pin                         | 2                  |

| PC01            | I/O      | General Purpose Digital I/O Pin                         | 3                  |

| PC02            | I/O      | General Purpose Digital I/O Pin                         | 4                  |

| PA00            | I/O      | General Purpose Digital I/O Pin                         | 5                  |

| PA01            | I/O      | General Purpose Digital I/O Pin                         | 6                  |

| PA02            | I/O      | General Purpose Digital I/O Pin                         | 7                  |

| PA03            | I/O      | General Purpose Digital I/O Pin                         | 8                  |

| PA04            | I/O      | General Purpose Digital I/O Pin                         | 9                  |

| PA05            | I/O      | General Purpose Digital I/O Pin                         | 10                 |

| PA06            | I/O      | General Purpose Digital I/O Pin                         | 11                 |

| PA07            | I/O      | General Purpose Digital I/O Pin                         | 12                 |

| PA08            | I/O      | General Purpose Digital I/O Pin                         | 13                 |

| PA09            | I/O      | General Purpose Digital I/O Pin                         | 14                 |

| VDD33           | Supply   | 3.3V Voltage Supple                                     | 15                 |

| VSS33           | Ground   | Ground                                                  | 16                 |

| PD15_XTAL32_OUT | I/O      | General Purpose Digital I/O Pin                         | 17                 |

| PD14_XTAL32_IN  | I/O      | General Purpose Digital I/O Pin                         | 18                 |

| PD13_XTAL_OUT   | I/O      | General Purpose Digital I/O Pin                         | 19                 |

| PD12_XTAL_IN    | I/O      | General Purpose Digital I/O Pin                         | 20                 |

| PD11_NRST       | I/O      | General Purpose Digital I/O Pin                         | 21                 |

| PD10            | I/O      | General Purpose Digital I/O Pin                         | 22                 |

| PD09            | I/O      | General Purpose Digital I/O Pin                         | 23                 |

| PD08            | I/O      | General Purpose Digital I/O Pin                         | 24                 |

| PD07            | I/O      | General Purpose Digital I/O Pin                         | 25                 |

| PB11            | I/O      | General Purpose Digital I/O Pin                         | 26                 |

| N.C.            | -        | No Connection                                           | 27, 33, 37, 41, 45 |

| VCC             | Supply   | Voltage Supply                                          | 28                 |

| SGND            | Ground   | Logic Ground And Low-Side Gate Drivers Ground           | 29                 |

| LOW             | 0        | Phase-W Low-Side Gate Driver Output                     | 30                 |

| LOV             | 0        | Phase-V Low-Side Gate Driver Output                     | 31                 |

| LOU             | 0        | Phase-U Low-Side Gate Driver Output                     | 32                 |

| VSW             | Supply   | Phase-W High-Side Driver Floating Supply Offset Voltage | 34                 |

| HOW             | 0        | Phase-W High-Side Driver Output                         | 35                 |

| VBW             | Supply   | Phase-W High-Side Driver Floating Supply                | 36                 |

| VSV             | Supply   | Phase-V High-Side Driver Floating Supply Offset Voltage | 38                 |

| HOV             | 0        | Phase-V High-Side Driver Output                         | 39                 |

| VBV             | Supply   | Phase-V High-Side Driver Floating Supply                | 40                 |

| VSU             | Supply   | Phase-U High-Side Driver Floating Supply Offset Voltage | 42                 |

| HOU             | 0        | Phase-U High-Side Driver Output                         | 43                 |

| VBU             | Supply   | Phase-U High-Side Driver Floating Supply                | 44                 |

| PB03            | I/O      | General Purpose Digital I/O Pin                         | 46                 |

| PB02            | I/O      | General Purpose Digital I/O Pin                         | 47                 |

| PB01            | I/O      | General Purpose Digital I/O Pin                         | 48                 |

## 3.1 MULTIPLEXING PINS FUNCTION SELECTION

The following tables describes PT32M625's microcontroller's available pin and its corresponding alternate function. The peripheral signals multiplexed to the GPIO lines. Alternate Function (AF) is enabled by configuring the GPIOx\_AFRL and GPIOx\_AFRH registers.

Altermete Frunctions

Note: In the microcontroller, all pins are in AF0 mode by default, with the exception of following cases:

- Crystal Oscillator Pinout: Respective pins PD [15:11] are defaulted to the AF8 functionality.

- Serial Wire Debug Interface Pinout: Respective PB [6:5] are defaulted to the AF6 functionality.

- \*: To enable PT32M625 gate driver functionality, PB [10:5] must be configured to AF7 (PWM signal).

- Some pins are not availiabled in PT32M625.

| Pin Name               |      |           |                      |          | Alternate Functions |        |           |         |           |  |  |  |  |

|------------------------|------|-----------|----------------------|----------|---------------------|--------|-----------|---------|-----------|--|--|--|--|

| Pin Name               | AF0  | AF1       | AF2                  | AF3      | AF4                 | AF5    | AF6       | AF7     | AF8       |  |  |  |  |

| PC06                   |      |           |                      |          |                     |        |           |         |           |  |  |  |  |

| PC07                   |      |           |                      |          |                     |        |           |         |           |  |  |  |  |

| PC08                   |      |           |                      |          |                     |        |           |         |           |  |  |  |  |

| PC09                   |      |           |                      |          |                     |        |           |         |           |  |  |  |  |

| PC10                   |      |           |                      |          |                     |        |           |         |           |  |  |  |  |

| PC11                   |      |           |                      |          |                     |        |           |         |           |  |  |  |  |

| PA00                   | PA00 |           |                      | SPI_MISO | PWM1_A              | CCP1_A |           |         | AD0_CAIP0 |  |  |  |  |

| PA01                   | PA01 | UART0_RTS | I <sup>2</sup> C_SDA | SPI_MOSI | PWM1_B              | CCP1_B | UART1_RXD |         | AD1_CAIN0 |  |  |  |  |

| PA02                   | PA02 |           | UART1_TXD            | SPI_MISO | PWM2_A              | CCP2_A |           |         | AD2_CAIP1 |  |  |  |  |

| PA03                   | PA03 |           | UART1_RXD            | SPI_MOSI | PWM2_B              | CCP_2B |           |         | AD3_CAIN1 |  |  |  |  |

| PA04                   | PA04 | UART1_TXD |                      |          | PWM1_A              | CCP1_A |           |         | AD4       |  |  |  |  |

| PA05                   | PA05 | UART1_RXD |                      |          | PWM1_B              | CCP1_B |           |         | AD5       |  |  |  |  |

| PA06                   | PA06 | UART1_CTS |                      |          | PWM2_A              | CCP2_A |           |         | AD6       |  |  |  |  |

| PA07                   | PA07 | UART1_RTS |                      |          | PWM2_B              | CCP2_B |           |         | AD7       |  |  |  |  |

| PA08                   | PA08 | UART1_TXD | I <sup>2</sup> C_SDA |          | PWM0_A              | CCP1_A |           |         | CAIP2     |  |  |  |  |

| PA09                   | PA09 |           | UART1_RTS            | SPI_SCSN | PWM0_B              | CCP0_B |           |         | CAIN2     |  |  |  |  |

| PA10                   | PA10 |           |                      |          |                     |        |           |         | CAIP3     |  |  |  |  |

| PA11                   | PA11 |           |                      |          |                     |        |           |         | CAIN3     |  |  |  |  |

| VDDA                   |      |           |                      |          |                     |        |           |         |           |  |  |  |  |

| VSSA                   |      |           |                      |          |                     |        |           |         |           |  |  |  |  |

| PD15<br>XTAL32_O<br>UT |      |           |                      |          |                     |        |           |         |           |  |  |  |  |

| PD14_<br>XTAL32_IN     |      |           |                      |          |                     |        |           |         |           |  |  |  |  |

| PD13_<br>XTAL_OUT      | PD13 |           |                      |          |                     |        |           |         | XTAL_OUT  |  |  |  |  |

| PD12_<br>XTAL_IN       | PD12 |           |                      |          |                     |        |           |         | XTAL_IN   |  |  |  |  |

| PD11_<br>NRST          | PD11 |           |                      | SPI_SCSN | PWM_FALT            | CCP1B  | PWM1_B    |         | NRST      |  |  |  |  |

| PD10                   | PD10 |           |                      |          | PWM_FALT            |        |           |         | WKUP_V33  |  |  |  |  |

| PD09                   | PD09 |           |                      | SPI_SCSN |                     |        |           |         |           |  |  |  |  |

| PD08                   | PD08 |           |                      | SPI_SCKK |                     |        |           |         |           |  |  |  |  |

| PD07                   | PD07 |           |                      |          |                     |        |           |         |           |  |  |  |  |

| PB11                   | PB11 |           |                      |          |                     |        |           |         |           |  |  |  |  |

| PB10                   | PB10 |           |                      | SPI_SCLK |                     |        |           | PWM2_B* |           |  |  |  |  |

## PT32M625

| Pin Name |      |                      |                      |          | Alternate Fund | tions     |         |         |  |

|----------|------|----------------------|----------------------|----------|----------------|-----------|---------|---------|--|

| PB09     | PB09 |                      |                      | SPI_MISO |                |           |         | PWM1_B* |  |

| PB08     | PB08 |                      | UART1_TXD            | SPI_MOSI | PWM_FALT       |           |         | PWM0_B* |  |

| PB07     | PB07 | I <sup>2</sup> C_SDA | UART1_RXD            | SPI_SCSN | PWM2_B         |           |         | PWM2_A* |  |

| PB06     | PB06 | UART0_CTS            | UART1_CTS            | SPI_MOSI | PWM2_A         | UART0_TXD | SWCLK   | PWM1_A* |  |

| PB05     | PB05 | UART0_RTS            | UART1_RTS            | SPI_MISO | PWM1_B         | UART0_RXD | SWDA    | PWM0_A* |  |

| VDD33    |      |                      |                      |          |                |           |         |         |  |

| PB04     |      |                      |                      |          |                |           |         |         |  |

| PB03     | PB03 |                      |                      | SPI_MOSI |                | UART0_RXD | SWCLK   |         |  |

| PB02     | PB02 | UART0_CTS            | I <sup>2</sup> C_SCK | SPI_SCKK | PWM1_A         | CCP1_A    | SWDA    | MCO     |  |

| PB01     | PB01 | UART0_TXD            | I <sup>2</sup> C_SCK | SPI_SCSN | PWM0_B         | CCP0_B    |         |         |  |

| PB00     | PB00 | UART0_RXD            | I <sup>2</sup> C_SDA | SPI_MISO | PWM0_A         | CCP0_A    |         |         |  |

| PC00     | PC00 |                      |                      |          | PWM_FALT       |           | RTC_1HZ | PWM2_B  |  |

| PC01     | PC01 |                      |                      |          |                |           |         | PWM1_B  |  |

| PC02     | PC02 |                      |                      |          |                |           |         | PWM0_B  |  |

| PC03     |      |                      |                      |          |                |           |         |         |  |

| PC04     |      |                      |                      |          |                |           |         |         |  |

| PC05     |      |                      |                      |          |                |           |         |         |  |

## 3.2 SIGNAL DESCRIPTION

The following table describes the details on signals names classified by peripheral.

#### Table 3.2-1 : Alternate Function Description

| Table 5.2-1 . Alternate Funct  | 1          |                                                            |

|--------------------------------|------------|------------------------------------------------------------|

| Function Name                  | I/O        | Function Description                                       |

|                                |            | ansmitter (UART0, UART1), x = 0, 1                         |

| UARTx_TXD                      | 0          | UART x Data output pins                                    |

| UARTx_RXD                      |            | UART x Data Input pins                                     |

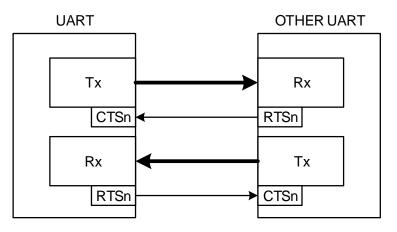

| UARTx_CTSn                     | I/O        | UART x Clear to Send pins                                  |

| UARTx_RTSn                     | I/O        | UART x Request to Send pins                                |

| Serial Wire Debug (SWD)        |            |                                                            |

| SWCLK                          |            | SWD Clock                                                  |

| SWDA                           | I/O        | SWD Data Input/Output                                      |

| Inter Intergrated Circuit (I20 |            |                                                            |

| I2C_SDA                        | I/O        | I2C Data                                                   |

| I2C_SCK                        | I/O        | I2C Clock                                                  |

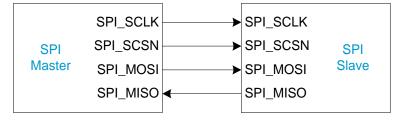

| Serial Peripheral Interface    | (SPI)      |                                                            |

| SPI_MISO                       | I/O        | SPI Master Input Slave Output                              |

| SPI_MOSI                       | I/O        | SPI Master Output Slave Input                              |

| SPI_SCSN                       | I/O        | SPI Chip Select                                            |

| SPI_SCLK                       | I/O        | SPI Clock                                                  |

| General Purpose Input/Out      | put (GPIO) |                                                            |

| PA11-PA00                      | I/O        | GPIO Port A                                                |

| PB11-PB00                      | I/O        | GPIO Port B                                                |

| PC11-PC00                      | I/O        | GPIO Port C                                                |

| PD15-PD04                      | I/O        | GPIO Port D                                                |

| Pulse Width Modulation (P)     | NMO, PWN   | 11, PWM2), x = 0, 1, 2                                     |

| PWMx_A                         | 0          | PWM x Signals                                              |

| PWMx_B                         | 0          | PWM x Signals                                              |

| PWM_FALT                       | I          | PWM Fault Input                                            |

| General-Purpose Timer (GF      | TO, GPT1   | , GPT2), x = 0, 1, 2                                       |

| CCPx_A                         | I/O        | GPTimer x Compare and Capture A                            |

| CCPx_B                         | I/O        | GPTimer x Compare and Capture B                            |

| Analog to Digital Converter    | (ADC)      |                                                            |

| AD[7:0]                        | 1          | ADC Single End Channel Input /                             |

|                                | I          | *ADC Differential Channel Input Positive or Negative Input |

| Analog Comparator (AC0, A      | AC1, AC2,  | AC3), x=0, 1, 2, 3                                         |

| CAIPx                          | I          | Comparator x Positive Input                                |

| CAINx                          | I          | Comparator x Negative Input                                |

| System Control (SC)            |            |                                                            |

| XTAL32_IN                      | I          | 32.768K RTC Clock Input                                    |

| XTAL32_OUT                     | 0          | 32.768K RTC Clock Output                                   |

| XTAL_IN                        | I          | High Speed 8MHZ Crystal Clock Input                        |

| XTAL_OUT                       | 0          | High Speed 8MHZ Crystal Clock Output                       |

| NRST                           | I          | System Reset                                               |

| WKUP                           | I          | Wakeup                                                     |

| МСО                            | 0          | Microcontroller Clock Output                               |

| RTC_1HZ                        | 0          | RTC 1 Second Output                                        |

|                                | -          | · · · · · · · · · · · · · · · · · · ·                      |

# **4. FUNCTIONAL DESCRIPTION**

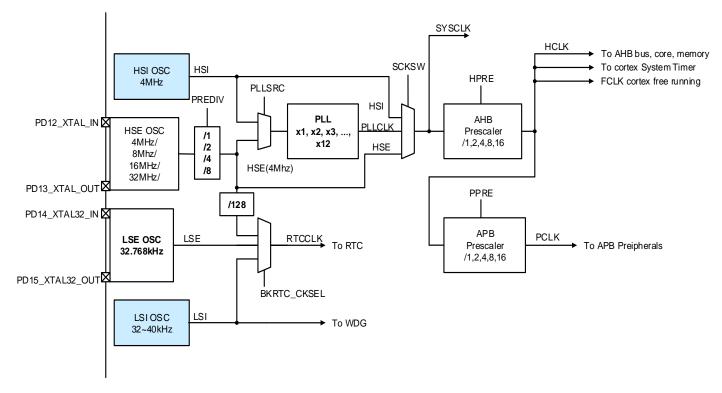

## 4.1 SYSTEM AND MEMORY OVERVIEW

The PT32 microcontrollers is a series of low-power microcontrollers incorporating a high-performance ARM CortexTM-M0 32-bit RISC core operating at a 48 MHz frequency, high-speed embedded memories and an extensive range of enhanced peripherals and I/O s. A comprehensive set of power-saving modes allows it to be employed in low-power applications.

The PT32U301 MCUs give you any essential functionality as a General-purpose MCU. With its highly customizable peripherals, it eases the process of making your own ideal product.

This chapter introduces you to PT32U301 features, its system and memory structure.

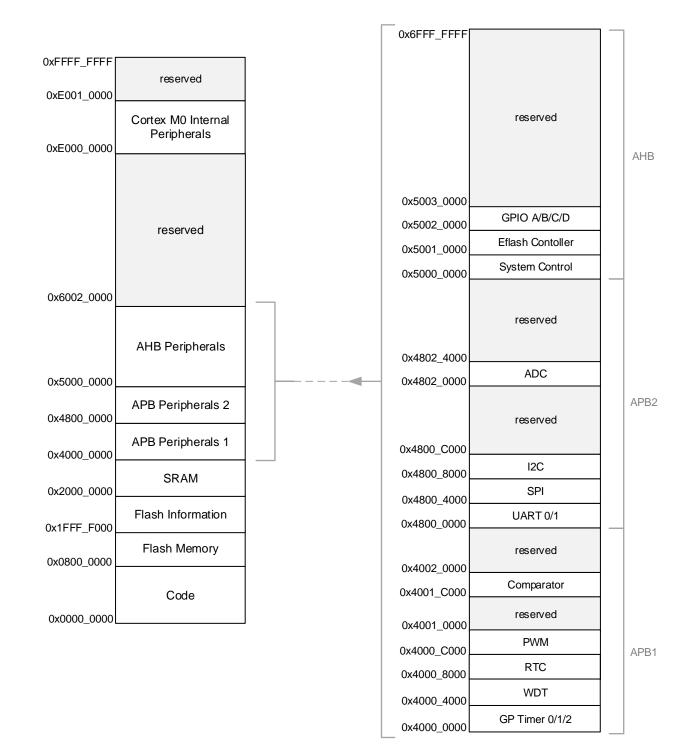

## 4.1.1 PT32U301 MEMORY MAPPING

The system, bus is implemented as a bus matrix. All system bus addresses are fixed and cannot be remapped.

#### Figure 4.1-1: Memory Mapping

## Table 4.1-1: Peripheral register boundary addresses

| Bounda      | ry address  | Depth  | Peripheral Description                                                          | Reference | BUS  |

|-------------|-------------|--------|---------------------------------------------------------------------------------|-----------|------|

| Start       | End         | (Byte) | · · ·                                                                           | Section   |      |

| 0x0000_0000 | 0x1FFF_FFFF | 6K     | Mask ROM, Main Flash memory or System RAM depending<br>on Booting Configuration | -         | _    |

| 0x0800_0000 | 0x0800_7FFF | 64K    | Embedded Flash Memory Field                                                     | 4.3.2     |      |

| 0x1FFF_F000 | 0x1FFF_FBFF | ЗK     | Embedded Flash Information Memory Field                                         | 4.3.2     |      |

| 0x1FFF_FC00 | 0x1FFF_FFFF | 1K     | Embedded Flash Information Memory Field                                         | 4.3.2     | AHB  |

| 0x2000_0000 | 0x2000_0FFF | 4K     | System RAM                                                                      | -         |      |

| 0x2000_1000 | 0x3FFF_FFFF | -      | Reserved                                                                        | -         | _    |

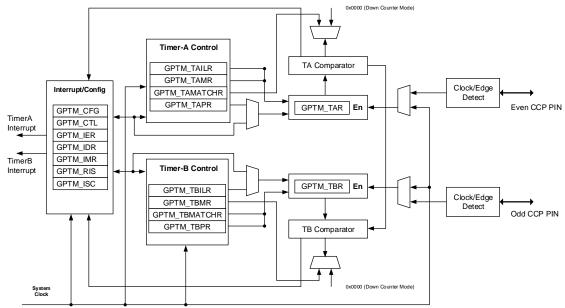

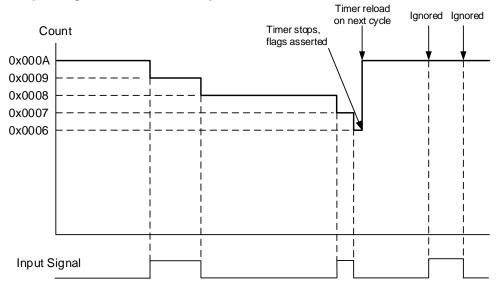

| 0x4000_0000 | 0x4000_3FFF |        | General-purpose Timer 0/1/2 Control Register                                    | 4.7.3     |      |

| 0x4000_4000 | 0x4000_7FFF |        | Watchdog Control Register                                                       | 4.10.3    |      |

| 0x4000_8000 | 0x4000_BFFF |        | RTC Control Register                                                            | 4.10.3    |      |

| 0x4000_C000 | 0x4000_FFFF |        | Pulse Width Modulation (PWM) Control Register                                   |           | APB1 |

| 0x4001_0000 | 0x4001_BFFF | -      | Reserved                                                                        | -         |      |

| 0x4001_C000 | 0x4001_FFFF |        | Analog Comparator(AC) Control Register                                          | 4.8.4     |      |

| 0x4002_0000 | 0x47FF_FFFF | -      | Reserved                                                                        | -         |      |

| 0x4800_0000 | 0x4800_3FFF |        | UART 0/1 Control Register                                                       | -         |      |

| 0x4800_4000 | 0x4800_7FFF |        | SPI Control Register                                                            | 4.12.3    |      |

| 0x4800_8000 | 0x4800_BFFF |        | I2C Control Register                                                            | 4.12.3    | APB2 |

| 0x4800_C000 | 0x4801_FFFF |        | Reserved                                                                        | -         | AFDZ |

| 0x4802_0000 | 0x4802_3FFF |        | ADC Control Register                                                            | 4.7       |      |

| 0x4802_4000 | 0x4FFF_FFFF | -      | Reserved                                                                        | -         |      |

| 0x5000_0000 | 0x5000_FFFF |        | System Control Register                                                         | 4.3       |      |

| 0x5001_0000 | 0x5001_FFFF |        | Embedded Flash Control Register                                                 | 4.5.2     | AHB  |

| 0x5002_0000 | 0x5002_FFFF |        | GPIO A/B/C/D Control Register                                                   | 4.5.2     |      |

| 0x5003_0000 | 0x6FFF_FFFF |        | Reserved                                                                        | -         |      |

| 0x6002_0000 | 0xDFFF_FFFF |        | Reserved                                                                        | -         |      |

| 0xE000_0000 | 0xE00F_FFFF |        | ARM ® Cortex <sup>™</sup> -M0 System Timer (SysTick) Control Register           | 4.2.1     |      |

| 0xE001_0000 | 0xFFFF_FFF  | -      | Reserved                                                                        | -         |      |

## 4.2 ARM ® CORTEX<sup>™</sup>-M0 CORE

The ARM Cortex<sup>™</sup>-M0 processor is the smallest and most energy- efficient ARM processor available. It satisfies the demand for ever-lower-cost applications with increasing connectivity. The M0 processor is a configurable, multistage, 32-bit RISC processor.

In PT32U301, this processor configures following features:

- Built-in Nested Vectored Interrupt Controller (NVIC): 32 external Interrupt

- Little-endian

- Integrated system timer SysTick

- Halting debug support

- Fast multiplier

- Support Serial Wire Debug (SWD) connections.

This chapter provide basic information of the following processor peripherals,

- CPU System Timer Control (SysTick)

- CPU Nested Vectored Interrupt Controller (NVIC)

- CPU System Control

For further information, please refer to:

- ARM Cortex<sup>™</sup>-M0 Technical Reference Manual

- ARM v6-M Architecture Reference Manual

## 4.2.1 CPU SYSTEM TIMER CONTROL REGISTER (SYST)

The Cortex<sup>™</sup>-M0 includes an integrated system timer - SysTick, providing a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism. The counter can be used as a Real Time Operating System (RTOS) tick timer or as a simple counter.

When the system timer is enabled, it starts counting down from the value in the SysTick Current Value Register (SYST\_CVR) to 0, and reload (wrap) to the value in the SysTick Reload Value Register (SYST\_RVR) in the next clock cycle, then decrements on subsequent clocks. Once the counter transitions to 0, the COUNTFLAG status bit is set. The COUNTFLAG bit clears on reads.

The SYST\_CVR value is UNKNOWN at reset. Before enabling this feature. Software should write to the register to clear it to zero before enabling the feature. This ensures the timer will count from the SYST\_RVR value rather than an arbitrary value when it is enabled.

If the SYST\_RVR is 0, the timer will be maintained with a current value of 0 after it is reloaded with this value. This mechanism can be used to disable the feature independently from the timer enable bit.

PT32M625

## 4.2.2 SYST REGISTER MAPS

#### Base Address: 0xE000\_E000

| Offset | Symbol | Туре | Reset Value | Description                         | See<br>page |

|--------|--------|------|-------------|-------------------------------------|-------------|

| 0x0010 | CSR    | R/W  | 0x0000_0000 | SysTick Control and Status Register | 12          |

| 0x0014 | RVR    | R/W  | -           | SysTick Reload Value Register       | 13          |

| 0x0018 | CVR    | R/W  | -           | SysTick Current Value Register      | 13          |

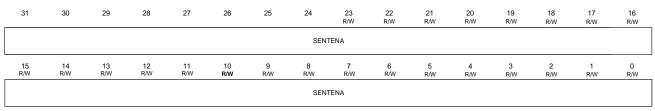

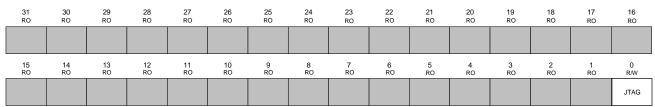

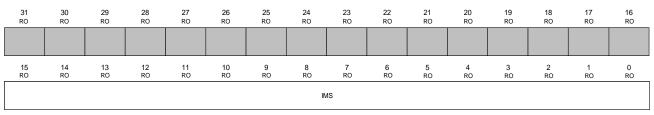

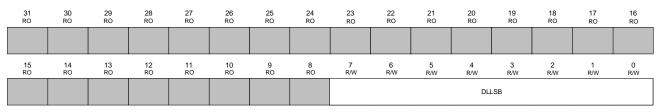

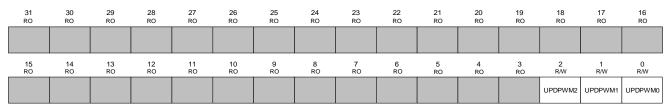

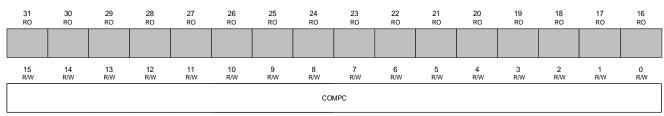

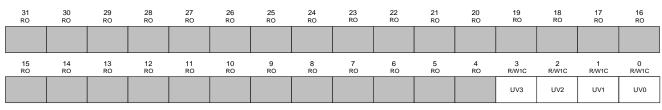

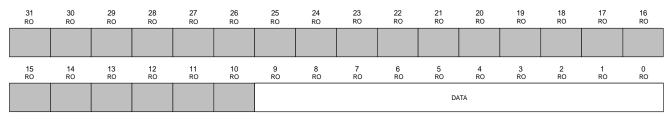

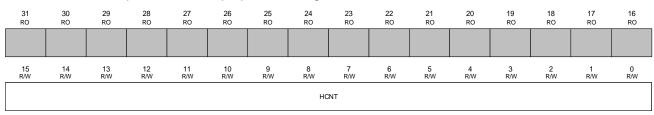

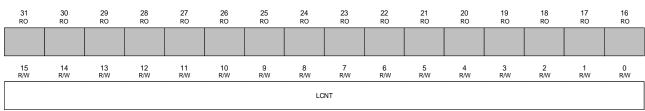

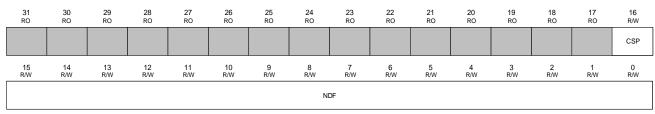

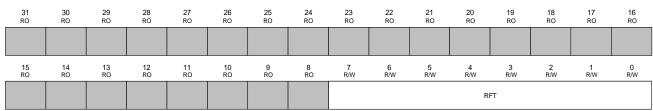

### 4.2.2.1 SYST\_CSR - SYSTICK CONTROL AND STATUS REGISTER

The SYST\_CSR enables the SysTick features.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18     | 17     | 16     |

|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|--------|--------|

| RO     | RO     | R/W    |

|    |    |    |    |    |    |    |    |    |    |    |    |    |        |        | COUNT  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2      | 1      | 0      |

| RO | R/W    | R/W    | R/W    |

|    |    |    |    |    |    |    |    |    |    |    |    |    | CLKSRC | TICKIE | ENABLE |

| Bit   | Name     | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|----------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:17 | reserved | RO   | 0x0   | Software should not rely on the value of a reserved bit. Considering the compatibility with other products, the values of this should not be written or read.                                                                                                                                                                                                                                  |

| 16    | COUNT    | R/W  | 0     | Count Flag<br>0: The SysTick timer has not counted to 0 since the last time this bit was<br>read.<br>1: The SysTick timer has counted to 0 since the last time this bit was read<br>COUNT is cleared on read or by a write to the Current Value register.                                                                                                                                      |

| 15:3  | reserved | RO   | 0x0   | Software should not rely on the value of a reserved bit. Considering the compatibility with other products, the values of this should not be written or read.                                                                                                                                                                                                                                  |

| 2     | CLKSRC   | R/W  | 0     | System Tick Clock Source Selection<br>0: Clock source is (optional) external reference clock.<br>1: Core clock used for SysTick.                                                                                                                                                                                                                                                               |

| 1     | TICKIE   | R/W  | 0     | <ul> <li>System Tick Interrupt Enable</li> <li>0: Counting down to 0 does not cause the SysTick exception to be pended. Software can use COUNTFLAG to determine if a count to 0 has occurred.</li> <li>1: Counting down to 0 will cause the SysTick exception to be pended. Clearing the SysTick Current Value register by a write in software will not cause SysTick to be pended.</li> </ul> |

| 0     | ENABLE   | R/W  | 0     | System Tick Counter Enabled<br>0: Counter is disabled.<br>1: Counter operates in a multi-shot manner.                                                                                                                                                                                                                                                                                          |

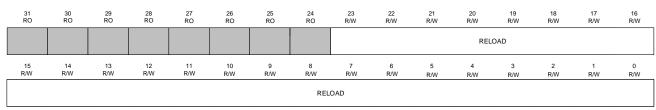

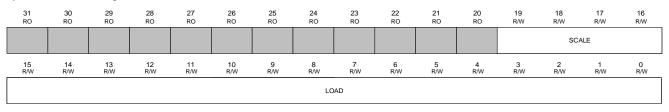

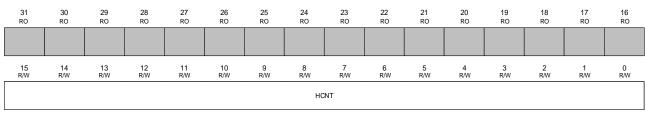

## 4.2.2.2 SYST\_RVR - SYSTICK RELOAD VALUE REGISTER

The SYST\_RVR specifies the start value to load into the SYST\_CVR.

#### Offset: 0x0014

| Bit   | Name     | Туре | Reset | Description                                                                                                                                                   |

|-------|----------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | reserved | RO   | 0x0   | Software should not rely on the value of a reserved bit. Considering the compatibility with other products, the values of this should not be written or read. |

| 23:0  | RELOAD   | R/W  | R0    | Reload Value<br>Value to load into the SysTick Current Value Register (SYST_CVR)<br>register when the counter reaches 0.                                      |

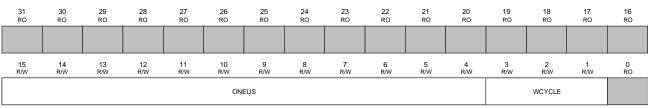

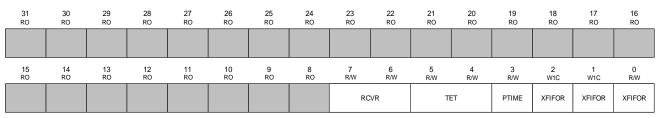

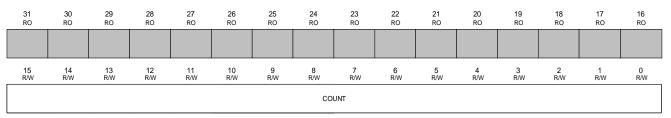

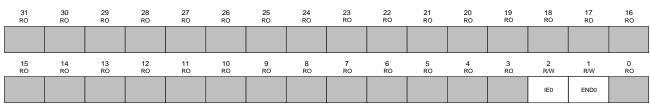

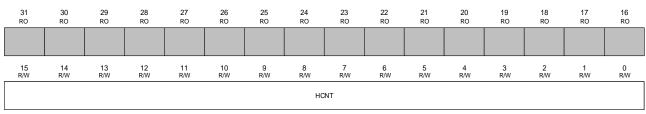

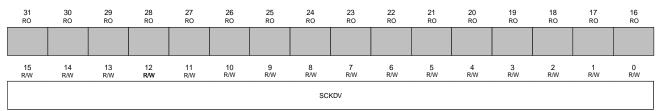

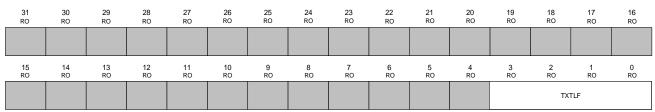

### 4.2.2.3 SYST\_CVR - SYSTICK CURRENT VALUE REGISTER

The SYST\_CVR contains the current value of the SysTick counter.

| 31<br>RO | 30<br>RO | 29<br>RO | 28<br>RO | 27<br>RO | 26<br>RO | 25<br>RO | 24<br>RO | 23<br>R/W | 22<br>R/W | 21<br>R/W | 20<br>R/W | 19<br>R/W | 18<br>R/W | 17<br>R/W | 16<br>R/W |

|----------|----------|----------|----------|----------|----------|----------|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|          |          |          |          |          |          |          |          |           |           |           | CURF      | RENT      |           |           |           |

| 15       | . 14     | 13       | 12       | 11       | 10       | 9        |          | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

| R/W       | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       |

| Bit   | Name     | Туре | Reset | Description                                                                                                                                                                                                                                                                  |

|-------|----------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | reserved | RO   | 0x0   | Software should not rely on the value of a reserved bit. Considering the compatibility with other products, the values of this should not be written or read.                                                                                                                |

| 23:0  | CURRENT  | R/W  | 0     | System Tick Current Value<br>Current counter value. This is the value of the counter at the time it is<br>sampled. The counter does not provide read-modify-write protection. The<br>register is write-clear. A software write of any value will clear the register<br>to 0. |

## 4.2.3 CPU NESTED VECTORED INTERRUPT CONTROLLER (NVIC)

The Cortex<sup>™</sup>-M0 provides an interrupt controller as an integral part of the exception mode, named as "Nested Vectored Interrupt Controller (NVIC)", which is closely coupled with the processor core and provides following features:

- Support Nested and Vectored interrupt

- Automatic processor state saving and restoration

- Reduced and deterministic interrupt latency

- 32 maskable interrupts

- 4 levels of priority

The NVIC prioritizes and handles all supported exceptions. All exceptions are handled in "Handler Mode". This NVIC architecture supports up to 32 discrete interrupts request (IRQ [31:0]) with up to 4 levels of priority. All of the interrupts and most of the system exceptions can be configured to different priority levels. When an interrupt occurs, the NVIC will compare the priority of the new interrupt to the current running one. If the priority of the new interrupt is higher than the current one, the new interrupt handler will override the current handler.

When an interrupt is accepted, the starting address of the interrupt service routine (ISR) is fetched from a vector table in memory. There is no need to determine which interrupt is accepted and branch to the starting address of the correlated ISR by software. While the starting address is fetched, NVIC will also automatically save processor state including the registers "PC, PSR, LR, R0~R3, R12" to the stack. At the end of the ISR, the NVIC will restore the mentioned registers from stack and resume the normal execution. Thus it will take less and deterministic time to process the interrupt request.

The NVIC supports "Tail Chaining" which handles back-to-back interrupts efficiently without the overhead of states saving and restoration and therefore reduces delay time in switching to pending ISR at the end of current ISR. The NVIC also supports "Late Arrival" which improves the efficiency of concurrent ISRs. When a higher priority interrupt request occurs before the current ISR starts to execute (at the stage of state saving and starting address fetching), the NVIC will give priority to the higher one without delay penalty. Thus it advances the real-time capability.

#### Exceptions Modes and System Interrupt Map

The following table lists the exception models. Software can set four levels of priority on some of these exceptions as well as on all interrupts. The highest user-configurable priority is denoted as "0" and the lowest priority is denoted as "3". The default priority of all the user-configurable interrupts is "0". Note that priority "0" is treated as the fourth priority on the system, after three system exceptions "Reset", "NMI" and "Hard Fault".

| Vector No. | Exception Name       | Priority     |

|------------|----------------------|--------------|

| 1          | Reset                | -3           |

| 2          | NMI                  | -2           |

| 3          | Hard Fault           | -1           |

| 4 - 10     | Reserved             | Reserved     |

| 11         | SCCall               | Configurable |

| 12 - 13    | Reserved             | Reserved     |

| 14         | PendSV               | Configurable |

| 15         | Sys Tick             | Configurable |

| 16 - 47    | Interrupt(IRQ[31:0]) | Configurable |

#### Table 4.2-1: Exception Model

## Table 4.2-2: System Interrupt Map

| IRQ No. | Name             | Description                      |  |  |  |  |

|---------|------------------|----------------------------------|--|--|--|--|

| 31      | WAKEUP           | CPU Wake Up Interrupt            |  |  |  |  |

| 30      | PVD              | Power Voltage Detector Interrupt |  |  |  |  |

| 29 ~ 19 | Reserved         | -                                |  |  |  |  |

| 18      | ADC              | ADC Interrupt                    |  |  |  |  |

| 17      | COMP             | Analog Comparator Interrupt      |  |  |  |  |

| 16      | PWM_FAULT        | PWM Fault Interrupt              |  |  |  |  |

| 15      | PWM2             | PWM2Interrupt                    |  |  |  |  |

| 14      | PWM1             | PWM1Interrupt                    |  |  |  |  |

| 13      | PWM0             | PWM0 Interrupt                   |  |  |  |  |

| 12      | TIMER2           | TIMER2 Interrupt                 |  |  |  |  |

| 11      | TIMER1           | TIMER1 Interrupt                 |  |  |  |  |

| 10      | TIMER0           | TIMER0 Interrupt                 |  |  |  |  |

| 9       | WDT              | Watch Dog Interrupt              |  |  |  |  |

| 8       | RTC              | RTC Interrupt                    |  |  |  |  |

| 7       | l <sup>2</sup> C | I2C Interrupt                    |  |  |  |  |

| 6       | SPI0             | SPI Interrupt                    |  |  |  |  |

| 5       | UART1            | UART1 Interrupt                  |  |  |  |  |

| 4       | UART0            | UART0 Interrupt                  |  |  |  |  |

| 3       | GPIO_D           | GPIO D Port Interrupt            |  |  |  |  |

| 2       | GPIO_C           | GPIO C Port Interrupt            |  |  |  |  |

| 1       | GPIO_B           | GPIO B Port Interrupt            |  |  |  |  |

| 0       | GPIO_A           | GPIO A Port Interrupt            |  |  |  |  |

### 4.2.3.1 VECTOR TABLE

When an interrupt is accepted, the processor will automatically fetch the starting address of the interrupt service routine (ISR) from a vector table in memory. For ARMv6-M, the vector table base address is fixed at 0x000000000. The vector table contains the initialization value for the stack pointer on reset, and the entry point addresses for all exception handlers. The vector number on previous page defines the order of entries in the vector table associated with exception handler entry as illustrated in previous section.

#### Table 4.2-3: Vector Table Format

| Vector Table Word Offset | Description                                      |

|--------------------------|--------------------------------------------------|

| 0                        | SP_main – The Main stack pointer                 |

| Vector Number            | Exception Entry Pointer using that Vector Number |

### 4.2.3.2 OPERATION DESCRIPTION

NVIC interrupts can be enabled or disabled by writing to their corresponding Interrupt Set-Enable or Interrupt Clear-Enable register bit-field. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current enabled state of the corresponding interrupts. When an interrupt is disabled, interrupt assertion will cause the interrupt to become Pending, however, the interrupt will not activate. If an interrupt is Active when it is disabled, it remains in its Active state until cleared by reset or an exception return. Clearing the enable bit prevents new activations of the associated interrupt.

NVIC interrupts can be pended/un-pended using a complementary pair of registers to those used to enable/disable the interrupts, named the Set-Pending Register and Clear-Pending Register respectively. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current pended state of the corresponding interrupts. The Clear-Pending Register has no effect on the execution status of an Active interrupt.

NVIC interrupts are prioritized by updating an 8-bit field within a 32-bit register (each register supporting four interrupts). The general registers associated with the NVIC are all accessible from a block of memory in the System Control Space and will be described in next section.

## 4.2.4 NVIC REGISTER MAPS

### Base Address 0xE000\_E100

| Offset | Symbol    | Туре | Reset Value | Description                             | See page |

|--------|-----------|------|-------------|-----------------------------------------|----------|

| 0x0000 | NVIC_ISER | R/W  | 0x0000_0000 | IRQ Set Enable Control Register         | 18       |

| 0x0080 | NVIC_ICER | R/W  | 0x0000_0000 | IRQ Clear Enable Control Register       | 18       |

| 0x0100 | NVIC_ISPR | R/W  | 0x0000_0000 | IRQ Set Pending Control Register        | 19       |

| 0x0180 | NVIC_ICPR | R/W  | 0x0000_0000 | IRQ Clear Pending Control Register      | 19       |

| 0x0300 | NVIC_IPR0 | R/W  | 0x0000_0000 | IRQ0 - IRQ3 Priority Control Register   | 20       |

| 0x0304 | NVIC_IPR1 | R/W  | 0x0000_0000 | IRQ4 - IRQ7 Priority Control Register   | 21       |

| 0x0308 | NVIC_IPR2 | R/W  | 0x0000_0000 | IRQ8 - IRQ11 Priority Control Register  | 22       |

| 0x030C | NVIC_IPR3 | R/W  | 0x0000_0000 | IRQ12 - IRQ15 Priority Control Register | 23       |

| 0x0310 | NVIC_IPR4 | R/W  | 0x0000_0000 | IRQ16 - IRQ19 Priority Control Register | 24       |

| 0x0314 | NVIC_IPR5 | R/W  | 0x0000_0000 | IRQ20 - IRQ23 Priority Control Register | 25       |

| 0x0318 | NVIC_IPR6 | R/W  | 0x0000_0000 | IRQ24 - IRQ27 Priority Control Register | 26       |

| 0x031C | NVIC_IPR7 | R/W  | 0x0000_0000 | IRQ28 - IRQ31 Priority Control Register | 27       |

####

## 4.2.4.1 NVIC\_ISER - NVIC IRQ SET ENABLE CONTROL REGISTER

The NVIC\_ISER registers enable interrupts, and show which interrupts are enabled.

#### Offset: 0x0000

| Bit  | Name   | Туре | Reset | Description                                                                                                                                                                                                                                                                              |

|------|--------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | SETENA | R/W  | 0x0   | Interrupt enable<br>Enable one or more interrupts. Each bit represents and interrupt number<br>from IRQ0 – IRQ31<br>0: On a read, indicates the interrupt is disabled.<br>On a write, no effect<br>1: On a read, indicates the interrupt is enabled<br>On a write, enables the interrupt |

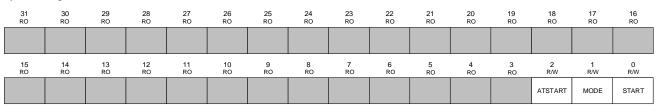

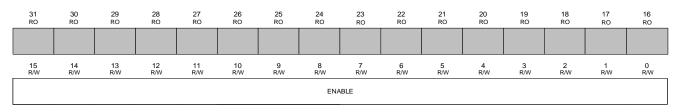

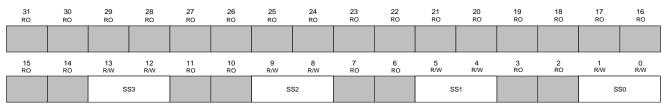

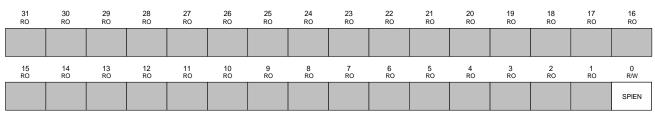

### 4.2.4.2 NVIC\_ICER - NVIC IRQ CLEAR ENABLE CONTROL REGISTER

The NVIC\_ICER registers disable interrupts, and show which interrupts are enabled.

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21   | 20   | 19   | 18   | 17  | 16   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|-----|------|

| R/W  | R/W  | R/W  | R/W  | R/W | R/W  |

|     |     |     |     |     |     |     | CLR | ENA |     |      |      |      |      |     |      |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5    | 4    | 3    | 2    | 1   | 0    |

| R/W  | R/W  | R/W  | R/W  | R/W | R/W  |

|     |     | -   |     |     |     |     |     |     |     | 1411 | 1011 | 1011 | 1011 |     | 1011 |

| Bit  | Name   | Туре | Reset | Description                                                                                                                                                                                                                                                                                  |

|------|--------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | CLRENA | R/W  | 0x0   | Interrupt disable<br>Disable one or more interrupts. Each bit represents and interrupt number<br>from IRQ0 to IRQ31.<br>0: On a read, indicates the interrupt is disabled.<br>On a write, no effect<br>1: On a read, indicates the interrupt is enabled<br>On a write, enables the interrupt |

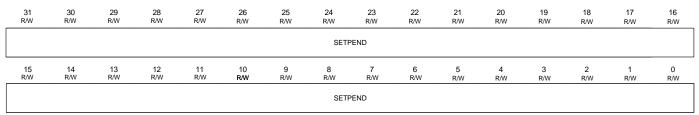

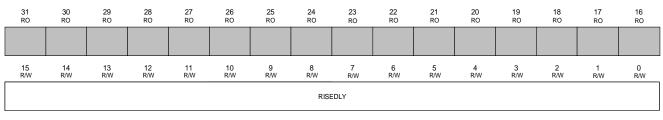

## 4.2.4.3 NVIC\_ISPR - NVIC IRQ SET PENDING CONTROL REGISTER

The ISPR registers force interrupts into the pending state, and show which interrupts are pending.

#### Offset: 0x0100

| Bit  | Name    | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                     |

|------|---------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | SETPEND | R/W  | 0x0   | Set Interrupt Pending<br>Disable one or more interrupts. Each bit represents and interrupt number<br>from IRQ0 to IRQ31<br>0: On a read, indicates that the interrupt is not pending.<br>On a write, no effect<br>1: On a read, indicates that the interrupt is pending.<br>On a write, the corresponding interrupt is set to pending even if it is<br>disabled |

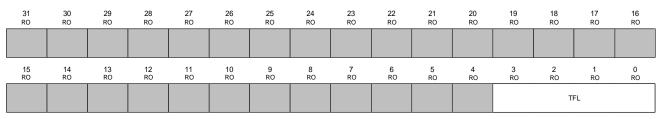

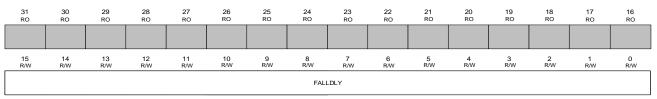

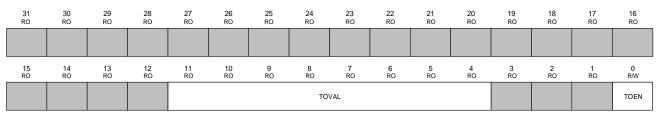

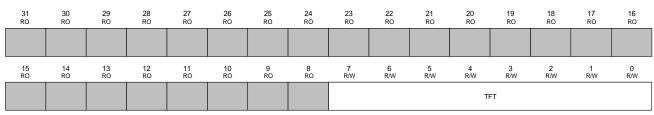

### 4.2.4.4 NVIC\_ICPR - NVIC IRQ CLEAR PENDING CONTROL REGISTER

The ICPR registers remove the pending state from interrupts, and show which interrupts are pending.

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24   | 23   | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|------|------|-----|-----|-----|-----|-----|-----|-----|

| R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

|     |     |     |     |     |     |     | CLRF | PEND |     |     |     |     |     |     |     |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8    | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

|     |     |     |     |     |     |     | CLR  | PEND |     |     |     |     |     |     |     |

| Bit  | Name    | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                         |

|------|---------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | CLRPEND | R/W  | 0x0   | Set Interrupt Pending<br>Disable one or more interrupts. Each bit represents and interrupt number<br>from IRQ0 to IRQ31<br>0: On a read, indicates that the interrupt is not pending.<br>On a write, no effect<br>1: On a read, indicates that the interrupt is pending.<br>On a write, write 1 to clear pending state, so that the corresponding interrupt<br>in no longer pending |

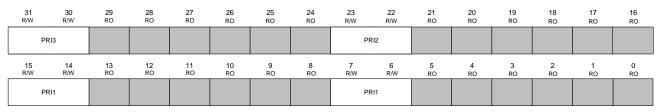

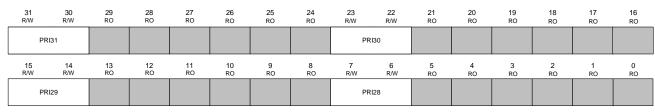

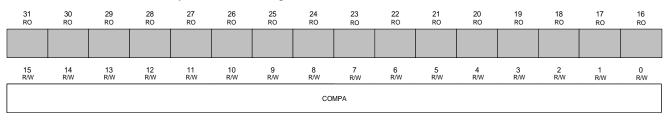

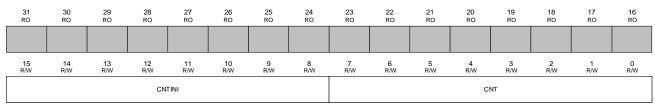

## 4.2.4.5 NVIC\_IPR0 - NVIC IRQ0 - IRQ3 PRIORITY CONTROL REGISTER

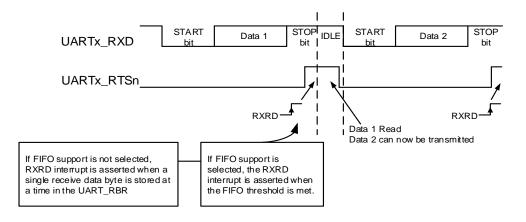

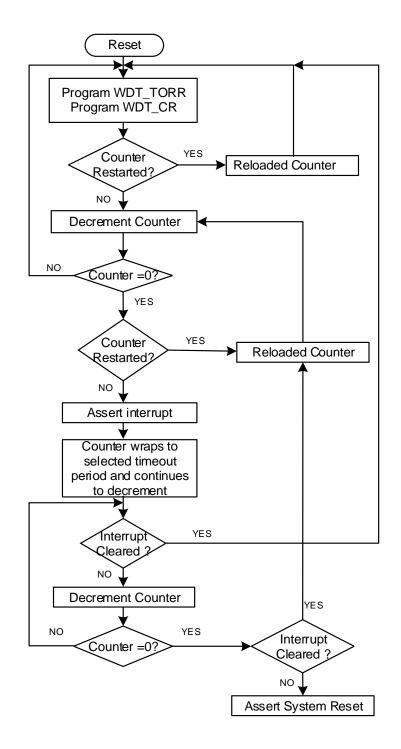

The IPR0 registers provide an 8-bit priority field for each interrupt and each register holds four priority fields (IRQ [3:0]). While setting each priority field, "0" always denotes the highest priority and "3" always denotes the lowest priority