# Low Power PWM Controller with On-Chip Power Switch

The NCP1032 is a miniature high-voltage monolithic switching converter with on-chip power switch and startup circuits. It incorporates in a single IC all the active power control logic and protection circuitry required to implement, with minimal external components several switching regulator applications, such as a secondary side bias supply or a low power DC-DC converter. This converter is ideally suited for 24 V and 48 V telecom and medical isolated power supply applications. The NCP1032 can be configured in any single-ended topology such as forward or flyback converter. The NCP1032 is targeted for applications requiring up to 3 W.

The internal error amplifier allows the NCP1032 to be easily configured for secondary or primary side regulation operation in isolated and non-isolated configurations. The fixed frequency oscillator is optimized for operation up to 1 MHz and is capable of external frequency synchronization, providing additional design flexibility. In addition, the NCP1032 incorporates undervoltage and overvoltage line detectors, programmable cycle-by-cycle current limit, internal soft-start, and thermal shutdown to protect the controller under fault conditions.

#### **Features**

- On Chip High 200 V Power Switch Circuit and Startup Circuit

- Internal Startup Regulator with Auxiliary Winding Override

- Programmable Oscillator Frequency Operation up to 1 MHz

- External Frequency Synchronization Capability

- Frequency Fold-down Under Fault Conditions

- Trimmed ± 2% Internal Reference

- Programmable Cycle-by-Cycle Current Limit

- Internal Soft-Start

- Active Leading Edge Blanking Circuit

- Line Under and Over Voltage Protection

- Over Temperature Protection

- These are Pb-Free Devices

## **Typical Applications**

- POE (Power Over Ethernet)/PD. Refer to Application Note AND8247

- Secondary Side Bias Supply for Isolated DC-DC Converters

- Stand Alone Low Power DC-DC Converter

- Low Power Bias Supply

- Low Power Boost Converter

- Medical Isolated Power Supplies

- Bias Supply for Telecom Systems. Refer to App Note AND8119/D

1

## ON Semiconductor®

www.onsemi.com

## MARKING DIAGRAMS

## WDFN8 MN SUFFIX CASE 511BH

1032 = Specific Device Marking

x = A or B

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

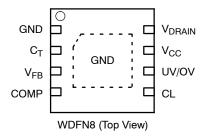

#### PIN CONNECTIONS

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 20 of this data sheet.

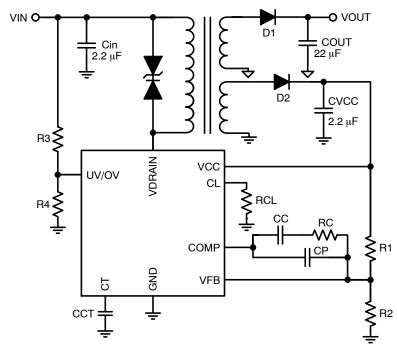

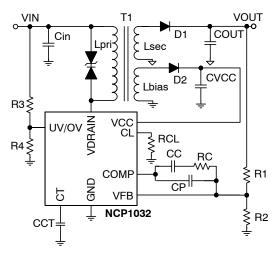

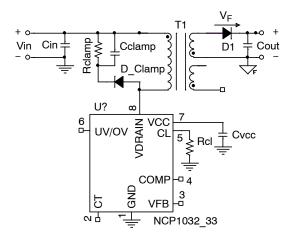

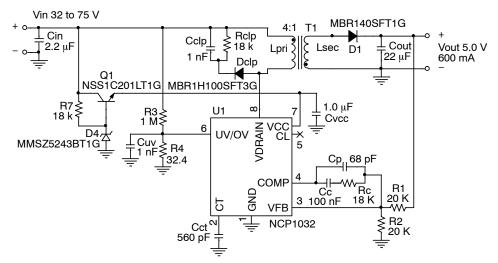

Figure 1. Typical Application – Dual Output Auxiliary Regulated Isolated Flyback

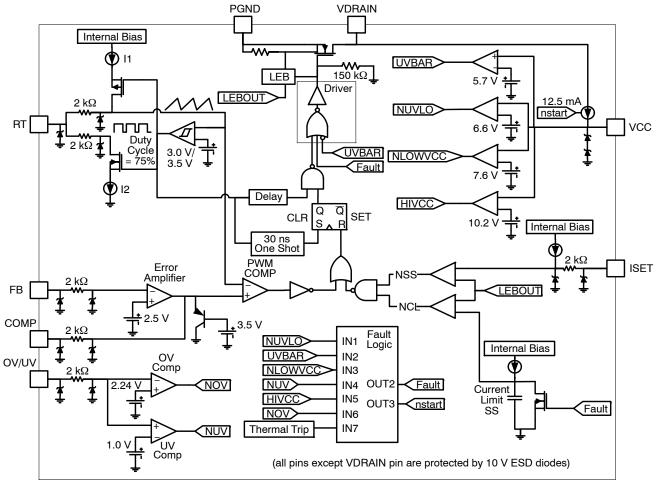

Figure 2. NCP1032 Simplified Block Diagram

**Table 1. FUNCTIONAL PIN DESCRIPTION**

| Pin | Name            | Function                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-----------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND             | IC Ground                                              | Ground reference pin for the circuit.                                                                                                                                                                                                                                                                                                                                                                              |

| 2   | C <sub>T</sub>  | Oscillator Frequency<br>Selection                      | An external capacitor connected to this pin sets the oscillator frequency up to 1 MHz. The oscillator can be synchronized to a higher frequency by charging or discharging CT to trip the internal 3.0 V/3.5 V comparators. If a fault condition exists, the power switch is disabled and the frequency is reduced.                                                                                                |

| 3   | $V_{FB}$        | Feedback Signal Input                                  | The regulated voltage is scaled down to 2.5 V by means of a resistor divider. Regulation is achieved by comparing the scaled voltage to an internal 2.5 V reference.                                                                                                                                                                                                                                               |

| 4   | COMP            | Error Amplifier<br>Compensation                        | The output of the internal error amplifier. External compensation network between COMP and VFB pin is required for stable operation.                                                                                                                                                                                                                                                                               |

| 5   | CL              | Current Limit Threshold<br>Selection                   | A resistor $R_{CL}$ connected between this pin and ground sets the peak current value of the current limit. If the CL pin is left open, the current limit value is set to its initial maximum value of approximately 12 mA ( $C_{LIM\_MAX}$ ). Programmable current limit threshold, together with internal soft–start feature effectively limits the primary transformer high current peaks during startup phase. |

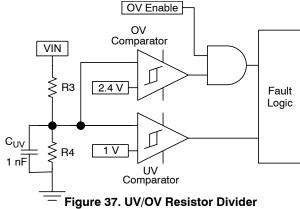

| 6   | UV/OV           | Input Line Undervoltage<br>and Overvoltage<br>Shutdown | Input line voltage is scaled down using an external resistor divider. The minimum operating Vin voltage is achieved when the voltage on UV/OV pin reaches UV threshold 1.0 V. The maximum operating voltage is then limited by 2.4 V on UV/OV pin. A device version without OV protection feature is available, see ordering information section.                                                                  |

| 7   | V <sub>CC</sub> | Powers the Internal<br>Circuitry                       | Supplies power to the internal control circuitry. Connect an external capacitor for energy storage during startup. The Vcc voltage should not exceed 16 V during operation.                                                                                                                                                                                                                                        |

| 8   | $V_{DRAIN}$     | Drain Connection                                       | Connects the power switch and startup circuit to the primary transformer windings.                                                                                                                                                                                                                                                                                                                                 |

| EP  | EP              | Thermal Flag                                           | This is the thermal flag for the IC and should be soldered to the ground plane.                                                                                                                                                                                                                                                                                                                                    |

## **Table 2. MAXIMUM RATINGS**

| Rating                                                                                                                                   | Symbol              | Value           | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|------|

| Power Switch and Startup Circuits Voltage                                                                                                | BVdss               | -0.3 to +200    | V    |

| VCC Power Supply Voltage                                                                                                                 | V <sub>CC</sub>     | -0.3 to +16     | V    |

| Power Supply Voltage on all Pins, except VDRAIN and VCC                                                                                  | V <sub>IO</sub>     | -0.3 to +10     | V    |

| Drain Current Peak During Transformer Saturation                                                                                         | I <sub>DS(pk)</sub> | 1.0             | Α    |

| Thermal Resistance Junction-to-Air -W DFN8 3x3, case 511BH (100 sq mm, 2oz) (Note 4) (500 sq mm, 2oz) (Note 4) (100 sq mm,2oz,) (Note 5) | $R_{	hetaJA}$       | 109<br>64<br>44 | °C/W |

| Maximum Junction Temperature                                                                                                             | $T_{JMAX}$          | 150             | °C   |

| Storage Temperature Range                                                                                                                | T <sub>STG</sub>    | -60 to +150     | °C   |

| ESD Capability, Human Body Model Pins 1-7 (Note 1)                                                                                       |                     | 4.0             | kV   |

| ESD Capability, Machine Model Pins 1-7 (Note 1)                                                                                          |                     | 400             | V    |

| Pin 8 is connected to the high voltage startup and power switch which is protected to the maximum drain voltage                          |                     | 200             | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. This device series contains ESD protection and passes the following tests: Human Body Model (HBM) ± 2.0 kV per JEDEC standard: JESD22–A114.

- Machine Model (MM) ± 200 V per JEDEC standard: JESD22–A115.

2. This device contains latch–up protection and it exceeds ± 100 mA per JEDEC standard: JESD78 class II

- 3. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A

- 4. EIA JEDEC 51.3, single layer PCB with added heat spreader

5. EIA JEDEC 51.7, four layer PCB with added heat spreader

$\textbf{Table 3. ELECTRICAL CHARACTERISTICS} \\ (For typical values Tj = 25^{\circ}C, for min/max values Tj = -40^{\circ}C to +125^{\circ}C, V_{DRAIN} = 48 \text{ V}, V_{CC} = 12 \text{ V}, unless otherwise noted})$

| · //                              | , , , , , ,                                                             | , Brown , co                                                                                                                                        | <u> </u>     |            |              |      |  |  |

|-----------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|--------------|------|--|--|

| Symbol                            | Parameter                                                               | Conditions                                                                                                                                          | Min          | Тур        | Max          | Unit |  |  |

| SUPPLY SECTION AND VCC MANAGEMENT |                                                                         |                                                                                                                                                     |              |            |              |      |  |  |

| V <sub>CC_ON</sub>                | Vcc Voltage at Which the Switcher<br>Starts Operation                   | V <sub>CC</sub> Increasing                                                                                                                          | 9.9          | 10.2       | 10.5         | V    |  |  |

| V <sub>CC_MIN</sub>               | Minimum Operating VCC After Turn on at Which HV Current Source Restarts | V <sub>CC</sub> Decreasing                                                                                                                          | 7.40         | 7.55       | 7.7          | V    |  |  |

| V <sub>CC_RST</sub>               | Vcc Undervoltage Lockout Voltage                                        | V <sub>CC</sub> Decreasing, V <sub>FB</sub> = V <sub>COMP</sub>                                                                                     | 6.75         | 6.95       | 7.15         | ٧    |  |  |

| I <sub>CC1</sub>                  | Internal IC Consumption<br>Power Switch Enabled                         | MOSFET is switching at 300 kHz                                                                                                                      | 2.0          | 2.9        | 4.0          | mA   |  |  |

| I <sub>CC2</sub>                  | Internal IC Consumption<br>Power Switch Disabled                        | No Fault condition, V <sub>FB</sub> = 2.7 V                                                                                                         | -            | 2.0        | 2.5          | mA   |  |  |

| I <sub>CC3</sub>                  | Internal IC Consumption<br>Power Switch Disabled                        | Fault condition,<br>V <sub>FB</sub> = 2.7 V, V <sub>UV/OV</sub> < 1.0 V                                                                             | -            | 0.75       | 1.5          | mA   |  |  |

| POWER SW                          | VITCH CIRCUIT                                                           |                                                                                                                                                     | •            | •          |              | •    |  |  |

| R <sub>DSON</sub>                 | Power Switch Circuit On–State<br>Resistance                             | $I_D = 100 \text{ mA}$<br>$T_J = 25^{\circ}\text{C}$<br>$T_J = 125^{\circ}\text{C}$                                                                 | -<br>-       | 4.2<br>4.9 | 5.1<br>8.0   | Ω    |  |  |

| BVdss                             | Power Switch Circuit and Startup<br>Breakdown Voltage                   | $I_{DS\_OFF}$ = 100 $\mu$ A, $V_{UV\_OV}$ < 1.0 $V$                                                                                                 | 200          | -          | -            | V    |  |  |

| I <sub>DS_OFF</sub>               | Power Switch Circuit and Startup<br>Circuit Off-State Leakage Current   | $V_{DRAIN} = 200 \text{ V}, V_{UV_{OV}} < 1.0 \text{ V}$ $T_{J} = 25^{\circ}\text{C}$ $T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ | -<br>-       | 20<br>20   | 25<br>30     | μΑ   |  |  |

| t <sub>R</sub>                    | Switching Characteristics - Rise Time                                   | $V_{DS}$ = 48 V, R <sub>L</sub> = 480 Ω, Time (10%–90%)                                                                                             | -            | 7          | -            | ns   |  |  |

| t <sub>f</sub>                    | Switching Characteristics – Fall Time                                   | $V_{DS}$ = 48 V, R <sub>L</sub> = 480 Ω, Time (90%–10%)                                                                                             | -            | 10         | _            | ns   |  |  |

| INTERNAL                          | STARTUP CURRENT SOURCE                                                  |                                                                                                                                                     |              |            |              | -    |  |  |

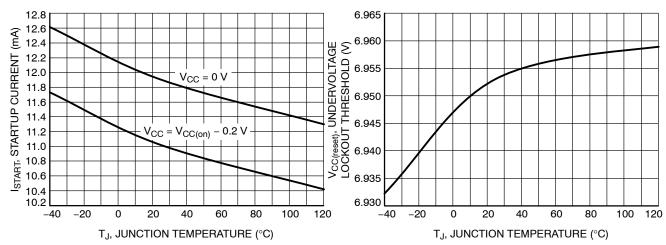

| I <sub>START1</sub>               | HV Current Source                                                       | Vcc = 0 V,<br>Tj = 25°C<br>Tj = -40°C to 125°C                                                                                                      | 10.0<br>9.0  | 12.0<br>-  | 14.0<br>15.0 | mA   |  |  |

| I <sub>START2</sub>               | HV Current Source                                                       | $Vcc = V_{CC ON} - 0.2 V$ $Tj = 25^{\circ}C$ $Tj = -40^{\circ}C \text{ to } 125^{\circ}C$                                                           | 9.0<br>8.0   | 11.0<br>-  | 13.0<br>16.0 | mA   |  |  |

| V <sub>start_min</sub>            | Minimum Startup Voltage                                                 | I <sub>START2</sub> = 0.5 mA,<br>Vcc = V <sub>CC_ON</sub> - 0.2 V, Tj = 25°C                                                                        | -            | 16.3       | -            | V    |  |  |

| ERROR AM                          | IPLIFIER                                                                |                                                                                                                                                     | •            | •          | -            |      |  |  |

| V <sub>REF</sub>                  | Reference Voltage                                                       | $V_{COMP} = V_{FB}$ , Follower Mode<br>$T_{J} = 25^{\circ}C$<br>$T_{J} = -40^{\circ}C$ to 125°C                                                     | 2.45<br>2.40 | 2.5<br>2.5 | 2.55<br>2.60 | V    |  |  |

| REG <sub>LINE</sub>               | Line Regulation                                                         | V <sub>CC</sub> = 8 V to 16 V, T <sub>J</sub> = 25°C                                                                                                | -            | 1.0        | 3.0          | mV   |  |  |

| I <sub>VFB</sub>                  | Input Bias Current                                                      | V <sub>FB</sub> = 2.3 V                                                                                                                             | _            | 70         | 150          | nA   |  |  |

| I <sub>SRC</sub>                  | COMP Source Current                                                     | V <sub>FB</sub> = 2.3 V                                                                                                                             | 80           | 95         | 125          | μΑ   |  |  |

| I <sub>SNK</sub>                  | COMP Sink Current                                                       | V <sub>FB</sub> = 2.7 V                                                                                                                             | 500          | 700        | 900          | μΑ   |  |  |

| V <sub>C_MAX</sub>                | COMP Maximum Voltage                                                    | I <sub>SRC</sub> = 0 μA, V <sub>FB</sub> = 2.3 V                                                                                                    | 3.95         | 4.17       | 4.5          | ٧    |  |  |

| $V_{C\_MIN}$                      | COMP Minimum Voltage                                                    | I <sub>SNK</sub> = 0 μA, V <sub>FB</sub> = 2.7 V                                                                                                    | -            | 91         | 200          | mV   |  |  |

| A <sub>VOL</sub>                  | Open Loop Voltage Gain                                                  | (Note 6)                                                                                                                                            | -            | 80         | -            | dB   |  |  |

| GBW                               | Gain Bandwidth Product                                                  | (Note 6)                                                                                                                                            | -            | 1.0        | -            | MHz  |  |  |

## **Table 3. ELECTRICAL CHARACTERISTICS**

(For typical values  $T_j = 25^{\circ}C$ , for min/max values  $T_j = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{DRAIN} = 48$  V,  $V_{CC} = 12$  V, unless otherwise noted)

| Symbol               | Parameter                       | Conditions                                                                                                          | Min        | Тур      | Max        | Unit    |

|----------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------|------------|----------|------------|---------|

| CURRENT              | LIMIT AND PWM COMPARATOR        | •                                                                                                                   |            | •        |            | <u></u> |

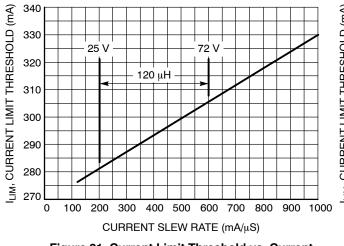

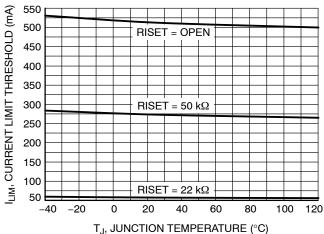

| C <sub>LIM_MAX</sub> | Max Current Limit Threshold     | CL pin Floating, $T_J = 25^{\circ}C$ , $(di/dt = 0.5 \text{ A/}\mu\text{s})$                                        | 420        | 512      | 600        | mA      |

| C <sub>LIM_MIN</sub> | Min Current Limit Threshold     | $R_{CL}$ = 20 k $\Omega$ , $T_{J}$ = 25°C, (di/dt = 0.1 A/ $\mu$ s)                                                 | -          | 57       | -          | mA      |

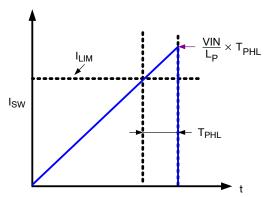

| T <sub>PLH</sub>     | Propagation Delay               | from Current Limit Detection to the Drain OFF State (Note 6)                                                        | -          | 100      | -          | ns      |

| T <sub>ON_MIN</sub>  | Min On Time Pulse Width         | FSW = 300 kHz (Note 6)                                                                                              | -          | 240      | -          | ns      |

| T <sub>ss</sub>      | Soft-Start Duration             | (Note 6)                                                                                                            | _          | 2.0      | -          | ms      |

| LINE UNDE            | ER/OVERVOLTAGE PROTECTIONS      |                                                                                                                     |            | •        |            | •       |

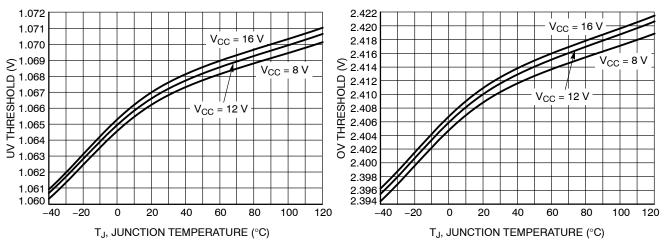

| V <sub>uv</sub>      | Undervoltage Lockout Threshold  | V <sub>FB</sub> = V <sub>COMP</sub> , Vin decreasing                                                                | 0.95       | 1.067    | 1.18       | V       |

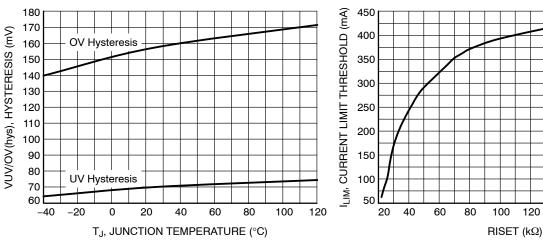

| V <sub>UV_hys</sub>  | Undervoltage Lockout Hysteresis |                                                                                                                     | -          | 70       | -          | mV      |

| luv                  | Input Bias Current              | V <sub>FB</sub> = 2.3 V                                                                                             | -          | 0        | 1          | μΑ      |

| V <sub>OV</sub>      | Overvoltage Lockout Threshold   | V <sub>FB</sub> = V <sub>COMP</sub> , Vin increasing (Note 7)                                                       | 2.3        | 2.41     | 2.5        | V       |

| V <sub>ov_hys</sub>  | Overvoltage Lockout Hysteresis  |                                                                                                                     | -          | 158      | -          | mV      |

| TEMPERAT             | TURE MANAGEMENT                 |                                                                                                                     |            |          |            |         |

| TSD                  | Thermal Shutdown                | (Note 6)                                                                                                            |            | 165      |            | °C      |

|                      | Hysteresis in Shutdown          | (Note 6)                                                                                                            |            | 20       |            | °C      |

| INTERNAL             | OSCILLATOR                      | •                                                                                                                   |            |          |            |         |

| f <sub>OSC1</sub>    | Oscillation Frequency, 300 kHz  | $C_T = 560 \text{ pF (Note 8)}$<br>$T_J = 25^{\circ}\text{C}$<br>$T_J = -40^{\circ}\text{C to }125^{\circ}\text{C}$ | 275<br>270 | 300<br>- | 325<br>335 | kHz     |

| f <sub>OSC2</sub>    | Oscillation Frequency, 960 kHz  | C <sub>T</sub> = 100 pF, T <sub>J</sub> = 25°C                                                                      | -          | 960      | -          | kHz     |

| I <sub>CT_C</sub>    | Timing Charge Current           | V <sub>CT</sub> = 3.25 V                                                                                            | -          | 172      | -          | μΑ      |

| I <sub>CT_D</sub>    | Timing Discharge Current        | V <sub>CT</sub> = 3.25 V                                                                                            |            | 517      |            | μΑ      |

| V <sub>R_pk</sub>    | Oscillator Ramp Peak Voltage    |                                                                                                                     | -          | 3.492    | -          | V       |

| $V_{R\_VLY}$         | Oscillator Ramp Valley          |                                                                                                                     | -          | 2.992    | -          | V       |

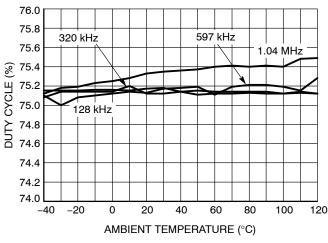

| DC <sub>MAx</sub>    | Maximum Duty Cycle              |                                                                                                                     | 70         | 76.5     | 80         | %       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

6. Guaranteed by design and characterized

7. The OV/UV option is disabled on the NCP1032B version

- 8. Oscillator frequency can be externally synchronized to the maximum frequency of the device

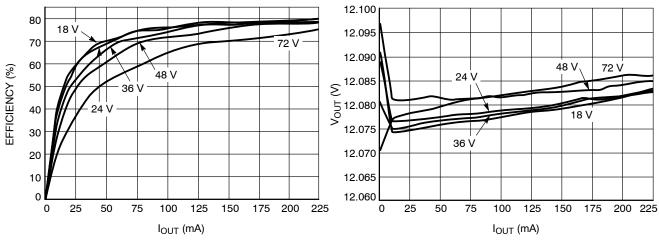

## TYPICAL OPERATING CHARACTERISTICS - Dual Output Isolated Flyback Converter

Figure 3. Efficiency vs.  $I_{OUT}$  at  $V_{IN}$  = 24, 36, 48 and 72 V, T1 = CoilCraft B0226–EL

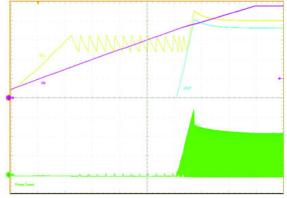

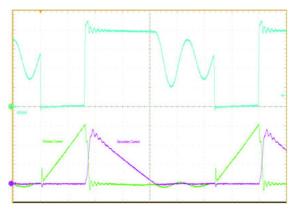

Figure 5. Startup Sequence, R<sub>CL</sub> Open, Output Load = 80  $\Omega$  (I<sub>OUT</sub> = 150 mA), 1 V<sub>CC</sub> 3.0 V/div DC, 2 V<sub>OUT</sub> 3.0 V/div DC, 3 V<sub>IN</sub> 10.0 V/div DC, 4 I<sub>PRI</sub> 100 mA/div DC, T = 20 ms/div

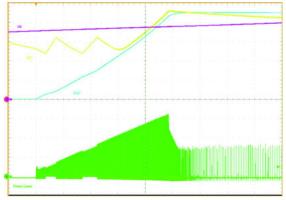

Figure 6. Soft–Start,  $R_{CL}$  open, Output No Load 1  $V_{CC}$  3.0 V/div DC, 2  $V_{OUT}$  3.0 V/div DC, 3 VIN 10.0 V/div DC, 4  $I_{PRI}$  100 mA/div DC,  $T = 500 \, \mu s/div$

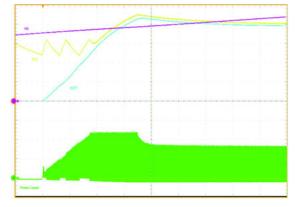

Figure 7. Soft–Start,  $R_{CL}$  = 32 k $\Omega$  ( $C_{LIM}$  = 250 mA), Output Load = 240  $\Omega$  ( $I_{OUT}$  = 50 mA), 1  $V_{CC}$  3.0 V/div DC, 2  $V_{OUT}$  3.0 V/div DC, 3  $V_{IN}$  10.0 V/div DC, 4  $I_{PRI}$  100 mA/div DC, T = 1.0 ms/div

Figure 8. Discontinuous Conduction Mode (DCM),  $I_{OUT}$  = 150 mA, 2  $V_{DRAIN}$  20 V/div DC, 3  $I_{SEC}$  30 mA/div DC, 4  $I_{PRI}$  100 mA/div, DC, T = 500 ns/div

## TYPICAL OPERATING CHARACTERISTICS

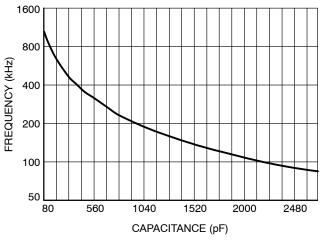

Figure 9. Frequency vs. Timing Capacitor C<sub>T</sub> at 25°C

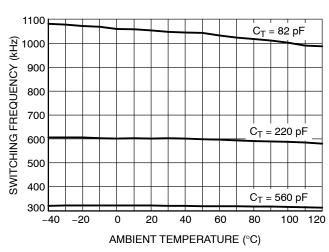

Figure 10. Oscillator Frequency vs. Junction Temperature

Figure 11. Maximum Duty Ratio vs. Temperature

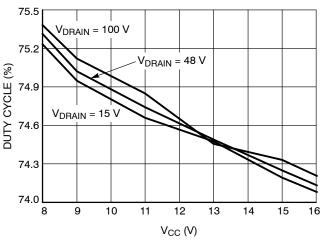

Figure 12. Maximum Duty Ratio vs. VCC Voltage

Figure 13. Minimum On Time vs. VCC

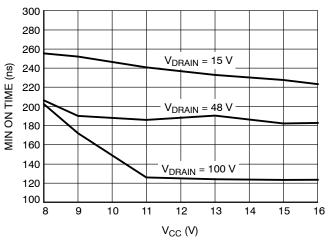

Figure 14. Power Switch Circuit and Startup Circuit Leakage Current vs. Drain Voltage

## TYPICAL OPERATING CHARACTERISTICS

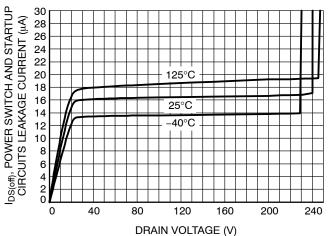

Figure 15. Power Switch R<sub>DSON</sub> vs. Junction Temperature

Figure 16. Vdrain Startup Threshold over Temperature

Figure 17. Startup Current vs. Junction Temperature

Figure 18. Undervoltage Lockout Threshold vs. Junction Temperature

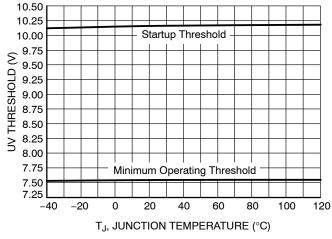

Figure 19. Supply Voltage Thresholds vs.

Junction Temperature

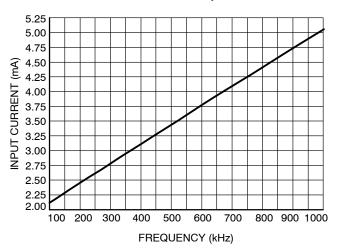

Figure 20. VCC Input Current at 12 V with an 18 V applied Drain voltage 25°C VS Oscillator Frequency

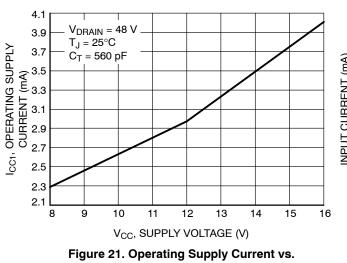

## TYPICAL OPERATING CHARACTERISTICS

6.5 1.04 MHz 6.0 INPUT CURRENT (mA) 5.5 5.0 4.5 597 kHz 4.0 3.5 320 kHz 3.0 2.5 128 kHz 2.0 -20 20 40 60 80 -40 0 100 120 AMBIENT TEMPERATURE (°C)

Supply Voltage at 320 kHz

Figure 22. VCC Input Current vs. Temperature over Frequency span VDrain = 48 V

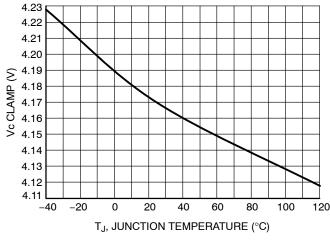

Figure 23. COMP Clamp Voltage vs. Junction Temperature

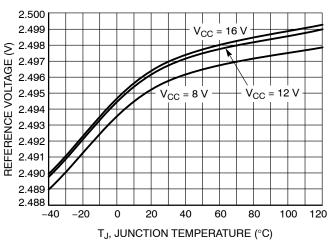

Figure 24. Reference Voltage vs. Junction Temperature

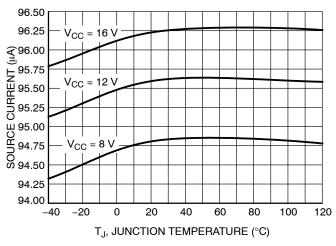

Figure 25. COMP Source Current vs. Junction **Temperature**

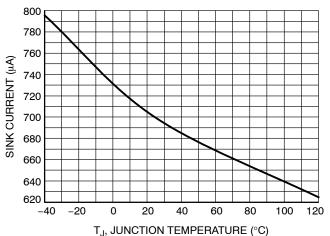

Figure 26. COMP Sink Current vs. Junction **Temperature**

## TYPICAL OPERATING CHARACTERISTICS

Figure 27. Undervoltage Threshold vs. Junction Temperature

Figure 28. Overvoltage Threshold vs. Junction Temperature

Figure 29. Under/Overvoltage Hysteresis vs. Junction Temperature

Figure 30. Current Limit Threshold vs.  $R_{CL}$ , Current Slew Rate = 0.5 A/ $\mu s$

140

160

180 200

Figure 31. Current Limit Threshold vs. Current Slew Rate

Figure 32. Current Limit Threshold vs.  $T_J$ , Current Slew RISET = Open = 0.5 A/ $\mu$ s, RISET = 55 k $\Omega$  = 0.3 A/ $\mu$ s, RISET = 22 k $\Omega$  = 0.1 A/ $\mu$ s

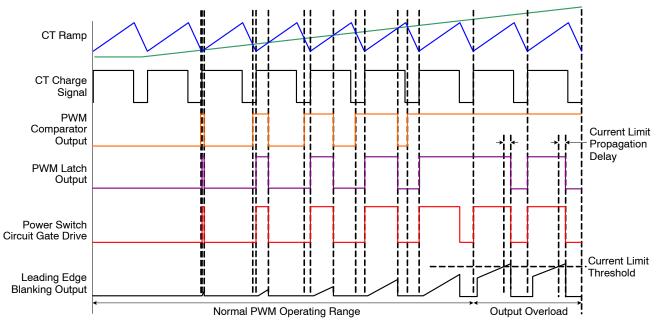

Figure 33. Pulse Width Modulation Timing Diagram

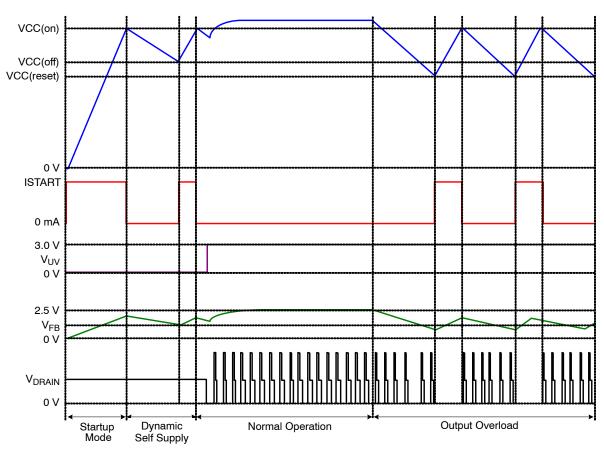

Figure 34. Auxiliary Winding Operation with Output Overload Timing Diagram

#### Introduction

The NCP1032 is a monolithic voltage-mode switching regulator designed for isolated and non-isolated bias supply applications. The internal startup circuit and the MOSFET are rated at 200 V, making them ideal for 24 V through 48 V telecom and 42 V automotive applications. In addition, the NCP1032 can operate from an existing 12 V supply. The regulator is optimized for operation up to 1 MHz.

The NCP1032 device incorporates all of the active power, control logic, protection circuitry, and power switch in a single IC. The compact design allows the designer to use minimal external components on several switching regulator applications, such as a secondary side bias supply or a low power DC–DC converter.

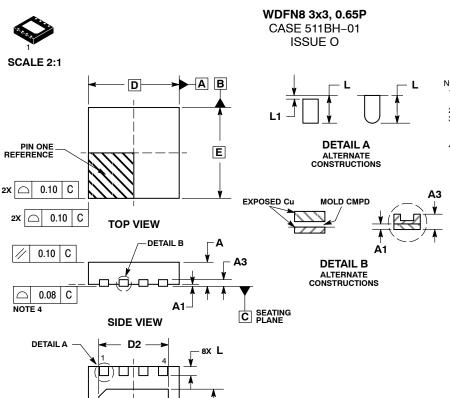

The NCP1032 is available in the space saving WDFN8 3 x 3 mm package and is targeted for applications requiring up to 3 W.

The NCP1032 has an extensive set of features including programmable cycle-by-cycle current limit, internal soft-start, input line under and over voltage detection comparators with hysteresis, regulator output undervoltage lockout with hysteresis and over temperature protection providing protection during fault conditions. A description of each of the functional blocks is given below and the functional block diagram is shown in Figure 2.

## **Startup Supply Circuit and Undervoltage Lockout**

The NCP1032 contains an internal 200 V startup regulator that eliminates the need for external startup components. The startup regulator consists of a 12 mA (typical) current source that supplies power from the input line (VDRAIN) pin to charge the capacitor on the V<sub>CC</sub> pin (C<sub>VCC</sub>). The act of charging the C<sub>VCC</sub> capacitor until it reaches 10.2 V while holding the power switch off is called Startup Mode (SM). Once the current source charges the  $V_{CC}$  voltage to 10.2 V (typical) the startup circuit is disabled and if no faults are present, the power switch circuit is enabled. The internal control circuitry will draw its current from the energy held by the C<sub>VCC</sub> capacitor. The startup regulator turns on again once  $V_{CC}$  reaches 7.55 V. The charging of the  $C_{VCC}$ capacitor to 10.2 V by the current source and the discharging by the control circuitry to 7.55 V will be henceforth referred to as Dynamic Self Supply (DSS).

If  $V_{CC}$  falls below 7.55 V while switching, the device enters a Restart Mode (RM). While in the RM the  $C_{VCC}$  capacitor is allowed to discharge to 6.95 V while the power switch is enabled. Once the 6.95 V threshold is reached, the power switch circuit is disabled, and the startup regulator is enabled to charge the  $C_{VCC}$  capacitor. The power switch is enabled again once the  $V_{CC}$  voltage reaches 10.2 V. Therefore, the external  $C_{VCC}$  capacitor must be sized such that a voltage greater than 6.95 V is maintained on the  $V_{CC}$  pin while the converter output reaches regulation. The output is delayed 0.4 ms ( $T_{SS\_Delay}$ ) from the released undervoltage lockout to the first switching pulse. The soft–start time  $T_{SS}$  is fixed at 2 ms to ramp the current from

its minimum value to its maximum value. The soft–start time is load and RCL dependent and can be computed in the soft–start section. The designer must evaluate the current draw of the regulator at the desired switching frequency over the  $V_{CC}$  and temperature operating range shown in Figures 20-22.  $C_{VCC}$  is calculated using the following equation:

$$C_{VCC} = \frac{I_{CC} \times \left(T_{SS\_Delay} + T_{SS}\right)}{V_{CC\_ON} - V_{CC\_MIN}} \rightarrow (eq. 1)$$

$$2.95 \ \mu F = \frac{4.0 \ mA \times \left(0.4 \ ms + 2.0 \ ms\right)}{10.2 \ V - 6.95 \ V}$$

I<sub>CC</sub> includes the NCP1032 bias current (I<sub>CC1\_MAX</sub>) and any additional current used to bias the feedback (if used). Assuming an I<sub>CC1\_MAX</sub> of 3.5 mA plus a 0.5 mA bias current for the feedback sensing resistors (if used), and Tss of 2 ms,  $C_{VCC}$  is calculated at 2.95 μF and should be rounded up to ensure design margin to 3.3 μF. Please note that if the feedback sensing resistors are connected to the  $V_{CC}$  pin (isolated main output topology) and  $C_{VCC}$  is increased to match  $C_{OUT}$ , the transient response of the converter will suffer. The poor transient response is due to the imbalanced capacitance to current ratio. The auxiliary winding has a significantly greater capacitance to current ratio than the output winding, taking it longer for  $C_{VCC}$  to follow  $C_{OUT}$  during a transient condition.

After initial startup, the  $V_{CC}$  pin should be biased above  $V_{CC\_min}$  using an auxiliary winding. This will prevent the startup regulator from turning on during normal operation, reducing device power dissipation. A load should not be directly connected to the  $V_{CC}$  pin. A load greater than 12 mA will override the startup circuit possibly damaging the part. The maximum voltage rating of the startup circuit is 200 V. Power dissipation should be observed to avoid exceeding the maximum power dissipation of the package. Figure 35 shows the recommended configuration for a non–isolated flyback converter.

Figure 35. Non-Isolated Bias Supply Configuration

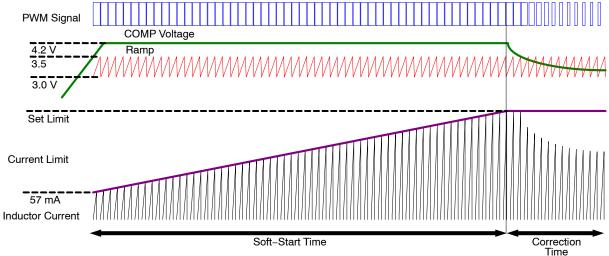

#### Soft-Start

The NCP1032 features an internal soft-start which reduces power-on stress and also contributes to the lower output overshoot. Once the V<sub>CC ON</sub> threshold is reached and there are no fault conditions, the power switch is enabled and the cycle-by-cycle current limit is ramped up slowly to the current limit threshold set by the CL pin. If the CL pin is open, the current limit will be set to its maximum value

and the soft-start time will be 2 ms as shown in Figure 36. The equation below can be used to calculate the soft-start time for all other current limit set values.

$$TSSR = \frac{Set_{Current} - Min_{Current}}{Max_{Current} - Min_{Current}} \times T_{SS} \rightarrow$$

$$1.07 \text{ ms} = \frac{300 \text{ mA} - 57 \text{ mA}}{512 \text{ mA} - 57 \text{ mA}} \times 2 \text{ ms}$$

(eq. 2)

Figure 36. Soft-Start Time

The compensation of the converter must be manipulated to minimize the overshoot of the output voltage during startup, details are in the compensation section.

## **Line Under and Over Voltage Detectors**

The NCP1032 incorporates Vin input line under voltage (UV) and over voltage (OV) shutdown circuits. If the UV/OV pin is set below 1.0 V or above 2.4 V thresholds the power switch will stop switching and the part will use DSS until the problem is corrected. The comparators incorporate typical voltage hysteresis of 70 mV (UV) and 158 mV (OV) to prevent noise from inadvertently triggering the shutdown circuit. The UV/OV sense pin can be biased using an external resistor divider from the input line as shown in Figure 37. The UV/OV pin should be bypassed using a 1 nF capacitor to prevent triggering the UV/OV circuit during normal switching operation.

from the Input Line

The resistive network impedance must not be too high to keep good voltage accuracy and not too low to minimize power losses. A 200 k $\Omega$  to 1.2 M $\Omega$  range is recommended for the high side resistor R3. If the designer wanted to set the undervoltage threshold to 32 V, the resistor divider should be designed according to the following equation:

$$R4 = \frac{V_{UV} \times R3}{V_{IN\_UV} - V_{UV}} \rightarrow \tag{eq. 3}$$

$$34.49 \text{ k}\Omega = \frac{1.067 \times 1 \text{ M}\Omega}{32 \text{ V} - 1.067} \approx 34.0 \text{ k}\Omega \text{ (R96 Value)}$$

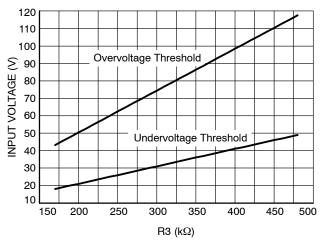

The OV threshold monitored at the UV/OV pin is 2.41 times higher than the UV threshold, leading to an OV threshold of 73.3 V for the calculated R96 value. Designers can quickly set the OV/UV thresholds by referencing Figure 38.

Figure 38. UV/OV Resistor Divider Thresholds with R4 Set to 10 k

The UV/OV pin can also be used to implement a remote enable/disable function. If an external transistor pulls the UV/OV pin below 1.0 V (or above 2.4 V) the converter will be disabled and no switching is allowed. A device version is available without the OV protection feature, see the ordering information section.

## **Error Amplifier**

The internal error amplifier (EA) regulates the output voltage of the bias supply. The scaled signal is fed into the feedback pin (VFB) which is the inverting input of the error amplifier. It compares a scaled voltage signal to an internal trimmed 2.5 V reference connected to its non-inverting input.

The output of the error amplifier is internally connected to a PWM comparator and also available externally through the COMP pin for frequency compensation. To insure normal operation, the EA compensation should be selected such that the EA frequency response crosses 0 dB below 80 kHz.

The error amplifier feedback bias current is less than 200 nA over the operating range. The output source and sink currents are typically 95  $\mu A$  and 700  $\mu A$ , respectively.

Under load transient conditions, COMP may need to move from the bottom to the top of the  $C_T$  ramp. A large current is required to complete the COMP swing if small resistors or large capacitors are used to implement the compensation network. In which case, the COMP swing will be limited by the EA source current. Optimum transient responses are obtained if the compensation components allow the COMP pin to swing across its operating range in 1 cycle.

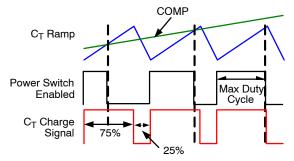

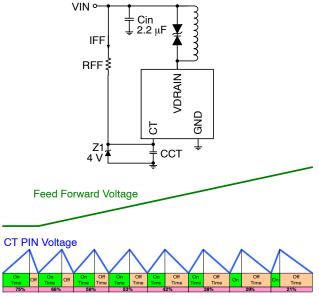

## Oscillator, Voltage Feed Forward, and Sync Capability

The oscillator is optimized for operation up to 1 MHz and its frequency is set by the external timing capacitor ( $C_T$ ) connected to the  $C_T$  pin. The oscillator has two modes of operation: free running and synchronized (sync). While in free running mode, an internal current source sequentially charges and discharges  $C_T$  generating a voltage ramp between 3.0 V and 3.5 V. Under normal operating conditions, the charge ( $I_{CT\_C}$ ) and discharge ( $I_{CT\_D}$ ) currents are typically 172  $\mu A$  and 515  $\mu A$ , respectively. The charge/discharge current ratio of 1:3 discharges  $C_T$  in 25% of the total period. The power switch is disabled while  $C_T$  is discharging, guaranteeing a maximum duty cycle of 75% as shown in Figure 39.

Figure 39. Auxiliary Winding Operation with Output Overload Timing Diagram

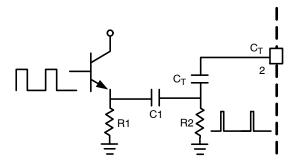

The oscillator frequency should be set no more than 25% below the target sync frequency to maintain an adequate voltage ramp and provide good noise immunity. A possible circuit to synchronize the oscillator is shown in Figure 40.

Figure 40. External Frequency Synchronization Circuit

Voltage feed forward can be implemented by connecting a resistor from the input voltage to the  $C_T$  pin. RFF supplies a current that allows the input voltage to modify the maximum duty cycle rather than the standard 75% maximum. If the designer wanted to implement a fixed lower duty cycle, a resistor can be tied to a fixed voltage source such as  $V_{AUX}$  or a voltage reference. If voltage feed forward is used, the frequency can shift dramatically depending on the value of the resistor.

Figure 41. Voltage Feed Forward

$$\begin{split} R_{VFF} &= \frac{\text{VIN}_{\text{MIN}} - \text{Ramp}}{\text{I}_{\text{CT\_D}} - \text{D}_{\text{MAX}} \times \left(\text{I}_{\text{CT\_C}} + \text{I}_{\text{CT\_D}}\right)} \Rightarrow \\ 320 \text{ k}\Omega &= \frac{32 \text{ V} - 3.25 \text{ V}}{517 \text{ }\mu\text{A} - 62\% \times \left(172 \text{ }\mu\text{A} + 517 \text{ }\mu\text{A}\right)} \end{split}$$

#### **PWM Comparator and Latch**

The Pulse Width Modulator (PWM) comparator compares the error amplifier output (COMP) to the  $C_T$  ramp and generates a proportional duty cycle. The power switch is disabled while COMP voltage is below the  $C_T$  ramp signal. Once COMP reaches the ramp signal, the power switch is enabled. If COMP is at the bottom of the  $C_T$  ramp, the converter operates at minimum duty cycle. While COMP increases, the duty cycle increases until COMP reaches the peak of the  $C_T$  ramp, at which point the controller operates at maximum duty cycle.

The  $C_T$  charge signal is filtered through a one shot pulse generator to set the PWM latch and enable switching at the beginning of each period. Switching is allowed while the  $C_T$  ramp is below COMP and a current limit fault is not present.

The pulse width modulation technique is seen in Figure 39.

The PWM comparator and latch propagation delay are less than 200 ns. If the system is designed to operate with a minimum on time less than 200 ns (no or light load), the converter will skip pulses. Skipping pulses is usually not a problem, unless operating at a frequency close to the audible range. Skipping pulses is more likely when operating at high frequencies during high input voltage and minimum load conditions.

A 2 k $\Omega$  series resistor is included for ESD protection between the internal EA output and the COMP pin. Under normal operation, a 220 mV offset is observed between the  $C_T$  ramp and the COMP crossing points. The series resistor does not interact with the error amplifier transfer function.

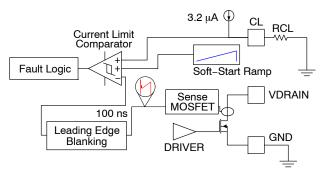

## **Programmable Current Limit**

The power switch circuit incorporates SENSEFET® technology to monitor the drain current. A sense voltage is generated by driving a sense element, R<sub>SENSE</sub>, with a current proportional to the drain current. The sense voltage is compared to an externally programmable reference voltage on the non–inverting input of the current limit comparator. If the sense voltage exceeds the setup reference level, the comparator resets the PWM latch and the switching cycle is terminated. The reference level threshold is programmable by a resistor (R<sub>CL</sub>) connected to the CL pin shown in Figure 42.

By limiting the peak current to the needs of the application, the transformer sizing can be scaled appropriately to the specific requirements which allows the PCB footprint to be minimized. The NCP1032 maximum drain current limit thresholds are 512 mA.

Please refer to Figure 30 for I<sub>LIM</sub> vs. R<sub>CL</sub> relationship.

Figure 42. Current Limit Threshold and Propagation Delay

The propagation delay is measured from the time an overcurrent fault appears at power switch circuit drain, to the start of the turn-off transition as shown in Figure 43. The current limit propagation delay time is typ. 100 ns. The propagation must be accounted for when designing the power supply, as it will result in a constant power output through the transformer when the output is shorted. The constant power can cause the transformer to rise in temperature permanently damaging the magnetics. This can be mitigated by placing a  $10~\Omega$  resistor in series with the output rectification diode.

Figure 43. Current Limit Threshold and Propagation Delay

## **Adaptive Leading Edge Blanking**

Each time the power switch circuit is turned on, a narrow voltage spike appears across R<sub>SENSE</sub>. The spike is due to the power switch circuit gate to source capacitance, transformer interwinding capacitance, and output rectifier recovery time. The spike can cause a premature reset of the PWM latch. A proprietary active Leading Edge Blanking (LEB) circuit masks the current signal to prevent the voltage spike from resetting the PWM latch. The active LEB masks the current signal until the power switch turn on transition is complete. The adaptive LEB period provides better current limit control compared to a fixed blanking period.

## **Power Switch Circuit Protection**

The NCP1032 monolithically integrates a 200 V power switch with control logic circuitry. The power switch is designed to directly drive the converter transformer. The gate drive is tailored to control switching transitions and help limit electromagnetic interference (EMI).

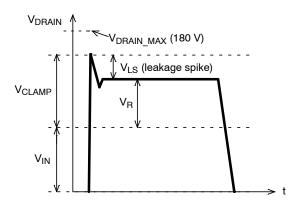

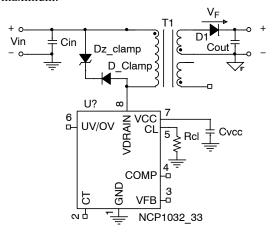

For a Flyback topology a large transient voltage spike appears at the transformers primary side after the power switch turns off. These spikes are a function of the transformer leakage inductance ( $L_{LP}$ ) on either the primary or secondary side. A circuit is needed to clamp the leakage spike, limiting the voltage drain excursion to a safe value. The operating  $V_{DRAIN\_MAX}$  is 200 V as depicted in Figure 44. Two such circuits are the passive RCD network or a zener clamp as depicted in Figure 45 and Figure 46.

Figure 44. Power Switch Waveforms with Clamping

Figure 45. Passive RCD Clamp Network

The passive RCD network is the most standard circuitry and the formula below is used to calculate  $R_{CLAMP}$  and  $C_{CLAMP}$ .

$$\begin{split} R_{CLAMP} &= \frac{2 \times V_{CLAMP} \times \left(V_{CLAMP} - (V_{OUT} + V_F) \times N\right)}{L_{LP} \times I_{PEAK}^2 \times F_{SW}} \\ C_{CLAMP} &= \frac{V_{CLAMP}}{V_{LS} \times F_{SW} \times R_{CLAMP}} \end{split} \tag{eq. 5}$$

The voltage leakage spike ( $V_{LS}$ ) is usually selected 50 to 70% above the reflected value  $V_R = N \ x \ (V_{OUT} + V_F)$  and ( $V_{IN} + V_{CLAMP}$ ) must be below the operating  $V_{DRAIN-MAX}$  which is 200 V. The diode used for the clamping circuit needs to be at minimum fast or ultrafast recovery and an MURA110 represents a good choice. One major drawback of the RCD network lies in its dependency upon the peak current. The worse case occurs when  $I_{PEAK}$  and  $V_{IN}$  are at the maximum.

Figure 46. Zener Clamp Network

The zener diode is probably the most expensive but offers the best protection and a very precise clamping level. Select the zener voltage to set  $V_{LS}$  level between 10 to 15 V above the reflected voltage  $V_R$  so VZener =  $V_{LS} + V_R$ . The zener diode must be able to handle the voltage rating and power dissipation during the switch turn-off time. For the NCP1032, a 0.5 W zener diode, like the MMSZ47T1 is suitable.

#### Thermal Shutdown

Internal thermal shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated at 165°C, the power switch circuit is disabled. Once the junction temperature falls below 145°C, the NCP1032 is allowed to resume normal operation. This feature is provided to prevent catastrophic failures from accidental device overheating. It is not intended to be used as a substitute for proper heat sinking.

## **Application Considerations**

## **Typical Applications**

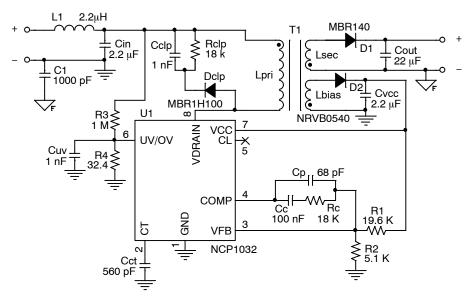

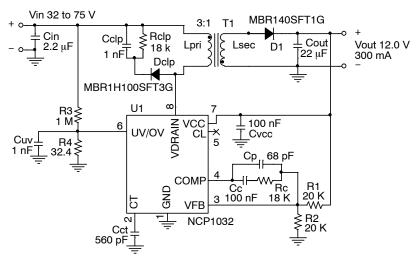

A  $12\,\mathrm{V}/3\,\mathrm{W}$  bias supply for  $36\,\mathrm{V}$  to  $75\,\mathrm{V}$  telecom systems,  $1500\,\mathrm{V}$  isolation DC–DC converters. The NCP1032 is configured in Flyback topology and operates in Discontinuous Conduction Mode (DCM) to offer a low–cost, high efficiency solution. The circuit schematic is shown in Figure 47. Transformer T1 is available as a CoilCraft B0226–EL. Capacitor  $C_{CT}$  sets the switching frequency at approximately  $300\,\mathrm{kHz}$ .

Output voltage regulation and overall efficiency are shown in Figure 3 and Figure 4 on page 6. The resistor divider formed by R3 and R4 sets the undervoltage lockout threshold at about 32 V.

Application Note AND8119/D describes the design of this bias supply system.

Figure 47. 48 V to Isolated 12 V / 3 W Bias Supply Schematic

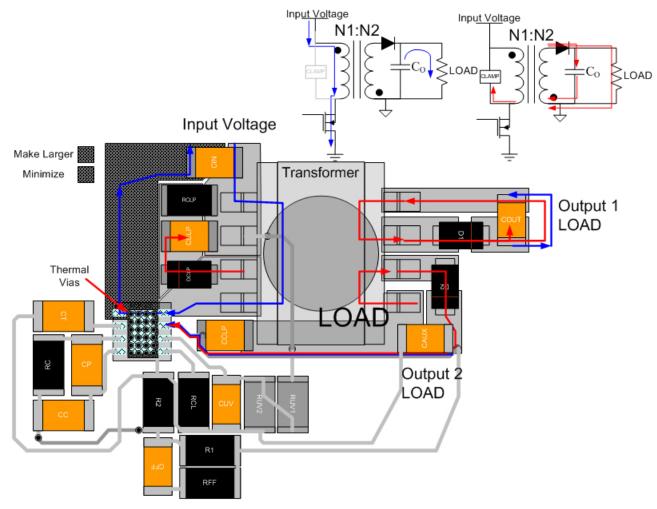

### **Layout Recommendations**

To prevent EMI problems high current copper traces which have high frequency switching should be optimized. Therefore, use short and wide traces for power current paths and for power ground traces especially transformer trace connections (primary and secondary). When power is transferred from input to output, there is a period of time when the power switch is on, referred to as "on time," and a period of time when the switch is off, referred to as "off time." When the power switch is on, the input voltage is applied across the primary side of the transformer and current increases in the primary inductance. Further, when the power switch is on the output current is supplied from the output capacitance. When the power switch is off, current on the primary side conducts through the clamp or snubber circuit. On the secondary side current is conducting through the rectification diode, providing power to the output and replenishing energy in the output capacitances as shown in Figure 48. Electromagnetic radiation is minimized by keeping VDRAIN leads, output diode, and output bypass capacitor leads as short as possible. It is important to minimize the area of the VDRAIN nodes and used the ground plane under the switcher circuitry to prevent interplane coupling and minimize cross-talk to sensitive

signals and ICs. The exposed pad of the package must be connected to the ground plane of the board which is important for EMI and thermal management. Finally, it is always good practice to keep sensitive traces such as feedback connection (VFB and COMP) as far away from switched signal connections (VDRAIN) as possible. Figure 48 shows an example of an optimized PCB layout.

#### **Thermal Considerations**

Careful attention must be paid to the internal power dissipation of the NCP1032. Power dissipation is a function of efficiency and output power. As output power requirements increase, proper component selection includes adjusting RDSON, forward voltage of diodes, and enlarging packages. For example, if a transformer's size were increased to lower the DCR or/and increase the inductance efficiency will improve at heavier loads. The exposed thermal pad is designed to be soldered to the ground plane used as a heat sink. The ground plane size should be maximized and connected to the internal and bottom copper ground planes with thermal vias placed directly under the package to spread heat generated by the NCP1032 as depicted Figure 48.

Figure 48. Recommended PCB Layout

Figure 49. 48 V to 5.0 V DC-DC Converter Without Auxiliary Winding

Figure 50. 48 V to 12.0 V DC-DC Converter Without Auxiliary Winding

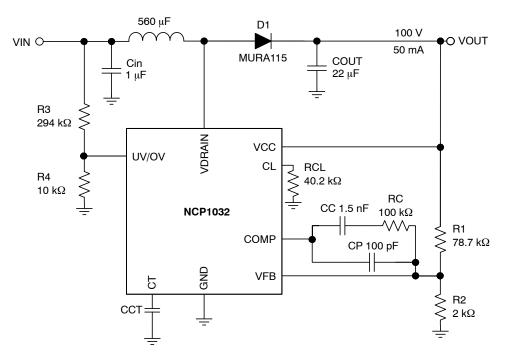

Figure 51. Typical Application Circuit Boost Circuit Configuration

## **ORDERING INFORMATION**

| Device        | OV Protection | Marking | Package                | Shipping <sup>†</sup> |

|---------------|---------------|---------|------------------------|-----------------------|

| NCP1032AMNTXG | Enable        | 1032A   | WDFN8 3x3<br>(Pb-Free) | 3,000 / Tape & Reel   |

| NCP1032BMNTXG | Disable       | 1032B   | WDFN8 3x3<br>(Pb-Free) | 3,000 / Tape & Reel   |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

0.10 C A B

0.05 C NOTE 3

Ф

**DATE 21 JUL 2010**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION 6 APPLIES TO PLATED

TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM FROM TERMINAL TIP. COPLANARITY APPLIES TO THE EXPOSED

- PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |  |  |  |  |  |

|-----|-------------|------|--|--|--|--|--|

| DIM | MIN MAX     |      |  |  |  |  |  |

| Α   | 0.70        | 0.80 |  |  |  |  |  |

| A1  | 0.00        | 0.05 |  |  |  |  |  |

| A3  | 0.20        | REF  |  |  |  |  |  |

| b   | 0.25        | 0.35 |  |  |  |  |  |

| D   | 3.00        | BSC  |  |  |  |  |  |

| D2  | 2.20 2.40   |      |  |  |  |  |  |

| E   | 3.00        | BSC  |  |  |  |  |  |

| E2  | 1.40 1.6    |      |  |  |  |  |  |

| е   | 0.65 BSC    |      |  |  |  |  |  |

| K   | 0.45 REF    |      |  |  |  |  |  |

| L   | 0.20 0.40   |      |  |  |  |  |  |

| L1  | 0.15        |      |  |  |  |  |  |

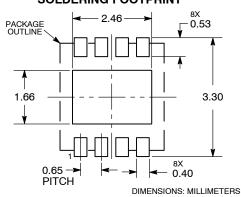

#### **RECOMMENDED SOLDERING FOOTPRINT\***

**BOTTOM VIEW**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON49350E       | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | WDFN8, 3X3, 0.65P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative