# 8-Port PSE Controller for PoE Systems

#### **Features**

- IEEE 802.3AF-2003 and 802.3AT-2009 compliant

- Single DC power supply voltage input (45~57V)

- Pin Compatible with IP808

- Wide temperature range: -40°C ~+85°C

- Supplies 8 independent power ports

- Built-in power FETs

- 0.1R sense embedded

- Built in Total current limit for Smart power management.

- I<sup>2</sup>C Bus to access up to 8 x IP808AR devices

- Continuous system monitoring for every port

- Independent system parameters setting for every port

- Thermal monitoring and protection

- Built-in 3.3V regulators for external devices

- Built-in Power on Reset

- Configurations: (1) 30W x 8 ports

- Built-in LEDs control for multi-port use

- Built-in EEPROM interface for dumb application managements.

- Low power dissipation

- Direct or Shift Overload LED

- H/W ALT A/ALT B mode Setting

- Package and operation temperature 48 Pin(7mmx7mm) QFN, -40~85°C

# **Application**

- 8 port PSE Switch

- 24 port PSE Switch

### **General Description**

IP808AR is an 8-port PSE (Power Sourcing Equipment) controller IC for PoE (Power over Ethernet) systems. It integrates power, analog and logic circuits into a single chip, and can be used for Midspans and Endpoint PSE applications.

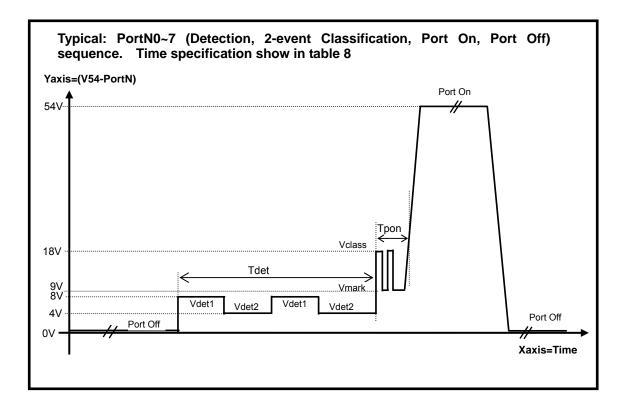

IP808AR meets all IEEE 802.3AF-2003 requirements, such as multi-point resistor detection, PD classification, DC Disconnect, and Back-off for Midspans. It also meets all IEEE 802.3AT-2009 requirements, such as two-event classification and supply maximum 36W per port.

IP808AR comprises internal temperature monitoring and thermal protection to protect against junction overheating. The 3.3V regulator is built-in to support external devices. Multiple IP808ARs can integrate to build an 8 x N ports PSE system, and I<sup>2</sup>C bus uses to collect PD power status from each IP808AR to support global power managements.

Management switch host has options to communicate IP808ARs via I<sup>2</sup>C bus for PSE management activities. Optocouplers can be implemented to provide electrical isolations between the host and IP808ARs for signal communication.

# **Table of Contents**

|    | atures                                             |    |

|----|----------------------------------------------------|----|

|    | eneral Description                                 |    |

|    | ble of Contents                                    |    |

|    | t of Figures                                       |    |

|    | t of Tables                                        |    |

| Re | vision History                                     |    |

| 1  |                                                    | 5  |

|    | 1.1 IP808AR Pin diagram (QFN48)                    |    |

| 2  | IP808AR application diagram                        | 6  |

|    | 2.1 Dumb & Smart device application                |    |

| 3  | Block diagram                                      |    |

|    | 3.1 Blocks Description                             |    |

|    | 3.1.1 Global Blocks                                |    |

|    | 3.1.2 Per Port Block                               |    |

|    | Pin description                                    |    |

| 5  | Functional Description                             |    |

|    | 5.1 System Reset                                   |    |

|    | 5.2 Operation Modes & System Configuration         | 14 |

|    | 5.3 I <sup>2</sup> C Slave Interface               |    |

|    | 5.4 EEPROM controller                              |    |

|    | 5.5 PSE State Machine                              |    |

|    | 5.6 Power Manager                                  |    |

|    |                                                    |    |

|    | 5.6.2 Power Configuration                          |    |

|    | 5.6.4 Power Event Handling                         |    |

|    | 5.7 Real time Monitor Power Event                  | 30 |

|    | 5.8 Port Status and Interrupt                      |    |

|    | 5.9 Total Current Limit                            |    |

|    | 5.10 LED Interface                                 |    |

| 6  | IP808AR Register descriptions                      |    |

| 7  | Electrical Characteristics                         |    |

| •  | 7.1 Absolute Maximum Ratings                       |    |

|    | 7.2 Operating Conditions                           |    |

|    | 7.3 Electrical Characteristics for Analog I/O Pins |    |

|    | 7.4 IEEE802.3 AF/AT Mode Parameters                |    |

|    | 7.5 Digital Electrical Characteristics             |    |

|    | 7.6 AČ Timing                                      |    |

|    | 7.6.1 Power On Sequence and Reset Timing           |    |

|    | 7.6.2 EEPROM Timing                                |    |

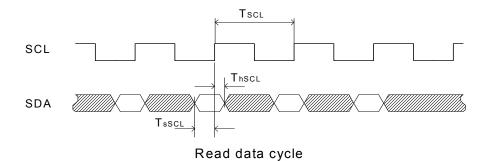

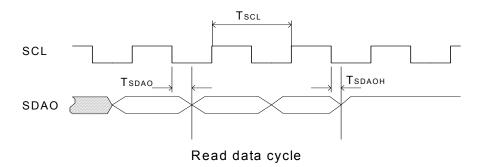

|    | 7.6.2.1 Data read cycle                            | 52 |

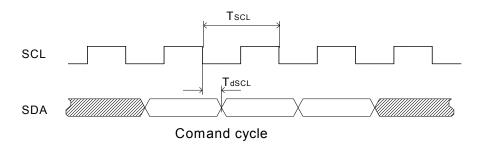

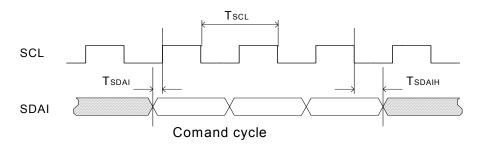

|    | 7.6.2.2 Command cycle                              |    |

|    | 7.6.3 I <sup>2</sup> C Timing                      | 53 |

|    | 7.6.3.1 Data read cycle                            | 53 |

|    | 7.6.3.2 Command cycle                              | 53 |

|    | 7.7 Thermal Data                                   |    |

| 8  | Order Information                                  |    |

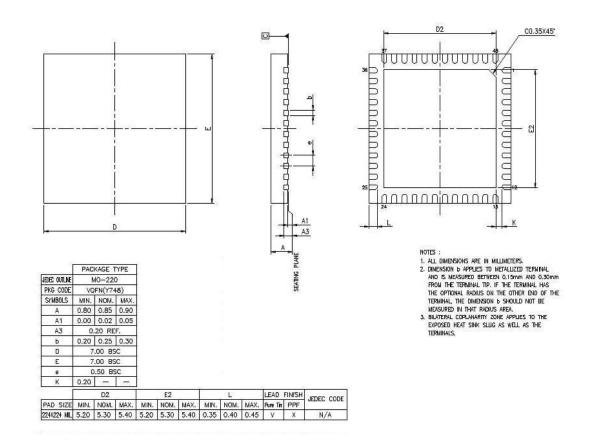

| 9  | Package Detail                                     |    |

|    | 9.1 48 OFN Outline Dimensions (in mm)              | 55 |

| <b>List of Figure</b> | S                                                               |          |

|-----------------------|-----------------------------------------------------------------|----------|

| Figure 1              | IP808AR Pin Diagram                                             | <u>5</u> |

| Figure 2              |                                                                 |          |

| Figure 3              |                                                                 |          |

| Figure 4              |                                                                 |          |

| Figure 5              |                                                                 |          |

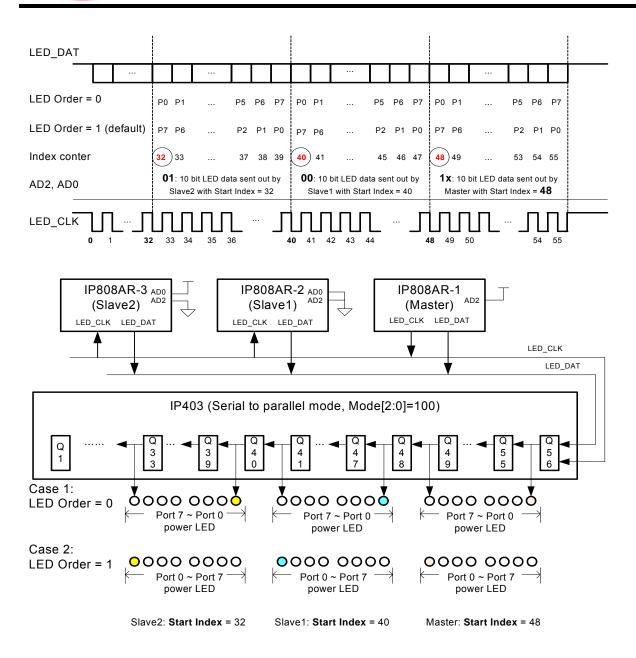

| Figure 6              | LED behavior and system diagram of multiple IP808AR application | 39       |

| Figure 7              |                                                                 |          |

| Figure 8              |                                                                 | 51       |

| Figure 9              |                                                                 | 52       |

| Figure 1              | 0 EEPROM Command Cycle Timing Diagram                           | 52       |

| Figure 1              | EEPROM Command Cycle Timing Diagram                             | 53       |

| Figure 1              | 2 I <sup>2</sup> C Command Cycle Timing Diagram                 | 53       |

| Figure 1              | 3 Package Outline Dimensions                                    | 55       |

| List of Tables        |                                                                 |          |

|                       | Die description                                                 | 44       |

| Table 1<br>Table 2    | Pin description                                                 |          |

| Table 3               | Mode Setting  Available functions in Operation modes            |          |

| Table 3               | Port power off conditions                                       |          |

| Table 4               |                                                                 |          |

| Table 5               | Register Page 0 description                                     |          |

| Table 7               | Electrical Characteristics                                      |          |

| Table 7               | IEEE802.3 AF/AT Mode Parameters                                 |          |

| Table 9               | Digital Electrical Characteristics                              |          |

|                       | Order Information                                               |          |

| Table 10              |                                                                 |          |

# **Revision History**

| Revision #       | Date       | Change Description |

|------------------|------------|--------------------|

| IP808AR-DS-Darft | 2018/08/07 | Initial release    |

| •                |            |                    |

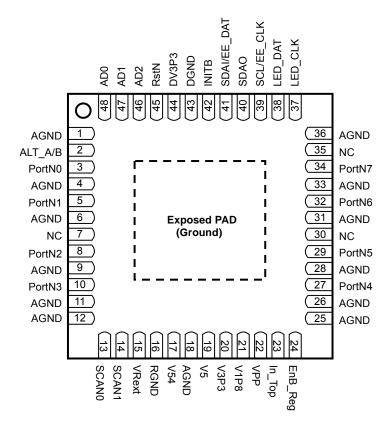

# 1 Pin diagram

## 1.1 IP808AR Pin diagram (QFN48)

(7mm X 7mm Top view)

Exposed pad is system GND, must be soldered to PCB ground plane

Figure 1 IP808AR Pin Diagram

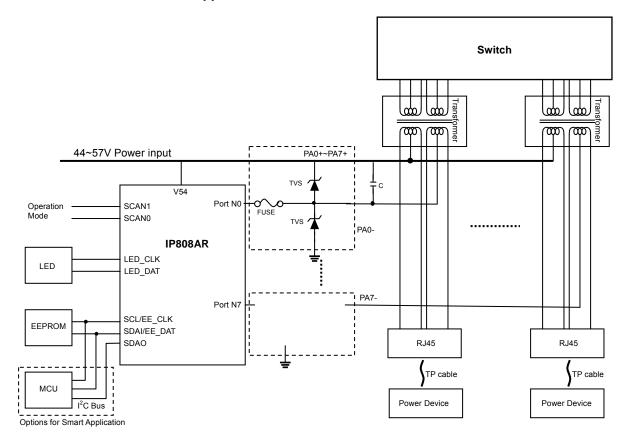

# 2 IP808AR application diagram

## 2.1 Dumb & Smart device application

Figure 2 Application Diagram

| Application | MCU | EEPROM                  | IP808AR Mode setting | Reference   |

|-------------|-----|-------------------------|----------------------|-------------|

| Smart       | V   | X                       | Manual mode          | Section 5.3 |

| Dumb        | X   | V: update default value | Auto mode            | Section 5.4 |

| Dullib      | ^   | X: use default value    | Auto mode            | Section 5.4 |

V: necessary; X: unnecessary

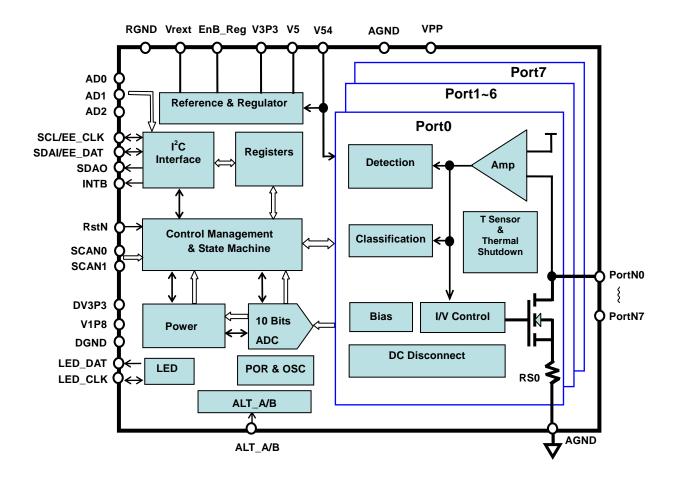

# 3 Block diagram

Figure 3 Block Diagram

### 3.1 Blocks Description

## The blocks of IP808AR include global blocks for and per port blocks as below:

Global blocks for 8 ports:

- Reference & Regulator

- ◆ I<sup>2</sup>C Interface

- Registers

- ◆ Control Management & State Machine

- Power Management

- ◆ 10 Bits ADC

- ◆ POR & OSC

### Per port blocks for individual port:

- Detection

- Classification

- ◆ I/V Control & Fold-back

- Amp

- DC Disconnect

- ◆ T sensor & Thermal Shutdown

- ◆ Bias

- Power MOSFET

#### 3.1.1 Global Blocks

#### > Reference & Regulator:

The Reference & Regulator generates 1.8V, 3.3V and 5V power for internal use and 3.3V power also can supply typical 6mA current on V3P3 pin for external devices if EnB\_Reg pin is connected to GND. If EnB\_Reg is connected to 3.3V, the internal 3.3V regulator is disabled and V3P3 pin should be connected to an external 3.3V power source.

It also generates 1.25V voltage on VREXT pin, which is connected to ground through an external  $62K\Omega$  resistor, to generate internal bias current.

### > Registers:

The "Registers" provides the 8 bits data for Ilim, Icut programming registers, and all other needing registers per port

### Control Management & State Machine:

This block provides all the control procedures to perform PoE function. The "State Machine" implements as specified in the IEEE802.3AF/AT.

### Power Management:

The "Power Management" provides power management method to meet PD power requirement, or not to power PD if power is not enough.

### > 10 Bits ADC:

The 10 Bits ADC used to convert analog signals into digital bus for Control Management, State Machine, and Power Management for request.

#### POR & OSC:

The POR generates an internal power on reset signal when V54 is power on. The POR also monitors V3P3, DV3P3, V5, & V54 voltage level. If these voltages level are below specific thresholds, a reset signal generates and resets IP808AR.

The OSC is an internal oscillator to generate 8MHz clock for IP808AR timing source.

#### > I<sup>2</sup>C Interface:

A host (master) can communicates with multiple IP808AR (slave) via I<sup>2</sup>C Interface (SCL/EE\_CLK, SDAO, SDAI/EE\_DAT) to collect PD power status to support global power managements and all control requirements.

#### 3.1.2 Per Port Block

#### > Detection:

The IP808AR uses 4 points detection method to discover PD. It shall accepted resistance as a valid "AF/AT PD" between  $19K\Omega$  and  $26.5K\Omega$ , with a paralleled capacitance small than 0.15uF.

It shall rejects resistance with paralleled capacitance as an invalid "AF/AT PD" small than 15K $\Omega$ , larger than 33K $\Omega$ , or capacitance larger than 10uF.

The specification is as specified in the IEEE802.3AF/AT.

#### > Classification:

The "Classification" is to distinguish the requested power of PD as specified in the IEEE802.3AF/AT. In IEEE 802.3AF, classification is 1-event method.

In IEEE 802.3AT, classification is 2-event method.

#### > I/V Control:

The "I/V Control" is to control the slew rate during "detection, classification, inrush, short circuit, power off ... and so on", as specified in IEEE802.3AF/AT

When short circuit event occurs, the "I/V control" will reduce the port current instantaneously to protect the power MOSFET from damages.

### > Amp:

The "AMP" is used to convert the differential voltage between V54 and PortNx into single end voltage. This voltage will be fed into the "Detection, Classification, I/V Control" blocks to perform the IEEE8023AF/AT specifications.

#### > DC Disconnect:

The IP808AR supports DC Disconnect function according to IEEE 802.3AF-2003 & IEEE 802.3AT-2009 requirement.

This DC Disconnect continuously monitors port current after port inrush time, and disconnects port current when port current is below 7.5mA (typical) for more than 360ms (typical) .Please refer to Tmpdo in table 8 for detail information.

#### > T sensor & Thermal Shutdown:

The "T sensor" senses the temperature of each port, and will shutdown the port current as temperature beyond 150°C. When temperature goes down to 129°C, the port will start again.

#### Bias:

The "Bias" provides the current & voltage bias for all ports according to control signals.

# 4 Pin description

| Type | Description              | Туре | Description               |

|------|--------------------------|------|---------------------------|

| Р    | Power or Ground          | 0    | Output                    |

| I    | Input                    | OD   | Open drain                |

| IL   | Input latched upon reset | NC   | No connection in internal |

Table 1 Pin description

| Pin<br>no. | Label   | Туре | Description                                                                                                                                                                                                                                                                                                                       |  |  |

|------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|            | EPAD    | Р    | Exposed pad, it should be connected to AGND.                                                                                                                                                                                                                                                                                      |  |  |

| 1          | AGND    | Р    | Analog ground                                                                                                                                                                                                                                                                                                                     |  |  |

| 2          | ALT_A/B | IL   | This pin is latched upon power-on reset to define the ALT_A/B Type 1: ALT_A (Default) 0: ALT_B                                                                                                                                                                                                                                    |  |  |

| 3          | PortN0  | ı    | Port0 negative feeding voltage input.                                                                                                                                                                                                                                                                                             |  |  |

| 4          | AGND    | Р    | Analog ground                                                                                                                                                                                                                                                                                                                     |  |  |

| 5          | PortN1  | ı    | Port1 negative feeding voltage input.                                                                                                                                                                                                                                                                                             |  |  |

| 6          | AGND    | Р    | Analog ground                                                                                                                                                                                                                                                                                                                     |  |  |

| 7          | NC      | NC   | No connection.                                                                                                                                                                                                                                                                                                                    |  |  |

| 8          | PortN2  |      | Port2 negative feeding voltage input.                                                                                                                                                                                                                                                                                             |  |  |

| 9          | AGND    | Р    | Analog ground                                                                                                                                                                                                                                                                                                                     |  |  |

| 10         | PortN3  |      | Port0 negative feeding voltage input.                                                                                                                                                                                                                                                                                             |  |  |

| 11         | AGND    | Р    | Analog ground                                                                                                                                                                                                                                                                                                                     |  |  |

| 12         | AGND    | Р    | Analog ground                                                                                                                                                                                                                                                                                                                     |  |  |

| 13         | SCAN0   | ļ    | Operation mode, please refer to section 5.2 table 2 for more detail information.                                                                                                                                                                                                                                                  |  |  |

| 14         | SCAN1   | ı    | Operation mode, please refer to section 5.2 table 2 for more detail information. It should be connected to AGND for normal operation.                                                                                                                                                                                             |  |  |

| 15         | Vrext   | 0    | Connecting to RGND through a $62K\Omega\pm1\%$ resistor, it is for internal bias only.                                                                                                                                                                                                                                            |  |  |

| 16         | RGND    | Р    | Low noise analog reference ground, it should be connected to AGND.                                                                                                                                                                                                                                                                |  |  |

| 17         | V54     | Р    | Main power supply input for chip The 1uF capacitor should be added between V54 and AGND.                                                                                                                                                                                                                                          |  |  |

| 18         | AGND    | Р    | Analog ground                                                                                                                                                                                                                                                                                                                     |  |  |

| 19         | V5      | Р    | Internal 5V generation for internal use only.<br>A 4.7uF capacitor should be added between V5 and AGND.                                                                                                                                                                                                                           |  |  |

| 20         | V3P3    | Р    | When EnB_Reg is connected to AGND, the built-in 3.3v regulator is active, and besides IP808AR itself, V3P3 can provide 3.3v (6mA) for external device.  When EnB_Reg is connected to 3.3v, V3P3 should be connected to an external power 3.3V (6mA minimum) for IP808AR. A 4.7uF capacitor should be added between V3P3 and AGND. |  |  |

| 21         | V1P8    | Р    | Internal 1.8V for internal use only<br>Adding an 1uF capacitor between V1P8 and AGND                                                                                                                                                                                                                                              |  |  |

| 22         | VPP     | Р    | Connecting to V5 for EFuse power                                                                                                                                                                                                                                                                                                  |  |  |

# (Continued)

| Pin |             | _    |                                                                                                                      |

|-----|-------------|------|----------------------------------------------------------------------------------------------------------------------|

| no. | Label       | Type | Description                                                                                                          |

| 23  | In_Top      | Р    | It should be connected to AGND for normal operation.                                                                 |

| 24  | EnB_Reg     | I    | Enable/Disable the internal 3.3V regulator Please refer to pin description of V3P3.                                  |

| 25  | AGND        | Р    | Analog ground                                                                                                        |

| 26  | AGND        | Р    | Analog ground                                                                                                        |

| 27  | PortN4      |      | Port4 negative feeding voltage input.                                                                                |

| 28  | AGND        | Р    | Analog ground                                                                                                        |

| 29  | PortN5      | ı    | Port5 negative feeding voltage input.                                                                                |

| 30  | NC          | NC   | No connection                                                                                                        |

| 31  | AGND        | Р    | Analog ground                                                                                                        |

| 32  | PortN6      | ı    | Port6 negative feeding voltage input.                                                                                |

| 33  | AGND        | Р    | Analog ground                                                                                                        |

| 34  | PortN7      | ı    | Port7 negative feeding voltage input.                                                                                |

| 35  | NC          | NC   | No connection                                                                                                        |

| 36  | AGND        | Р    | Analog ground                                                                                                        |

| 37  | LED_CLK     | OD   | Serial LED clock output, please refer to section 5.9 LED interface.                                                  |

| 38  | LED_DAT     | OD   | Serial LED data output, direct to Overload LED                                                                       |

| 39  | SCL/EE_CLK  | I/OD | In manual mode, this pin is I <sup>2</sup> C clock input. In auto mode, this pin is clock out to EEPROM.             |

| 40  | SDAO        | OD   | I <sup>2</sup> C serial data output                                                                                  |

| 41  | SDAI/EE_DAT | I/OD | In manual mode, this pin is I <sup>2</sup> C serial data input.<br>In auto mode, this pin is data input from EEPROM. |

| 42  | INTB        | OD   | Interrupt output and low active                                                                                      |

| 43  | DGND        | Р    | Digital ground, it should be connected to AGND.                                                                      |

| 44  | DV3P3       | Р    | Digital power 3.3V A 4.7uF capacitor should be added between DV3P3 and DGND and DV3P3 should be connected to V3P3.   |

| 45  | RstN        | ı    | It is a low active signal to reset IP808AR.                                                                          |

| 46  | AD2         | IL   | I <sup>2</sup> C device address bus AD2                                                                              |

| 47  | AD1         | IL   | I <sup>2</sup> C device address bus AD1                                                                              |

| 48  | AD0         | IL   | I <sup>2</sup> C device address bus AD0                                                                              |

## 5 Functional Description

### 5.1 System Reset

System reset occurs in either of the following conditions:

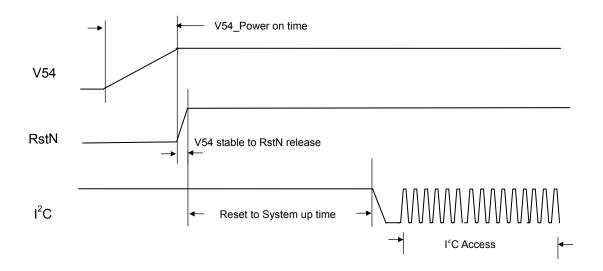

1. Reset triggered by the built-in power-on-reset circuit

IP808AR generates an internal power on reset signal when V54 is power on. It didn't leave reset state until V54 reaching V54\_UVL. After reset, IP808AR still keeps on monitoring voltage level of V3P3, DV3P3, and V54. If the voltage level of V54 (V3P3) is below V54\_UVL(V3P3\_UVL),or over V54\_OVL (V3P3\_OVL), IP808AR enters reset state. Please refer to section 7.3 for detail specification of V54\_UVL, and V3P3\_UVL. It is note that there are two values for one parameter because of hysteresis.

- 2. Reset triggered by the reset pin (RstN)

- 3. Reset triggered by the Software

### System Control Register @ 0x02 of Page 1

| Bit # | R/W | Default | Description                                                                                                                                                                         |

|-------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1   | R   | 0       | Reserved.                                                                                                                                                                           |

| 0     | R/W | 0       | Software Reset. Writing 1 to this bit initiates a system reset. After system reset, this bit is automatically cleared. Writing 0 has no effects. Reading this bit always returns 0. |

#### 5.2 Operation Modes & System Configuration

IP808AR operates in four possible modes, namely the **Auto Mode**, **Manual Mode**, **Diagnostic Mode**, and **Scan Mode**. The mode in which the chip operates in is determined by the two pins **SCAN<1:0>** at system reset.

➤ **Auto Mode** means the chip is operating in a stand alone fashion, i.e. without the need for software intervention. The state machine does the detection, classification, power configuration, and system event monitoring automatically. The system events and status will be recorded in the corresponding registers, however, no interrupt will be generated and I<sup>2</sup>C bus in this mode could be used.

If there is an EEPROM, the contents of the EEPROM are loaded into the register file as initial values. Please refer to the section 5.4 for the description of the syntax of the contents of the EEPROM.

- ➤ Manual Mode means the chip will not be working, that is all ports are disabled, until the software has (1) enabled the port by writing 0x01 to the Port Power Control Register, the state machine start doing the detection, classification, power configuration, and system event monitoring as does in auto mode. The interrupt output pin will be active if the interrupt masks are turned off by software and predefined events occur. The ports can be disabled (power turned off and no further detection activity) by writing 0x00 to the Port Power Control Register. If the operation mode is either in manual mode or diagnostic mode, the host CPU can read register 0 (I²C LSB Device Address Register) to make sure that IP808AR has done the system start up procedure.

- ➤ Diagnostic Mode, as its name suggests, is not for normal operation. It is used in field diagnosis and mass production test. In this mode, the state machine will be working in a step-by-step fashion, in which the state machine will stop at each detection, classification, and power configuration step and can be controlled by software to advance to the next step. The port current, voltage, or temperature measured by the ADC can be read in each step. Another use of diagnostic mode is to program the E-Fuse during mass production.

- > Scan Mode is also not for normal operation. It is used to execute the scan test through the scan in, scan out, and scan enable pins. The state machine will not be working in this mode.

| Mode        | A      | Auto Mod | le      | Manual Mode |       |         | Diagnostic | Scan |

|-------------|--------|----------|---------|-------------|-------|---------|------------|------|

|             | LED    | LED      | LED     | LED         | LED   | LED     | Mode       | Mode |

| Pin setting | Master | Slave    | Disable | Master      | Slave | Disable |            |      |

| SCAN0       | 0      | 0        | 0       | 1           | 1     | 1       | 0          | 1    |

| SCAN1       | 0      | 0        | 0       | 0           | 0     | 0       | 1          | 1    |

| AD2         | 1      | 0        | Χ       | 1           | 0     | Х       | Х          | Χ    |

| LED_CLK     | 1      | 1        | 0       | 1           | 1     | 0       | 0          | Х    |

| LED DAT     | 1      | 1        | 0       | 1           | 1     | 0       | Х          | Χ    |

Please refer to Section 5.10 for LED mode setting.

Table 2 Mode Setting

A summary of available functions in different modes

| Function                                         | Auto<br>mode | Manual<br>mode | Diagnostic mode | Reference    |

|--------------------------------------------------|--------------|----------------|-----------------|--------------|

| Auto start detection, classfiction, and power up | V            | 1              | -               | Section 5.2  |

| Program to detection, classfiction, and power up | ı            | <b>&gt;</b>    | -               | Section 5.2  |

| Stepbystepdetection classfiction, and power up   | -            | -              | V               | Section 5.2  |

| Access register through I <sup>2</sup> C         | 1            | V              | V               | Section 5.3  |

| Load EEPROM                                      | <b>&gt;</b>  |                |                 | Section 5.4  |

| LED master & slave                               | V            | V              | -               | Section 5.10 |

Table 3 Available functions in Operation modes

# > System Configuration Register @ 0x01 of Page 1

| Bit # | R/W | Default        | Description                                                                                                                                                                                                                                        |

|-------|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6   | R   | Pin<br>Setting | Operation Modes. At system reset, these bits latch the input pins SCAN<1:0> to determine the operation mode.  00b: Auto Mode.  01b: Manual Mode.  10b: Diagnostic Mode.  11b: Scan Mode.                                                           |

| 5     | R   | 0              | Reserved.                                                                                                                                                                                                                                          |

| 4     | R/W | Pin<br>Setting | Alternative Indicator.  At system reset, IP808AR latches the input pins ALT_A_B to determine the wiring alternative. However, this bit can also be set by software in manual mode or by EEPROM in auto mode.  0: Alternative A.  1: Alternative B. |

| 3:2   | R   | 0              | Reserved.                                                                                                                                                                                                                                          |

| 1     | R/W | 0              | Suspend Power Up. When set to 1 and the operation mode is manual mode, the state machine will be suspended before entering the power up state (thus the port will not be powered up) until the Start Power Up bit is set to be 1.                  |

| 0     | R/W | 0              | Enable $I^2C$ Checksum.<br>Enable $I^2C$ checksum mechanism. Please refer to the $I^2C$ slave interface.<br>0 = disable, 1 = enable.                                                                                                               |

## Hardware Revision Registers @ 0x03~0x04 of Page 1

| Bit # | R/W | Default | Description            |

|-------|-----|---------|------------------------|

| 7:0   | R   | 08x0    | Hardware Revision MSB. |

| Bit # | R/W | Default | Description            |

|-------|-----|---------|------------------------|

| 7:0   | R   | A8x0    | Hardware Revision LSB. |

## Watchdog Timer Register @ 0x05 of Page 1

| Bit # | R/W | Default | Description                                                        |

|-------|-----|---------|--------------------------------------------------------------------|

| 7     | R/W | 0       | Watchdog Timer Enable.                                             |

|       |     |         | 0 = enable watchdog timer.                                         |

|       |     |         | 1 = disable watchdog timer.                                        |

| 6:0   | R/W | 0x7F    | Watchdog Timer.                                                    |

|       |     |         | When enabled, the watchdog timer starts counting down every        |

|       |     |         | 100mS, when the watchdog timer reaches 0, a watchdog reset will be |

|       |     |         | generated to reset the whole chip.                                 |

# Scratch Register @ 0x06 of Page 1

| Bit # | R/W | Default | Description                                                                                         |

|-------|-----|---------|-----------------------------------------------------------------------------------------------------|

| 7     | R/W | 0       | Scratch Register.                                                                                   |

|       |     |         | A scratch pad that can be written any value. The value will be reset to 0 when system reset occurs. |

## Alternative A/B Register @ 0x07 of Page 1

| Bit # | R/W | Default        | Description                                                                                                                                                                                                                |

|-------|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | R/W | Pin<br>Setting | Alternative A/B. At system reset, IP808AR latches the input pins ALT_A_B to determine the wiring alternative. However, these bits can also be set by software in manual mode or by EEPROM in auto mode.  0: Alternative A. |

|       |     |                | 1: Alternative B.  Bit 0 corresponds to port 0, bit 1 corresponds to port 1, and so on.                                                                                                                                    |

## AF/AT Mode Register @ 0x25 of Page 0

| Bit # | R/W | Default | Description                                                                                                                                                          |

|-------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | R/W | 0xFF    | AF/AT Mode. The 8 bits represent the AF/AT mode of the 8 ports, where bit 0 corresponds to port 0, and bit 1 corresponds to port 1, etc.  0 = AF mode.  1 = AT mode. |

#### 5.3 I<sup>2</sup>C Slave Interface

Through the I<sup>2</sup>C slave interface of IP808AR, host CPU can access the register file in IP808AR. It consists of SCL, SDAO and SDAI pins, where SCL is Clock, SDAO is Serial Data Output and SDAI is Serial Data Input. It should be note that SDAO and SDAI could be connected to implement a bidirectional data pin. This I<sup>2</sup>C interface supports the 7-bit addressing mode of the I<sup>2</sup>C standard. The clock speed can be up to 1M bit/sec.

There can be up to eight IP808AR chips on one I<sup>2</sup>C bus, the LSB 3 bits of the I<sup>2</sup>C address can be assigned with the address pin AD2~AD0. The MSB 4 bits of the I<sup>2</sup>C address are fixed at **1110b**.

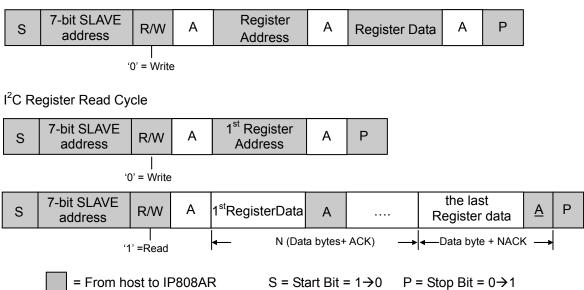

The following diagram is the register read/write cycles of the I<sup>2</sup>C bus.

= From IP808AR to host

Figure 4 I<sup>2</sup>C bus read/write cycles diagram

A = ACK Bit=0

A = NACK Bit=1

Following the 7-bit slave address and read/write bit, the 1<sup>st</sup> data byte received by IP808AR is always interpreted as the register address to be accessed, thus named the address byte.

In a write cycle, following the address byte, there is only one byte, which contains the register data to be written. IP808AR replies an ACK to the host whenever it receives a data byte. After writing this byte, the host should terminate the write cycle by sending a STOP bit.

In a read cycle, the host writes only one byte, which contains the initial address of registers to be read, to the IP808AR firstly. Then the host needs to start another I<sup>2</sup>C cycle with its read/write bit set to 1. IP808AR will continue to send out the next data and increase the address by one automatically whenever the host acknowledges a data byte with an ACK, If the calculated register address is valid (within valid address range). The host can terminates a read cycle by sending a NACK following by a STOP bit. If the address of the data to be sent back falls out of valid register address range, IP808AR always returns 00h.

### I<sup>2</sup>C Device Address Register @ 0x00 of Both Pages

| Bit # | R/W | Default | Description                                                                                                                                                           |

|-------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | R   | 0       | Reserved.                                                                                                                                                             |

| 6     | R/W | 0       | Register Page.  This bit specifies the page number of the register to be accessed through the I <sup>2</sup> C interface.  0: page 0 1: page 1                        |

| 5:3   | R   | 0       | Reserved.                                                                                                                                                             |

| 2:0   | R   | 000b    | I <sup>2</sup> C Device LSB Address. Unique device address to identify this chip on the I <sup>2</sup> C bus. This address is latched in from the input pins AD2~AD0. |

The highest I<sup>2</sup>C clock speed supported is 1MHz. However, in order to prevent abnormal activity on the I<sup>2</sup>C bus from hanging IP808AR, the I<sup>2</sup>C interface implements a time out mechanism. Host CPU can stop the I<sup>2</sup>C clock when it's low and resume the clock within 10ms. If the clock does not resume within 10ms, the I<sup>2</sup>C interface will abort the current I<sup>2</sup>C cycle and wait for the next START condition.

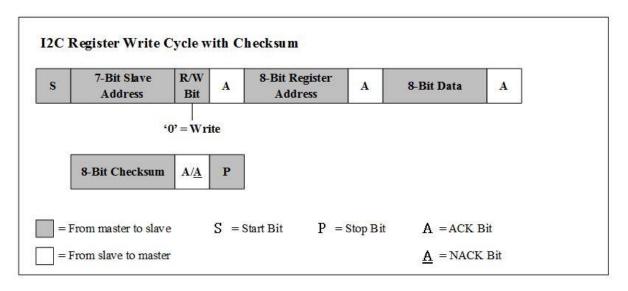

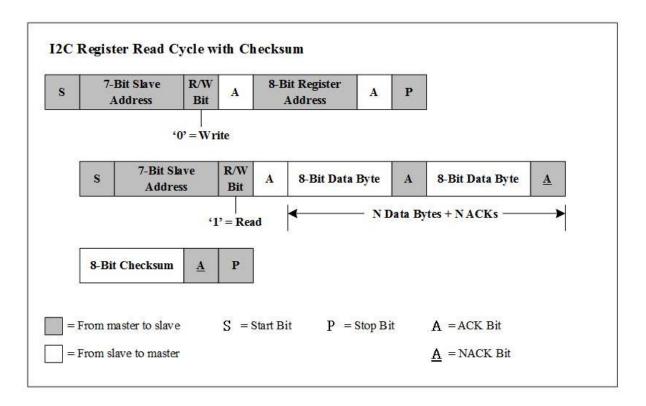

To improve reliability, the  $I^2C$  slave can optionally support checksum mechanism. The  $I^2C$  checksum mechanism is enabled using the **System Configuration Register**. When the checksum mechanism is enabled, checksums will be added to the  $I^2C$  read/write cycles. When checksum fails in write cycle, access to the register is ignored. When checksum fails in read cycle, the data read by the  $I^2C$  master should be considered corrupted. The following diagrams are the register read/write cycles of the  $I^2C$  interface with checksum enabled

The 8-bit checksum for I2C write cycle is calculated as the following:

0xFF - (7-bit slave address and R/W bit + 8-bit register address + 8-bit data + carry out bits) = 8-bit checksum.

In write cycle, the IP808AR will verify the checksum bits and if the checksum fails, the data will not be written into the register and a NACK bit is sent back to the host. If the checksum succeeds, the register will be written and an ACK bit is sent back to the host.

The 8-bit checksum for I2C read cycle is calculated as the following:

### 0xFF - (7-bit slave address and R/W bit + 8-bit data + carry out bits) = 8-bit checksum.

When the desired data byte is read by the host, the host can send a NACK bit to IP808AR; in return, IP808AR will send out an 8-bit checksum. The host should again send a NACK bit to IP808AR and then the STOP bit. The checksum then can be used by the host to verify if the read data byte is corrupted.

#### 5.4 EEPROM controller

When IP808AR operates in auto mode, the register file can be loaded with some initial value from external EEPROM (24xx series EEPROM, Maximum support to 24C16). IP808AR reads the EEPROM starting from address 0, parses the contents of the EEPROM command blocks, checks for integrity of the contents, and then writes the designated registers. This process continues until there is either no more data or the integrity check fails. EEPROM is necessary only if user wants to modify the default value of registers in auto mode.

The format of the EEPROM follows:

| BYTE  | Bit 7                     | Bit 6       | Bit 5 | Bit 4           | Bit 3      | Bit 2 | Bit 1 | Bit 0 |  |  |

|-------|---------------------------|-------------|-------|-----------------|------------|-------|-------|-------|--|--|

| 0     | Devid                     | ce ID (AD2~ | AD0)  | # of Data Bytes |            |       | X     |       |  |  |

| 1     | Starting Register Address |             |       |                 |            |       |       |       |  |  |

| 2     | Data Byte 1               |             |       |                 |            |       |       |       |  |  |

| 3     | Data Byte 2               |             |       |                 |            |       |       |       |  |  |

|       |                           |             |       |                 |            |       |       |       |  |  |

| 1 + N | Data Byte N               |             |       |                 |            |       |       |       |  |  |

| 2 + N | Checksum Byte             |             |       |                 |            |       |       |       |  |  |

| 3 + N |                           |             |       | Next comr       | nand block |       |       |       |  |  |

Figure 5 EEPROM Format

#### Where:

- ➤ **Device ID**: (AD2~AD0)=100b = Master, 000b = Slave0, 001b = Slave1, 010b = Slave2, 011b = Slave3, other values of Device ID are invalid and the EEPROM loading process will be stopped. On normal mode IP808AR doesn't check this field

- > # Of Data Bytes: the number of data bytes in this command block. 0 = 1 byte, 1 = 2 bytes, etc.

- > Starting Register Address: the starting register address to be loaded by the following data bytes.

- Data Bytes: the data bytes to be loaded in to specified registers.

- ➤ Checksum Byte: the checksum byte is the checksum of all previous bytes in the command block. The checksum is calculated by adding all the previous bytes with the carry bit (if any) adding back to the sum. If the checksum fails, the system start up procedure fails and the system halt.

#### 5.5 PSE State Machine

IP808AR has eight ports and each port is mainly controlled by a state machine to perform the detection, classification, and powering up procedures. As the eight state machines run in parallel, they contend for ADC 1 in the detection and classification procedures. Thus an arbiter is needed to grant the access rights among the eight state machines.

Furthermore, to limit the chip inrush current, a maximum of two ports are allowed to start their classification procedures simultaneously. And only one port is allowed to turn on power at a time. After successful detection, classification, and power configuration, the port power is turned on.

The state machine is also designed to respond to abnormal power events, such as overload, short circuit, and overheat (thermal shutdown); basically port power will be turned off when such event happens. It takes time to cool off the device after power is turned off, so the state machine will delay a certain amount of time before starting next detection procedure for the port. The above mentioned programmable amount of time is set in the **Error Delay Register**.

### Port 0~7 Power Control Registers @ 0x98~0x9F of Page 1

| Bit # | R/W  | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | R/W  | 0       | Enable Power Up Suspended Interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |      |         | When the state machine is suspended before entering the power up state and                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |      |         | this bit is 1, an interrupt will be issued.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6:2   | R    | 0x0     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |      |         | PSE Enable.  00b = PSE port disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1:0   | R/W  | 0x0     | The port is disabled, port power is turned off, and the PSE state machine returns to the IDLE state.  101b = PSE port enabled.  The port is enabled, and the PSE state machine starts the detection process if the port is not in error condition and the Start State Machine bit in the State Machine Control Register is set to be 1.                                                                                                                                                                    |

| 1.0   | R/VV | UXU     | <ul> <li>10b = PSE port force power on. The port is forced to turn power on without going through the normal detection, classification, and power configuration processes. This is used for testing purpose, not for normal operation.</li> <li>11b = PSE port enabled (skip detection process). The port is enabled, and the PSE state machine skips the detection process and starts the classification process directly. This is only used for testing purpose and not for normal operation.</li> </ul> |

#### Port 0~7 State Machine Control Registers @ 0x90~0x97 of Page 1

| Bit # | R/W | Default | Description                                                                                                                                                                                                                                                                                                                                             |

|-------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | R   | 0       | Power Up Suspended.                                                                                                                                                                                                                                                                                                                                     |

|       |     |         | When in manual mode and when the <b>Suspend Power Up</b> bit is set, the state machine will be suspended before entering the power up state. At which time, this bit will be set to 1 by hardware.                                                                                                                                                      |

|       |     |         | When the state machine is re-started by setting the <b>Start Power Up</b> bit, this bit will be cleared automatically by hardware.                                                                                                                                                                                                                      |

| 6     | R/W |         | Step State Machine. When in diagnostic mode, writing 1 to this bit will advance the state machine to the next state, after which this bit will be cleared by hardware. Writing 0 has no effect.  Note that not every state can be stepped; Basically, only those states directly related to the detection and classification procedures can be stepped. |

| Bit # | R/W | Default | Description                                                                  |

|-------|-----|---------|------------------------------------------------------------------------------|

| 5     | R/W | 0       | Start Power Up.                                                              |

|       |     |         | When in manual mode and when the Suspend Power Up bit is set, the state      |

|       |     |         | machine will be suspended before entering the power up state. Writing a 1 to |

|       |     |         | this bit will re-start the state machine to enter the power up state. After  |

|       |     |         | entering the power up state, this bit will be cleared by hardware.           |

| 4:0   | R   | 0       | Current State of the State Machine.                                          |

|       |     |         | Current state of the state machine.                                          |

|       |     |         | 0 = DISABLED                                                                 |

|       |     |         | 1 = TEST_MODE                                                                |

|       |     |         | 2 = TEST_ERROR                                                               |

|       |     |         | 3 = IDLE                                                                     |

|       |     |         | 4 = START_DETECTION                                                          |

|       |     |         | 5 = DETECT_EVAL                                                              |

|       |     |         | 6 = SINATURE_INVALID                                                         |

|       |     |         | 7 = BACKOFF                                                                  |

|       |     |         | 8 = START_CLASSIFICATION (AF Mode)                                           |

|       |     |         | 1-EVENT_CLASS (AT Mode)                                                      |

|       |     |         | 9 = CLASS_EV1 (AT Mode)                                                      |

|       |     |         | 10 = MARK_EV1 (AT Mode)                                                      |

|       |     |         | 11 = CLASS_EV2 (AT Mode)                                                     |

|       |     |         | 12 = MARK_EV2 (AT Mode)                                                      |

|       |     |         | 13 = CLASSIFICATION_EVAL                                                     |

|       |     |         | 14 = POWER_DENIED                                                            |

|       |     |         | 15 = POWER_UP                                                                |

|       |     |         | 16 = POWER_ON                                                                |

|       |     |         | 19 = ERROR_DELAY                                                             |

|       |     |         | 20 = PWRUP_SUSPENDED                                                         |

# ➤ Port 0~7 Detected Signature Registers @ 0x68~0x6F of Page 0

| Bit # | R/W | Default | Description                                                              |

|-------|-----|---------|--------------------------------------------------------------------------|

| 7:3   | R   | 0x0     | Reserved.                                                                |

| 1:0   | R   | 0       | Detected Signature.  00b = R <sub>BAD</sub> .  01b = R <sub>GOOD</sub> . |

# ➤ Port 0~7 Invalid Signature Event Registers @ 0xDC of Page 1

| Bit # | R/W   | Default | Description                                                                                                                                                                             |

|-------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | R/W0C | 0       | Invalid Signature Event In manual or diagnostic mode, write 0 to clear the bit. Writing 1 to this bit has no effect. Bit 0 corresponds to port 0, and bit 1 corresponds to port 1, etc. |

# ➤ Port 0~3 Classification Event Number Registers @ 0xA0 of Page 1

| Bit # | R/W | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6   | R/W | 2       | Number of Classification Events for Port 3.  Valid value range is from 0 to 2. The value 3 will be regarded as 2. If the value is 0, no classification is executed, and the PD is always deemed class 0 device.  This register can be written to by host CPU. However, according to IEEE802.3 standard, if the port is in AF mode, only one classification event is executed, and in AT mode, there will be two classification events. So, this register will be automatically updated when the AF/AT Mode Register is updated. |

| Bit # | R/W | Default | Description                                 |

|-------|-----|---------|---------------------------------------------|

| 5:4   | R/W | 2       | Number of Classification Events for Port 2. |

| 3:2   | R/W | 2       | Number of Classification Events for Port 1. |

| 1:0   | R/W | 2       | Number of Classification Events for Port 0. |

## Port 4~7 Classification Event Number Registers @ 0xA1 of Page 1

| Bit # | R/W | Default | Description                                 |

|-------|-----|---------|---------------------------------------------|

| 7:6   | R/W | 2       | Number of Classification Events for Port 7. |

| 5:4   | R/W | 2       | Number of Classification Events for Port 6. |

| 3:2   | R/W | 2       | Number of Classification Events for Port 5. |

| 1:0   | R/W | 2       | Number of Classification Events for Port 4. |

### PSE Skip Event 2 Register @ 0xA2 of Page 1

| Bit #   R/W   Default   Description                                                                                                                                             |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:0 R/W 0xFF Skip the Second Classification Event. Bit 0 corresponds to port 0, bit 1 corresponds to port 1, etc 0 = do not skip event 2 in AT mode 1 = skip event 2 in AT mode |  |

## ➤ Port 0~1 Detected PD Class Registers @ 0x88 of Page 0

| Bit # | R/W | Default | Description                  |

|-------|-----|---------|------------------------------|

| 7     | R   | 0       | Reserved.                    |

|       |     |         | Detected PD Class of Port 1. |

|       |     |         | 0 = Class 0                  |

|       |     |         | 1 = Class 1                  |

| 6:4   | R   | 5       | 2 = Class 2                  |

|       |     |         | 3 = Class 3                  |

|       |     |         | 4 = Class 4                  |

|       |     |         | 5 = Unknown                  |

| 3     | R   | 0       | Reserved.                    |

| 2:0   | R   | 5       | Detected PD Class of Port 0. |

## > Port 2~3 Detected PD Class Registers @ 0x89 of Page 0

| Bit # | R/W | Default | Description                  |

|-------|-----|---------|------------------------------|

| 7     | R   | 0       | Reserved.                    |

| 6:4   | R   | 5       | Detected PD Class of Port 3. |

| 3     | R   | 0       | Reserved.                    |

| 2:0   | R   | 5       | Detected PD Class of Port 2. |

# ➤ Port 4~5 Detected PD Class Registers @ 0x8A of Page 0

| Bit # | R/W | Default | Description                  |

|-------|-----|---------|------------------------------|

| 7     | R   | 0       | Reserved.                    |

| 6:4   | R   | 5       | Detected PD Class of Port 5. |

| 3     | R   | 0       | Reserved.                    |

| 2:0   | R   | 5       | Detected PD Class of Port 4. |

## ➤ Port 6~7 Detected PD Class Registers @ 0x8B of Page 0

| Bit # | R/W | Default | Description                  |

|-------|-----|---------|------------------------------|

| 7     | R   | 0       | Reserved.                    |

| 6:4   | R   | 5       | Detected PD Class of Port 7. |

| 3     | R   | 0       | Reserved.                    |

| 2:0   | R   | 5       | Detected PD Class of Port 6. |

# ➤ Port I<sub>CLASS</sub> Registers @ 0x78~0x87 of Page 0

| Bit # | R/W | Default | Description                                                                                                                                       |

|-------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6   | R   | 0       | Reserved.                                                                                                                                         |

| 5:0   | R   | 5       | Port I <sub>CLASS</sub> MSB. The current detected in classification. The MSB 10 bits are integer and the LSB 4 bits are fractional. Unit is in mA |

| Bit # | R/W | Default | Description                                                                                                                                       |

| 7:0   | R   | 0x00    | Port I <sub>CLASS</sub> LSB.                                                                                                                      |

# > Error Delay Register @ 0xE4 Page 0

| Bit# | R/W | Default | Description                                                        |

|------|-----|---------|--------------------------------------------------------------------|

| 7:0  | R/W | 0x10    | Error Delay.                                                       |

|      |     |         | The programmable error delay in units of 0.1S. Minimum value is 9. |

#### 5.6 Power Manager

Power manager is responsible for two tasks: **power configuration** and **power monitoring**. Power configuration is the task to allocate power to the ports requesting for power. Power monitoring is the task to monitor power conditions (current, voltage, and temperature). When invalid conditions occur, proper actions will be taken to prevent hazardous consequences.

#### 5.6.1 Power Trunks

Before doing power configuration, the total available power must be determined first. IP808AR supports two trunks of power, where each power trunk has its own set of parameters to facilitate the calculation of total available power.

> Trunk Power Limit is the maximum power supply capacity allocated to the power trunk.

### > Trunk 0 Power Limit Register @ 0x40~0x41 of Page 1

| Bit # | R/W | Default | Description                                                                                                       |

|-------|-----|---------|-------------------------------------------------------------------------------------------------------------------|

| 7:3   | R   | 0       | Reserved.                                                                                                         |

| 2:0   | R/W | 1       | Trunk 0 Power Limit (MSB).                                                                                        |

| Bit # | R/W | Default | Description                                                                                                       |

| 7:0   | R/W |         | Trunk 0 Power Limit (LSB). Trunk Power Limit specifies the upper limit of the power supply. Default is 300 Watts. |

#### > Trunk 1 Power Limit Register @ 0x42~0x43 of Page 1

| Bit | t # | R/W | Default | Description                                           |

|-----|-----|-----|---------|-------------------------------------------------------|

| 7:  | :3  | R   | 0       | Reserved. 0x42                                        |

| 2:  | :0  | R/W | 1       | Trunk 1 Power Limit (MSB). 0x42                       |

| 7:  | :0  | R/W | 11771.  | Trunk 1 Power Limit (LSB). 0x43 Default is 300 Watts. |

### > Trunk Select Register @ 0x69 of Page 1

| Bit # | R/W | Default | Description                                                                                                                                                                                                                                                                           |

|-------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3   | R   | 0       | Reserved.                                                                                                                                                                                                                                                                             |

| 1:0   | R/W | 0       | <b>Trunk Select</b> . Writing to this register will switch power trunk. Note that whenever the parameters of the power trunk currently in use are updated, this Trunk Select Register must also be written to make the newly updated parameters in effect.  0 = Trunk 0, 1 = Trunk 1. |

#### 5.6.2 Power Configuration

Power manager is responsible to allocate powers to the ports that pass the detection and classification process. To do so, several parameters must be specified or be calculated in advance:

- 1) Maximun Trunk Power (specified in register 0x40~0x43, page1).

- 2) Power configuration Mode (specified in register 0x10, page1).

- Power configuration Mode specifies the way to determine the requested port power of the power device (RPP of Power configuration Mode Register) in the power configuration process.

- > Requested Port Power is determined in the power configuration process according to RPP of power configuration mode.

## ➤ Power configuration Mode Register @ 0x10 of Page 1

| Bit # | R/W | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5   | R/W | 0       | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4:3   | R/W | 1       | Requested port power (RPP) specifies ways to determine the port power requested by the power device in the power configuration process  0 = Host Defined Power Limit (HDPL) specified in Host Defined Power Limit registers  1 = Class defined power limit (CDPL) specified in Class Defined Power Limit registers.  2 = highest possible power (set by AT/AF flag). In AF mode, the maximum power allowed is 15.5Watts; in AT mode, the maximum power allowed is 30 Watts. |

| 2:0   | R   | 0       | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### > PD Requested Power @ 0x90~0x97 of Page 0

| Bit # | R/W | Default | Description                                                                                                                                                                                                                              |

|-------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |     |         | PD Requested Power.                                                                                                                                                                                                                      |

| 7:0   | R   | 0x00    | The power requested by and allocated to the PD, which is calculated according to the power allocation mode and the class of the PD.  The unit is Watt. The MSB 6 bits are the integer number and the LSB 2 bits are the fraction number. |

### Class 0 Defined Power Limit Registers @ 0x12 of Page 1

| Bit # | R/W | Default | Description                                                                                                                                                                                                                                                               |

|-------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | R/W | 0x3e    | Class 0 Port Power Limit (C0DPL).  The maximum allowable port power for class 0 devices if RPP is set to be 1.  Bit 7~2 specifies the integral part of the power limit, whereas bit 1~0 specifies the fractional part of the power limit value.  Default is 0x3e = 15.5W. |

#### Class 1 Defined Power Limit Registers @ 0x13 of Page 1

| Bit # | R/W | Default | Description                                                                                                                                                                                                                                                                             |

|-------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | R/W | 0x10    | Class 1 Port Power Limit (C1DPL). The maximum allowable port power for class 1 devices if RPP is set to be 1. Bit $7\sim2$ specifies the integral part of the power limit, whereas bit $1\sim0$ specifies the fractional part of the power limit value. Default is $0\times10 = 4.0$ W. |

### Class 2 Defined Power Limit Registers @ 0x14 of Page 1

| Bit # | R/W | Default | Description                                                                 |

|-------|-----|---------|-----------------------------------------------------------------------------|

|       |     |         | Class 2 Port Power Limit (C2DPL).                                           |

| 7:0   | R/W | 0x1c    | The maximum allowable port power for class 2 devices if RPP is set to be 1. |

|       |     |         | Bit 7~2 specifies the integral part of the power limit, whereas bit 1~0     |

| Bit # | R/W | Default | Description                                             |

|-------|-----|---------|---------------------------------------------------------|

|       |     |         | specifies the fractional part of the power limit value. |

|       |     |         | Default is 0x1c = 7.0W.                                 |

## ➤ Class 3 Defined Power Limit Registers @ 0x15 of Page 1

| Bit # | R/W | Default | Description                                                                                                                                                                                                                                                               |

|-------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|