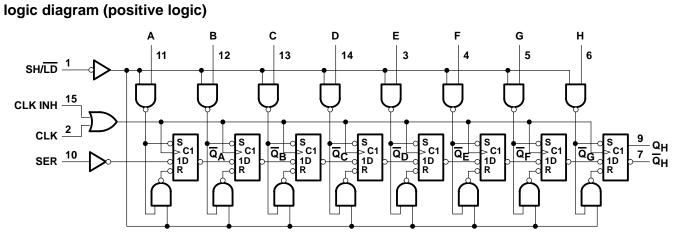

- Complementary Outputs

- Direct Overriding Load (Data) Inputs

- Gated Clock Inputs

- Parallel-to-Serial Data Conversion

| TYPE     | TYPICAL MAXIMUM<br>CLOCK FREQUENCY | TYPICAL<br>POWER DISSIPATION |

|----------|------------------------------------|------------------------------|

| 74I S165 | 35 MHz                             | 90 mW                        |

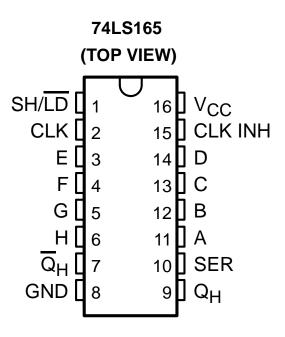

### description

74LS165 are 8-bit serial shift

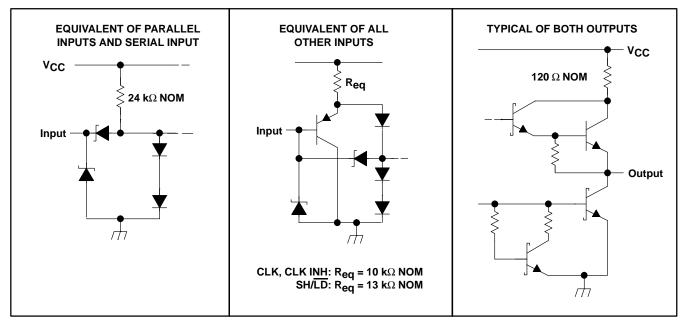

registers that shift the data in the direction of  $Q_A$  toward  $Q_H$  when clocked. Parallel-in access to each stage is made available by eight individual, direct data inputs that are enabled by a low level at the shift/load (SH/LD) input. These registers also feature gated clock (CLK) inputs and complementary outputs from the eighth bit. All inputs are diode-clamped to minimize transmission-line effects, thereby simplifying system design.

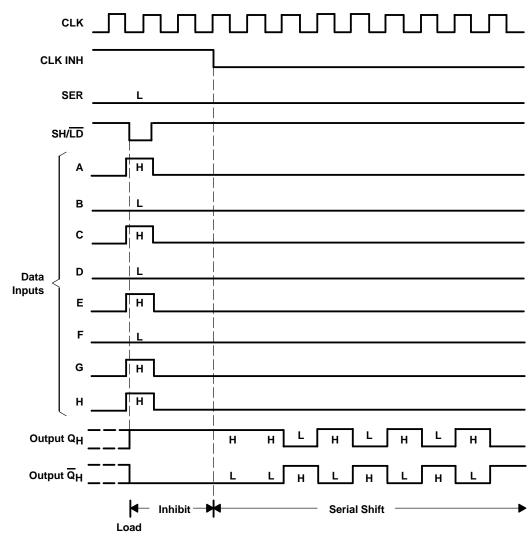

Clocking is accomplished through a two-input positive-NOR gate, permitting one input to be used as a clock-inhibit function. Holding either of the clock inputs high inhibits clocking, and holding either clock input low with SH/LD high enables the other clock input. Clock inhibit (CLK INH) should be changed to the high level only while CLK is high. Parallel loading is inhibited as long as SH/LD is high. Data at the parallel inputs are loaded directly into the register while SH/LD is low, independently of the levels of CLK, CLK INH, or serial (SER) inputs.

| TA          | PAC         | KAGE <sup>†</sup> | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|-------------|-------------|-------------------|--------------------------|---------------------|

|             | DIP         | Tube              | XD74LS165                | XD74LS165           |

| 0°C to 70°C | 000 to 7000 |                   | XL74LS165                | XL74LS165           |

| 0 0 10 70 0 | SOP         | Tape and reel     | XL74LS165                | AL14L0100           |

### **ORDERING INFORMATION**

| INPUTS |                 |            |                |                    |                    | RNAL<br>PUTS    | OUTPUT          |  |  |

|--------|-----------------|------------|----------------|--------------------|--------------------|-----------------|-----------------|--|--|

| SH/LD  | CIKINH CIK SERI |            | PARALLEL<br>AH | $\overline{Q}_{A}$ | $\overline{Q}_{B}$ | QH              |                 |  |  |

| L      | Х               | Х          | Х              | ah                 | а                  | b               | h               |  |  |

| н      | L               | L          | Х              | Х                  | Q <sub>A0</sub>    | $Q_{B0}$        | Q <sub>H0</sub> |  |  |

| н      | L               | $\uparrow$ | Н              | Х                  | н                  | Q <sub>An</sub> | Q <sub>Gn</sub> |  |  |

| н      | L               | $\uparrow$ | L              | Х                  | L                  | Q <sub>An</sub> | Q <sub>Gn</sub> |  |  |

| н      | Н               | Х          | Х              | х                  | Q <sub>A0</sub>    | Q <sub>B0</sub> | Q <sub>H0</sub> |  |  |

#### FUNCTION TABLE

### schematics of inputs and outputs

74LS165

Pin numbers shown are for D, J, N, NS, and W packages.

## typical shift, load, and inhibit sequences

### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

|                                             | 5.5 V                                  |

|---------------------------------------------|----------------------------------------|

|                                             | ackage                                 |

| Np                                          | ackage 67°C/W                          |

| NS                                          | package 64°C/W                         |

| Storage temperature range, T <sub>stg</sub> | —————————————————————————————————————— |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Voltage values, except interemitter voltage, are with respect to network ground terminal.

2. This is the voltage between two emitters of a multiple-emitter transistor. This rating applies for the '165 to the SH/LD input in conjunction with the CLK INH input.

3. The package thermal impedance is calculated in accordance with JESD 51-7.

|                       |                                                             |            | 7    | 74LS165 |      |      |  |

|-----------------------|-------------------------------------------------------------|------------|------|---------|------|------|--|

|                       |                                                             |            | MIN  | NOM     | MAX  | UNIT |  |

| VCC                   | Supply voltage                                              |            | 4.75 | 5       | 5.25 | V    |  |

| VIH                   | High-level input voltage                                    |            | 2    |         |      | V    |  |

| VIL                   | Low-level input voltage                                     |            |      |         | 0.8  | V    |  |

| ЮН                    | High-level output current                                   |            |      |         | -0.4 | mA   |  |

| IOL                   | Low-level output current                                    |            |      |         | 8    | mA   |  |

| fclock                | Clock frequency                                             |            | 0    |         | 25   | MHz  |  |

| <b>.</b>              | Width of clock input pulse Clock high   Clock low Clock low | Clock high | 15   |         |      |      |  |

| <sup>t</sup> w(clock) |                                                             | 25         |      |         | ns   |      |  |

| + <i>a</i>            | Width of load input pulse                                   | Clock high |      |         |      | -    |  |

| <sup>t</sup> w(load)  | Width of load input pulse                                   | Clock low  | 17   |         |      | ns   |  |

| t <sub>su</sub>       | Clock-enable setup time                                     |            | 30   |         |      | ns   |  |

| t <sub>su</sub>       | Parallel input setup time                                   |            | 10   |         |      | ns   |  |

| t <sub>su</sub>       | Serial input setup time                                     |            | 20   |         |      | ns   |  |

| t <sub>su</sub>       | Shift setup time                                            |            | 45   |         |      | ns   |  |

| <sup>t</sup> h        | Hold time at any input                                      |            |      |         |      | ns   |  |

| Т <sub>А</sub>        | Operating free-air temperature                              |            | 0    |         | 70   | °C   |  |

### recommended operating conditions

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                                        | TEST CONDITIONST                       |                                 |                        |                           |                          |      |      |    |

|----------------------------------------|----------------------------------------|---------------------------------|------------------------|---------------------------|--------------------------|------|------|----|

| PARAMETER TEST CONDITIONS <sup>†</sup> |                                        |                                 |                        |                           | MIN TYP <sup>‡</sup> MAX |      | UNIT |    |

| VIK                                    | $V_{CC} = MIN,$                        | lj = -18 mA                     |                        |                           |                          |      | -1.5 | V  |

| VOH                                    | $V_{CC} = MIN,$                        | V <sub>IH</sub> = 2 V,          | $V_{IL} = MAX,$        | I <sub>OH</sub> = -0.4 mA | 2.7                      | 3.5  |      | V  |

| Vei                                    | V <sub>OL</sub> V <sub>CC</sub> = MIN, | $V_{IH} = 2 V$ , $V_{IL} = MAX$ | I <sub>OL</sub> = 4 mA |                           | 0.25                     | 0.4  | V    |    |

| VOL                                    |                                        |                                 |                        | I <sub>OL</sub> = 8 mA    |                          | 0.35 | 0.5  | v  |

| Ц                                      | $V_{CC} = MAX,$                        | $V_{CC} = MAX,  V_I = 7 V$      |                        |                           |                          |      | 0.1  | mA |

| Чн                                     | $V_{CC} = MAX,$                        | Vj = 2.7 V                      |                        |                           |                          |      | 20   | μΑ |

| Ι <sub>ΙL</sub>                        | $V_{CC} = MAX,$                        | VI = 0.4 V                      |                        |                           |                          |      | -0.4 | mA |

| IOS§                                   | V <sub>CC</sub> = MAX                  |                                 |                        | -20                       |                          | -100 | mA   |    |

| ICC                                    | V <sub>CC</sub> = MAX,                 |                                 |                        |                           |                          | 18   | 30   | mA |

NOTE 4. With the outputs open, CLK INH and CLK at 4.5 V, and a clock pulse applied to SH/LD, ICC is measured first with the parallel inputs at 4.5 V, then with the parallel inputs grounded.

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate values specified under recommended operating conditions.

<sup>‡</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C. § Not more than one output should be shorted at a time, and the duration of the short-circuit should not exceed one second.

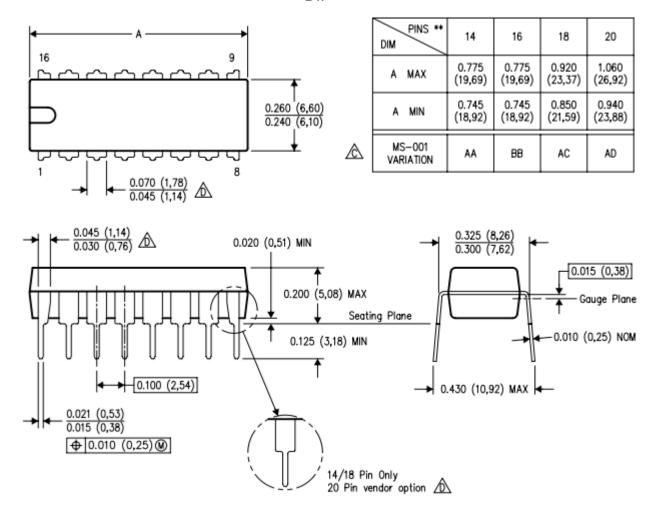

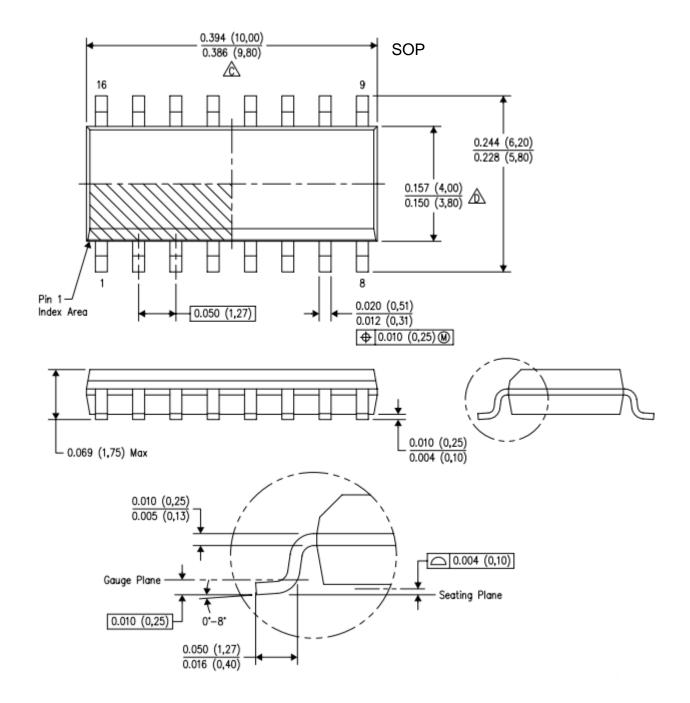

## XD74LS165 DIP-16 XL74LS165 SOP16

| PARAMETER <sup>†</sup> | FROM<br>(INPUT) | TO<br>(OUTPUT)                          | TEST CONDITIONS                           | MIN | ТҮР | MAX | UNIT |

|------------------------|-----------------|-----------------------------------------|-------------------------------------------|-----|-----|-----|------|

| f <sub>max</sub>       |                 |                                         |                                           | 25  | 35  |     | MHz  |

| <sup>t</sup> PLH       | LD              | Any                                     | $P_{1} = 2kO_{1}C_{1} = 15 pE$            |     | 21  | 35  |      |

| <sup>t</sup> PHL       | LD              | Any                                     | $R_L = 2 k\Omega$ , $C_L = 15 pF$         |     | 26  | 35  | ns   |

| <sup>t</sup> PLH       | CLK             | Δον                                     | $R_{1} = 2 k\Omega, C_{1} = 15 pF$        |     | 14  | 25  | ns   |

| <sup>t</sup> PHL       | ULK             | Any                                     | R[ = 2 K22, θ] = 15 βi                    |     | 16  | 25  | 113  |

| <sup>t</sup> PLH       | н               | 0                                       | $R_{L} = 2 k\Omega$ , $C_{L} = 15 pF$     |     | 13  | 25  | ns   |

| <sup>t</sup> PHL       |                 | Q <sub>H</sub>                          | $K_{L} = 2 K_{22}, O_{L} = 15 \text{ pm}$ |     | 24  | 30  | 115  |

| <sup>t</sup> PLH       | н               | $\overline{Q}_{H}$                      |                                           |     | 19  | 30  |      |

| <sup>t</sup> PHL       |                 | \ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ | $R_L = 2 k\Omega$ , $C_L = 15 pF$         |     | 17  | 25  | ns   |

# 74LS165 switching characteristics, $V_{CC}$ = 5 V, $T_A$ = 25°C

† f<sub>max</sub> = maximum clock frequency, tpLH = propagation delay time, low-to-high-level output, tpHL = propagation delay time, high-to-low-level output

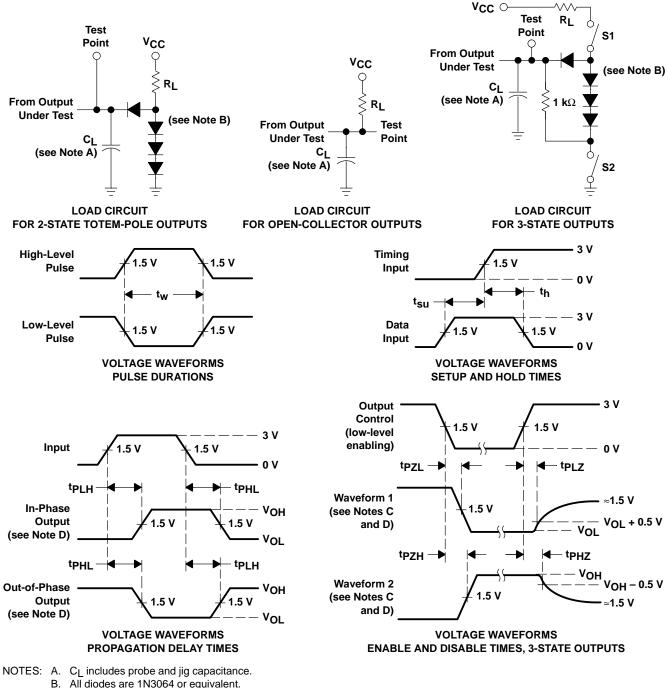

### PARAMETER MEASUREMENT INFORMATION

- - C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. S1 and S2 are closed for tpLH, tpHL, tpHZ, and tpLZ; S1 is open and S2 is closed for tpZH; S1 is closed and S2 is open for tpZL.

- E. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz, Z<sub>O</sub>  $\approx$  50  $\Omega$ ; t<sub>r</sub> and t<sub>f</sub>  $\leq$  7 ns for Series 74LS165 devices and  $t_r$  and  $t_f \le 2.5$  ns for Series 74LS165 devices.

- F. The outputs are measured one at a time with one input transition per measurement.

### Figure 1. Load Circuits and Voltage Waveforms

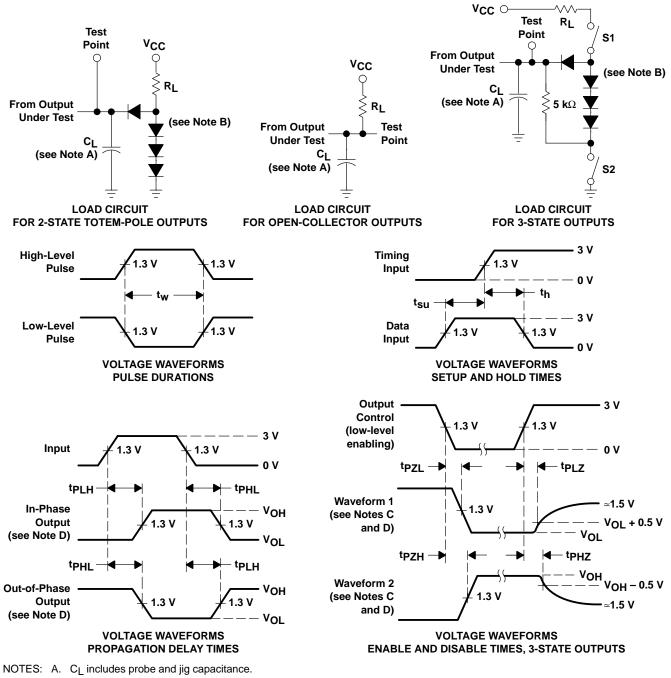

### PARAMETER MEASUREMENT INFORMATION

- B. All diodes are 1N3064 or equivalent.

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control. D. S1 and S2 are closed for tpLH, tpHL, tpHZ, and tpLZ; S1 is open and S2 is closed for tpZH; S1 is closed and S2 is open for tpZL.

- E. Phase relationships between inputs and outputs have been chosen arbitrarily for these examples.

- F. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz, Z<sub>O</sub>  $\approx$  50  $\Omega$ , t<sub>f</sub>  $\leq$  1.5 ns, t<sub>f</sub>  $\leq$  2.6 ns.

- G. The outputs are measured one at a time with one input transition per measurement.

### Figure 2. Load Circuits and Voltage Waveforms

## XD74LS165 DIP-16 XL74LS165 SOP16

DIP