# APW7264

I2C Controlled 3A Single Cell USB Charger with Narrow VDC Power Path Management and USB OTG

### Features

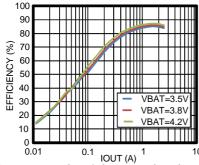

- High Efficiency 3A Switch Mode Charge

Single Input USB-compliant/Adapter Charge

Input Voltage and Current Limit Supports USB 2.0 and USB 3.0

- Input Current Limit: 100mA, 150mA, 500mA, 900mA, 1A, 1.5A, 2A and 3A

- 3.9V 6.2V Input Operating Voltage Range

- Support Adapter with Input Voltage DPM Regulation

- USB OTG with Adjustable Output 4.55V to 5.5V at 1 A or 1.5A

- Accurate +/- 15%

- Hiccup Mode Overcurrent Protection

- Narrow VDC (NVDC) Power Path Management

- Instant-on Works with No Battery or Deeply Discharged Battery

- Ideal Diode Operation in Battery Supplement Mode

- 1.5MHz Switching Frequency for Low Profile Inductor

- Autonomous Battery Charging with or without Host Management

- Battery Charge Enable

- Battery Charge Preconditioning

- Charge Termination and Recharge

- · Accuracy

- +0.5% Charge Voltage Regulation

- +7% Charge Current Regulation

- +7.5% Input Current Regulation

- <u>+</u>3% Output Regulation in Boost Mode

### High Integration

- Power Path Management

- Synchronous Switching MOSFETs

- Integrated Current Sensing

- Internal Loop Compensation

- Safety

- Battery Temperature Sensing for Charging and Discharging in OTG Mode

- Battery Charging Safety Timer

- Thermal Regulation and Thermal Shutdown

- Input System Over-Voltage Protection

- MOSFET Over-Current Protection

- Charge Status Outputs for LED or Host Processor

- Maximum Power Tracking capability by Input Voltage Regulation

- 32mA Low Battery Leakage Current and Support Shipping Mode

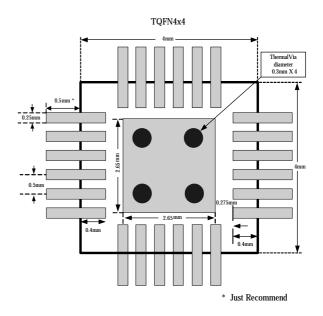

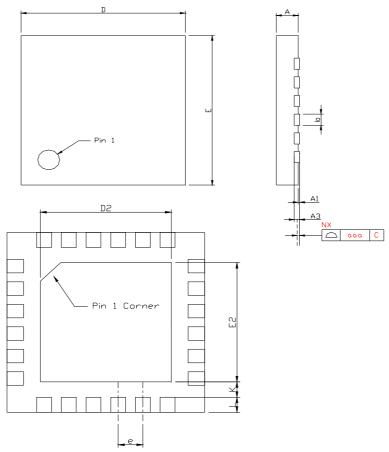

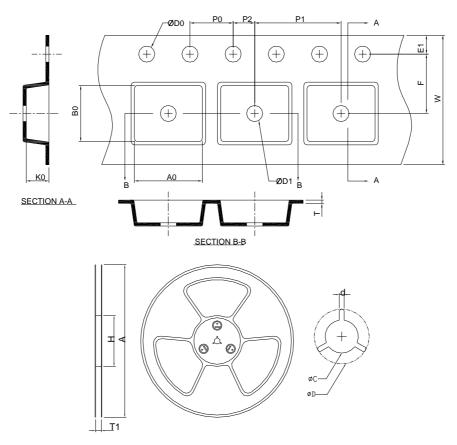

- TQFN 4x4 Package

- Lead Free and Green Devices Available (RoHS Compliant)

## **Applications**

- · Tablet PC

- Smart Phone

- · Portable Audio Speaker

- · Portable Media Players

- · Internet Devices

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

Copyright © ANPEC Electronics Corp. Rev. A.4 - Dec., 2018

# APW7264

### **General Description**

The APW7264 is a highly-integrated switch-mode battery charge management and system power path management device for single cell Li-ion and Li-polymer battery in a wide range of tablet and other portable devices. Its low impedance power path optimizes switch-mode operation efficiency, reduces battery charging time and extends battery life during discharging phase. The I<sup>2</sup>C serial interface with charging and system settings makes the device a truly flexible solution.

The device supports 3.9V - 6.2V USB input sources, including standard USB host port and USB charging port with 6. 4V over-voltage protection. The device supports USB 2.0 and USB 3.0 power specifications with input current and voltage regulation. To set the default input current limit, the APW7264 takes the result from the detection circuit in the system, such as USB PHY device. The device also supports USB On-the-Go operation by providing fast startup and supplying adjustable voltage 4.55 °V 5.5V (default 5V) on the VBUS with an accurate current limit up to 1.5A. The power path management regulates the system slightly above battery voltage but does not drop below 3.5V minimum system voltage (programmable). With this feature, the system keeps operating even when the battery is completely depleted or removed. When the input source current or voltage limit is reached, the power path management automatically reduces the charge current to zero and then starts discharges the battery until the system power requirement is met. This supplement mode operation keeps the input source from getting overloaded.

The device initiates and completes a charging cycle when host control is not available. It automatically charges the battery in three phases: pre-conditioning, constant current and constant voltage. In the end, the charger automatically terminates when the charge current is below a preset limit in the constant voltage phase. Later on, when the battery voltage falls below the recharge threshold, the charger will automatically start another charging cycle. The charge device provides various safety features for battery charging and system operation, including negative thermistor monitoring, charging safety timer and over-voltage/over-current protections. The thermal regulation reduces charge current when the junction temperature exceeds 120°C (programmable).

The STAT output reports the charging status and any fault conditions. The INT immediately notifies host when fault occurs.

2

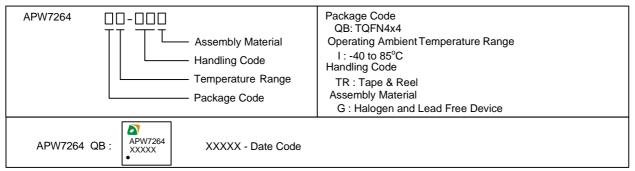

The APW7264 is available in a 24-pin, 4x4 mm<sup>2</sup> thin QFN package.

### **Pin Configuration**

Ο

1

2

4

VBUS

PSEL

PGB 3

STAT

SCL 5

SDA 6

Copyright © ANPEC Electronics Corp. Rev. A.4 - Dec., 2018

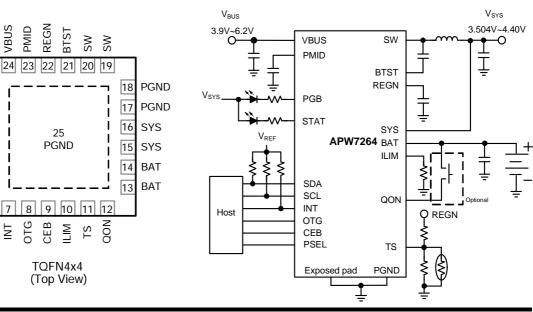

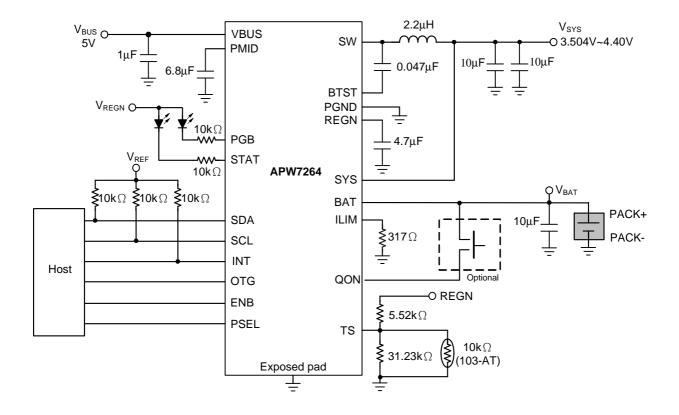

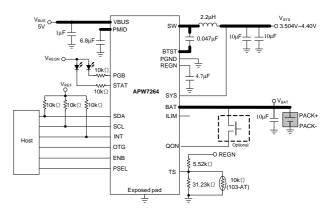

# Simplified Application Circuit

## Ordering and Marking Information

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS and compatible with both SnPb and lead-free soldiering operations. ANPEC lead-free products meet or exceed the leadfree requirements of IPC/JEDEC J STD-020C for MSL classification at lead-free peak reflow temperature.

## Absolute Maximum Ratings (Note 1)

| Sym bol           | Parameter                                                         | Rating     | Unit |

|-------------------|-------------------------------------------------------------------|------------|------|

| V <sub>VBUS</sub> | VBUS to GND Voltage                                               | -2 ~ 15    | V    |

|                   | PMID to GND Voltage                                               | -0.3 ~ 15  | V    |

|                   | BTST, STAT, PGB to GND Voltage                                    | -0.3 ~ 12  | V    |

|                   | SW to GND Voltage                                                 | -2 ~ 7     | V    |

|                   | BAT, SYS (converter not switching) to GND Voltage                 | -0.3 ~ 6   | V    |

|                   | SDA, SCL, INT, OTG, ILIM, REGN, TS, QON, CEB, PSEL to GND Voltage | -0.3 ~ 7   | V    |

|                   | BTST to SW Voltage                                                | -0.3 ~ 7   | V    |

|                   | PGND to GND                                                       | -0.3 ~ 0.3 | V    |

|                   | INT, STAT, PGB Output Sink Current                                | 6          | mA   |

| TJ                | Maximum Junction Temperature                                      | -40 ~ 150  | °C   |

| T <sub>STG</sub>  | Storage Temperature                                               | -65 ~ 150  | °C   |

| T <sub>SDR</sub>  | Maximum Lead Soldering Temperature (10 Seconds)                   | 260        | °C   |

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

## **Thermal Characteristics**

| Sym bo l      | Parameter                                           | Typical Value | Unit |

|---------------|-----------------------------------------------------|---------------|------|

| $\theta_{JA}$ | Junction-to-Ambient Resistance in free air (Note 2) | 52            | °C/W |

| θ」C           | Junction-to-Case Resistance                         | 7             | °C/W |

Note 2:  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. The exposed pad of TQFN4x4 is soldered directly on the PCB

# Recommended Operating Conditions (Note 3)

| Symbol            | Pa ra mete r          | Range     | Unit |

|-------------------|-----------------------|-----------|------|

| $V_{\text{VBUS}}$ | VBUS to GND Voltage   | 3.9 ~ 6.2 | V    |

| I <sub>SYS</sub>  | SYS Output Current    | 0 ~ 3.5   | А    |

| V <sub>BAT</sub>  | BAT to GND Voltage    | 3.5 ~ 4.4 | V    |

| I <sub>BAT</sub>  | Fast Charging Current | ~ 3       | А    |

| T <sub>A</sub>    | Ambient Temperature   | -40 ~ 85  | °C   |

| TJ                | Junction Temperature  | -40 ~ 125 | °C   |

Note 3: Refer to the typical application circuit.

## **Electrical Characteristics**

Unless otherwise specified, these specifications apply over  $V_{VBUS_UVLOZ} < V_{VBUS} < V_{ACOV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ , and  $T_A = -40$  to 85 °C. Typical values are at  $T_A = 25^{\circ}$ C

| Symbol                        | Baramatar                                                                                                                                                  | Test Conditions                                                                                                                                |                             | APW 7264 |      |      | Unit |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------|------|------|------|

| Symbol                        | Parameter                                                                                                                                                  | Test Con                                                                                                                                       | lations                     | Min      | Тур  | Max  |      |

| QUIESCEN                      | IT CURRENTS                                                                                                                                                |                                                                                                                                                |                             |          |      |      |      |

|                               |                                                                                                                                                            | V <sub>VBUS</sub> =flaoting, V <sub>BAT</sub> =<br>leakage between<br>(VBUS to GND Leak                                                        | BAT and VBUS                | -        | -    | 5    | μA   |

| I <sub>BAT</sub>              | Battery Discharge Current<br>(BAT, SW, SYS)                                                                                                                | High-Zmode, orno'<br>BATFET disabled (R<br>T <sub>A</sub> = -40 to 85 °C                                                                       |                             | -        | 32   | 55   | μΑ   |

|                               |                                                                                                                                                            | High-Z mode, or no<br>BATFET enabled RE<br>T <sub>A</sub> = -40 to 85 °C                                                                       | /                           | -        | 32   | 55   | μA   |

|                               |                                                                                                                                                            | V <sub>vвus</sub> =5V, High-Z mo                                                                                                               | ode, No battery             | -        | 32   | 55   | μA   |

|                               |                                                                                                                                                            | V <sub>VBUS</sub> >V <sub>VBUS_UVLOZ</sub> , V<br>converternot switch                                                                          |                             |          | 4.5  | 6    | mA   |

| I <sub>VBUS</sub>             | Input Supply Current (VBUS)                                                                                                                                | V <sub>VBUS</sub> >V <sub>VBUS_UVLOZ</sub> ,<br>V <sub>VBUS</sub> >V <sub>BAT</sub> , converte<br>V <sub>BAT</sub> =3.2V, I <sub>SYS</sub> =0A | er switching,               | - 35 -   |      | mA   |      |

|                               | V <sub>VBUS</sub> >V <sub>VBUS</sub> _UVLOZ,<br>V <sub>VBUS</sub> >V <sub>BAT</sub> , converter<br>switching, V <sub>BAT</sub> =3.8V, I <sub>SYS</sub> =0A |                                                                                                                                                |                             | -        | 35   | -    | mA   |

| I <sub>OTGBOOST</sub>         | Battery Discharge Current In Boot Mode                                                                                                                     | V <sub>BAT</sub> =4.2V, Boost mo<br>I <sub>VBUS</sub> =0A, converters                                                                          | ,                           | -        | 25   | -    | mA   |

| VBUS/BAT                      | POWER UP                                                                                                                                                   |                                                                                                                                                |                             |          |      |      |      |

|                               | VBUS Operating Voltage Range                                                                                                                               |                                                                                                                                                |                             | 3.9      | -    | 6.2  | V    |

| V <sub>VBUS_UVLOZ</sub>       | VBUS For Active I <sup>2</sup> C, No Battery                                                                                                               | V <sub>VBUS</sub> rising                                                                                                                       |                             | 3.6      | -    | -    | V    |

| $V_{SLEEP}$                   | Sleep Mode Falling Threshold                                                                                                                               | $V_{VBUS}$ falling, $V_{VBUS}$ -V                                                                                                              | / <sub>BAT</sub>            | 35       | 80   | 120  | m٧   |

| $V_{\text{SLEEPZ}}$           | Sleep Mode Rising Threshold                                                                                                                                | V <sub>VBUS</sub> rising, V <sub>VBUS</sub> -V                                                                                                 | BAT                         | 170      | 250  | 350  | m۷   |

| V <sub>ACOV</sub>             | VBUS Over Voltage Rising Threshold                                                                                                                         | V <sub>VBUS</sub> rising                                                                                                                       |                             | 6.2      | -    | 6.6  | V    |

| $V_{\text{ACOV}\_\text{HYS}}$ | VBUS Over Voltage Falling Hysteresis                                                                                                                       | V <sub>VBUS</sub> falling                                                                                                                      |                             | -        | 200  | -    | mV   |

| $V_{\text{BAT}\_\text{DPL}}$  | Battery Depletion Threshold                                                                                                                                | V <sub>BAT</sub> falling                                                                                                                       |                             | -        | 2.4  | 2.6  | V    |

| V <sub>BAT_DPL_HYS</sub>      | Battery Depletion Rising Hysteresis                                                                                                                        | V <sub>BAT</sub> rising                                                                                                                        |                             | -        | 150  | -    | mV   |

| POWER P                       | ATH MANAGEMENT                                                                                                                                             |                                                                                                                                                |                             |          |      |      |      |

| $V_{\text{SYS}\_\text{MAX}}$  | Maximum DC System Voltage Output                                                                                                                           | I <sub>SYS</sub> =0A, BATFET (Q4) off, V <sub>BAT</sub> up to<br>4.35V                                                                         |                             | -        | -    | 4.43 | V    |

| $V_{\text{SYS}\_\text{MIN}}$  | Minimum DC System Voltage Output                                                                                                                           | REG01[3:1]=101, V <sub>SYSMIN</sub> =3.5V                                                                                                      |                             | 3.5      | 3.65 | -    | V    |

| $R_{\text{ON}(\text{RBFET})}$ | Internal Top Reverse Blocking MOSFET<br>On-Resistance                                                                                                      | Measured between VBUS and PMID                                                                                                                 |                             | -        | 28   | 41   | mΩ   |

| Ray                           | Internal Top Switching MOSFET On-resistance                                                                                                                | Measured between                                                                                                                               | $T_{A}$ =-40°C ~85°C        | -        | 61   | 82   | mΩ   |

| $R_{ON_{HS}}$                 |                                                                                                                                                            | PMID and SW $T_A=-40^{\circ}C\sim125^{\circ}C$                                                                                                 | -                           | 61       | 90   |      |      |

| Paula                         |                                                                                                                                                            | Measured between                                                                                                                               | T <sub>A</sub> =-40°C~85°C  | -        | 61   | 82   | mΩ   |

| R <sub>ON_LS</sub>            | On-resistance                                                                                                                                              | SW and PGND                                                                                                                                    | T <sub>A</sub> =-40°C~125°C | -        | 61   | 90   |      |

## **Electrical Characteristics (Cont.)**

Unless otherwise specified, these specifications apply over  $V_{VBUS_{UVLOZ}} < V_{VBUS} < V_{ACOV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ , and  $T_A = -40$  to 85 °C. Typical values are at  $T_A = 25^{\circ}$ C

| Cum hal                        | Parameter Test Conditions                    |                                                                                   |                                  | APW726 | 4    | Unit |          |

|--------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------|--------|------|------|----------|

| Symbol                         | Para meter                                   | lest Cond                                                                         | itions                           | Min    | Тур  | Max  | Unit     |

| POWER PATH                     | H MANAGEMENT                                 |                                                                                   |                                  |        |      |      | <u>.</u> |

| V <sub>FWD</sub>               | BATFET Forward Voltage In Supplement<br>Mode | t V <sub>BAT</sub> -V <sub>SYS</sub> , BAT discharge current<br>10mA              |                                  | -      | 30   | -    | mV       |

| VBATGD                         | Battery Good Comparator Rising Threshold     | V <sub>BAT</sub> rising                                                           |                                  | -      | 3.55 | -    | V        |

| $V_{\text{BATGD}_{HYS}}$       | Battery Good Comparator falling Hysteresis   | V <sub>BAT</sub> falling                                                          |                                  | -      | 100  | -    | mV       |

| BATTERY CH                     | ARGER                                        |                                                                                   |                                  |        |      |      |          |

| $V_{BAT\_REG\_ACC}$            | Charge Voltage Regulation Accuracy           | V <sub>BAT</sub> =4.112V and 4.208V                                               |                                  | -0.5   | -    | +0.5 | %        |

|                                |                                              | V 2.0V                                                                            | ſ <sub>A</sub> = 25°C            | -4     | -    | +4   |          |

| ICHG_REG_ACC                   | Fast Charge Current Regulation Accuracy      |                                                                                   | Γ <sub>Α</sub> = -20°C<br>-125°C | -7     | -    | +7   | %        |

|                                |                                              | V <sub>BAT</sub> =3.8V, T <sub>A</sub> = -20°C<br>I <sub>CHG</sub> =1792mA ~125°C |                                  | -10    | -    | +10  | -        |

| I <sub>CHG_20%</sub>           | Charge Current With 20% Option On            | V <sub>BAT</sub> =3.8V, REG02=01                                                  |                                  | -      | 100  | -    | mA       |

| VBATLOWV_F                     | Battery LOWV Falling Threshold               | Fast charge to precha                                                             | rge, REG04[1]=1                  | 2.6    | 2.8  | 2.9  | V        |

| V <sub>BATLOWV_R</sub>         | Battery LOWV Rising Threshold                | Precharge to fast cha                                                             | rge, RE G04[1]=1                 | 2.8    | 3.0  | 3.1  | V        |

| I <sub>PRECHG_ACC</sub>        | Precharge Current Regulation Accuracy        | V <sub>BAT</sub> =2.6V, I <sub>CHG</sub> =128m                                    | hΑ                               | -      | 20   | -    | %        |

| ITERM_ACC                      | Termination CurrentAccuracy                  | I <sub>TERM</sub> =256mA, I <sub>CHG</sub> =20                                    | 48mA                             | -20    | -    | +20  | %        |

| V <sub>BAT_SHORT</sub>         | Battery Short Voltage                        | V <sub>BAT</sub> falling                                                          |                                  | -      | 2    | -    | V        |

| V <sub>BAT_SHORT_HYS</sub>     | Battery Short Voltage Hysteresis             | V <sub>BAT</sub> rising                                                           |                                  | -      | 200  | -    | mV       |

| ISHORT                         | Battery Short Current                        | V <sub>BAT</sub> <2.2V                                                            |                                  | -      | 100  | -    | mA       |

| VRECHG                         | Recharge Threshold Below VBAT_REG            | V <sub>BAT</sub> falling, REG04[0]                                                | =0                               | -      | 100  | -    | mV       |

| t <sub>RECHG</sub>             | Recharge Deglitch Time                       | V <sub>BAT</sub> falling, REG04[0]                                                | =0                               | -      | 100  | -    | ms       |

| 5                              |                                              | T <sub>A</sub> = 25°C                                                             |                                  | -      | 24   | 28   |          |

| Ron_batfet                     | SYS-BAT MOSFET On-resistance                 | T <sub>A</sub> = -20°C ~125°C                                                     |                                  | -      | 24   | 35   | mΩ       |

| INPUT VOLTA                    | AGE/CURRENT REGULATION                       |                                                                                   |                                  |        |      |      | <u> </u> |

| V <sub>INDPM_REG_ACC</sub>     | Input Voltage Regulation Accuracy            |                                                                                   |                                  | -2     | -    | +2   | %        |

|                                |                                              |                                                                                   | USB100                           | 85     | -    | 100  | mA       |

|                                |                                              | V <sub>BUS</sub> =5V, currer                                                      | USB150                           | 125    | -    | 150  | mA       |

| USB_DPM                        | USB Input Current Regulation Limit           | pulled from SW                                                                    | USB500                           | 440    | -    | 500  | mA       |

|                                |                                              | USB900                                                                            |                                  | 750    | -    | 900  | mA       |

| IADPT_D PM                     | Input Current Regulation Accuracy            | Input current limit 1.5/<br>REG00[2:0]=101                                        | λ,                               | 1.3    | -    | 1.5  | A        |

| I <sub>IN_START</sub>          | Input Current Limit During Start Up          | V <sub>SYS</sub> <2.2V                                                            |                                  | -      | 100  | -    | mA       |

|                                | ILIM Pin Source Current                      | ILIM Pin Current Limit                                                            | method                           | 17     | 20   | 23   | μA       |

| BATTERY OV                     | ER-VOLTAGE PROTECTION                        | 1                                                                                 |                                  |        |      | 1    |          |

| VBATOVP                        | Battery Over-Voltage Threshold               | V <sub>BAT</sub> rising, as percen                                                | tage of $V_{BAT_REG}$            | -      | 106  | -    | %        |

| $V_{\text{BATOVP}_\text{HYS}}$ | Battery Over-Voltage Hysteresis              | V <sub>BAT</sub> falling, as percen                                               | tage of $V_{BAT_REG}$            | -      | 2    | -    | %        |

| THERMAL RE                     | EGULATION AND THERMAL SHUTDOWN               |                                                                                   |                                  |        |      |      |          |

| $T_{J\_REG}$                   | Junction Temperature Regulation              | REG06[1:0]=11                                                                     |                                  | -      | 120  | -    | °C       |

| T <sub>SHUT</sub>              | Thermal Shutdown Rising Temperature          | Temperature increasir                                                             | ng                               | -      | 160  | -    | °C       |

| T <sub>SHUT_HYS</sub>          | Thermal Shutdown Hysteresis                  |                                                                                   |                                  | -      | 30   | -    | °C       |

## **Electrical Characteristics (Cont.)**

Unless otherwise specified, these specifications apply over  $V_{VBUS_{UVLOZ}} < V_{VBUS} < V_{ACOV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ , and  $T_A = -40$  to 85 °C. Typical values are at  $T_A = 25^{\circ}$ C

| Cumbal                      | Do romoto r                             | Toot Conditions                                                                                       | A    | PW726 | 4    | l Incid |

|-----------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------|------|-------|------|---------|

| Symbol                      | Para mete r                             | Test Conditions                                                                                       | Min  | Тур   | Max  | Unit    |

| COLD/HOT                    | THERMISTER COMPARATOR                   | -                                                                                                     |      |       |      |         |

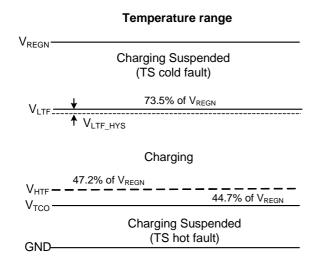

| $V_{LTF}$                   | Cold Temperature Threshold              | TS pin voltage rising threshold. Charger suspends charge. As percentage to V <sub>REGN</sub>          | 73   | 73.5  | 74   | %       |

| $V_{\text{LTF}_\text{HYS}}$ | Cold Temperature Hysteresis             | TS pin voltage falling. As percentage to $V_{\mbox{\scriptsize REGN}}$                                | -    | 0.4   | -    | %       |

| $V_{\text{HTF}}$            | Hot Temperature Threshold               | TS pin voltage rising threshold. As percentage to V <sub>REGN</sub>                                   | 46.6 | 47.2  | 48.8 | %       |

| V <sub>TCO</sub>            | Cut-off Temperature Threshold           | TS pin voltage falling. As percentage to $V_{\mbox{\scriptsize REGN}}$                                | 44.2 | 44.7  | 45.2 | %       |

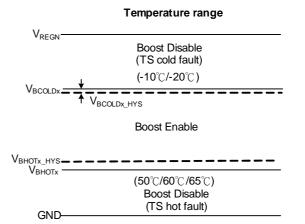

| V <sub>BCOLD0</sub>         | Cold Temperature Threshold 0            | TS pin voltage rising, As persentage to<br>V <sub>REGN</sub> REG02[1]=0<br>(Approx10°C w/103AT)       | 75   | 76    | 77   | %       |

| V <sub>BCOLD0_HYS</sub>     | Cold Temperature Threshold 0 Hysteresis | TS pin voltage falling, As persentage to<br>V <sub>REGN</sub> REG02[1]=0<br>(Approx. 1°C w/103AT)     | -    | 1     | -    | %       |

| V <sub>BCOLD1</sub>         | Cold Temperature Threshold 1            | TS pin voltage rising, As persentage to<br>V <sub>REGN</sub> REG02[1]=1<br>(Approx20°C w/103AT)       | 77.5 | 78.5  | 79.5 | %       |

| $V_{BCOLD1_HYS}$            | Cold Temperature Threshold 1 Hysteresis | TS pin voltage falling, As persentage to<br>V <sub>REGN</sub> REG02[1]=0<br>(Approx. 1°C w/103AT)     | -    | 1     | -    | %       |

| V <sub>BHOT0</sub>          | Hot Temperature Threshold 0             | TS pin voltage falling, As persentage to<br>V <sub>REGN</sub> REG06[3:2]=01<br>(Approx. 55°C w/103AT) | 35.5 | 36    | 36.5 | %       |

| V BHOTO_HYS                 | Hot Temperature Threshold 0 Hysteresis  | TS pin voltage rising, As persentage to<br>V <sub>REGN</sub> REG06[3:2]=01<br>(Approx. 3°C w/103AT)   | -    | 3     | -    | %       |

| V <sub>BHOT1</sub>          | Hot Temperature Threshold 1             | TS pin voltage falling, As persentage to<br>V <sub>REGN</sub> REG06[3:2]=00<br>(Approx. 60°C w/103AT) | 32.5 | 33    | 33.5 | %       |

| $V_{BHOT1\_HYS}$            | Hot Temperature Threshold 1 Hysteresis  | TS pin voltage rising, As persentage to<br>V <sub>REGN</sub> REG06[3:2]=00<br>(Approx. 3°C w/103AT)   | -    | 3     | -    | %       |

| V <sub>BHOT2</sub>          | Hot Temperature Threshold 2             | TS pin voltage falling, As persentage to<br>V <sub>REGN</sub> REG06[3:2]=10<br>(Approx. 65°C w/103AT) | 29.5 | 30    | 30.5 | %       |

| V <sub>BHOT2_HYS</sub>      | Hot Temperature Threshold 2 Hysteresis  | TS pin voltage rising, As persentage to<br>V <sub>REGN</sub> REG06[3:2]=10<br>(Approx. 3°C w/103AT)   | -    | 3     | -    | %       |

| CHARGE O                    | VER-CURRENT COMPARATOR                  | · · · · · ·                                                                                           |      |       |      |         |

| I <sub>HSFET_OCP</sub>      | HSFET Over-Current Threshold            |                                                                                                       | 5.3  | 7     | -    | А       |

| CHARGE U                    | NDER-CURRENT COMPARATOR (CYCLE-         | BY-CYCLE)                                                                                             |      |       |      | ·       |

| I <sub>LSFET_ZC</sub>       | Low Side MOSFET Zero Crossing Threshold | From sync mode to non-sync mode                                                                       | -    | 100   | -    | mA      |

| PWMOPER                     | ATION                                   |                                                                                                       |      |       |      |         |

| f <sub>SW</sub>             | PWM Switching Frequency                 |                                                                                                       | 1.3  | 1.5   | 1.7  | MHz     |

| D <sub>MAX</sub>            | Maximum PWM Duty Cycle                  |                                                                                                       | -    | 97    | -    | %       |

## **Electrical Characteristics (Cont.)**

Unless otherwise specified, these specifications apply over  $V_{VBUS_{UVLOZ}} < V_{VBUS} < V_{ACOV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ , and  $T_A = -40$  to 85 °C. Typical values are at  $T_A = 25^{\circ}$ C

| Symbol                        | Parameter                                                 | Test Conditions                                         | APW7264 |      |     | Unit |

|-------------------------------|-----------------------------------------------------------|---------------------------------------------------------|---------|------|-----|------|

| Symbol                        | Falameter                                                 | Test Conditions                                         | Min     | Тур  | Max | Onit |

| BOOSTMO                       | DDE OPERATION                                             |                                                         |         |      |     |      |

| $V_{OTG\_REG}$                | OTG Output Voltage                                        | I <sub>VBUS</sub> =0A, REG06[7:4]=0111(4.998V)          | -       | 5    | -   | V    |

| Votg_reg_acc                  | OTG Output Voltage Accuracy                               | I <sub>VBUS</sub> =0A, REG06[7:4]=0111(4.998V)          | -3      | -    | +3  | %    |

| $V_{\text{INOTG}_\text{BAT}}$ | Battery Voltage Into OTG mode                             | VBAT Rising, IOTG=0A, REG04[1]=1                        | -       | -    | 3.1 | V    |

| V <sub>OUTOTG_BAT</sub>       | Battery Voltage Exit OTG mode                             | VBAT Falling, IOTG=0A, REG04[1]=1                       | 2.9     | -    | -   | V    |

| 1                             | OTO Made Output Ourrent                                   | REG01[0]=0                                              | 1       | -    | -   | _    |

| I <sub>OTG</sub>              | OTG Mode Output Current                                   | REG01[0]=1                                              | 1.5     | -    | -   | A    |

| Votg_ovp                      | OTG Over-Voltage Threshold                                | Rising threshold                                        | -       | 6    | -   | V    |

| V BATMAX                      | Maximum Battery Voltage for Boost Mode                    | V <sub>BAT</sub> Rising Edge During Boost Mode          | -       | 4.9  | -   | V    |

| VBATMAX_HYS                   | Maximum Battery Voltage Hysteresis for<br>Boost Mode      | $V_{\text{BAT}}$ Falling From Above $V_{\text{BATMAX}}$ | -       | 200  | -   | mV   |

| I <sub>OTG_LIM</sub>          | Low Side MOSFET Cycle-by-cycle Current<br>Limit           |                                                         | -       | 5    | -   | A    |

| I <sub>OTG_ZC</sub>           | High Side MOSFET Zero Crossing<br>Threshold               | High side FET current falling                           | -       | 100  | -   | mA   |

| I <sub>R BFET_LIM</sub>       | RBFET Current Limit Threshold                             | REG01[0]=1                                              | 1.5     | 1.7  | 1.9 | A    |

|                               |                                                           | REG01[0]=0                                              | 1       | 1.15 | 1.3 |      |

| T <sub>OTG_OCP_OFF</sub>      | OTG OCP Off Time                                          | OTG mode over-current protection off<br>cycle time      | -       | 32   | -   | ms   |

| T <sub>OTG_OCP_ON</sub>       | OTG OCP On Tim e                                          | OTG mode over-current protection on<br>cycle time       | -       | 2    | -   | ms   |

| REGN LDO                      |                                                           |                                                         |         |      | -   |      |

| V <sub>REGN</sub>             | REGN LDO Output Voltage                                   | V <sub>VBUS</sub> =5V, I <sub>REGN</sub> =0mA           | 4.8     | 5    | 5.5 | V    |

| * REGN                        |                                                           | $V_{VBUS}=5V, I_{REGN}=20mA$                            | 4.4     | 4.8  | -   | V    |

| IREGN                         | REGN LDO Output Current                                   | V <sub>VBUS</sub> =5V, V <sub>REGN</sub> =3.8V          | 30      | -    | -   | mA   |

| LOGIC I/O                     | PIN CHARACTERISTICS (OTG, CEB, STAT,                      | QON, PSEL, PGB)                                         |         |      |     |      |

| VIL                           | Input Low Voltage                                         |                                                         | -       | -    | 0.4 | V    |

| V <sub>IH</sub>               | Input High Voltage                                        |                                                         | 1.3     | -    | -   | V    |

| $V_{O_LOW}$                   | Output Low Saturation Voltage                             | Sink current=5mA, Include STAT/PGB<br>Pins              | -       | -    | 0.4 | V    |

| I <sub>BIAS</sub>             | High Level Leakage Current (OTG, CEB,<br>STAT, PSEL, PGB) | Pull up rail 1.8V                                       | -       | -    | 1   | μA   |

| IBIAS                         | High Level Leakage Current (QON)                          | Pull up rail 3.6V                                       | -       | -    | 8   | μA   |

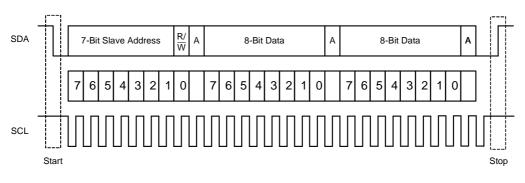

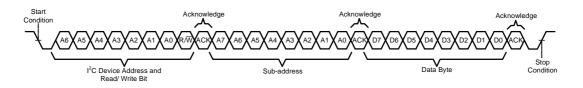

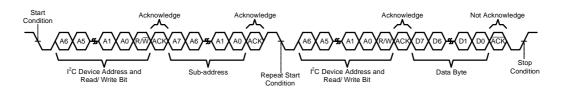

| I <sup>2</sup> C INTERF       | ACE (SDA, SCL, INT)                                       |                                                         |         |      |     | 4    |

| VIH                           | Input High Threshold Level                                | VPULL-UP=1.8V, SDA and SCL                              | 1.3     | -    | -   | V    |

| V <sub>IL</sub>               | Input Low Threshold Level                                 | VPULL-UP=1.8V, SDA and SCL                              | -       | -    | 0.4 | V    |

| V <sub>O_LOW</sub>            | Output Low Threshold Level                                | Sink current=5mA                                        | -       | -    | 0.4 | V    |

| I <sub>BIAS</sub>             | High Level Leakage Current                                | VPULL-UP=1.8V, SDA and SCL                              | -       | -    | 1   | μA   |

| f <sub>SCL</sub>              | SCL Clock Frequency                                       |                                                         | -       | -    | 400 | kHz  |

|                               | LOCK AND WATCHDOG TIMER                                   | · · · · · · · · · · · · · · · · · · ·                   |         | 1    |     |      |

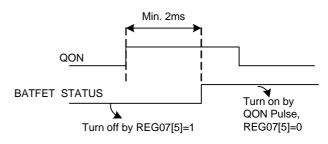

| T <sub>QON</sub>              | QON Pulsed width                                          | QON Pin High to Turn On BATFET                          | 2       | -    | -   | ms   |

| t <sub>WDT</sub>              | Watchdog Timer                                            | REG05[5:4]=11                                           | -       | 160  | -   | sec  |

# **Pin Description**

| PIN      |             |                                                                                                                                                                                                                                                                                              |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.      | NAME        | FUNCTION                                                                                                                                                                                                                                                                                     |

| 1,24     | VBUS        | Charger input voltage. Place a $1\mu F$ ceramic capacitor from VBUS to PGND and place it as close as possible to IC.                                                                                                                                                                         |

| 2        | PSEL        | Power source selection input. Low indicates an adapter source and High indicates a USB host source.                                                                                                                                                                                          |

| 3        | PGB         | Open drain active low power good indicator. Connect to the pull up rail via $10k\Omega$ resistor. Low indicates a good input source if the input voltage is between UVLO and ACOV, above SLEEP mode threshold.                                                                               |

| 4        | STAT        | Open drain charge status output to indicate various charger operation. Connect to the pull up rail via a $10k\Omega$ resistor. Low indicates charge in progress. High indicates charge complete or charge disabled. When any fault condition occurs, STAT pin blinks at 1Hz.                 |

| 5        | SCL         | I <sup>2</sup> C interface clock.                                                                                                                                                                                                                                                            |

| 6        | SDA         | I <sup>2</sup> C interface data.                                                                                                                                                                                                                                                             |

| 7        | INT         | Open interrupt output. Connect the INT to the pull up rail via $10k\Omega$ resistor. The INT pin sends active low, $256\mu$ s pulse to host to report charger device status and fault.                                                                                                       |

| 8        | OTG         | USB current limit selection pin during buck mode, and OTG mode enabled control pin.<br>In buck mode with USB host (PSEL=High), when OTG=High, IIN limit=500mA and when OTG=Low, IIN<br>limit=100mA.                                                                                          |

|          |             | The OTG mode is activated when the REG01[5:4]="10" or "11" and OTG pin is high.                                                                                                                                                                                                              |

| 9        | CEB         | Active low charge enable pin. Battery charging is enabled when REG01[6:5]="01" and CEB pin=low.<br>CEB pin must be pulled high or low.                                                                                                                                                       |

| 10       | ILIM        | Input Current Limit Setting Pin. Connect a resistor ( $R_{LIM}$ ) from this pin to the GND. This resistor, an internal 20µA current source ( $I_{ILM}$ ) set the maximum input current limit. The actual input current limit is the lower on set by ILIM and by I <sup>2</sup> C REG00[2:0]. |

| 11       | TS          | Temperature qualification voltage input. Connect a negative temperature coefficient thermistor.<br>Program temperature window with a resistor divider from REGN to TS to GND. Charge suspends when TS pin is out of range. Recommend 103AT-2 thermistor.                                     |

| 12       | QON         | BATFET enable control in shipping mode. A logic low to high transition on this pin with minim um 2ms high level turns on BATFET to exit shipping mode.                                                                                                                                       |

| 13       | BAT         | Battery connection point to the positive terminal of the battery pack. The internal BATFET is connected between BAT and SYS. Connect a $10\mu$ F closely to the BAT pin.                                                                                                                     |

| 14       |             |                                                                                                                                                                                                                                                                                              |

| 15<br>16 | SYS         | System connection point. The internal BATFET is connected between BAT and SYS. When the battery falls below the minimum system voltage, switch-mode converter keeps SYS above the minimum                                                                                                    |

| 17       |             | system voltage.<br>Power ground connection for high-current power converter node. Internally, PGND is connected to the source of the N-channel low side MOSFET. On PCB layout, connect directly to ground connection of                                                                      |

| 18       | - PGND      | input and output capacitors of the charger. A single point connection is recommended between power PGND and the analog GND near the IC PGND pin.                                                                                                                                             |

| 19       | 014/        | Junction point of the Internal high-side MOSFET Source, output filter inductor and internal the low-side MOSFET Drain.                                                                                                                                                                       |

| 20       | SW          | Connect the 47nF bootstrap capacitor from SW to BTST.                                                                                                                                                                                                                                        |

| 21       | BTST        | Supply Input for the Internal high-side gate driver and an internal level-shift circuit. Connect to an external ceramic capacitor 47nF from SW to BTST to create a boosted voltage suitable to drive a logic-level N-channel MOSFET.                                                         |

| 22       | REGN        | PWM low side driver positive supply output. Internally, REGN is connected to the anode of the boost-strap diode. Connect a 4.7μF (10V rating) ceramic capacitor from REGN to analog GND. The capacitor should be placed close to the IC. REGN also serves as bias rail of TS pin.            |

| 23       | PMID        | Converter Input Voltage. Connect at least 6.8µF ceramic capacitor from PMID to PGND and place it as close as possible to IC.                                                                                                                                                                 |

| -        | Exposed Pad | Exposed pad beneath the IC for heat dissipation and also the IC analog ground. Always solder thermal pad to the board,<br>and have vias on the thermal pad plane to PGND and ground plane for high-current power converter.                                                                  |

# APW7264

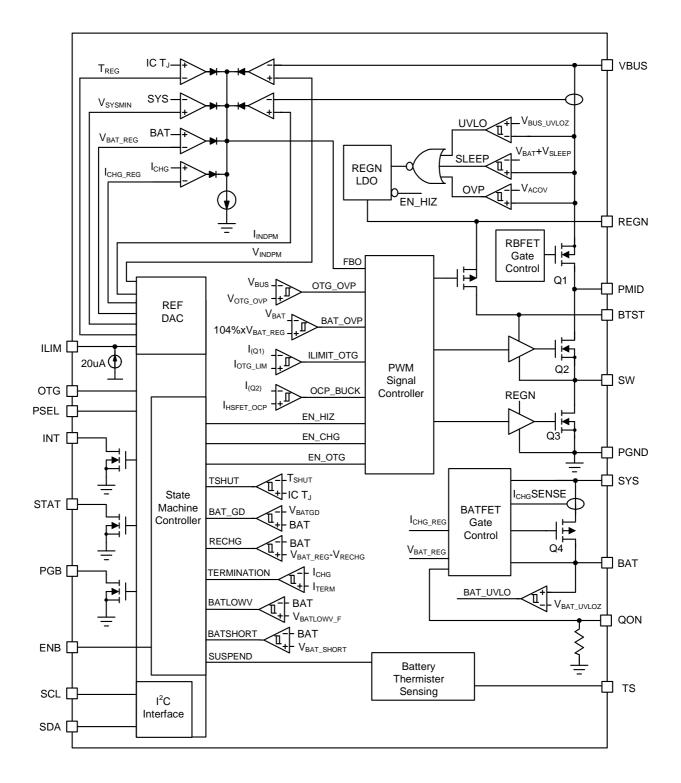

## **Block Diagram**

# APW7264

# **Typical Application Circuit**

## **Function Description**

The APW7264 is an I<sup>2</sup>C controlled power path management device and a single cell Li-Ion battery charger. It integrates the input reverse-blocking FET (RBFET, Q1), high-side switching FET (HSFET, Q2), low-side switching FET (LSFET, Q3), and BATFET (Q4) between system and battery.

The APW7264 is a switch-mode battery charger with fixed 1.5MHz switching frequency, which drives two integrated N-channel power MOSFETs. The step-down DC/DC converter is ideally suited for portable electronic devices. In addition, the APW7264 can supply 5V to USB On-The-Go (OTG) peripherals through I<sup>2</sup>C programmable.

The APW7264 has three operation states in substance: 1.Charge State - charges a single-cell Li-ion or Li-polymer battery with an integrated synchronous rectification buck regulator.

2.Boost State - supply 5V power to USB-OTG with an integrated synchronous rectification boost regulator using battery terminal as input.

3.High-Impedance State - Both the charging and OTG circuits are off. This state consumes low quiescent current from VBUS or the battery.

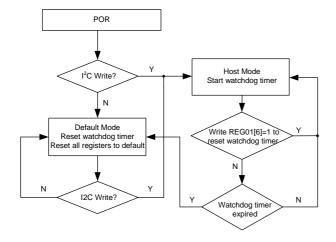

#### Power-On-Reset (POR)

The internal bias circuits are powered from the higher voltage of VBUS and BAT. The battery depletion comparator, sleep comparator and BATFET driver are active when VBUS or VBAT rises above UVLOZ. I<sup>2</sup>C interface is actived and all the registers are reset to default value.

#### Power Up from Battery without DC Source

If only battery is present and the VBAT voltage is above depletion threshold ( $V_{BAT_DEPL}$ ), it turns the BATFET on to connect battery to system. The REGN LDO stays off to minimize the quiescent current and maximize the battery run time.

#### **BATFET Turn Off**

The host can through I<sup>2</sup>C REG07[5] force the BATFET to tunn off . When the battery condition becomes abnormal during charging, the user can use this bit to independently turn off the BATFET. When the BATFET is off, there is no path to charge or discharge the battery.

Copyright © ANPEC Electronics Corp. Rev. A.4 - Dec., 2018 When battery is not attached, the BATFET should be turned off by setting REG07[5] to 1 to disable charging and supplement mode. In general, no the battery attached condition is not recommended.

#### **Shipping Mode**

When end equipment is assembled, the system is connected to battery through BATFET. There will be a small leakage current to discharge the battery even when the system is powered off. In order to extend the battery life during shipping and storage, the device can turn off BATFET so that the system voltage is zero to minimize the leakage.

In order to keep BATFET off during shipping mode, the host has to turn off BATFET (REG07[5]=1) and disable the watchdog timer (REG05[5:4]=00) at the same time. Once the BATFET is disabled, one of the following events can turn on BATFET and clear REG07[5] (BATFET\_DISABLE) bit.

- 1. Plug in adapter

- 2. Write REG07[5] = 0

- 3. Watchdog timer expiration

- 4. Register reset (REG01[7] = 1)

- 5. A logic low to high transition on QON pin

Turn on BATFET by QON Low to high Pulse

#### Power Up from DC Source

When the DC source plugs in, the APW7264 checks the input source voltage to turn on REGN LDO and all the bias circuits. It also cateches the input current limit setting value before starts the buck converter.

#### REGNLDO

The APW7264 internal bias circuits as well as the HSFET and LSFET gate drive are supplied by REGN LDO. The REGN LDO also provides bias rail to TS external resistors and the pull-up rail of STAT and PGB can be connected to REGN as well.

The REGN is enabled when all the conditions are valid. 1. VBUS above UVLOZ

2. VBUS above battery + VSLEEPZ in buck mode or VBUS below battery + VSLEEPZ in boost mode

If one of the above conditions is not valid, the device is in high impedance mode (HIZ) with REGN LDO off. In HIZ state, the device draws less than  $50\mu$ A from VBUS. The system powered up by battery when the device is in HIZ.

#### Input Current Limit Detection

The USB ports on personal computers are convenient charging source for portable devices (PDs). If the portable device is attached to a USB host, the USB specification requires the portable device to draw limited current (100mA/500mA in USB 2.0, and 150mA/900mA in USB 3. 0). If the portable device is attached to a charging port, it is allowed to draw up to 3A. After the PGB is low or REG08 [2] goes high, the charger device always runs input current limit detection when a DC source plugs in unless the charger is in HIZ during host mode. The APW7264 sets input current limit through PSEL/OTG and ILIM pins. After the input current limit detection is done, the host can write to REG00[2:0] to change the input current limit.

#### **PSEL/OTG Pins Set Input Current Limit**

The APW7264 has PSEL and OTG pin instead of D+/D-. It directly takes the USB PHY device output to decide whether the input is USB host or charging port.

| PSEL | OTG  | Input Current Limit | REG08[7:6] |

|------|------|---------------------|------------|

| HIGH | LOW  | 100mA               | 01         |

| HIGH | HIGH | 500mA               | 01         |

| LOW  | Х    | 3A                  | 10         |

#### **Converter Power-Up**

After the input current limit is set, the converter is enabled and the HSFET and LSFET start switching. If battery charging is disabled, BATFET turns off. Otherwise, BATFET stays on to charge the battery.

When the system rail is below 2V, the input current limit is forced to 100mA. After the system rises above 2.2V, the charger device sets the input current limit value by the lower value between register and ILIM pin setting. As a battery charger, the APW7264 deploys a 1.5MHz stepdown switching regulator. The fixed frequency oscillator keeps tight control of the switching frequency under all conditions of input voltage, battery voltage, charge current and temperature, simplifying output filter design.

In order to improve light-load efficiency, the device provides PFM control at light load condition. During the PFM operation, the switching duty cycle is set by the ratio of SYS and VBUS.

#### **Boost Mode Operation from Battery**

The APW7264 supports boost converter operation to deliver power from the battery to other portable devices through USB port. The boost mode output current rating meets the USB On-The-Go 1A output requirement. The maximum output current is 1.5A. The following conditions are valid to enable the boost operation.

1. VBAT above BATLOWV threshold (V\_{ $_{\rm BATLOWV}}$  set by REG04 [1])

2. VBUS less than VBAT+V<sub>SLEEP</sub> (in sleep mode)

3. Boost mode operation is enabled (OTG pin HIGH and REG01[5:4]=10)

4. After 40ms delay from boost mode enable

In boost mode, APW7264 employs a 1.5MHz step-up switching regulator. To improve ligh load efficiency, the device operates on PFM operation at light load.

During boost mode, the status register REG08[7:6] is set to 11, the VBUS output is 5V. The output current selected via I<sup>2</sup>C (REG01[0]) can reach up to 1A or 1.5A. Any fault during boost operation sets the fault register REG09[6] to 1 and an INT is asserted.

#### **Power Path Management**

The APW7264 accommodates a wide range of input sources from wall adapter, USB, to car battery. The system (SYS) is provided by the automatic power path selection from input source (VBUS), battery (BAT), or both.

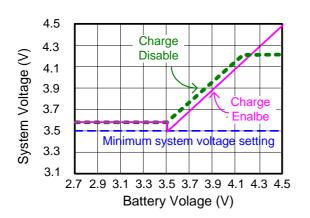

#### Narrow VDC Architecture

The device deploys Narrow VDC architecture (NVDC) with BATFET separating system from battery. The minimum system voltage is programmed by REG01[3:1]. The system is regulated above the minimum system voltage (default 3.5V) even with a fully depleted battery.

The BATFET operates in linear mode, and the system is 150mV above the minimum system voltage setting when the battery is below minimum system voltage setting. As the battery voltage rises above the minimum system voltage, the BATFET is fully on and the voltage difference between the system and battery is the VDS of BATFET.

When the battery charging, termination are disabled and the battery voltage is above minimum system volatge setting, the system is regulated at 150mV above the battery voltage until  $V_{SYS}$  reaches to the programmed battery charging target. The status register REG08[0] goes high when the system is in minimum system voltage regulation.

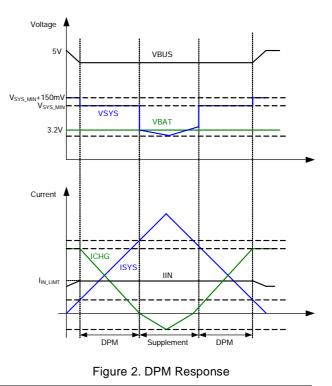

#### **Dynamic Power Management**

The total input current is a function of the system supply current and the battery charging current. When the summation of system power and charge power exceeds the maximum VBUS input power, the device will reduce input current by using Dynamic Power Management (DPM).

When input current exceeds the programmed input current limit (REG00[2:0]) or the VBUS falls below the programmed input voltage limit (REG00[6:3]), the device then reduces the charge current until the input current falls below the input current limit and the input voltage rises above the input voltage limit.

When the charge current is reduced to zero, but the input source is still overloaded, the system voltage starts to drop. Once the system voltage falls below the battery voltage, the device automatically enters the supplement mode where the battery starts discharging so that the system is provided from both the input source and battery.

During DPM mode (either VINDPM or IINDPM), the status register REG08[3] will go high.

The Figure 2. as below shows the DPM response and supplement mode.

Figure 1. System Voltage vs. Battery Volage

Copyright © ANPEC Electronics Corp. Rev. A.4 - Dec., 2018

#### Supplement Mode

When the system voltage falls below the battery voltage, the device fully turns on the BATFET. At this point onwards, the BATFET  $V_{DS}$  linearly increases with discharge current. BATFET turns off to exit supplement mode when the battery is below battery depletion threshold.

#### **Battery Charging Management**

The APW7264 charges 1-cell Li-lon battery with up to 2. 5A charge current for high capacity tablet battery. The  $24m\Omega$  BATFET improves charging efficiency and minimizes the voltage drop during discharging.

#### **Autonomous Charging Cycle**

With battery charging enabled at POR (REG01[5:4]=01), the APW7264 can complete a charging cycle without host involvement.

When the following conditions are valid, a new charge cycle will start.

- Converter starts

- Battery charging is enabled by I<sup>2</sup>C register bit (REG01[5:4]) = 01 and CEB is low

- No safety timer fault

- No thermistor fault on TS

- BATFET is not forced to turn off (REG07[5])

When the charging current is below programmed termination threshold and battery voltage is above recharge threshold, the charger device automatically terminates the charging cycle. When a full battery voltage is discharged below recharge threshold (REG04[0]), the APW7264 automatically starts another charging cycle. The STAT output indicates the charging status. STAT is low, the device is in charging state; STAT is high, the device is in charging complete or charge disable; STAT is blinking, the device indicates the charging fault. The status register REG08[5:4] indicates the different charging phases: 00-charging disable, 01-precharge, 10-fast charge, 11charging done. Once a charging cycle is complete, an INT is asserted to notify the host. The host can always control the charging operation by writing to the registers through I<sup>2</sup>C.

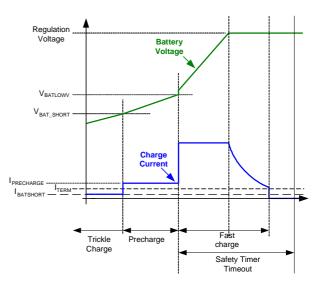

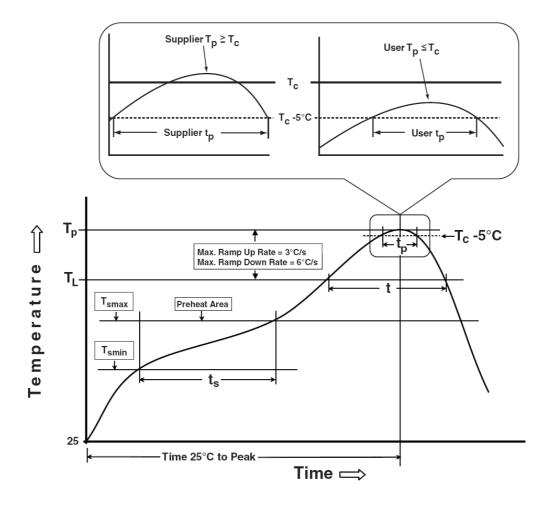

### **Battery Charging Profile**

The device charges the battery in three phases: preconditioning, constant current and constant voltage. At the beginning of a charging cycle, the device checks the battery voltage and determines the applied current.

| VBAT | Charging current | Register default setting | Reg08[5:4] |

|------|------------------|--------------------------|------------|

| <2V  | 100mA            | -                        | 01         |

| 2~3V | Reg03[7:4]       | 128mA                    | 01         |

| >3V  | Reg02[7:2]       | 2048mA                   | 10         |

The actual charging current will be less than the programmed value if the charger device is in DPM state or thermal regulation during charging. In this case, termination is temporarily disabled and the charging safety timer is counted at half the clock rate.

Figure 3. Battery Chaging Profile

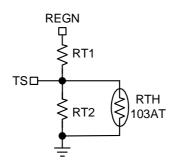

#### **Thermistor Qualification**

The high capacity battery usually has two or more single cells in parallel. The APW7264 provides TS pins to monitor the thermistor (NTC) in each cell independently.

#### **Cold/Hot Temperature Window**

By measuring the voltage between the TS pin and ground, typically determined by a negative temperature coefficient thermistor and an external voltage divider to continuously monitor battery temperature. The device compares this voltage against its internal thresholds to determine if charging is allowed. When the V<sub>TS</sub> rises above the V<sub>LTF</sub> threshold or falls below the V<sub>TCO</sub> threshold, the charging is suspended until the battery temperature is back to the NTC Fault Hysteresis range, V<sub>LTF HYS</sub> and V<sub>HTF</sub>.

Figure 4. TS Resistor Network

When the TS fault occurs, the fault register REG09[2:0] indicates the actual condition on each TS pin and an INT is asserted to the host. When charging is suspended, the fault status will be indicated on STAT pin.

Figure5. TS pin thermistor sense thresholds in Charge Mode

Copyright © ANPEC Electronics Corp. Rev. A.4 - Dec., 2018

Figure6. TS pin thermistor sense thresholds in OTG Mode

For the charge mode case, assuming a 103AT NTC thermistor is used on the battery pack Figure 4, the value RT1 and RT2 can be determined by using the following equation:

$$RT2 = \frac{V_{VREF} \times RTH_{COLD} \times RTH_{HOT} \times \left(\frac{1}{V_{LTF}} - \frac{1}{V_{TCO}}\right)}{RTH_{HOT} \times \left(\frac{V_{VREF}}{V_{TCO}} - 1\right) - RTH_{COLD} \times \left(\frac{V_{VREF}}{V_{LTF}} - 1\right)}$$

$$RT1 = \frac{\frac{V_{VREF}}{V_{LTF}} - 1}{\frac{1}{RT2} + \frac{1}{RTH_{COLD}}}$$

Select 0°C to 45°C range for Li-ion or Li-polymer battery, RTHCOLD = 27.28 k $\Omega$ RTHHOT = 4.911 k $\Omega$ RT1 = 5.52 k $\Omega$ RT2 = 31.23 k $\Omega$

#### **Charging Termination**

The APW7264 terminates a charge cycle when the battery voltage is above recharge threshold, and the current is below programmed termination current. After the charging cycle is complete, the BATFET turns off. The converter keeps running to supply the system. When the device is into supplement mode, the device can turn on BATFET to supply the system. When termination occurs, the status register REG08[5:4] is 11, and an INT is asserted to the host. Termination is temporarily disabled if the charger device is in DPM or thermal regulation. Termination also can be disabled by writing 0 to REG05[7].

#### Termination when REG02[0] = 1

When REG02[0] is "1" to reduce the charging current by 80%, the charging current could be less than the termination current. The charger device termination function should be disabled. When the battery is charged to fully capacity, the host disables charging through CEB pin or REG01[5:4].

#### **Charging Safety Timer**

The APW7264 has safety timer to prevent extended charging cycle due to abnormal battery conditions.

In default mode, the device keeps charging the battery with 8-hour fast charging safety timer (default value). At the end of the 8 hours, the EN\_HIZ (REG00[7]) is set 1 to stops the buck converter operation and the system load is supplied by the battery. The EN\_HIZ bit can be cleared to restart the buck converter.

In host mode, the device keeps charging the battery until the fast charging safety timer expired. The duration of safety timer can be set by the REG05[2:1] bits (default = 8 hours). At the end of safety timer, the EN\_HIZ (REG00[7]) is cleared to signal the buck converter continues to operation to supply system load.

The safety timer is 1 hour when the battery is below BATLOWV threshold. The user can program fast charge safety timer through I<sup>2</sup>C (REG05[2:1]). When safety timer expires, the fault register REG09[5:4] goes 11 and an INT is asserted to the host. The safety timer feature can be disabled via I<sup>2</sup>C (REG05[3]).

The following actions restart the safety timer:

- At the beginning of a new charging cycle

- Toggle the CEB pin High to Low to High (charge enable)

- Write REG01[5:4]= 00 and to 01 (charge enable)

- Write REG05[3]= 0 and to 1 (safety timer enable)

- Write REG01[7] to 1 (software reset)

During input voltage/current regulation or thermal regulation, or when FORCE\_20PCT (REG02[0]) bit is set with  $V_{BAT} > V_{SYS\_MIN}$ , the safety timer counts at half clock rate. For example, if the charger is in input voltage regulation (VINDPM) throughout the whole charging cycle, and the safety time is set to 5 hours, the safety timer will expire in 10 hours. This feature can be disabled by writing 0 to REG07[6].

#### USB Timer when Charging from USB100mA Source

When the device is in default mode from USB100mA source, the charging time is limited by a 45-min max timer. At the end of the timer, the device stops the converter and goes to HIZ.

#### Host Mode and Default Mode

The APW7264 can operate in default mode without host management. In default mode, APW7264 can be used as an autonomous charger without host or with host in sleep mode. When the charger is in default mode, REG09[7] is High. When the charger is in host mode, REG09[7] is Low.

After power-on-reset, the device starts in watchdog timer expiration state, or default mode. And all the registers are in the default settings.

All the device parameters can be programmed by the host. Writing any command to APW7264 transitions the device from default mode to host mode. The host has to reset the watchdog timer by writing 1 to REG01[6] before the watchdog timer expires (REG05[5:4]), or disable watchdog timer by setting REG05[5:4]=11 to keep the device in host mode.

#### Status Outputs (PG, STAT, and INT)

#### Power Good Indicator (PG)

In APW7264 PGB goes Low to indicate a good input source when:

1. VBUS above UVLO

- 2. VBUS above battery (not in sleep mode)

- 3. VBUS below ACOV threshold

#### **Charging Status Indicator (STAT)**

The APW7264 indicates charging state on STAT pin. The STAT pin can drive LED as the application circuit shows.

| Charging State                                                               | STAT     |

|------------------------------------------------------------------------------|----------|

| Charging in progress                                                         | Low      |

| Charging complete                                                            | High     |

| Sleep mode, charge disable                                                   | High     |

| Charge suspend (input over-voltage, TS fault, timer fault, BAT over-voltage) | Blinking |

#### Interrupt to Host (INT)

In some applications, the host does not always monitor the charger operation. The INT notifies the system on the device operation. The following events will generate INT pulse.

USB/adapter source identified (through PSEL with OTG

pin)

- Good input source detected

- Not in sleep mode

- Not in VBUS OV

- Input removed or VBUS OV

- Charge Complete

- FAULT event in REG09

When a fault occurs, the device sends out INT 256µs low pulse width and latches the first fault state in REG09 until the host reads the fault register. Before the host reads REG09, the charger device would not send any INT upon new faults except NTC fault (REG09[2:0]). The NTC fault is not latched and always reports the current thermistor conditions. The host has to read REG09 two times consecutively to read the current fault status. The first reads fault register status from the last INT and the second reads the current fault register status.

### Charge/Buck Mode Protections Input Current Limit on ILIM

For safe operation, theAPW7264 has an additional hardware pin on ILIM to limit maximum input current on ILIM pin. The input maximum current is set by a resistor from ILIM pin to ground as:

### $V_{ILIM} = 20uA \times R_{ILIM}$ $I_{ILIM} = V_{ILIM} \times 2$

For example, if R  $_{_{ILIM}}$  = 50 kΩ, we can get V  $_{_{ILIM}}$  =1V and then the I  $_{_{ILIM}}$  =2A.

The actual input current limit is the lower value between ILIM setting and register setting (REG00[2:0]). For example, if the register setting is 111 for 3A, and ILIM has a 50k $\Omega$  resistor to ground for 2A, the input current limit is 2A.

When  $I_{ILIM}$  pin is flaoting, the input current limit is programmed by the resigister 00[2:0]. When the  $V_{ILIM}$  voltage is below 250mV (typ), the device ignores the  $I_{ILIM}$  pin setting and the input current limit is programmed by the resigister 00[2:0] at the same time.

#### Thermal Regulation and Thermal Shutdown

The APW7264 monitors the internal junction temperature T<sub>J</sub> to avoid overheat the chip and limits the IC surface temperature. When the internal junction temperature exceeds the programmed thermal regulation threshold (REG06[1:0]), the device starts to decrease the charge current. The wide thermal regulation range from 60°C to 120°C allows the user to optimize the system thermal performance.

During thermal regulation, the termination is disabled, the safety timer runs at half the clock rate, and the status register REG08[1] goes high.

The device also has thermal shutdown protection to turn off the converter. When the device triggers the thermal shutdown threshold, the fault register REG09[5:4] is 10 and an INT is asserted to the host.

#### Input Over-Voltage (ACOV)

If VBUS voltage exceeds 6.2V to trigger the input overvoltage threshold (ACOV), the device stops switching immediately. During input over voltage (ACOV), the fault register REG09[5:4] will be set to 01. An INT is asserted to the host.

#### System Over-Voltage Protection (SYSOVP)

The APW7264 always monitors the voltage at SYS terminal. When system over-voltage is detected, the converter is stopped to protect components connected to SYS from high voltage damage.

#### Voltage and Current Monitoring in Boost Mode

The APW7264 closely monitors the VBUS voltage, as well as HSFET and LSFET current to ensure safe boost mode operation.

#### **VBUS Over-Voltage Protection**

The boost mode regulated output is 5V. During boost mode, the VBUS voltage will rise above regulation target when an adapter plugs in. Once the VBUS voltage exceeds 6V, the device stops switching and the device exits boost mode. The OTG Enable bit REG01[5] is cleared to 0 simultaneously. The fault register REG09[6] is set high to indicate fault in boost operation. An INT is asserted to the host.

#### Copyright © ANPEC Electronics Corp. Rev. A.4 - Dec., 2018

#### **VBUS Over-Current Protection**

When the VBUS terminal load is bigger than the register BOOST\_LIM setting value, the device will operate in hiccup mode for protection. While in hiccup mode cycle, the device turns off RBFET for  $t_{OTG_OCP_OFF}$  (32ms typical) and turns on RBFET for  $t_{OTG_OCP_OFF}$  (32ms typical) to attempt to restart. If the over-current condition is removed, the RBFET is continuous turned on and the VBUS OTG output will operate normally. When over-current condition still exists, the device will repeat the hiccup cycle until over-current condition is removed. When over-current condition is detected, the fault register bit OTG\_FAULT (REG09[6]) is set high to indicate fault in boost operation. An INT is asserted to the host.

#### **Battery Protection**

#### **Battery Over-Current Protection (BATOVP)**

When the battery voltage is at 4% above the battery regulation voltage, the APW7264 immediately disables charge opreration. The fault register REG09[3] goes high and an INT is asserted to the host.

#### **Charging During Battery Short Protection**

If the battery voltage falls below 2V, the charge current is reduced to 100mA for battery safety.

## **Application Information**

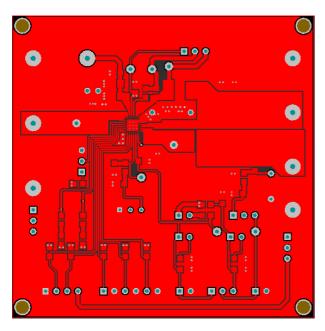

#### Layout Consideration

In any high switching frequency converter, a correct layout is important to ensure proper operation of the regulator. With power devices switching at higher frequency, the resulting current transient will cause voltage spike across the interconnecting impedance and parasitic circuit elements. As an example, consider the turn-off transition of the PWM MOSFET. Before turn-off condition, the MOSFET is carrying the full load current. During turn-off, current stops flowing in the MOSFET and is freewheeling by the lower MOSFET and parasitic diode. Any parasitic inductance of the circuit generates a large voltage spike during the switching interval. In general, using short and wide printed circuit traces should minimize interconnecting impedances and the magnitude of voltage spike. Below are Layout consideration checklist, recommended layout Schematic diagram and demoboard layout for your reference:

Keep the switching nodes (BTST and SW) away from sensitive small signal nodes since these nodes are fast moving signals. Therefore, keep traces to these nodes as short as possible and there should be no other weak signal traces in parallel with theses traces on any layer.

The large layout plane between the drain of the MOSFETs (VBUS, PMID and SW nodes) can get better heat sinking.

The high-current charge paths into VBUS, PMID and from the SW pins must be sized appropriately for the maximum charge current in order to avoid voltage drops

in these traces. - Place all decoupling capacitors close to their respective IC pins and close to PGND (do not place components such that routing interrupts power stage currents). All small control signals should be routed away from the high current paths.

- The output bulk capacitors should be close to the loads. The input capacitor's ground should be close to the grounds of the output capacitors.

- In order to better anti-interference ability, the middle layer of the board covered with GND is recommended.

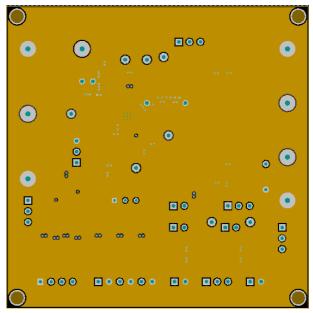

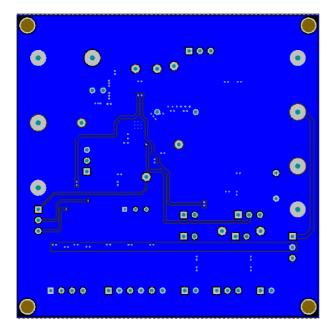

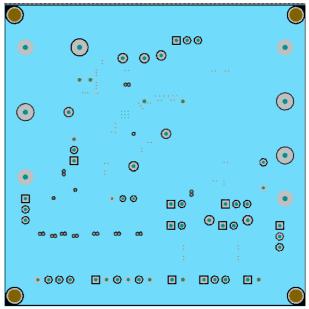

Figure 5. Layout Circuit Abridged General View

#### Minimum Footprint

Figure 6. Recommended Minimum Footprint

# APW7264

## **Application Information (Cont.)**

**Evalution Board**

TOPLAYER

MIDLAYER1

#### BOTTOMLAYER

MIDLAYER2

# APW7264