3MHz Synchronous Switch-Mode Battery Charger with Full USB Compliance and USB-OTG Boost Regulator

### Features

- · Charge Faster Than Linear Charger

- 3MHz with Wide Duty Cycle Synchronous Switch-Mode Charger with 1.5A Integrated N-MOSFETs

- 4V-6V Input Operating Range

- 20V Absolute Maximum Input Voltage

- · Safety

- -Reverse leakage protection to prevent battery drainage

- -Thermal regulation and protection

- -Input/output over-voltage protection

- -Cycle-by-cycle current limit

- · Accuracy

- -<u>+</u>1% charge voltage regulation (0 to 85°C)

-+5% charge current regulation

- -<u>+</u>5% input current regulation (100mA and 500mA)

- Built-In Input Current Sensing and Limiting

- Automatic Charging

- Programmable Through High-Speed I<sup>2</sup>C Interface (3.4Mb/s)

- -Input Current Limit

- -Fast-Charge and Termination Current

- -Charge Regulation Voltage

- -VIN DPM Threshold

- -Termination Enable/Disable

- -OTG Enable/Disable

- -Reset All Parameter Control

- -Safety Timer with Reset Control

- 5V, 500mA Boost Mode for USB OTG for 2.5V to 4.

5V Battery Input

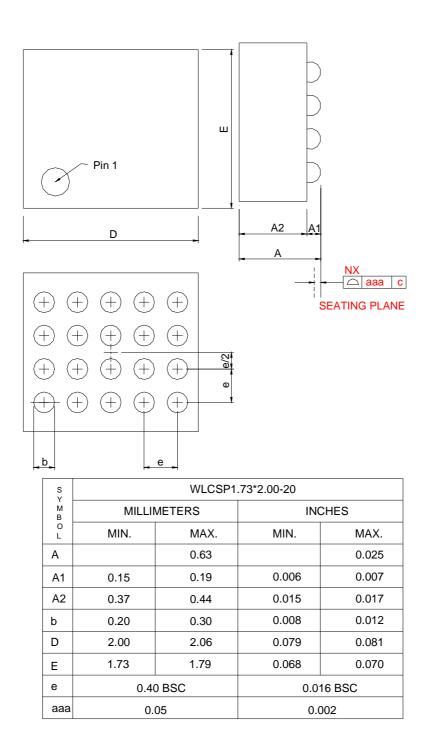

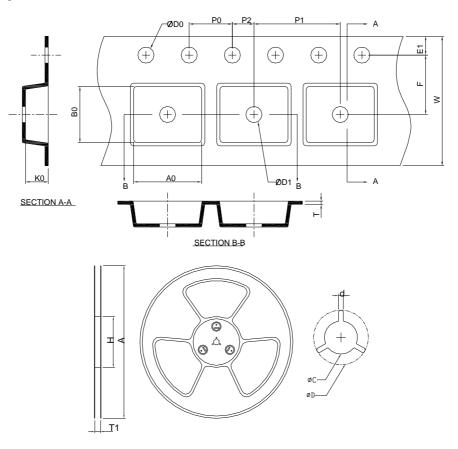

- Available in 1.73mmx2.0mm WLCSP-20 Package

### **General Description**

The APW7261 combine switch-mode battery charger and a boost regulator with fixed 3MHz switching frequency, which drives two integrated N-channel power MOSFETs. In battery charging, the high-efficiency step-down DC/DC converter is capable of delivering 1.5A output current over a wide input voltage range from 4V to 6V for APW7261, the step-down DC/DC converter is ideally suited for portable electronic devices that are powered from 1-cell Li-ion battery. The Charging parameters and operating modes can be programmed through an I<sup>2</sup>C interface. The APW7261 has high accuracy regulation of input current, charge current and charge voltage. It equipped with charge termination, and charge status monitoring for battery detection.

The APW7261 charge the battery in three phases: conditioning, constant current and constant voltage. The APW7261 features Dynamic Power Management (DPM) mode to accomplish input power limiting. The input current is limited to the value set by the I<sup>2</sup>C host. This feature reduces battery charge current when the input power limit is reached to avoid overloading the AC adapter when supplying the load and the battery charger simultaneously. The charge termination is based on battery voltage, a programmed minimum current level and charge current termination bit set by the I<sup>2</sup>C host.

If the battery voltage falls below an internal threshold, the APW7261 automatically restarts the charge cycle, and when the input voltage falls below the battery voltage, it will enter a low-quiescent current sleep mode. The APW7261 supports the thermal regulation and over temperature protection to maintain the junction temperature of 120°C by reducing charge current.

The APW7261 can operate as a boost regulator. To support USB OTG device, APW7261 can provide VBUS (5.05V) by boosting the battery voltage.

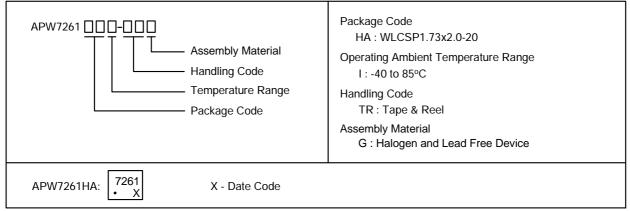

The APW7261 is available in1.73mmx2.0mm WLCSP-20 package.

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

### **Applications**

- · Cell Phones, Smart Phones and PDAs

- · Tablet PC

- · Portable Media Players, Handheld Device

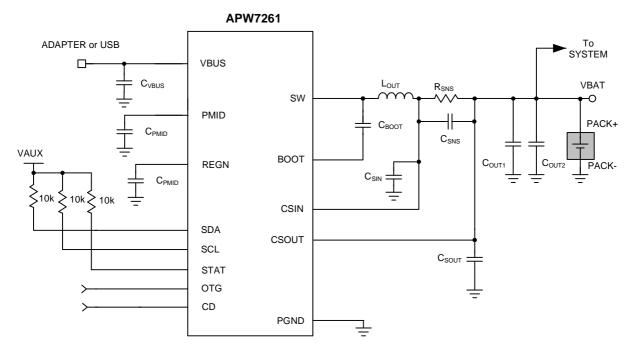

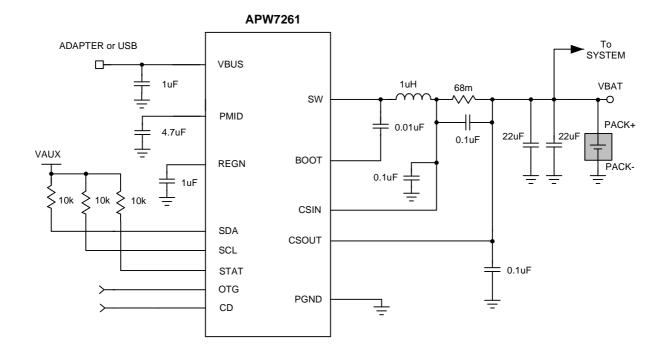

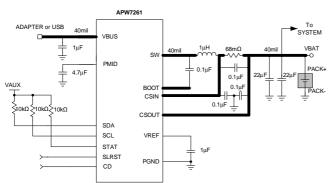

# **Simplified Application Circuit**

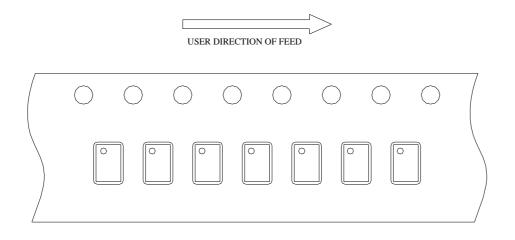

### Ordering and Marking Information

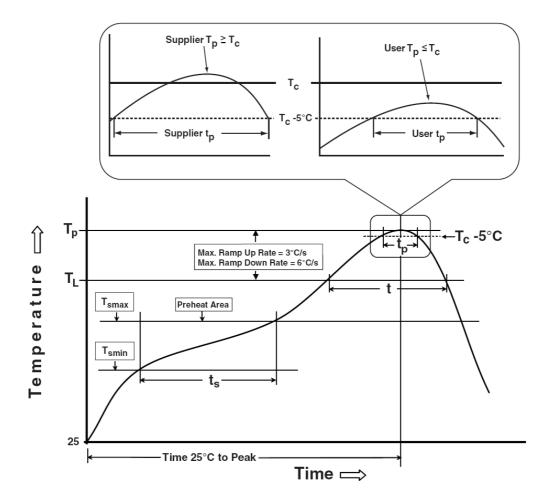

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or CI does not exceed 900ppm by weight in homogeneous material and total of Br and CI does not exceed 1500ppm by weight).

Copyright © ANPEC Electronics Corp. Rev. A.1 - Jun., 2016

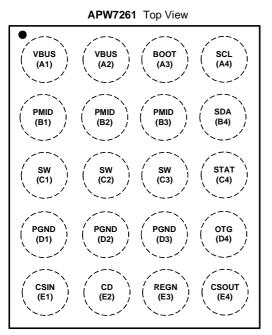

### **Pin Configuration**

1.73X2.0mm 20-pin WLCSP-20

## Absolute Maximum Ratings (Note 1,2)

| Symbol            | Parameter                                               | Rating     | Unit |

|-------------------|---------------------------------------------------------|------------|------|

|                   | VBUS, PMID and STAT to PGND Voltage                     | -0.3 to 20 | V    |

| V <sub>I/O</sub>  | BOOT and SW to PGND Voltage                             | -0.3 to 20 | V    |

|                   | SCL, SDA, OTG, REGN, CSIN, CSOUT and CD to PGND Voltage | -0.3 to 7  | V    |

| V <sub>BOOT</sub> | BOOT Supply Voltage (BOOT to SW)                        | -0.3 ~ 7   | V    |

| TJ                | Maximum Junction Temperature                            | 150        | °C   |

| T <sub>STG</sub>  | Storage Temperature                                     | -65 to 150 | °C   |

| T <sub>SDR</sub>  | Maximum Lead Soldering Temperature (10 Seconds)         | 260        | °C   |

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

Note 2: The device is ESD sensitive. Handling precautions are recommended.

## Thermal Characteristics (Note 3)

| Sym bol       | Parameter                                  | Typical Value | Unit |

|---------------|--------------------------------------------|---------------|------|

| $\theta_{JA}$ | Junction-to-Ambient Resistance in free air | 85            | °C/W |

| θJC           | Junction-to-Case Resistance in free air    | 25            | °C/W |

Note 3:  $\theta_{JA}$  is measured with the component mounted on a high effective the thermal conductivity test board in free air.

## Recommended Operating Conditions (Note 4)

| Symbol           | Parameter                                | Range       | Unit |

|------------------|------------------------------------------|-------------|------|

| V <sub>BUS</sub> | Supply Voltage (VBUS to GND)             | 4 to 6      | V    |

| V <sub>OUT</sub> | Converter Output Voltage                 | 3.5 to 4.44 | V    |

| ו <sub>סטד</sub> | Output Current (R <sub>SNS</sub> =68m Ω) | 0.55~1.55   | А    |

| T <sub>A</sub>   | Ambient Temperature                      | -40 to 85   | °C   |

| TJ               | Junction Temperature                     | -40 to 125  | °C   |

Note 4: Refer to the typical application circuit.

### **Electrical Characteristics**

Unless otherwise specified, these specifications apply over V<sub>BUS</sub>=5V, CD=0, HZ\_MODE=0, OPA\_MODE=0 and T<sub>A</sub>= -40 to 85 °C. Typical values are at T<sub>A</sub>=25°C.

| 0                      | De re meter                                                                                                                 | T of O a life of                                                                                                                     |      | APW7261 |      |      |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|------|

| Symbol                 | Pa ra mete r                                                                                                                | Test Conditions                                                                                                                      | Min  | Тур     | Max  | Unit |

| NPUTCURREN             | ١T                                                                                                                          |                                                                                                                                      |      |         |      |      |

| I <sub>VBUS</sub>      | VBUS supply current control                                                                                                 | V <sub>BUS</sub> > V <sub>BUS(min)</sub> , PWM switching                                                                             | -    | 10      | -    | mA   |

|                        |                                                                                                                             | $V_{BUS} > V_{BUS(min)}$ , PWM no switching                                                                                          | -    | -       | 5    | mA   |

|                        |                                                                                                                             | 0°C < T」 < 85°C, CD=1 or HZ_MODE=1                                                                                                   | -    | 140     | 260  | μA   |

| I <sub>LKG</sub>       |                                                                                                                             | 0°C < T <sub>J</sub> < 85°C, V <sub>CSOUT</sub> =4.2V, High<br>Impedance Mode, V <sub>BUS</sub> =0V                                  | -    | 0.2     | 5    | μA   |

|                        | Impedance Mode, (CSIN, CSOUT,                                                                                               | 0°C < T <sub>J</sub> < 85°C, V <sub>CSOUT</sub> =4.2V, High<br>Impedance Mode, SCL, SDA, OTG=0V or<br>1.8V                           | -    | 23      | 50   | μA   |

| OLTAGE REG             | ULATION                                                                                                                     |                                                                                                                                      |      |         |      |      |

| V <sub>OREG</sub>      | Output Regulation voltage programmable range                                                                                | Operating in voltage regulation                                                                                                      | 3.5  | -       | 4.44 | V    |

|                        |                                                                                                                             | $T_A = 25^{\circ}C$                                                                                                                  | -0.5 | -       | 0.5  |      |

|                        | Voltage regulation accuracy $T_A = -40 \sim 85^{\circ}C$                                                                    |                                                                                                                                      | -1   | -       | 1    | %    |

| CURRENT REG            | ULATION (FAST CHARGE)                                                                                                       |                                                                                                                                      |      |         |      |      |

| I <sub>O(CHARGE)</sub> | Output charge current programmable range                                                                                    | V <sub>LOWV</sub> ≦V <sub>CSOUT</sub> ≺V <sub>OREG</sub> , V <sub>BUS</sub> >V <sub>SLP</sub> ,<br>R <sub>SNS</sub> =68mΩ, LOW_CHG=0 | 550  | -       | 1500 | mA   |

|                        | Low charge current                                                                                                          | V <sub>LOWV</sub> ≦V <sub>CSOUT</sub> <v<sub>OREG, V<sub>BUS</sub>&gt;V<sub>SLP</sub>,<br/>R<sub>SNS</sub>=68mΩ, LOW_CHG=1</v<sub>   | -    | 325     | 350  | mA   |

|                        | Charge Current Accuracy Across                                                                                              | 20mV < V <sub>IREG</sub> < 40mV                                                                                                      | -8   | -       | 2    | %    |

|                        | Rans                                                                                                                        | 40mV < V <sub>IREG</sub>                                                                                                             | -6   | -       | 0    | %    |

|                        | Regulation accuracy of the voltage                                                                                          | $37.4mV \leq V_{IREG} < 44.2mV$                                                                                                      | -3.5 | -       | 3.5  |      |

|                        | across R <sub>SNS</sub> (for charge current<br>regulation)<br>V <sub>IREG</sub> = I <sub>O(CHARGE)</sub> x R <sub>SNS</sub> | 44.2mV $\leq$ V <sub>IREG</sub>                                                                                                      | -3   | -       | 3    | %    |

| OW BATTERY             |                                                                                                                             | -                                                                                                                                    |      | -       |      |      |

| VLOWV                  | Low battery voltage threshold                                                                                               |                                                                                                                                      | -    | -       | 3.7  | V    |

## **Electrical Characteristics**

Unless otherwise specified, these specifications apply over V<sub>BUS</sub>=5V, CD=0, HZ\_MODE=0, OPA\_MODE=0 and T<sub>A</sub>= -40 to 85 °C. Typical values are at T<sub>A</sub>=25°C.

| Symbol                | Pa ra mete r                                                    | Test Conditions                                                                 |                                                                       | Α   | PW72 | 61   |      |  |

|-----------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|------|------|------|--|

| Symbol                | Falameter                                                       | Test Conditions                                                                 |                                                                       |     | Тур  | Max  | Unit |  |

| Dand OTG PI           | N LOGIC LEVEL                                                   |                                                                                 |                                                                       |     |      |      |      |  |

| V <sub>IL</sub>       | Input low threshold level                                       |                                                                                 |                                                                       | -   | -    | 0.4  | V    |  |

| V <sub>IH</sub>       | Input high threshold level                                      |                                                                                 |                                                                       | 1.5 | -    | -    | V    |  |

| l <sub>bias</sub>     | Input bias current                                              | Voltage on control pin                                                          | is 5V                                                                 | -   | -    | 1    | μA   |  |

| HARGE TERM            | IINATION DETECTION                                              |                                                                                 |                                                                       |     |      |      |      |  |

| I <sub>TERM</sub>     | Termination charge current programmable range                   | V <sub>CSOUT</sub> >V <sub>OREG</sub> -V <sub>REGH</sub> , V                    | $V_{\text{BUS}}$ > $V_{\text{SLP}}$ , $R_{\text{SNS}}$ =68 m $\Omega$ | 50  | -    | 400  | mA   |  |

|                       | Deglitch time for charge termination                            | Both rising and fallin<br>t <sub>FAL</sub> L=100ns                              | g, 2mV overdrive, $t_{RISE}$ ,                                        | -   | 30   | -    | ms   |  |

|                       | Regulation accuracy for                                         | $3.4mV \leq V_{IREG_{TERM}} \leq 6$                                             | S.8mV                                                                 | -25 | -    | 25   |      |  |

|                       | termination current across RSNS                                 | $6.8mV \le V_{IREG_{TERM}} \le 1$                                               | 17mV                                                                  | -25 | -    | 25   | %    |  |

|                       | $V_{\text{IREG_TERM}} = I_{\text{OTERM}} \times R_{\text{SNS}}$ | 17mV≦V <sub>IREG_TERM</sub> ≦2                                                  | 7.2mV                                                                 | -5  | -    | 5    |      |  |

| NPUT BASED            | DYNAMIC POWER MANAGEMENT                                        | •                                                                               |                                                                       |     | -    |      |      |  |

| V <sub>IN_DPM</sub>   | In put voltage DPM threshold programmable range                 |                                                                                 |                                                                       | 4.2 | -    | 4.76 | V    |  |

|                       | VIN DPM threshold accuracy                                      |                                                                                 |                                                                       | -3  | -    | 3    | %    |  |

|                       |                                                                 |                                                                                 |                                                                       |     |      |      |      |  |

|                       |                                                                 | I <sub>IN</sub> =100mA                                                          | T <sub>A</sub> =25°C                                                  | 88  | 93   | 98   |      |  |

| I <sub>IN_LIMIT</sub> | In put current lim iting thre shold                             | I <sub>IN</sub> =500mA                                                          | T <sub>A</sub> =25°C                                                  | 450 | 475  | 500  | − mA |  |

| REF BIAS REG          | GULATOR                                                         | 4                                                                               |                                                                       |     | 1    |      |      |  |

| V <sub>REGN</sub>     | Input bias regulator voltage                                    | $V_{BUS}$ >V <sub>IN(min)</sub> or V <sub>CSOUT</sub><br>C <sub>REGN</sub> =1µF | $>V_{BUS(min)}, I_{REGN}=1mA,$                                        | -   | -    | 6.5  | V    |  |

|                       | V <sub>REGN</sub> output short current limit                    |                                                                                 |                                                                       | -   | 30   | -    | mA   |  |

| ATTERY RECI           | HARGE THRESHOLD                                                 |                                                                                 |                                                                       |     |      |      |      |  |

| V <sub>RCH</sub>      | Recharge threshold voltage                                      | Below V <sub>OREG</sub>                                                         |                                                                       | -   | 120  | -    | mV   |  |

|                       | Deglitch time                                                   | V <sub>CSOUT</sub> decreasing<br>t <sub>FALL</sub> =100ns, 10m V o v            | · · · · · · · · · · · · · · · · · · ·                                 | -   | 130  | -    | ms   |  |

| TAT OUTPUT            |                                                                 |                                                                                 |                                                                       |     |      |      |      |  |

|                       | Low-level output saturation voltage, STAT pin                   | I <sub>0</sub> =10mA, sink curren                                               | t                                                                     | -   | -    | 0.55 | V    |  |

| Vol(stat)             | High-level leakage current for STAT                             | Voltage on STAT pin is 5V                                                       |                                                                       | -   | -    | 1    | μA   |  |

| C BUS LOGIC           | LEVELS AND TIMING CHARACTER                                     | RISTIC                                                                          |                                                                       |     | -    |      |      |  |

| V <sub>OL</sub>       | Output low threshold level                                      | I <sub>o</sub> =10mA, sink curren                                               | t                                                                     | -   | -    | 0.4  | V    |  |

| V <sub>IL</sub>       | Input low threshold level                                       | V <sub>PULL UP</sub> =1.8V, SDA and SCL                                         |                                                                       | -   |      | 0.4  | V    |  |

| V <sub>IH</sub>       | Input high threshold level                                      | V <sub>PULL UP</sub> =1.8V, SDA a                                               |                                                                       | 1.2 | -    | -    | V    |  |

| IBIAS                 | Input bias current                                              | V <sub>PULL UP</sub> =1.8V, SDA a                                               |                                                                       | -   | -    | 1    | μA   |  |

| f <sub>SCL</sub>      | SCL clock frequency                                             | V <sub>PULL UP</sub> =1.8V, SDA a                                               |                                                                       | -   | L .  | 3.4  | MH   |  |

Copyright  $\circledcirc$  ANPEC Electronics Corp. Rev. A.1 - Jun., 2016

www.anpec.com.tw

## **Electrical Characteristics**

Unless otherwise specified, these specifications apply over V<sub>BUS</sub>=5V, CD=0, HZ\_MODE=0, OPA\_MODE=0 and T<sub>A</sub>= -40 to 85 °C. Typical values are at T<sub>A</sub>=25°C.

| Cumhal                        | Parameter                                                                                                                                      |                                                                                        |     | APW7261 |     |      |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|---------|-----|------|

| Symbol                        | Parameter Test Conditions                                                                                                                      |                                                                                        | Min | Тур     | Max | Unit |

| BATTERY DE                    | TECTION (In Termination)                                                                                                                       |                                                                                        |     |         |     |      |

| I                             | Battery detection current before                                                                                                               | Begins after termination detected,                                                     |     | -0.8    |     | mA   |

| DETECT                        | $\label{eq:local_local_relation} I_{\text{DETECT}}  \text{charge done (sink current)} \qquad \qquad V_{\text{CSOUT}} \!\leq\! V_{\text{OREG}}$ |                                                                                        | -   | -0.0    | -   | IIIA |

| t <sub>DETECT</sub>           | Battery detection time                                                                                                                         |                                                                                        | -   | 262     | -   | ms   |

| SLEEP COMP                    | ARATOR                                                                                                                                         |                                                                                        |     | _       |     |      |

| $V_{\text{SLP}}$              | SLEEP mode entry threshold,<br>V <sub>BUS</sub> -V <sub>CSOUT</sub>                                                                            | $2.3V \leq V_{CSOUT} \leq V_{OREG}, V_{BUS}$ falling                                   | 0   | 40      | 100 | mV   |

| $V_{\text{SLP}\_\text{EXIT}}$ | Sleep mode exit hysteresis                                                                                                                     | $2.3V \leq V_{CSOUT} \leq V_{OREG}$                                                    | 140 | 200     | 260 | mV   |

|                               | Deglitch time for V <sub>BUS</sub> rising above<br>V <sub>SLP</sub> +V <sub>SLP_EXIT</sub>                                                     | Rising voltage, 2mV overdrive, t <sub>RISE</sub> =100ns                                | -   | 30      | -   | ms   |

|                               | AGE LOCKOUT (UVLO)                                                                                                                             |                                                                                        |     |         |     |      |

| UVLO                          | IC active threshold voltage                                                                                                                    | V <sub>BUS</sub> rising, Exit UVLO                                                     | 3.6 | 3.8     | 4   | V    |

| UVLO_HYS                      | IC active hysteresis                                                                                                                           | V <sub>BUS</sub> falling below UVLO, Enter UVLO                                        | -   | 150     | -   | mV   |

| PWM                           | •                                                                                                                                              |                                                                                        |     |         | •   | 1    |

|                               | Internal top reverse blocking MOSFET on-resistance                                                                                             | I <sub>IN_LIMIT</sub> =500mA, Measured from VBUS to PMID                               | -   | 90      | 135 |      |

|                               | Internal top N-Channel Switching<br>MOSFET on-resistance                                                                                       | Measured from PMID to SW, $V_{BOOT}$ - $V_{SW}$ =4V                                    | -   | 130     | 225 | mΩ   |

|                               | Internal bottom N-Channel MOSFET<br>on-resistance                                                                                              | Measured from SW to PGND                                                               | -   | 120     | 180 |      |

| f <sub>OSC</sub>              | Oscillator frequency                                                                                                                           |                                                                                        | 2.7 | 3       | 3.3 | MHz  |

| CHARGE MO                     | DE PROTECTION                                                                                                                                  |                                                                                        |     |         |     | 1    |

| V <sub>OVP IN USB</sub>       | Input VBUS OVP threshold voltage                                                                                                               | V <sub>BUS</sub> threshold to turn off converter during charge V <sub>OVP_IN_USB</sub> | 6.3 | 6.5     | 6.7 | V    |

|                               | V <sub>OVP_IN_USB</sub> hysteresis                                                                                                             | VBUS falling from a bove V <sub>OVP_ℕ_USB</sub>                                        | -   | 170     | -   | mV   |

| V <sub>OVP</sub>              | Output OVP threshold voltage                                                                                                                   | $V_{\text{CSOUT}}$ threshold over $V_{\text{OREG}}$ to turn off charger during charge  | 110 | 117     | 121 | %    |

|                               | V <sub>OVP</sub> hysteresis                                                                                                                    | Lower limit for $V_{CSOUT}$ falling from above $V_{OVP}$                               | -   | 11      | -   | %    |

| I <sub>ILIMT</sub>            | Cycle-by-cycle current limit for<br>charge                                                                                                     | Charge mode operation                                                                  | 3   | 4       | 5   | A    |

|                               | Trickle to fast charge threshold                                                                                                               | V <sub>CSOUT</sub> rising                                                              | 1.9 | 2.1     | 2.3 | V    |

| VSHORT                        | V <sub>SHORT</sub> hysteresis                                                                                                                  | V <sub>CSOUT</sub> falling below V <sub>SHORT</sub>                                    | -   | 100     | -   | mV   |

## **Electrical Characteristics**

Unless otherwise specified, these specifications apply over V<sub>BUS</sub>=5V, CD=0, HZ\_MODE=0, OPA\_MODE=0 and T<sub>A</sub>= -40 to 85 °C. Typical values are at T<sub>A</sub>=25°C.

| Council of            |                                                                          |                                                              | APW7261 |      |      |      |  |

|-----------------------|--------------------------------------------------------------------------|--------------------------------------------------------------|---------|------|------|------|--|

| Symbol                | Parameter Test Conditions                                                |                                                              | Min     | Тур  | Max  | Unit |  |

| ARGE MODE             | PROTECTION                                                               |                                                              |         |      |      |      |  |

| I <sub>SHORT</sub>    | Trickle charge charging current                                          | $V_{CSOUT} \leq V_{SHORT}$                                   | 25      | 35   | 45   | mA   |  |

| OST MODE              | OPERATION FOR VBUS (OPA_MOD                                              | E=1, HZ_MODE=0)                                              |         |      |      |      |  |

| $V_{\text{BUS}\_B}$   | Boost output voltage (to VBUS pin)                                       | 2.5V <v<sub>CSOUT&lt;4.5V</v<sub>                            | 4.9     | 5.05 | 5.2  | V    |  |

|                       | Boost output voltage accuracy                                            | Including line and load regulation                           | -3      | -    | 3    | %    |  |

| I <sub>BO</sub>       | Maximum output current for boost                                         | V <sub>BUS_B</sub> =5.05V, 2.5V <v<sub>CSOUT&lt;4.5V</v<sub> | 500     | -    | -    | m/   |  |

| I <sub>BLIMIT</sub>   | Cycle by cycle current                                                   | V <sub>BUS_B</sub> =5.05V, 2.5V <v<sub>CSOUT&lt;4.5V</v<sub> | -       | 1.59 | -    | A    |  |

| VBUSOVP               | Overvoltage protection threshold fo boost (VBUS pin)                     | Threshold over VBUS to turn off converter during boost       | 5.8     | 6    | 6.2  | V    |  |

|                       | V <sub>BUSOVP</sub> hysteresis                                           | V <sub>BUS</sub> falling from above V <sub>BUSOVP</sub>      | -       | 162  | -    | ۳۱   |  |

| VBATMAX               | Maximum battery voltage for boost<br>(CSOUT pin)                         | V <sub>CSOUT</sub> rising edge during boost                  | 4.75    | 4.9  | 5.05 | V    |  |

|                       | V <sub>BATMAX</sub> hysteresis                                           | V <sub>CSOUT</sub> falling from above V <sub>BATMAX</sub>    | -       | 200  | -    | m\   |  |

| M                     | Minimum battery voltage for boost                                        | During boosting                                              | -       | 2.5  | -    | V    |  |

| VBATMIN               | (CSOUT pin)                                                              | Before boost starts                                          | -       | 2.9  | 3.2  | V    |  |

|                       | Boost output resistance at<br>high-impedance mode (From<br>VBUS to PGND) | CD=1 or HZ_MODE=1                                            | 220     | -    | -    | k۵   |  |

| OTECTION              |                                                                          |                                                              |         |      |      |      |  |

| T <sub>SHUTDOWN</sub> | Thermal trip                                                             |                                                              | -       | 150  | -    |      |  |

|                       | Thermal hysteresis                                                       |                                                              | -       | 25   | -    | °C   |  |

| $T_{CF}$              | Thermal regulation threshold                                             | Charge current begins to reduce                              | -       | 120  | -    |      |  |

| t <sub>4 OM</sub>     | 40 minute timer                                                          | 40 minute mode                                               | 35      | 40   | 45   | Mi   |  |

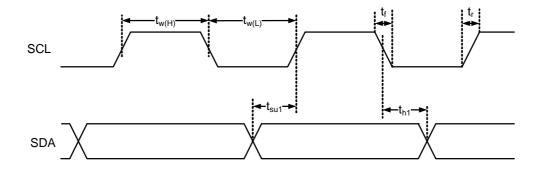

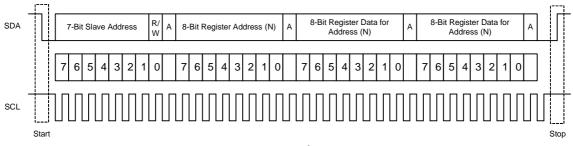

# I<sup>2</sup>C Serial Control Port Operation

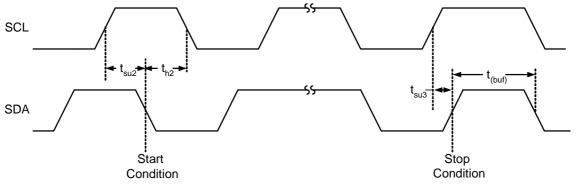

Timing characteristics for I<sup>2</sup>C Interface signals over recommended operating conditions (unless otherwise noted)

| Cumb al              | Beremeter                                         | Test Conditions        |     | AP W7261 |      |      |

|----------------------|---------------------------------------------------|------------------------|-----|----------|------|------|

| Symbol               | Parameter                                         | ameter Test Conditions |     | Тур.     | Max. | Unit |

| f <sub>SCL</sub>     | Frequency, SCL                                    | No Wait States         | -   | -        | 400  | kHz  |

| t <sub>W(H)</sub>    | Pulse Duration, SCL High                          |                        | 0.6 | -        | -    |      |

| t <sub>W(L)</sub>    | Pulse Duration, SCL Low                           |                        | 1.3 | -        | -    | μs   |

| tr                   | Rise Time, SCL and SDA                            |                        | -   | -        | 300  | ns   |

| t <sub>f</sub>       | Fall Time, SCL and SDA                            |                        | -   | -        | 300  | ns   |

| t <sub>setup1</sub>  | Setup Time, SCL to SDA                            |                        | 100 | -        | -    | ns   |

| t <sub>h old 1</sub> | Hold Time, SCL to SDA                             |                        | 0   | -        | -    | ns   |

| t <sub>(buf)</sub>   | Bus Free Time Between Stop<br>and Start Condition |                        | 1.3 | -        | -    |      |

| t <sub>setup2</sub>  | Setup Time, SCL to Start<br>Condition             |                        | 0.6 | -        | -    |      |

| t <sub>h old 2</sub> | Hold Time, Start condition to SCL                 |                        | 0.6 | -        | -    | μs   |

| t <sub>setup3</sub>  | Setup Time, SCL to Stop<br>Condition              |                        | 0.6 | -        | -    |      |

| CL                   | Load Capacitance for Each<br>Bus Line             |                        | -   | -        | 400  | pF   |

Figure1. SCL and SDA Timing

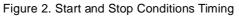

## **Reset Timing**

Control signal parameters over recommended operating conditions (unless otherwise noted). Please refer to "Recommended Use Model" section on usage of all terminals.

| Symbol                     | Parameter                        | Test Conditions APW 7261 |      | APW 7261 |      | Unit |

|----------------------------|----------------------------------|--------------------------|------|----------|------|------|

| Symbol                     | Faidilielei                      | Test Conditions          | Min. | Тур.     | Max. | onn  |

| t <sub>p(/RST)</sub>       | Pulse Duration, RESET<br>Active. | No Load                  | 1 00 | -        | -    | μs   |

| t <sub>d (I2C_Ready)</sub> | Time to Enable I <sup>2</sup> C  |                          | -    | -        | 13.5 | ms   |

Figure 3. Reset Timing

# **Pin Description**

| PIN        | NAME  | Description                                                                                                                                                                                                                                                                                  |

|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2     | VBUS  | Charge Input Voltage.                                                                                                                                                                                                                                                                        |

| A3         | BOOT  | Supply Input for the Internal high-side gate driver and an internal level-shift circuit. Connect to an external<br>ceramic capacitor and internal diode to create a boosted voltage suitable to drive a logic-level N-channel<br>MOS FET.                                                    |

| A4         | SCL   | I <sup>2</sup> C Interface Clock. This pin should not be left floating.                                                                                                                                                                                                                      |

| B1, B2, B3 | PMID  | Converter Input Voltage. Connect at least $4.7\mu F$ ceramic capacitor from PVCC to PGND and place it as close as possible to IC.                                                                                                                                                            |

| B4         | SDA   | I <sup>2</sup> C Interface Data. This pin should not be left floating.                                                                                                                                                                                                                       |

| C1, C2, C3 | SW    | Junction point of the Internal high-side MOSFET Source, output filter inductor and internal the low-side MOSFET Drain. Connect the $0.01\mu$ F bootstrap capacitor from SW to BOOT.                                                                                                          |

| C4         | STAT  | STAT is an open drain output used to indicate the status of the various charger operations. Low when charge in progress. STAT can be used to drive a LED or communicate with a host processor.                                                                                               |

| D1, D2, D3 | PGND  | Power ground. Ground connection for high current power converter node. This pin is used as sink for internal low-side gate drivers.                                                                                                                                                          |

| D4         | OTG   | Boost Mode Enable Control Pin. When OTG actives, the device operates in boost mode.                                                                                                                                                                                                          |

| E1         | CSIN  | Positive Input of current sensing Amplifier for charge terminal. A 0.1µF ceramic capacitor is placed from CSIN to CSOUT to provide differential-mode filtering. An optional 0.1µF ceramic capacitor is placed from CSIN pin to PGND for common-mode filtering.                               |

| E2         | CD    | Charge Disable. CD=Low, charge is enabled, CD=High, charge is disabled.                                                                                                                                                                                                                      |

| E3         | REGN  | Supply Voltage. This pin provides bias supply, low-side gate drivers and the bootstrap circuit for high-side drivers. Ensure that this pin is bypassed by a $1\mu$ F ceramic capacitor next to the pin.                                                                                      |

| E4         | CSOUT | Battery Output and Negative Input of current sensing Amplifier for charge terminal. A $0.1\mu$ F ceramic capacitor is placed from CSOUT to CSIN to provide differential-mode filtering. An optional $0.1\mu$ F ceramic capacitor is placed from CSOUT pin to PGND for common-mode filtering. |

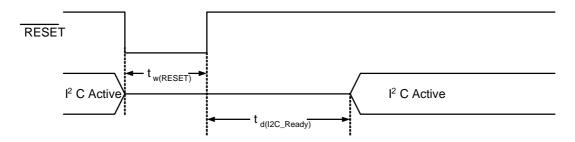

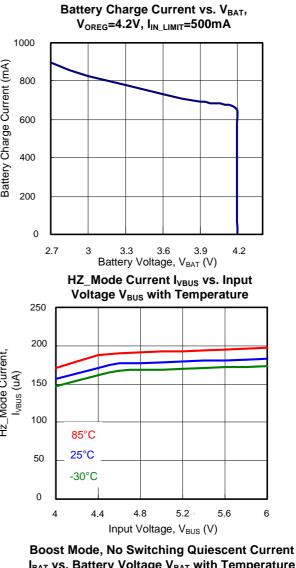

### **Typical Operating Characteristics**

Copyright © ANPEC Electronics Corp. Rev. A.1 - Jun., 2016

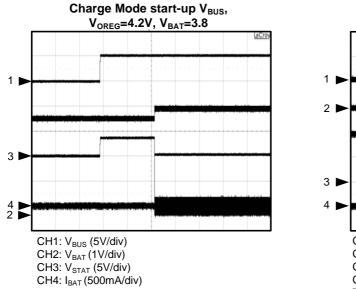

IBAT vs. Battery Voltage VBAT with Temperature

# **Typical Operating Characteristics**

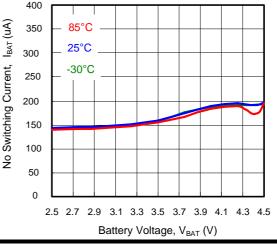

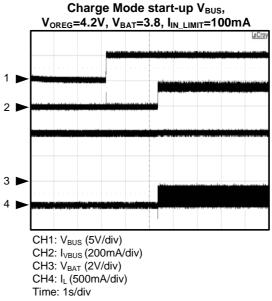

## **Operating Waveforms**

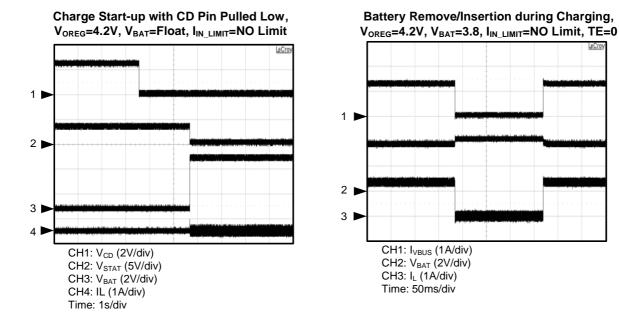

Time: 1s/div

V<sub>OREG</sub>=4.2V, V<sub>BAT</sub>=3.8, I<sub>IN\_LIMIT</sub>=800mA

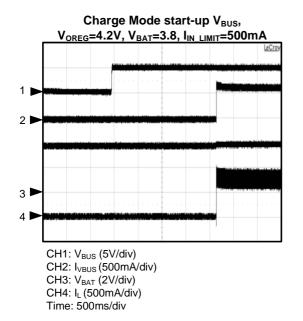

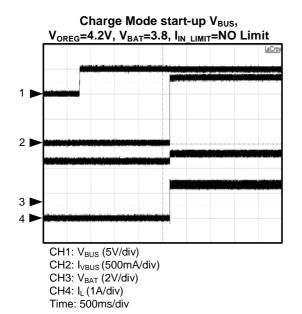

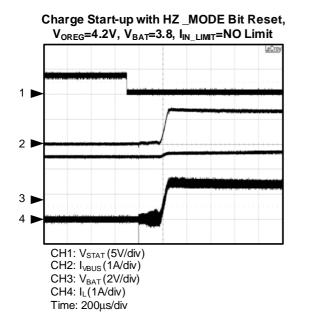

Charge Mode start-up V<sub>BUS</sub>,

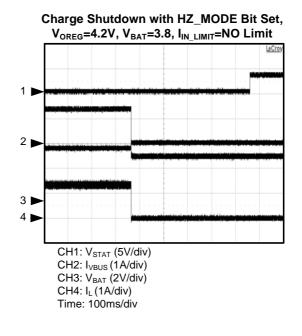

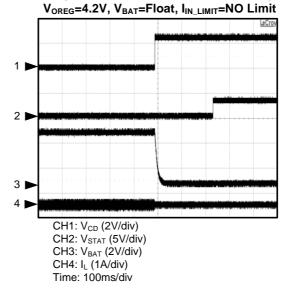

Charge Shutdown with CD Pin Pulled High,

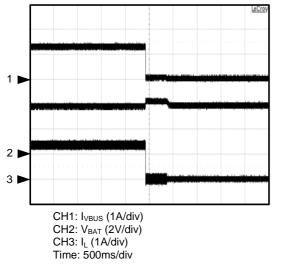

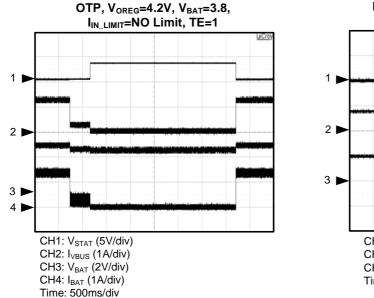

Battery Remove during Charging,  $V_{OREG}$ =4.2V,  $V_{BAT}$ =3.8,  $I_{IN\_LIMIT}$ =NO Limit, TE=1

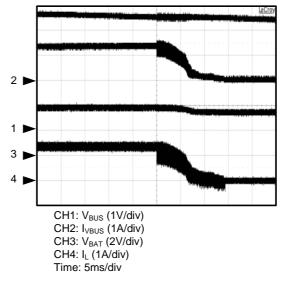

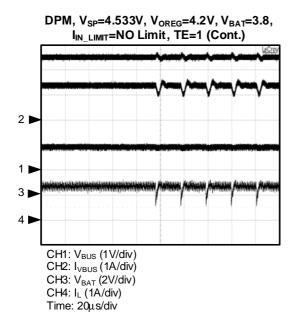

DPM,  $V_{SP}$ =4.533V,  $V_{OREG}$ =4.2V,  $V_{BAT}$ =3.8,  $I_{IN\_LIMIT}$ =NO Limit, TE=1

Charge Mode,  $V_{\text{BUS}}$  OVP/Released OVP,  $V_{\text{OREG}}\text{=}4.2V, V_{\text{BAT}}\text{=}3.8, I_{\text{IN}\_\text{LIMIT}}\text{=}\text{NO Limit}$ 2 🕨 1 3 🕨 4 🕨 CH1: V<sub>BUS</sub> (2V/div) CH2: V<sub>STAT</sub> (5V/div) CH3: V<sub>BAT</sub> (2V/div) CH4: IL (500mA/div) Time: 1s/div

Battery Overload, V<sub>OREG</sub>=4.2V, V<sub>BAT</sub>=Float, I<sub>IN LIMIT</sub>=NO Limit 1 2 🕨 1 2 3 🕨 3 🕨 4 4 🕨 CH1:  $V_{BUS}$  (2V/div) CH2:  $V_{BAT}$  (2V/div) CH1: V<sub>BUS</sub> (5V/div) CH2: V<sub>STAT</sub> (5V/div) CH3: V<sub>BAT</sub> (2V/div) CH3: V<sub>STAT</sub> (5V/div) CH4: IL (500mA/div) CH4: I<sub>L</sub> (1A/div) Time: 1s/div Time: 200µs/div

Charge Mode, Battery OVP/Released OVP, V<sub>OREG</sub>=4.2V, I<sub>IN\_LIMIT</sub>=NO Limit

Copyright © ANPEC Electronics Corp. Rev. A.1 - Jun., 2016

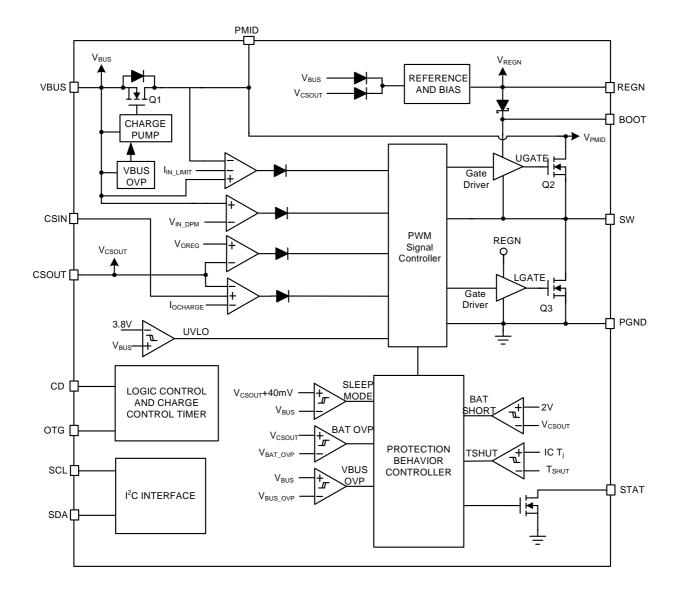

## **Block Diagram**

# **Typical Application Circuit**

## **Typical Application Circuit**

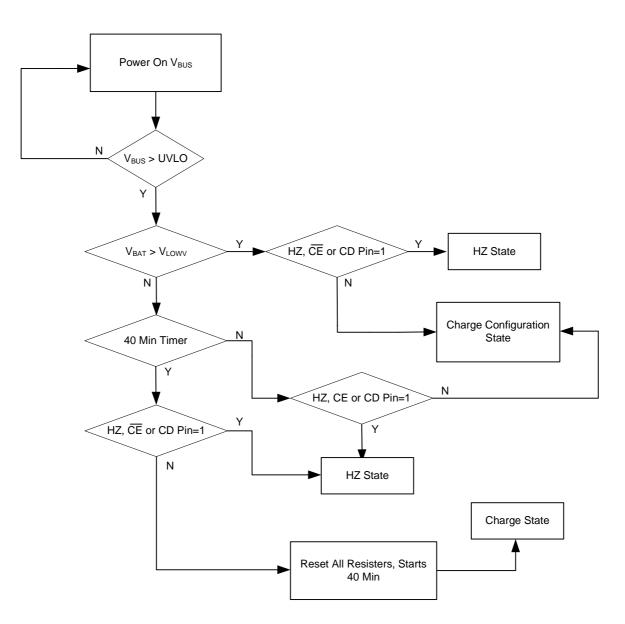

**Charger VBUS POR**

Figure 4. Charger VBUS POR Flow Chart

# **Typical Application Circuit**

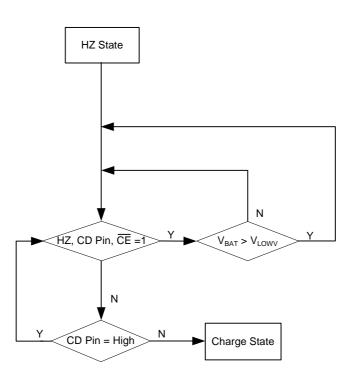

HZ State

Figure 5. HZ State Flow Chart

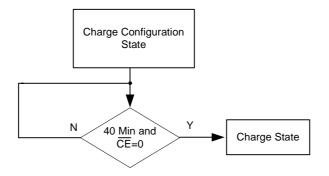

### **Charge Configuration State**

Figure 6. Charge Configuration Flow Chart

## **Typical Application Circuit**

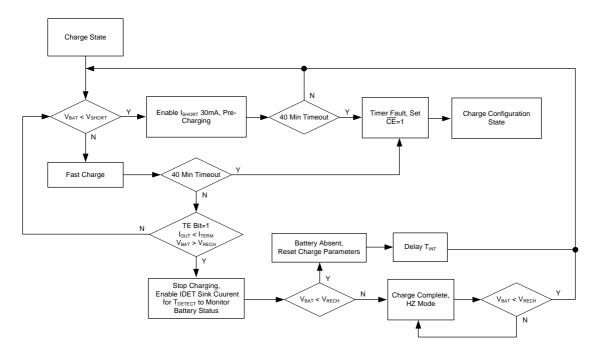

### **Charge State**

Figure 7. Operational Flow Chart in Charge Mode

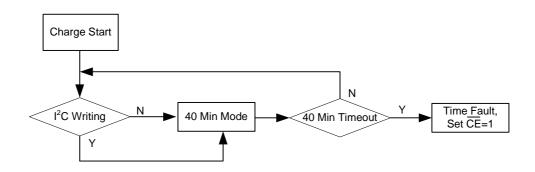

#### In Charge State=>Charge Start

Figure 8. Charger Timer Flow Chart

### **Function Description**

The APW7261 is a switch-mode battery charger with fixed 3MHz switching frequency, which drives two integrated N-channel power MOSFETs. The step-down DC/DC converter is ideally suited for portable electronic devices. In addition, the APW7261 can supply 5V to USB On-The-Go (OTG) peripherals through I<sup>2</sup>C programmable.

The APW7261 has three operation states in substance: 1.Charge State - charges a single-cell Li-ion or Li-polymer battery with an integrated synchronous rectification buck regulator.

2.Boost State - supply 5V power to USB-OTG with an integrated synchronous rectification boost regulator using battery terminal as input.

3.High-Impedance State - Both the charging and boost circuits are off. This state consumes low quiescent current from VBUS or the battery.

#### CHARGEMODE

#### **Battery Current Regulation**

Limits the maximum charging current. Using the resistor  $R_{_{SNS}}$  connected between CSIN and CSOUT as the battery sensing.

#### **Input Current Regulation**

The total input current is a function of the system supply current and the battery charging current. When the summation of system power and charge power exceeds the maximum VBUS input power, the device will reduce input current by using Dynamic Power Management (DPM). Using the internal MOSFET R<sub>DS(on)</sub> from VBUS to PMID terminal as the input current sensing.

#### **Charge Voltage Regulation**

The regulator is restricted from exceeding this voltage. When the voltage which is across  $R_{SNS}$  drops below the termination current threshold ( $I_{TERM}$ ), programmed by TE bit (REG1[3]) the battery charging is completed.

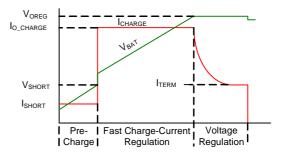

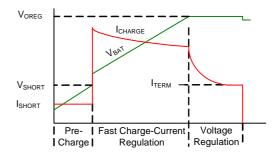

#### **Battery Charging Process**

While battery voltage is below the V<sub>SHORT</sub> threshold, the IC applies a constant short-circuit current I<sub>SHORT</sub>, to the battery. The charge current ramps up to fast charge current, I<sub>O(CHARGE)</sub>, or a charge current is limited by the input current of I<sub>IN\_LIMIT</sub> when the battery voltage is above V<sub>SHORT</sub> and below V<sub>OREG</sub>.

The input current limit,  $I_{IN\_LIMIT}$ , fast charge current,  $I_{O(CHARGE)}$ , and the battery regulation voltage,  $V_{OREG}$ , can be set by the host. Once the battery voltage reaches  $V_{OREG}$ , the charge current is decreased as shown in Figure 9.

(a) Charging Process, Not Limited by  ${\rm I}_{_{\rm IN \ LIMIT}}$

(b) Charge Curve, I<sub>IN LIMIT</sub> Limits I<sub>CHARGE</sub>

#### Figure 9. Typical Charge Process

The APW7261 monitors the battery-pack voltage between the CSOUT and PGND pins as voltage regulation feedback. The regulation voltage is adjustable from 3.5V to 4.44V and is programmed through I<sup>2</sup>C interface.

The IC monitors the charging current during the whole voltage regulation phase. The termination current level is programmable by I<sup>2</sup>C interface. The host can set the charge termination bit (REG1[3]) of charge control register to 0 to disable the charge current termination behavior. When below condition is occurred, a new charge cycle is initiated.

- The battery voltage falls below the  $\rm V_{_{OREG}}$  -  $\rm V_{_{RECH}}$  threshold when TE bit is set to 0.

### **Function Description**

### Safety Timer

At the beginning of charging process, the IC starts a 40minute timer that can be only disabled by VBUS POR Toggle. When the 40-minute timer times out, the IC turns off the charging operation, set CE bit to 1 (REG1[2]) and indicates a timer fault (110) on the FAULT bit (REG[2:0]). Toggle POR or write CE bit to 0 can restart charging process. Fault condition is cleared by POR and fault status bits can only be updated after the STAT bit are read by the host.

In default operation condition, 32-second timer is disabled and it can be programmable through 32sec timer bit (REG6[7]). If 32-second timer is enabled, it can be reset by any write-action performed by host through I<sup>2</sup>C interface. Writing "1" to reset the TMR\_RST bit (REG0[7]) will reset the 32-second timer and TMR\_RST is automatically set to "0" after the 32-second timer is reset. The charge is terminated and charge parameters are reset to default values when the 32-second timer expires. Then the 40-minute timer starts and the charge resumes.

#### **Special Charger**

The APW7261 has additional functionality to limit Input current in case a current-limited "special charger" is supplying VBUS. If  $V_{BUS}$  voltage is equal to the programmable  $V_{SP}$  (REG5[4]), the PWM controller starts to decrease the operation frequency and limits the charge current to keep  $V_{BUS}=V_{SP}$ .

#### Safety Settings

The APW7261 provides a SAFETY register (REG6) To avoid the value of the  $I_{O\_CHARGE}$  exceeding from the value of the ISAFE (REG4[6:4]).

The ISAFE register establishes value that limit the maximum value of I<sub>O\_CHARGE</sub> used by the control logic. If the host attempts to write a value higher than ISAFE to I<sub>O\_CHARGE</sub>, the ISAFE value as the I<sub>O\_CHARGE</sub> register value.

#### Input Current Limit

The APW7261 integrated the input current sensing circuit and control loop. When operating in boost mode, the input current limit is default 500mA. In charge mode, the input current limit is set by the programmed control bits in register 01H.

#### **Thermal Regulation**

To prevent overheating of the chip during the charging process, the IC monitors the junction temperature, T<sub>J</sub>, of the die. Once T<sub>J</sub> reaches the thermal regulation threshold, T<sub>CF</sub>, the IC begins to taper down the charge current. When the junction temperature increases approximately 10°C above T<sub>CF</sub>, the charge current is reduced to zero. In any state, The IC suspends charging if T<sub>J</sub> exceeds T<sub>SHTDWN</sub>. In thermal shutdown mode, PWM is turned off and all timers are frozen. When T<sub>J</sub> falls below T<sub>SHTDWN</sub> by approximately 10°C, the APW7261 resumes charging process.

#### Sleep Mode

If the V<sub>BUS</sub> voltage falls below the sleep mode entry threshold, V<sub>CSOUT</sub>+V<sub>SLP</sub>, the IC enters to the sleep mode. This feature prevents draining the battery during the absence of VBUS. During sleep mode, the internal reverse blocking switch and PWM controller are turned off.

#### **VBUS Low Voltage Detection (UVLO)**

During charging process, the APW7261 continuously monitors V<sub>BUS</sub> voltage. If V<sub>BUS</sub> falls below UVLO threshold, the IC stops to charge and sets STAT bits to "11", the FAULT bits to "011" off.

If VBUS rises above UVLO rising threshold, the charging process is repeated.

#### **VBUS Over-Voltage Protection**

The IC provides a built-in input over voltage protection (OVP) to protect the device and other components against damage if the VBUS voltage goes too high. When the VBUS OVP condition is detected, the IC turns off the PWM converter, sets the STAT bit to "11" and FAULT bits to "001". Once VBUS drops below the VBUS OVP exit threshold, the fault is cleared and charge process resumes.

#### **Battery Over-Voltage Protection**

The IC provides a built-in over voltage protection to protect the device and other components against damage if the battery voltage goes too high, as when the battery is suddenly removed. When the battery OVP condition is detected, the IC turns off the PWM converter, sets the STAT bit to "11" and FAULT bits to "100".

Once  $\rm V_{\scriptscriptstyle BAT}$  drops to the battery OVP threshold, the fault is cleared and charge process resumes.

### **Function Description**

### **Battery Short Circuit Protection**

If the battery voltage V<sub>BAT</sub> is below the short circuit threshold V<sub>SHORT</sub>, a constant current source I<sub>SHORT</sub> supplies V<sub>BAT</sub> until V<sub>BAT</sub> > V<sub>SHORT</sub>.

### Cycle-by-Cycle Charge Mode Current Limit

The APW7261 monitors internal high-side MOSFET for current sensing. If the peak current exceeds the highside MOSFET limit threshold, it will turn off the high-side MOSFET until the next cycle. When the current is below the over-current threshold, the high-side driver automatically resumes.

### **BOOST MODE**

BOOST mode can be enabled if OTG pin and OPA\_MODE bits as indicated in below table.

| OTG_EN | otg<br>Pin | OTG_PL | OPA_MODE | BOOST   |

|--------|------------|--------|----------|---------|

| 1      | HIGH       | 1      | Х        | ENABLE  |

| 1      | LOW        | 0      | Х        | ENABLE  |

| х      | х          | Х      | 1        | ENABLE  |

| 1      | HIGH       | 0      | 0        | DISABLE |

| 1      | LOW        | 1      | 0        | DISABLE |

| 0      | х          | Х      | 0        | DISABLE |

The APW7261 operates in boost mode and delivers power to VBUS from the battery. In normal boost mode, the APW7261 converts the battery voltage (2.5V to 4.5V) to VBUS (5V) and delivers a current  $I_{BO}$  500mA at lowest to support other USB OTG devices connected to the USB connector.

### PWM Controller in BOOST Mode

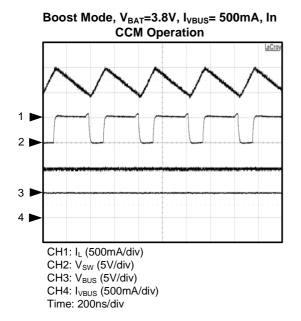

In boost mode, the APW7261 provides an integrated, fixed 3-MHz frequency voltage-mode controller to regulate output voltage VBUS as the same as charge mode operation.

In boost mode, cycle-by-cycle current limit is sensed through the  $R_{SNS}$  from CSIN to CSOUT. The peak current limit threshold is equal to  $(0.12V/R_{SNS})$ . For Example, if  $R_{SNS}$ =68m $\Omega$ , the peak current limit is about 1.76A. When current limit event is triggered, IC will turn off Q3 driver. If current limit event is released, it will re-back normal operation.

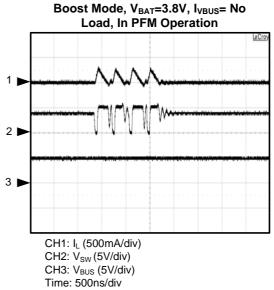

### PFM Mode at Light Load

In boost mode, under light load conditions, the IC operates in PFM mode (power saving) to reduce the power loss and improve the converter efficiency.

In PFM Mode, the on-time pulse width is constant and regulates off-time by zero crossing sensing.

### **VBUS Over-Voltage Protection**

The IC provides a built-in over voltage protection to protect the device and other components against damage if the  $V_{BUS}$  voltage goes too high. When the VBUS OVP condition is detected, the IC turns off the PWM converter, sets the STAT bit to "11", FAULT bits to "001" and resets OPA\_MODE bit to 0. And then, APW7261 will return to charge mode.

### **Battery Over-Voltage Protection**

In Boost mode, the IC provides a built-in input over voltage protection to protect the device and other components against damage if the VBAT voltage goes too high. When the VBAT OVP condition is detected, the IC turns off the PWM converter, sets the STAT bit to "11" and resets OPA\_MODE bit to 0. And then, APW7261 will return to charge mode.

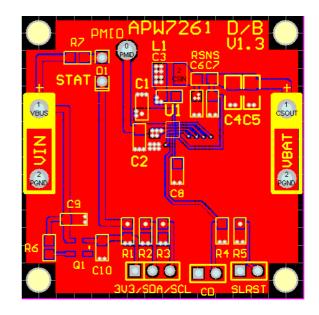

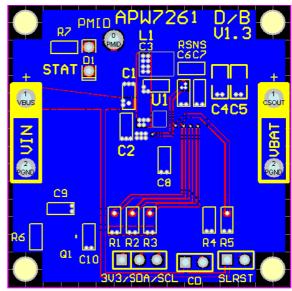

### Layout Consideration

In any high switching frequency converter, a correct layout is important to ensure proper operation of the regulator. With power devices switching at higher frequency, the resulting current transient will cause voltage spike across the interconnecting impedance and parasitic circuit elements. As an example, consider the turn-off transition of the PWM MOSFET. Before turn-off condition, the MOSFET is carrying the full load current. During turn-off, current stops flowing in the MOSFET and is freewheeling by the lower MOSFET and parasitic diode. Any parasitic inductance of the circuit generates a large voltage spike during the switching interval. In general, using short and wide printed circuit traces should minimize interconnecting impedances and the magnitude of voltage spike. And signal and power grounds are to be kept separating and finally combined to use the ground plane construction or single point grounding if the above seperated pinout ground condittions are satisfied.

## Function Description (Cont.)

#### Layout Consideration (Cont.)

Below are Layout consideration checklist, recommended layout Schematic diagram and demoboard layout for your reference:

Keep the switching nodes (BOOT and SW) away from sensitive small signal nodes since these nodes are fast moving signals. Therefore, keep traces to these nodes as short as possible and there should be no other weak signal traces in parallel with theses traces on any layer.

The large layout plane between the drain of the MOSFETs (VIN and SW nodes) can get better heat sinking.

- The sense resistor should be adjacent to the junction of the inductor and output capacitor. Route the sense leads connected across the RSNS back to the IC, close to each other (minimize loop area) or on top of each other on adjacent layers (do not route the sense leads through a high-current path).

- The high-current charge paths into VBUS, PMID and from the SW pins must be sized appropriately for the maximum charge current in order to avoid voltage drops in these traces.

- Place all decoupling capacitors close to their respective IC pins and close to PGND (do not place components such that routing interrupts power stage currents). All small control signals should be routed away from the high current paths.

- The output bulk capacitors should be close to the loads. The input capacitor's ground should be close to the grounds of the output capacitors.

**Top Layer**

#### **Bottom Layer**

Copyright © ANPEC Electronics Corp. Rev. A.1 - Jun., 2016

## I<sup>2</sup>C Introduction

### I<sup>2</sup>C SERIAL CONTROL INTERFACE

The APW7261 DAP has a bidirectional I<sup>2</sup>C interface that compatible with the I<sup>2</sup>C (Inter IC) bus protocol and supports standard mode (100-kHz), fast mode (400-kHz) and the high-speed mode (up to 3.4Mbps in wire mode) data transfer rates for single byte write and read operations. This is a slave only device that does not support a multi-master bus environment or wait state insertion. The control interface is used to program the registers of the device and to read device status.

The DAP supports the standard-mode I<sup>2</sup>C bus operation (100 kHz maximum), the fast I<sup>2</sup>C bus operation (400 kHz maximum) and the high-speed mode (up to 3.4Mbps in wire mode). The DAP performs all I2C operations without I<sup>2</sup>C wait cycles.

### General I<sup>2</sup>C Operation

The I<sup>2</sup>C bus uses two signals; SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Data is transferred on the bus serially one bit at a time. The address and data can be transferred in byte (8-bit) format, with the most significant bit (MSB) transferred first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus.

The bus uses transitions on the data pin (SDA) while the clock is high to indicate a start and stop conditions. A highto-low transition on SDA indicates a start and a low-to-high transition indicates a stop. Normal data bit transitions must occur within the low time of the clock period. These conditions are shown in Figure 10. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The APW7261 holds SDA low during the acknowledge clock period to indicate an acknowledgment. When this occurs, the master transmits the next byte of the sequence.

Each device is addressed by a unique 7-bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. An external pull-up resistor must be used for the SDA and SCL signals to set the high level for the bus.

Figure 10. Typical I<sup>2</sup>C sequence

There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. A generic data transfer sequence is shown in Figure 10. Pin A\_SEL defines the I<sup>2</sup>C device address. The device 7-bit address is defined as "1101010" (6AH) for APW7261.

## I<sup>2</sup>C Introduction

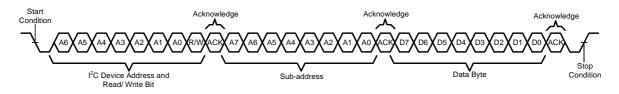

### Single-Byte Transfer

The serial control interface supports single-byte read/write operations for sub-addresses 0x00 to 0xFF.

Supplying a sub-address for each sub-address transaction is referred to as random I<sup>2</sup>C addressing. The APW7261 also supports sequential I<sup>2</sup>C addressing. For write transactions, if a sub-address is issued followed by data for that sub-address and the 15 sub-addresses that follow, a sequential I<sup>2</sup>C write transaction has taken place, and the data for all 16 sub-addresses is successfully received by the APW7261. For I<sup>2</sup>C sequential write transactions, the sub-address then serves as the start address, and the amount of data subsequently transmitted, before a stop or start is transmitted, determines how many sub-addresses are written. As was true for random addressing, sequential addressing requires that a complete set of data be transmitted. If only a partial set of data is written to the last sub-address, the data for the last sub-address is discarded. However, all other data written is accepted; only the incomplete data is discarded.

### Single-Byte Write

As shown in Figure 11, a single-byte data write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. The read/write bit determines the direction of the data transfer. For a write data transfer, the read/write bit will be a 0. After receiving the correct I<sup>2</sup>C device address and the read/write bit, the DAP responds with an acknowledge bit. Next, the master transmits the address byte or bytes corresponding to the APW7261 internal memory address being accessed. After receiving the address byte, the APW7261 again responds with an acknowledge bit. Next, the master device transmits the data byte to be written to the memory address being accessed. After receiving the data byte, the APW7261 again responds with an acknowledge bit. Next, the APW7261 again responds with an acknowledge bit. Next, the APW7261 again responds with an acknowledge bit. Start device transmits the data byte to be written to the memory address being accessed. After receiving the data byte, the APW7261 again responds with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single-byte data write transfer.

Figure 11. Single-Byte Write Transfer

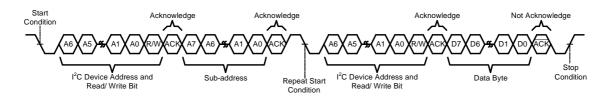

#### Single-Byte Read

As shown in Figure 12, a single-byte data read transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. For the data read transfer, both a write followed by a read are actually done. Initially, a write is done to transfer the address byte or bytes of the internal memory address to be read. As a result, the read/write bit becomes a 0. After receiving the APW7261 address and the read/write bit, APW7261 responds with an acknowledge bit. In addition, after sending the internal memory address byte or bytes, the master device transmits another start condition followed by the APW7261 address and the read/write bit again. This time the read/write bit becomes a 1, indicating a read transfer. After receiving the address and the read/write bit, the APW7261 again responds with an acknowledge bit. Next, the APW7261 transmits the data byte from the memory address being read. After receiving the data byte, the master device transmits a not acknowledge bit. Next, the address and the read/write bit again the APW7261 again responds with an acknowledge bit. Next, the APW7261 transmits the data byte from the memory address being read. After receiving the data byte, the master device transmits a not acknowledge followed by a stop condition to complete the single byte data read transfer.

## I<sup>2</sup>C Introduction

Single-Byte Read (Cont.)

Figure 12. Single-Byte Read Transfer

## **Register Description**

The APW7261 has seven user-accessible registers. It is as defined as below table.

| Register Address | Name                            | Read/Write/Read Only State | Default Value |

|------------------|---------------------------------|----------------------------|---------------|

| 00               | Control/Status                  | Read/Write                 | X1 XX 0XXX    |

| 01               | Control/Input Current Limit     | Read/Write                 | 0111 00 00    |

| 02               | Control/Battery Voltage         | Read/Write                 | 0000 1010     |

| 03               | Vender/Part/Revision            | Read Only                  | 010X XXXX     |

| 04               | Termination/Fast Charge Current | Read/Write                 | 0000 0001     |

| 05               | Enable/Special Charger Voltage  | Read/Write/Read Only       | 001X X100     |

| 06               | Safety Limit                    | Read/Write                 | 1100 0000     |

The below tables define the operation of each register bit. Default values are in **bold** text.

### Table1. Register Address: 00

| Bit   | Name        | Data | Read/Write | Description                                                                  |  |  |  |

|-------|-------------|------|------------|------------------------------------------------------------------------------|--|--|--|

|       |             |      | Write      | Default Condition, write "0" or "1" has no effect ; If call out 32sec timer, |  |  |  |

| 7     | TMR_RST/OTG |      | white      | Writing a 1 resets the t <sub>32s</sub> timer                                |  |  |  |

|       |             |      | Read       | OTG pin status. "0"=> OTG=Low; "1"=> OTG=High                                |  |  |  |

|       |             | 0    | Read/Write | Disable STAT pin function                                                    |  |  |  |

| 6     | EN_STAT     | 1    | Read/Write | Enable STAT pin function                                                     |  |  |  |

|       |             | 00   | Read       | Ready                                                                        |  |  |  |

| [5,4] | STAT        | 01   | Read       | Charge in process                                                            |  |  |  |

| [5:4] | STAI        | 10   | Read       | Charge done                                                                  |  |  |  |

|       |             | 11   | Read       | Fault                                                                        |  |  |  |

| 0     | 3 BOOST -   |      | Read       | Not in boost mode                                                            |  |  |  |

| 3     |             |      | Read       | In boost mode                                                                |  |  |  |

|       |             | 000  | Read       | Charge mode : Normal                                                         |  |  |  |

|       |             | 000  | Reau       | Boost mode : Normal                                                          |  |  |  |

|       |             | 001  | Read       | Charge mode : VBUS OVP                                                       |  |  |  |

| [2:0] | FAULT       | 001  | Reau       | Boost mode : VBUS OVP                                                        |  |  |  |

| [2.0] | FAULI       | 010  | Read       | Charge mode : Sleep mode                                                     |  |  |  |

|       |             | 010  | Reau       | Boost mode : Over load                                                       |  |  |  |

|       |             |      | Bood       | Charge mode : VBUS < UVLO                                                    |  |  |  |

|       |             | 011  | Read       | Boost mode : VBAT < UVLO <sub>BST</sub>                                      |  |  |  |

Copyright © ANPEC Electronics Corp. Rev. A.1 - Jun., 2016

| Bit   | Name        | Data     | Read/Write                                    | Description                                                     |

|-------|-------------|----------|-----------------------------------------------|-----------------------------------------------------------------|

|       | 100         | Read     | Charge mode : Battery OVP<br>Boost mode : N/A |                                                                 |

| [0.0] | [2:0] FAULT | 101 Read |                                               | Charge mode : Thermal Shutdown<br>Boost mode : Thermal Shutdown |

| [2:0] |             | 110      | Read                                          | Charge mode : Timer fault<br>Boost mode : Timer fault           |

|       |             | 111      | Read                                          | Charge mode : No battery<br>Boost mode : N/A                    |

### Table2. Register Address: 01

| Bit   | Name                    | Data | Read/Write | Description                        |  |  |

|-------|-------------------------|------|------------|------------------------------------|--|--|

|       |                         |      | Read/Write | 100mA                              |  |  |

| [7.0] | 1                       | 01   | Read/Write | 500m A                             |  |  |

| [7:6] | I <sub>IN_LIMIT</sub>   | 10   | Read/Write | 800mA                              |  |  |

|       |                         | 11   | Read/Write | No Current Limit                   |  |  |

|       |                         | 00   | Read/Write | 3.4V                               |  |  |

| 15.41 | N/                      | 01   | Read/Write | 3.5V                               |  |  |

| [5:4] | [5:4] V <sub>LOWV</sub> | 10   | Read/Write | 3.6V                               |  |  |

|       |                         | 11   | Read/Write | 3.7V                               |  |  |

| 3     | TE                      | 0    | Read/Write | Disable charge current termination |  |  |

| 3     | IC                      | 1    | Read/Write | Enable charge current termination  |  |  |

| 2     | CE                      | 0    | Read/Write | Charge enabled                     |  |  |

| 2     | CE                      | 1    | Read/Write | Charge disabled                    |  |  |

|       |                         | 0    | Read/Write | Not High-Impedance Mode            |  |  |

| 1     | 1 HZ_MODE               |      | Read/Write | High-Impedance Mode                |  |  |

| 0     |                         | 0    | Read/Write | Charge Mode                        |  |  |

| U     | 0 OPA_MODE              |      | Read/Write | Boost Mode                         |  |  |

Table3. Register Address: 02

| Bit   | Name | Data   | Read/Write | Description |

|-------|------|--------|------------|-------------|

|       |      | 000000 | Read/Write | 3.5V        |

|       |      | 000001 | Read/Write | 3.52V       |

|       |      | 000010 | Read/Write | 3.54V       |

|       |      | 000011 | Read/Write | 3.56V       |

|       |      | 000100 | Read/Write | 3.58V       |

|       |      | 000101 | Read/Write | 3.6V        |

|       |      | 000110 | Read/Write | 3.62V       |

|       |      | 000111 | Read/Write | 3.64V       |

|       |      | 001000 | Read/Write | 3.66V       |

|       |      | 001001 | Read/Write | 3.68V       |

|       |      | 001010 | Read/Write | 3.7V        |

|       |      | 001011 | Read/Write | 3.72V       |

|       |      | 001100 | Read/Write | 3.74V       |

|       |      | 001101 | Read/Write | 3.76V       |

|       |      | 001110 | Read/Write | 3.78V       |

|       |      | 001111 | Read/Write | 3.8V        |

|       |      | 010000 | Read/Write | 3.82V       |

|       |      | 010001 | Read/Write | 3.84V       |

| [7:2] | OREG | 010010 | Read/Write | 3.86V       |

|       |      | 010011 | Read/Write | 3.88V       |

|       |      | 010100 | Read/Write | 3.9V        |

|       |      | 010101 | Read/Write | 3.92V       |

|       |      | 010110 | Read/Write | 3.94V       |

|       |      | 010111 | Read/Write | 3.96V       |

|       |      | 011000 | Read/Write | 3.98V       |

|       |      | 011001 | Read/Write | 4V          |

|       |      | 011010 | Read/Write | 4.02V       |

|       |      | 011011 | Read/Write | 4.04V       |

|       |      | 011100 | Read/Write | 4.06V       |

|       |      | 011101 | Read/Write | 4.08V       |

|       |      | 011110 | Read/Write | 4.1V        |

|       |      | 011111 | Read/Write | 4.12V       |

|       |      | 100000 | Read/Write | 4.14V       |

|       |      | 100001 | Read/Write | 4.16V       |

|       |      | 100010 | Read/Write | 4.18V       |

|       |      | 100011 | Read/Write | 4.2V        |

|       |      | 100100 | Read/Write | 4.22V       |

Table3. Register Address: 02

| Bit   | Name   | Data   | Read/Write | Description         |

|-------|--------|--------|------------|---------------------|

|       |        | 100100 | Read/Write | 4.22V               |

|       |        | 100101 | Read/Write | 4.24V               |

|       |        | 100110 | Read/Write | 4.26V               |

|       |        | 100111 | Read/Write | 4.28V               |

|       |        | 101000 | Read/Write | 4.3V                |

|       |        | 101001 | Read/Write | 4.32V               |

|       |        | 101010 | Read/Write | 4.34V               |

|       |        | 101011 | Read/Write | 4.36V               |

|       |        | 101100 | Read/Write | 4.38V               |

|       |        | 101101 | Read/Write | 4.4V                |

|       |        | 101110 | Read/Write | 4.42V               |

|       |        | 101111 | Read/Write | 4.44V               |

|       |        | 110000 | Read/Write | 4.44V               |

| [7:2] | OREG   | 110001 | Read/Write | 4.44V               |

|       |        | 110010 | Read/Write | 4.44V               |

|       |        | 110011 | Read/Write | 4.44V               |

|       |        | 110100 | Read/Write | 4.44V               |

|       |        | 110101 | Read/Write | 4.44V               |

|       |        | 110110 | Read/Write | 4.44V               |

|       |        | 110111 | Read/Write | 4.44V               |

|       |        | 111000 | Read/Write | 4.44V               |

|       |        | 111001 | Read/Write | 4.44V               |

|       |        | 111010 | Read/Write | 4.44V               |

|       |        | 111011 | Read/Write | 4.44V               |

|       |        | 111100 | Read/Write | 4.44V               |

|       |        | 111101 | Read/Write | 4.44V               |

|       |        | 111110 | Read/Write | 4.44V               |

| 4     |        | 0      | Read/Write | OTG pin active Low  |

| 1     | OTG_PL | 1      | Read/Write | OTG pin active High |

| 0     | OTG_EN | 0      | Read/Write | OTG pin is disabled |

| U     |        | 1      | Read/Write | OTG pin is enabled  |

### Table4. Register Address: 03

| Bit   | Name        | Data | Read/Write | Description                  |

|-------|-------------|------|------------|------------------------------|

| [7:5] | Vender code | 010  | Read Only  |                              |

| [4:3] | PN          | XX   | Read Only  | For I <sup>2</sup> C Address |