## XD13700 DIP16 / XL13700 SOP16

#### 1 Features

- g<sub>m</sub> Adjustable Over 6 Decades

- Excellent g<sub>m</sub> Linearity

- · Excellent Matching Between Amplifiers

- Linearizing Diodes for reduced output distortion

- · High Impedance Buffers

- High Output Signal-to-Noise Ratio

## 2 Applications

- · Current-Controlled Amplifiers

- Stereo Audio Amplifiers

- Current-Controlled Impedances

- Current-Controlled Filters

- Current-Controlled Oscillators

- Multiplexers

- Timers

- Sample-and-Hold Circuits

## 3 Description

The XD13700 series consists of two currentcontrolled transconductance amplifiers, each with differential inputs and a push-pull output. The two amplifiers share common supplies but otherwise operate independently. Linearizing diodes are provided at the inputs to reduce distortion and allow higher input levels. The result is a 10-dB signal-tonoise improvement referenced to 0.5 percent THD. High impedance buffers are provided which are especially designed to complement the dynamic range of the amplifiers. The output buffers of the XD13700 differ from those of the XL13700 in that their input bias currents (and thus their output DC levels) are independent of IABC. This may result in performance superior to that of the XL13700 in audio applications.

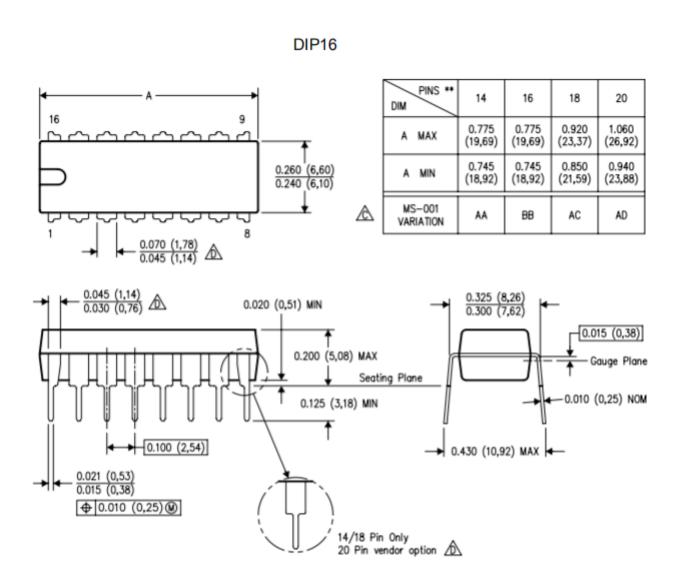

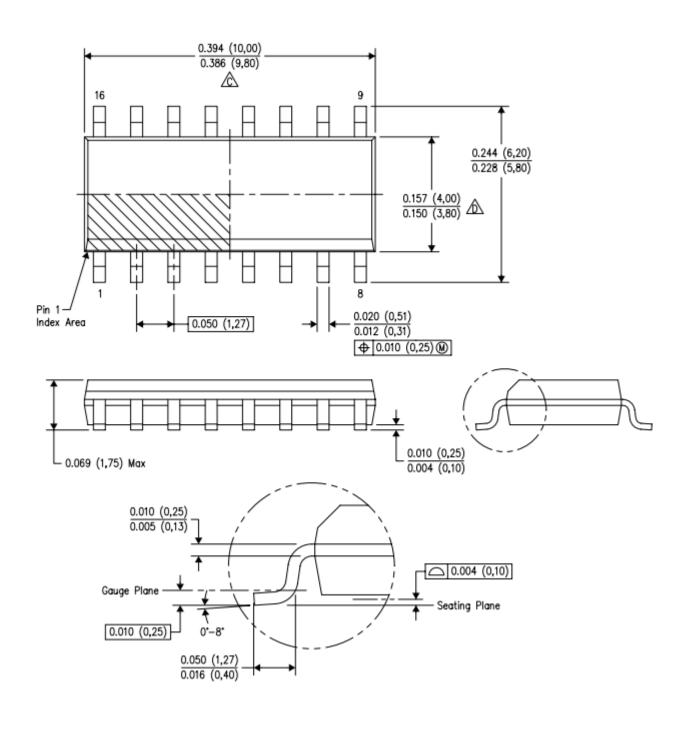

#### **Device Information**<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |

|-------------|-----------|---------------------|

| 13700       | SOIC (16) | 3.91 mm × 9.90 mm   |

|             | PDIP (16) | 6.35 mm × 19.304 mm |

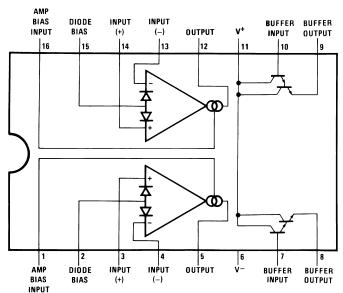

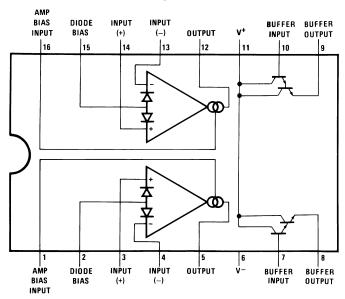

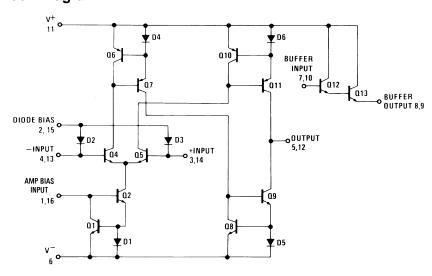

#### **Connection Diagram**

# **5 Pin Configuration and Functions**

#### **Pin Functions**

| PIN            |       | 1/0 | DESCRIPTION                  |  |  |

|----------------|-------|-----|------------------------------|--|--|

| NAME           | NO.   | 1/0 | DESCRIPTION                  |  |  |

| Amp bias input | 1, 16 | Α   | Current bias input           |  |  |

| Buffer input   | 7, 10 | Α   | Buffer amplifier input       |  |  |

| Buffer output  | 8, 9  | Α   | Buffer amplifier output      |  |  |

| Diode bias     | 2, 15 | Α   | Linearizing diode bias input |  |  |

| Input+         | 3, 14 | Α   | Positive input               |  |  |

| Input-         | 4, 13 | Α   | Negative input               |  |  |

| Output         | 5, 12 | Α   | Unbuffered output            |  |  |

| V <sup>+</sup> | 11    | Р   | Positive power supply        |  |  |

| V <sup>-</sup> | 6     | Р   | Negative power supply        |  |  |

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                  | MIN             | MAX                       | UNIT |

|------------------------------------------------------------------|-----------------|---------------------------|------|

| Supply voltage                                                   |                 | 36 V <sub>DC</sub> or ±18 | V    |

| DC input voltage                                                 | +V <sub>S</sub> | -V <sub>S</sub>           | V    |

| Differential input voltage                                       |                 | ±5                        | V    |

| Diode bias current (I <sub>D</sub> )                             |                 | 2                         | mA   |

| Amplifier bias current (I <sub>ABC</sub> )                       |                 | 2                         | mA   |

| Buffer output current (2)                                        |                 | 20                        | mA   |

| Power dissipation <sup>(3)</sup> T <sub>A</sub> = 25°C – XD13700 |                 | 570                       | mW   |

| Output short circuit duration                                    | Con             | Continuous                |      |

| Storage temperature, T <sub>stg</sub>                            | <b>-</b> 65     | 150                       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Buffer output current should be limited so as to not exceed package dissipation.

#### **6.2 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                       |         |      | MIN   | MAX | UNIT |

|---------------------------------------|---------|------|-------|-----|------|

| V+ (single-supply configuration)      |         | 9.5  | 32    | V   |      |

| V+ (dual-supply configuration)        |         | 4.75 | 16    | V   |      |

| V– (dual-supply configuration)        |         | -16  | -4.75 | V   |      |

| Operating temperature, T <sub>A</sub> | XD13700 |      | 0     | 70  | °C   |

#### 6.3 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | XD1      |            |      |

|-------------------------------|----------------------------------------------|----------|------------|------|

|                               |                                              | D (SOIC) | NFG (PDIP) | UNIT |

|                               |                                              | 16 PINS  | 16 PINS    |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 83.0     | 43.8       | °C/W |

| $R_{\theta JC(top)}$          | Junction-to-case (top) thermal resistance    | 44.0     | 34.9       | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 40.5     | 28.3       | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 11.5     | 19.1       | °C/W |

| ΨЈВ                           | Junction-to-board characterization parameter | 40.2     | 28.2       | °C/W |

<sup>(3)</sup> For operation at ambient temperatures above 25°C, the device must be derated based on a 150°C maximum junction temperature and a thermal resistance, junction to ambient, as follows: XD13700, 90°C/W; XL13700, 110°C/W.

# XD13700 DIP16 / XL13700 SOP16

#### 6.4 Electrical Characteristics

These specifications apply for  $V_S = \pm 15$  V,  $T_A = 25$ °C, amplifier bias current ( $I_{ABC}$ ) = 500  $\mu$ A, pins 2 and 15 open unless otherwise specified. The inputs to the buffers are grounded and outputs are open.

| PARAMETER                                  | TEST CONDITIONS                                            | MIN  | TYP   | MAX   | UNIT |  |

|--------------------------------------------|------------------------------------------------------------|------|-------|-------|------|--|

| Input offset voltage (V <sub>OS</sub> )    | Over specified temperature range                           |      | 0.4   | 4     | mV   |  |

|                                            | $I_{ABC} = 5 \mu A$                                        |      | 0.3   | 4     | mv   |  |

| V <sub>OS</sub> including diodes           | Diode bias current (I <sub>D</sub> ) = 500 μA              |      | 0.5   | 5     | mV   |  |

| Input offset change                        | 5 μA ≤ I <sub>ABC</sub> ≤ 500 μA                           |      | 0.1   | 3     | mV   |  |

| Input offset current                       |                                                            |      | 0.1   | 0.6   | μΑ   |  |

| Innuit bing assessed                       |                                                            |      | 0.4   | 5     |      |  |

| Input bias current                         | Over specified temperature range                           |      | 1     | 8     | μΑ   |  |

|                                            |                                                            | 6700 | 9600  | 13000 | 0    |  |

| Forward transconductance (g <sub>m</sub> ) | Over specified temperature range                           | 5400 |       |       | μS   |  |

| g <sub>m</sub> tracking                    |                                                            |      | 0.3   |       | dB   |  |

|                                            | $R_L = 0$ , $I_{ABC} = 5 \mu A$                            |      | 5     |       |      |  |

| Peak output current                        | R <sub>L</sub> = 0, I <sub>ABC</sub> = 500 μA              | 350  | 500   | 650   | μΑ   |  |

|                                            | R <sub>L</sub> = 0, Over Specified Temp Range              | 300  |       |       |      |  |

| Supply current                             | I <sub>ABC</sub> = 500 μA, both channels                   |      | 2.6   |       | mA   |  |

| CMRR                                       |                                                            | 80   | 110   |       | dB   |  |

| Common-mode range                          |                                                            | ±12  | ±13.5 |       | V    |  |

| Crosstalk                                  | Referred to input <sup>(1)</sup><br>20 Hz < f < 20 kHz     |      | 100   |       | dB   |  |

| Differential input current                 | $I_{ABC} = 0$ , input = ±4 V                               |      | 0.02  | 100   | nA   |  |

| Leakage current                            | I <sub>ABC</sub> = 0 (refer to test circuit)               |      | 0.2   | 100   | nA   |  |

| Input resistance                           |                                                            | 10   | 26    |       | kΩ   |  |

| Open-loop bandwidth                        |                                                            |      | 2     |       | MHz  |  |

| Slew rate                                  | Unity gain compensated                                     |      | 50    |       | V/µs |  |

| Buffer input current                       | See (1)                                                    |      | 0.5   | 2     | μΑ   |  |

| Peak buffer output voltage                 | See <sup>(1)</sup>                                         | 10   |       |       | V    |  |

| PEAK OUTPUT VOLTAGE                        |                                                            |      |       |       |      |  |

| Positive                                   | $R_L = \infty$ , 5 $\mu$ A $\leq I_{ABC} \leq$ 500 $\mu$ A | 12   | 14.2  |       | V    |  |

| Negative                                   | R <sub>L</sub> = ∞, 5 μA ≤ I <sub>ABC</sub> ≤ 500 μA       | -12  | -14.4 |       | V    |  |

| V <sub>OS</sub> SENSITIVITY                |                                                            |      |       |       |      |  |

| Positive                                   | $\Delta V_{OS}/\Delta V^{+}$                               |      | 20    | 150   | μV/V |  |

| Negative                                   | $\Delta V_{OS}/\Delta V^{-}$                               |      | 20    | 150   | μV/V |  |

<sup>(1)</sup> These specifications apply for  $V_S = \pm 15$  V,  $I_{ABC} = 500$   $\mu A$ ,  $R_{OUT} = 5$ -k $\Omega$  connected from the buffer output to  $\neg V_S$  and the input of the buffer is connected to the transconductance amplifier output.

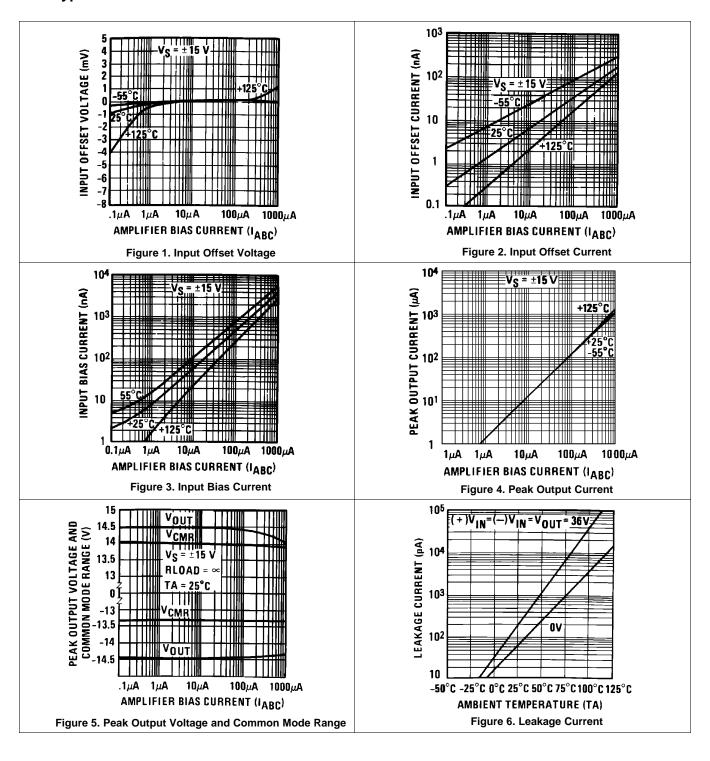

### 6.5 Typical Characteristics

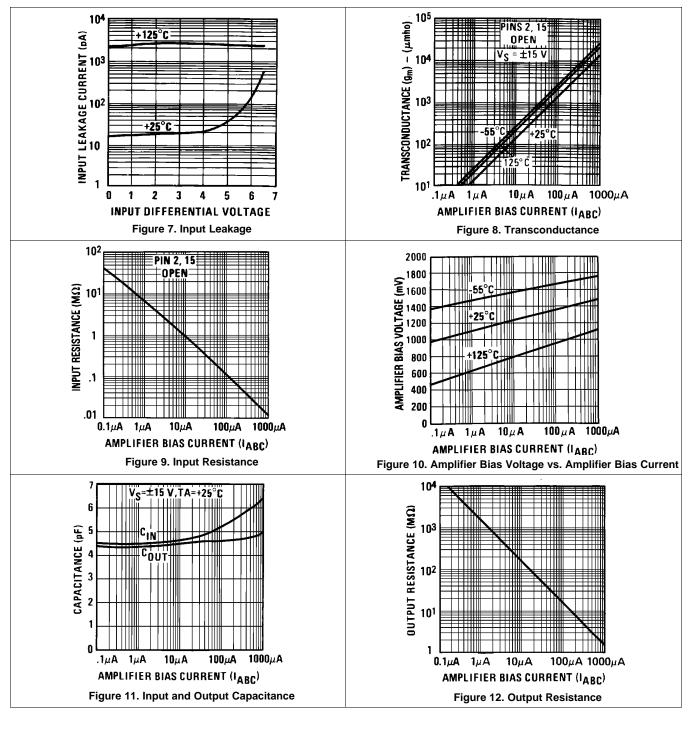

## **Typical Characteristics (continued)**

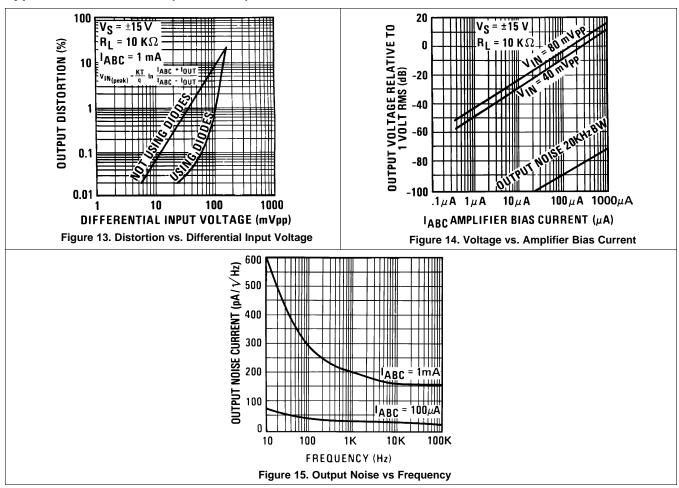

## **Typical Characteristics (continued)**

#### 7 Detailed Description

#### 7.1 Overview

The XD13700 is a two channel current controlled differential input transconductance amplifier with additional output buffers. The inputs include linearizing diodes to reduce distortion, and the output current is controlled by a dedicated pin. The outputs can sustain a continuous short to ground.

#### 7.2 Functional Block Diagram

Figure 16. One Operational Transconductance Amplifier

#### 7.3 Feature Description

#### 7.3.1 Circuit Description

The differential transistor pair  $Q_4$  and  $Q_5$  form a transconductance stage in that the ratio of their collector currents is defined by the differential input voltage according to the transfer function:

$$V_{IN} = \frac{kT}{q} \ln \frac{l_5}{l_4} \tag{1}$$

where  $V_{IN}$  is the differential input voltage, kT/q is approximately 26 mV at 25°C and  $I_5$  and  $I_4$  are the collector currents of transistors  $Q_5$  and  $Q_4$  respectively. With the exception of  $Q_{12}$  and  $Q_{13}$ , all transistors and diodes are identical in size. Transistors  $Q_1$  and  $Q_2$  with Diode  $D_1$  form a current mirror which forces the sum of currents  $I_4$  and  $I_5$  to equal  $I_{ABC}$ :

$$I_4 + I_5 = I_{ABC} \tag{2}$$

where I<sub>ABC</sub> is the amplifier bias current applied to the gain pin.

For small differential input voltages the ratio of  $I_4$  and  $I_5$  approaches unity and the Taylor series of the In function is approximated as:

$$\frac{kT}{q} \ln \frac{l_5}{l_4} \approx \frac{kT}{q} \frac{l_5 - l_4}{l_4}$$

$$l_4 \approx l_5 \approx \frac{l_{ABC}}{2}$$

(3)

$$V_{IN}\left[\frac{I_{ABC}q}{2kT}\right] = I_5 - I_4 \tag{4}$$

#### **Feature Description (continued)**

Collector currents  $I_4$  and  $I_5$  are not very useful by themselves and it is necessary to subtract one current from the other. The remaining transistors and diodes form three current mirrors that produce an output current equal to  $I_5$  minus  $I_4$  thus:

$$V_{IN}\left[\frac{I_{ABC}q}{2kT}\right] = I_{OUT} \tag{5}$$

The term in brackets is then the transconductance of the amplifier and is proportional to I<sub>ABC</sub>.

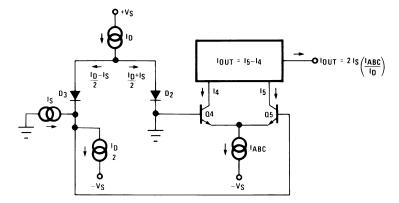

#### 7.3.2 Linearizing Diodes

For differential voltages greater than a few millivolts, Equation 3 becomes less valid and the transconductance becomes increasingly nonlinear. Figure 19 demonstrates how the internal diodes can linearize the transfer function of the amplifier. For convenience assume the diodes are biased with current sources and the input signal is in the form of current  $I_S$ . Since the sum of  $I_4$  and  $I_5$  is  $I_{ABC}$  and the difference is  $I_{OUT}$ , currents  $I_4$  and  $I_5$  is written as follows:

$$I_4 = \frac{I_{ABC}}{2} - \frac{I_{OUT}}{2}, I_5 = \frac{I_{ABC}}{2} + \frac{I_{OUT}}{2}$$

(6)

Since the diodes and the input transistors have identical geometries and are subject to similar voltages and temperatures, the following is true:

$$\frac{kT}{q} \ln \frac{\frac{I_D}{2} + I_S}{\frac{I_D}{2} - I_S} = \frac{kT}{q} \ln \frac{\frac{I_{ABC}}{2} + \frac{I_{OUT}}{2}}{\frac{I_{ABC}}{2} - \frac{I_{OUT}}{2}}$$

$$\therefore I_{OUT} = I_S \left(\frac{2I_{ABC}}{I_D}\right) \text{ for } |I_S| < \frac{I_D}{2}$$

(7)

Notice that in deriving Equation 7 no approximations have been made and there are no temperature-dependent terms. The limitations are that the signal current not exceed  $I_{\rm D}$  / 2 and that the diodes be biased with currents. In practice, replacing the current sources with resistors will generate insignificant errors.

#### 7.4 Device Functional Modes

Use in single ended or dual supply systems requires minimal changes. The outputs can support a sustained short to ground. Note that use of the XD13700 in  $\pm 5$  V supply systems requires will reduce signal dynamic range; this is due to the PNP transistors having a higher  $V_{BE}$  than the NPN transistors.

#### 7.4.1 Output Buffers

Each channel includes a separate output buffer which consists of a Darlington pair transistor that can drive up to 20mA.

#### 8 Application and Implementation

#### 8.1 Application Information

An OTA is a versatile building block analog component that can be considered an ideal transistor. The XD13700 can be used in a wide variety of applications, from voltage-controlled amplifiers and filters to VCOs. The 2 well-matched, independent channels make the XL13700 well suited for stereo audio applications.

#### 8.2 Typical Application

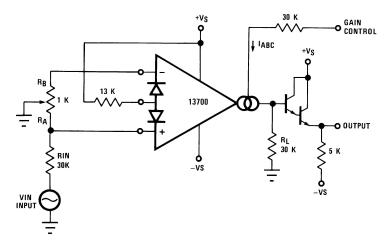

Figure 17. Voltage Controlled Amplifier

#### 8.2.1 Design Requirements

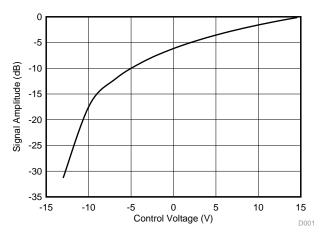

For this example application, the system requirements provide a volume control for a 1  $V_P$  input signal with a THD < 0.1% using ±15 V supplies. The volume control varies between -13 V and 15 V and needs to provide an adjustable gain range of >30dB.

#### 8.2.2 Detailed Design Procedure

Using the linearizing diodes is recommended for most applications, as they greatly reduce the output distortion. It is required that the diode bias current,  $I_D$  be greater than twice the input current,  $I_S$ . As the input voltage has a DC level of 0 V, the Diode Bias input pins are 1 diode drop above 0 V, which is +0.7 V. Tying the bias to the clean V+ supply, results in a voltage drop of 14.3 V across  $R_D$ . Using the recommended 1mA for  $I_D$  is appropriate here, and with VS=+15 V, the voltage drop is 14.3 V, and so using the standard value of 13-k $\Omega$  is acceptable and will provide the desired gain control.

To obtain the <0.1% THD requirement, the differential input voltage must be <60mVpp when the linearizing diodes are used. The input divider on the input will reduce the 1  $V_P$  input to 33m $V_{PP}$ , which is within the desired spec.

Next, set  $I_{BIAS}$ . The Bias Input pins (pins 1 or 16), are 2 diode drops above the negative supply, and therefore  $V_{BIAS} = 2(V_{BE}) + V_{-}$ , which for this application is -13.6 V. To set  $I_{BIAS}$  to 1ma when  $V_{C} = 15$  V requires a 28.6-k $\Omega$ ; 30-k $\Omega$  is a standard value and is used for this application. The gain will be linear with the applied voltage.

#### **Typical Application (continued)**

#### 8.2.3 Application Curve

Figure 18. Signal Amplitude vs Control Voltage

#### 8.3 System Examples

#### 8.3.1 Voltage-Controlled Amplifiers

Figure 20 shows how the linearizing diodes is used in a voltage-controlled amplifier. To understand the input biasing, it is best to consider the  $13-k\Omega$  resistor as a current source and use a Thevenin equivalent circuit as shown in Figure 21. This circuit is similar to Figure 19 and operates the same. The potentiometer in Figure 20 is adjusted to minimize the effects of the control signal at the output.

Figure 19. Linearizing Diodes

For optimum signal-to-noise performance,  $I_{ABC}$  should be as large as possible as shown by the Output Voltage vs Amplifier Bias Current graph. Larger amplitudes of input signal also improve the S/N ratio. The linearizing diodes help here by allowing larger input signals for the same output distortion as shown by the Distortion vs. Differential Input Voltage graph. S/N may be optimized by adjusting the magnitude of the input signal via  $R_{IN}$  (Figure 20) until the output distortion is below the desired level. The output voltage swing can then be set at any level by selecting  $R_{L}$ .

Although the noise contribution of the linearizing diodes is negligible relative to the contribution of the amplifier's internal transistors,  $I_D$  should be as large as possible. This minimizes the dynamic junction resistance of the diodes  $(r_e)$  and maximizes their linearizing action when balanced against  $R_{IN}$ . A value of 1 mA is recommended for  $I_D$  unless the specific application demands otherwise.