#### **General Description**

The EA8103 is a high switching frequency, high efficiency synchronous buck regulator, designed to operate from 2.6V to 6V input voltage range. Built-in low  $R_{\rm DS(ON)}$  high/low side Power-MOSFETS not only reduce external components and has up to 95% efficiency, ideal for 1.2A output current applications. The EA8103 is designed to take into account the light load mode operation and can provide high efficiency over a wide range of the load current. The internal compensation design not only allows users to more simplified application, and can reduce the cost of external components. The EA8103 is available in the SOT-23-5 package and easy to use.

#### **Features**

- ▶ 1uA Ultra Low Quiescent Current

- ▶ Built-in Low R<sub>DS(ON)</sub> Power-MOSFETS

- ► Efficiency Up to 96%

- ▶ 2.6V to 6V Input Voltage Range

- Adjustable Output Voltage Range as Low as to 1.13V

- ► Fixed 1.35MHz Switching Frequency

- ▶ 1.2A Continuous Load Current

- <1uA Shutdown Current</p>

- PFM Mode Operation at Light Load

- Internal Compensation

- Cycle-by-Cycle Current Limit

- Short Circuit Protection

- OTP Protection

- Available in SOT-23-5 Package

## <u>Applications</u>

- Battery Powered Devices

- Handheld Devices

- Wearable Devices.

- ▶ IOT

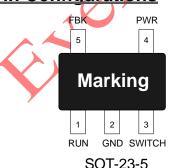

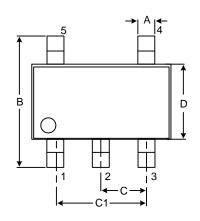

## Pin Configurations

**Datasheet**

### Pin Description

| Pin Name | Function Description                                                                                                                                                                                          | Pin No. |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| RUN      | The device turns on/turns off control input. Drive this pin above 1.5V to turn on, drive this pin below 0.4V to turn off. Don't leave this pin floating.                                                      | 1       |

| GND      | Ground pin.                                                                                                                                                                                                   | 2       |

| SWITCH   | Power switch output pin. Connect SWITCH pin to the switching node of the inductor.                                                                                                                            | 3       |

| PWR      | The EA8103 power input pin. It is recommended to use a 10uF MLCC capacitor between PWR pin and GND pin. The ceramic capacitor must be placed as close to the PWR pin as possible to avoid noise interference. | 74      |

| FBK      | Feedback input. Connect FBK pin and GND pin with voltage dividing resistors to set the output voltage.                                                                                                        | 5       |

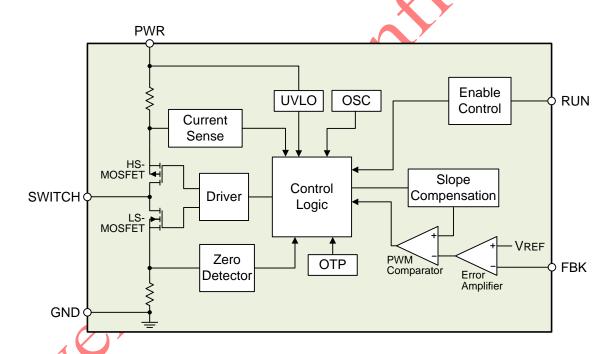

## Function Block Diagram

Figure 1. EA8103 internal function block diagram

Datasheet

# 1uA Ultra Low Quiescent Current 1.2A Sync. Buck Converter

## Absolute Maximum Ratings

| Parameter                                             | Value                             |

|-------------------------------------------------------|-----------------------------------|

| Input Supply Voltage (V <sub>PWR</sub> )              | -0.3V to +7V                      |

| RUN Pin Input Voltage (V <sub>RUN</sub> )             | -0.3V to +7V                      |

| SWITCH Pin Voltage (V <sub>SWITCH</sub> )             | -0.3V to (V <sub>PWR</sub> +0.3V) |

| FBK Pin Voltage (V <sub>FBK</sub> )                   | -0.3V to +7V                      |

| Ambient Temperature operating Range (T <sub>A</sub> ) | -40°C to +85°C                    |

| Maximum Junction Temperature (T <sub>Jmax</sub> )     | +150°C                            |

| Lead Temperature (Soldering, 10 sec)                  | +260°C                            |

| Storage Temperature Range (T <sub>S</sub> )           | -65°C to +150°C                   |

Note (1):Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

Exposure to "Absolute Maximum Ratings" conditions for extended periods may affect device reliability and lifetime.

## Package Thermal Characteristics

| Parameter                                                             | Value   |

|-----------------------------------------------------------------------|---------|

| SOT-23-5 Thermal Resistance ( $\theta_{\text{JC}}$ )                  | 125°C/W |

| SOT-23-5 Thermal Resistance (θ <sub>JA</sub> )                        | 250°C/W |

| SOT-23-5 Power Dissipation at T <sub>A</sub> =25°C (P <sub>Dmax</sub> | 0.5W    |

Note (1):  $P_{Dmax}$  is calculated according to the formula:  $P_{DMax} = (T_{JMAX} - T_A)/\theta_{JA}$ .

## Recommended Operating Conditions

| Parameter                                    | Value           |

|----------------------------------------------|-----------------|

| Input Supply Voltage (V <sub>PWR</sub> )     | +2.6V to +6V    |

| Junction Temperature Range (T <sub>J</sub> ) | -40°C to +125°C |

Datasheet

### Electrical Characteristics

$V_{PWR}$ =5V,  $T_A$ =25°C, unless otherwise noted

| Parameter                                   | Symbol                   | Test Conditions                                             | Min   | Тур  | Max   | Unit |

|---------------------------------------------|--------------------------|-------------------------------------------------------------|-------|------|-------|------|

| Input Voltage                               | $V_{PWR}$                |                                                             | 2.6   |      | 6     | V    |

| Shutdown Supply Current                     | $I_{SD}$                 | $V_{RUN} = 0V$                                              |       | 0.1  | 1     | uA   |

| Quiescent Current                           | IQ                       | $V_{RUN} = 2V, V_{FB} = 1.2V$                               |       | 1    | ,     | uA   |

| UVLO Threshold                              | $V_{UVLO}$               | V <sub>PWR</sub> Rising                                     | 2.2   | 2.35 | 2.5   | V    |

| UVLO Hysteresis                             | $V_{\text{UV-HYS}}$      |                                                             |       | 0.1  | K \   | V    |

| Output Load Current                         | $I_{LOAD}$               |                                                             |       |      | 1.2   | Α    |

| Reference Voltage                           | $V_{REF}$                |                                                             | 1.107 | 1.13 | 1.153 | V    |

| Switching Frequency                         | F <sub>SW</sub>          | $I_{LOAD} = 100 mA$                                         | >     | 1.35 |       | MHz  |

| PMOS On-Resistance                          | R <sub>DS(ON)-P</sub>    | $I_{LOAD} = 100mA$                                          | 2     | 200  |       | mΩ   |

| NMOS On-Resistance                          | R <sub>DS(ON)-N</sub>    | $I_{LOAD} = 100 mA$                                         | X     | 300  |       | mΩ   |

| PMOS Current Limit                          | I <sub>LIM-P</sub>       |                                                             | 1.8   | 2.4  |       | Α    |

| SWITCH Leakage Current                      | I <sub>LEAK-SWITCH</sub> | $V_{PWR} = 5V$ , $V_{RUN} = 0V$ , $V_{SWITCH} = 0V$ or $5V$ | -1    |      | 1     | uA   |

| FBK Leakage Current                         | I <sub>LEAK-FBK</sub>    | $V_{FB} = V_{PWR}$                                          | -1    |      | 1     | uA   |

| RUN Pin Input Low<br>Voltage                | V <sub>RUN-L</sub>       | 20                                                          |       |      | 0.4   | V    |

| RUN Pin Input High<br>Voltage               | V <sub>RUN-H</sub>       |                                                             | 1.5   |      |       | V    |

| Input Over-Voltage<br>Protection Threshold  | V <sub>OVP</sub>         |                                                             |       | 7    |       | V    |

| Input Over-Voltage<br>Protection Hysteresis | V <sub>OVP-HYS</sub>     |                                                             |       | 0.3  |       | V    |

| Thermal Shutdown Threshold                  | $T_{OTP}$                |                                                             |       | 160  |       | °C   |

Note (1): MOSFET on-resistance specifications are guaranteed by correlation to wafer level measurements.

<sup>(2)</sup> Thermal shutdown specifications are guaranteed by correlation to the design and characteristics analysis.

Datasheet

# 1uA Ultra Low Quiescent Current 1.2A Sync. Buck Converter

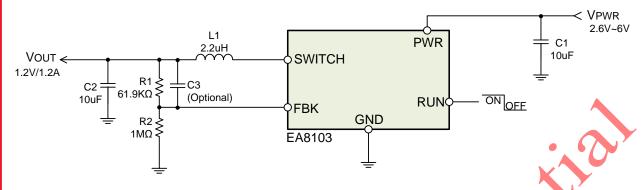

## **Application Circuit Diagram**

Figure 2. Typical application circuit diagram

### Ordering Information

| Part Number | Package Type | Packing Information |

|-------------|--------------|---------------------|

| EA8103T5R   | SOT-23-5     | Tape & Reel / 3000  |

Note (1):"T5": Package type code.

(2):"R": Tape & Reel.

Datasheet

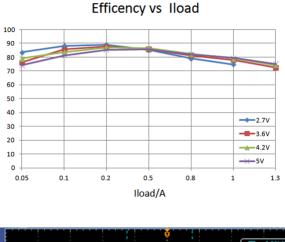

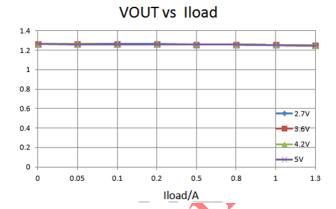

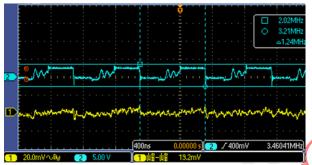

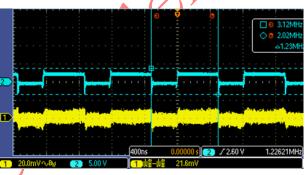

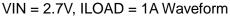

### Typical Operating Characteristics

$V_{PWR}$ =5V,  $V_{OUT}$ =1.2V, L1=2.2uH, C1=C2=10uF,  $T_A$ =25°C, unless otherwise noted

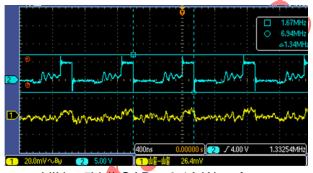

VIN = 2.7V, ILOAD = 0.1A Waveform

VIN = 5V, ILOAD = 0.1A Waveform

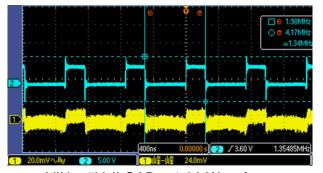

VIN = 5V, ILOAD = 1.2A Waveform

Datasheet

# 1uA Ultra Low Quiescent Current 1.2A Sync. Buck Converter

#### Application Information

**Output Voltage Setting**

The EA8103 output voltage can be set via a resistor divider (R1, R2). The output voltage is calculated by following equation:

$$V_{OUT} = 1.13 \times \frac{R1}{R2} + 1.13 \text{ V}$$

The following table lists common output voltage and the corresponding R1, R2 resistance value for reference.

| Output Voltage | R1 Resistance | R2 Resistance | Tolerance |

|----------------|---------------|---------------|-----------|

| 3.3V           | 965ΚΩ         | 499ΚΩ         | 1%        |

| 1.8V           | 300ΚΩ         | 499ΚΩ         | 1%        |

| 1.5V           | 332ΚΩ         | 1ΜΩ           | 1%        |

| 1.2V           | 61.9ΚΩ        | 1ΜΩ 🛕 🙋       | 1%        |

#### Input / Output Capacitors Selection

The input capacitors are used to suppress the noise amplitude of the input voltage and provide a stable and clean DC input to the device. Because the ceramic capacitor has low ESR characteristic, so it is suitable for input capacitor use. It is recommended to use X5R or X7R MLCC capacitors in order to have better temperature performance and smaller capacitance tolerance. In order to suppress the output voltage ripple, the MLCC capacitor is also the best choice. The suggested part numbers of input / output capacitors are as follows:

| Vendor | Part Number    | Capacitance | Edc | Parameter | Size |

|--------|----------------|-------------|-----|-----------|------|

| TDK    | C2012X5R1A106K | 10uF        | 10V | X5R       | 0805 |

| TDK    | C3216X7R1A106K | 10uF        | 10V | X7R       | 1206 |

#### **Output Inductor Selection**

The output inductor selection mainly depends on the amount of ripple current through the inductor  $\Delta I_{L}$ . Large  $\Delta I_{L}$  will cause larger output voltage ripple and loss, but the user can use a smaller inductor to save cost and space. On the contrary, the larger inductance can get smaller  $\Delta I_{L}$  and thus the smaller output voltage ripple and loss. But it will increase the space and the cost. The inductor value can be calculated as:

$$L = \frac{V_{\text{PWR}} - V_{\text{OUT}}}{\Delta I_{\text{L}} \times F_{\text{SW}}} \times \frac{V_{\text{OUT}}}{V_{\text{PWR}}}$$

For most applications, 1uH to 4.7uH inductors are suitable for EA8103.

#### PCB Layout Recommendations

For EA8103 PCB layout considerations, please refer to the following suggestions in order to get good performance.

- High current path traces need to be widened.

- Place the input capacitors as close as possible to the PWR pin to reduce noise interference.

- Keep the feedback path (from V<sub>OUT</sub> to FBK) away from the noise node (ex. SWITCH). SWITCH is a high current noise node. Complete the layout by using short and wide traces.

Datasheet

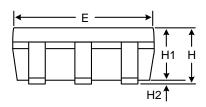

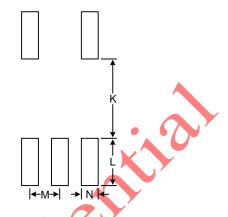

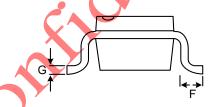

## Package Information

SOT-23-5 Package

Top View

Side View

Recommended Layout Pattern

Front View

| U | nit: | mm |  |

|---|------|----|--|

| Symbol   | Dimension |      | Symbol   | Dimension |

|----------|-----------|------|----------|-----------|

| Syllibol | Min       | Max  | Syllibol | Тур       |

| Α        | 0.25      | 0.52 | K        | 1.40      |

| В        | 2.59      | 3.01 | L        | 1.40      |

| С        | 0.85      | 1.05 | М        | 0.95      |

| C1       | 1.70      | 2.10 | N        | 0.65      |

| D        | 1.40      | 1.80 |          |           |

| Е        | 2,70      | 3.10 |          |           |

| F        | 0.30      | 0.62 |          |           |

| G        | 0.08      | 0.25 |          |           |

| H        | 0.89      | 1.35 |          |           |

| H1)      | 0.89      | 1.20 |          |           |

| H2       | 0.00      | 0.15 |          |           |