# EiceDRIVER<sup>TM</sup> SIL

# High Voltage IGBT Driver for Automotive Applications

# 1EDI2004AS Single Channel Isolated Driver for Inverter Systems AA Step

## 1 Overview

## **Quality Requirement Category: Automotive**

The 1EDI2004AS is a high-voltage IGBT gate driver designed for automotive motor drives above 5 kW. The 1EDI2004AS is based on Infineon's Coreless Transformer (CLT) technology, providing galvanic insulation between low voltage and high voltage domains. The device has been designed to support 400 V, 600 V and 1200 V IGBT technologies.

The 1EDI2004AS can be connected on the low voltage side ("primary" side) to 5 V logic. A standard SPI interface allows the logic to configure and to control the advanced functions implemented in the driver.

On the high voltage side ("secondary" side), the 1EDI2004AS is dimensioned to drive an external booster stage or directly small IGBTs. Short propagation delays and controlled internal tolerances lead to minimal distortion of the PWM signal.

A large panel of safety-related functions has been implemented in the 1EDI2004AS, in order to support functional safety requirements at system level (as per ISO 26262). Besides, those integrated features ease the implementation of Active Short Circuit (ASC) strategies.

The 1EDI2004AS can be used optimally with Infineon's 1EBN100XAE "EiceDRIVER™ Boost" booster stage family.

1

### **Features**

The following features are supported by the 1EDI2004AS:

- Single Channel IGBT Driver.

- On-chip galvanic insulation (up to 6kV).

- Support of 600 V and 1200 V IGBT technologies.

- Low propagation delay and minimal PWM distortion.

- Support of 5 V logic levels (primary side).

- 16-bit Standard SPI interface (up to 2 MBaud) with daisy chain support (primary side).

- Enable input pin (primary side).

- Pseudo-differential inputs for critical signals (primary side).

- Power-On Reset pin (primary side).

- Debug mode.

### Overview

- · Pulse Suppressor.

- Fully Programmable Active Clamping Inhibit signal (secondary side).

- · Optimal support of EiceBoost functions.

- Operation with unipolar secondary supply possible (V<sub>FF2</sub>=V<sub>GND2</sub>).

- Fullfil BISS standard 2.0 (Class 3) for conducted emissions.

- 36-pin PG-DSO-36 green package.

- Automotive qualified (as per AEC Q100).

### Safety Relevant Features

- Desaturation monitoring, with selectable blanking time in runtime.

- · Overcurrent protection.

- Fully programmable Two-Level Turn-Off (static programming).

- Automatic Emergency Turn-Off in failure case.

- Externally triggered disabling of the output stage (tristate).

- Under- and over-voltage supervision of the secondary power supplies.

- OVLO2 failure reaction can be modified in runtime.

- NFLTA and NFLTB notification pins for fast system response time (primary side).

- Safe internal state machine.

- Weak Turn-On functionality.

- Internal clock monitoring.

- · Gate signal monitoring comparators.

- Individual error and status flags readable via SPI.

- Support for Active Short Circuit strategies.

- · Full diagnostic capability.

- · In-application testability of safety critical functions.

- Suitable for systems up to ASIL D requirements (as per ISO 26262).

- Compliant to ISO 26262 standard ASIL A.

### **Target Applications**

- Inverters for automotive Hybrid Electric Vehicles (HEV) and Electric Vehicles (EV).

- High Voltage DC/DC converter.

- Industrial Drive.

| Туре       | Package      | Marking    |

|------------|--------------|------------|

| 1EDI2004AS | PG-DSO-36-63 | 1EDI2004AS |

| Revision Histor  | Revision History                                              |  |  |

|------------------|---------------------------------------------------------------|--|--|

| Page or Item     | Page or Item Subjects (major changes since previous revision) |  |  |

| Rev 1.8, 2018-12 | Rev 1.8, 2018-12-19                                           |  |  |

| All,             | Initial data sheet.                                           |  |  |

### **Trademarks of Infineon Technologies AG**

AURIX $^{\text{TM}}$ , C166 $^{\text{TM}}$ , Canpak $^{\text{TM}}$ , CIPOS $^{\text{TM}}$ , CIPURSE $^{\text{TM}}$ , EconoPack $^{\text{TM}}$ , CoolMos $^{\text{TM}}$ , CoolSet $^{\text{TM}}$ , CORECONTROL $^{\text{TM}}$ , CROSSAVE $^{\text{TM}}$ , DAVE $^{\text{TM}}$ , EasyPIM $^{\text{TM}}$ , EconoBRIDGE $^{\text{TM}}$ , EconoDUAL $^{\text{TM}}$ , EconoPIM $^{\text{TM}}$ , EiceDRIVER $^{\text{TM}}$ , eupec $^{\text{TM}}$ , FCOS $^{\text{TM}}$ , HITFET $^{\text{TM}}$ , HybridPack $^{\text{TM}}$ , ISOFACE $^{\text{TM}}$ , IsoPack $^{\text{TM}}$ , MiPaQ $^{\text{TM}}$ , ModSTACK $^{\text{TM}}$ , my-d $^{\text{TM}}$ , NovalithIC $^{\text{TM}}$ , OptiMoS $^{\text{TM}}$ , ORIGA $^{\text{TM}}$ , PRIMARION $^{\text{TM}}$ , PrimePack $^{\text{TM}}$ , PrimeSTACK $^{\text{TM}}$ , PROFET $^{\text{TM}}$ , RASIC $^{\text{TM}}$ , ReverSave $^{\text{TM}}$ , SatRIC $^{\text{TM}}$ , SIEGET $^{\text{TM}}$ , SINDRION $^{\text{TM}}$ , SmartLewIS $^{\text{TM}}$ , SOLID FLASH $^{\text{TM}}$ , TEMPFET $^{\text{TM}}$ , thinQ! $^{\text{TM}}$ , TRENCHSTOP $^{\text{TM}}$ , TriCore $^{\text{TM}}$ .

#### Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2011-02-24

## **Table of Contents**

# **Table of Contents**

| 1         | Overview                                          | 1    |

|-----------|---------------------------------------------------|------|

|           | Table of Contents                                 | 4    |

|           | List of Figures                                   | 7    |

|           | List of Tables                                    | 8    |

| 2         | Functional Description                            | . 10 |

| 2.1       | Introduction                                      | . 10 |

| 2.2       | Pin Configuration and Functionality               | . 11 |

| 2.2.1     | Pin Configuration                                 | . 11 |

| 2.2.2     | Pin Functionality                                 |      |

| 2.2.2.1   | Primary Side                                      | . 13 |

| 2.2.2.2   | Secondary Side                                    | . 14 |

| 2.2.2.3   | Pull Devices                                      | . 15 |

| 2.3       | Block Diagram                                     | . 17 |

| 2.4       | Functional Block Description                      | . 18 |

| 2.4.1     | Power Supplies                                    | . 18 |

| 2.4.2     | Clock Domains                                     |      |

| 2.4.3     | PWM Input Stage                                   | . 19 |

| 2.4.4     | SPI Interface                                     |      |

| 2.4.4.1   | Overview                                          | . 21 |

| 2.4.4.2   | General Operation                                 |      |

| 2.4.4.3   | Definitions                                       |      |

| 2.4.4.4   | SPI Data Integrity Support                        |      |

| 2.4.4.4.1 | Parity Bit                                        |      |

| 2.4.4.4.2 | SPI Error                                         | . 26 |

| 2.4.4.5   | Protocol Description                              | . 27 |

| 2.4.4.5.1 | Command Catalog                                   | . 27 |

| 2.4.4.5.2 | Word Convention                                   | . 27 |

| 2.4.4.5.3 | ENTER CMODE Command                               | . 28 |

| 2.4.4.5.4 | ENTER_VMODE Command                               | . 28 |

| 2.4.4.5.5 | EXIT_CMODE Command                                | . 28 |

| 2.4.4.5.6 | NOP Command                                       | . 29 |

| 2.4.4.5.7 | READ Command                                      | . 29 |

| 2.4.4.5.8 | WRITEH                                            | . 29 |

| 2.4.4.5.9 | WRITEL                                            | . 30 |

| 2.4.5     | Operating Modes                                   | . 31 |

| 2.4.5.1   | General Operation                                 | . 31 |

| 2.4.5.2   | Definitions                                       | . 32 |

| 2.4.5.2.1 | Events and State Transitions                      | . 32 |

| 2.4.5.2.2 | Emergency Turn-Off Sequence                       | . 33 |

| 2.4.5.2.3 | Ready, Disabled, Enabled and Active State         | . 33 |

| 2.4.5.3   | Operation Modes Description                       | . 34 |

| 2.4.5.4   | Activating the device after reset                 | . 36 |

| 2.4.5.5   | Activating the device after an Event Class A or B | . 36 |

| 2.4.5.6   | Debug Mode                                        | . 36 |

| 2.4.6     | Driver Functionality                              | . 37 |

| 2.4.6.1   | Overview                                          | . 37 |

| 2.4.6.2   | Switching Sequence Description                    | . 41 |

## **Table of Contents**

| 2.4.6.3    | Active Miller Clamping Transistor Clamping          |    |

|------------|-----------------------------------------------------|----|

| 2.4.6.4    | Disabling the output stage                          |    |

| 2.4.6.5    | Passive Clamping                                    |    |

| 2.4.7      | Fault Notifications                                 |    |

| 2.4.8      | EN Signal Pin                                       |    |

| 2.4.9      | Internal Supervision                                |    |

| 2.4.9.1    | Lifesign watchdog                                   |    |

| 2.4.9.2    | Oscillator Monitoring                               |    |

| 2.4.9.3    | Memory Supervision                                  |    |

| 2.4.9.4    | Hardware Failure Behavior                           |    |

| 2.4.10     | Reset Events                                        |    |

| 2.4.11     | Operation in Configuration Mode                     |    |

| 2.4.11.1   | Static Configuration Parameters                     |    |

| 2.4.11.1.1 | g                                                   |    |

| 2.4.11.1.2 |                                                     |    |

| 2.4.11.1.3 |                                                     |    |

| 2.4.11.1.4 |                                                     |    |

| 2.4.11.1.5 |                                                     |    |

| 2.4.11.1.6 |                                                     |    |

| 2.4.11.1.7 | g                                                   |    |

| 2.4.11.1.8 |                                                     |    |

| 2.4.11.1.9 |                                                     |    |

| 2.4.11.1.1 |                                                     |    |

| 2.4.11.2   | Delay Calibration                                   |    |

|            | Protection and Diagnostics                          |    |

| 3.1        | Supervision Overview                                |    |

|            | Protection Functions: Category A                    |    |

| 3.2.1      | Desaturation Protection                             |    |

| 3.2.2      | Overcurrent Protection                              |    |

| 3.2.3      | External Enable                                     |    |

|            | Protection Functions: Category B                    |    |

| 3.3.1      | Power Supply Voltage Monitoring                     |    |

|            | Protection Functions: Category C                    |    |

| 3.4.1      | Shoot Through Protection function                   |    |

| 3.4.2      | Gate Monitoring                                     |    |

| 3.4.3      | SPI Error Detection                                 |    |

| 3.4.4      | Active Short Circuit Support                        |    |

|            | Protection Functions: Category D                    |    |

| 3.5.1      | Operation in Verification Mode and Weak Active Mode |    |

| 3.5.2      | Weak Turn On                                        |    |

| 3.5.3      | DESAT Supervision Level 1                           |    |

| 3.5.4      | DESAT Supervision Level 2                           |    |

| 3.5.5      | DESAT Supervision Level 3                           |    |

| 3.5.6      | OCP Supervision Level 1                             |    |

| 3.5.7      | OCP Supervision Level 3                             |    |

| 3.5.8      | Power Supply Monitoring Supervision                 |    |

| 3.5.9      | Internal Clock Supervision                          | 72 |

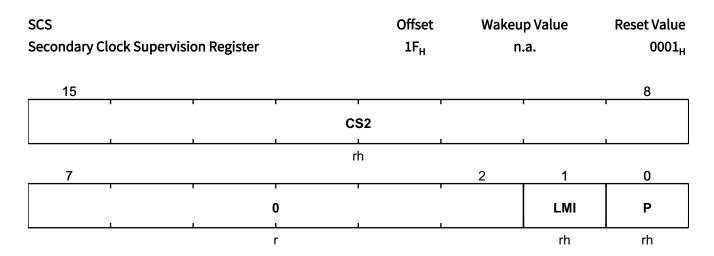

| 4          | Register Description                                | 73 |

|            | Primary Register Description                        |    |

|            | Secondary Registers Description                     |    |

|            |                                                     |    |

## **Table of Contents**

| 4.3    | Read / Write Address Ranges 1            | 116 |

|--------|------------------------------------------|-----|

| 5      | Specification 1                          | 118 |

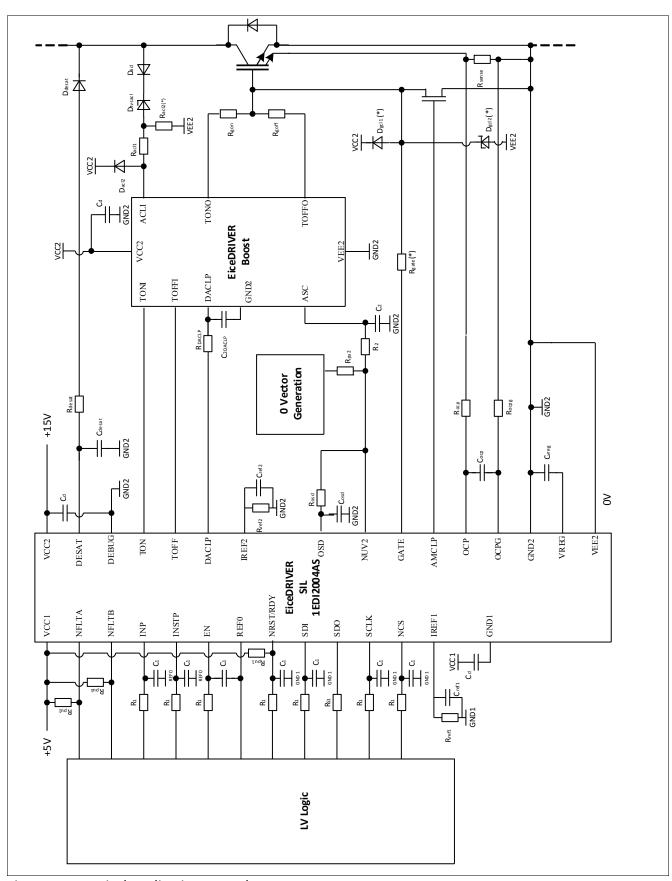

| 5.1    | Typical Application Circuit              |     |

| 5.2    | Absolute Maximum Ratings                 |     |

| 5.3    | Operating range                          |     |

| 5.4    | Thermal Characteristics                  |     |

| 5.5    | Electrical Characteristics               |     |

| 5.5.1  | Power Supply                             | 123 |

| 5.5.2  | Internal Oscillators                     |     |

| 5.5.3  | Primary I/O Electrical Characteristics   | 125 |

| 5.5.4  | Secondary I/O Electrical Characteristics |     |

| 5.5.5  | Switching Characteristics                |     |

| 5.5.6  | Desaturation Protection                  |     |

| 5.5.7  | Overcurrent Protection                   |     |

| 5.5.8  | Error Detection Timing                   |     |

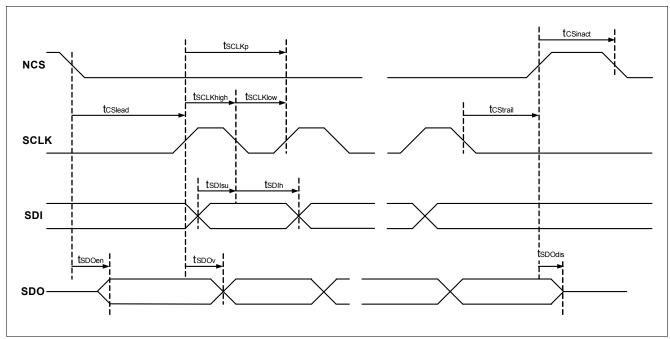

| 5.5.9  | SPI Interface                            |     |

| 5.5.10 | Insulation Characteristics               |     |

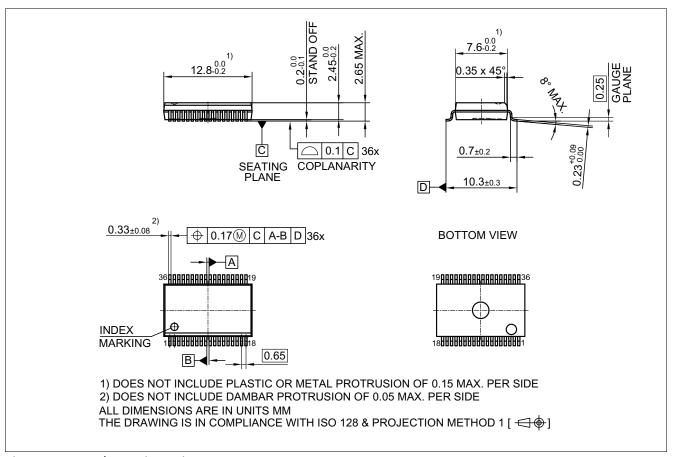

| 6      | Package Information                      | 136 |

## **List of Figures**

# **List of Figures**

| igure 1  | Pin Configuration                                   | 11 |

|----------|-----------------------------------------------------|----|

| igure 2  | Block Diagram                                       | 17 |

| igure 3  | PWM Input Stage                                     | 19 |

| igure 4  | STP: Inhibition Time Definition                     | 20 |

| igure 5  | STP: Example of Operation                           | 20 |

| igure 6  | SPI Regular Bus Topology                            | 22 |

| igure 7  | SPI Daisy Chain Bus Topology                        | 23 |

| igure 8  | Response Answer Principle - Daisy Chain Topology    | 25 |

| igure 9  | Response Answer Principle - Regular Topology        | 25 |

| igure 10 | SPI Commands Overview                               | 27 |

| igure 11 | Operating Modes State Diagram                       | 31 |

| igure 12 | Output Stage Diagram of Principle                   | 37 |

| igure 13 | TTOFF: Principle of Operation                       | 39 |

| igure 14 | TTOFF: pulse suppressor aborting a turn-on sequence | 40 |

| igure 15 | Idealized Switching Sequence (Regular Turn-Off)     | 42 |

| igure 16 | AMCLP operation                                     | 43 |

| igure 17 | DESAT Function: Diagram of Principle                | 56 |

| igure 18 | DESAT Operation                                     | 57 |

| igure 19 | DESAT Operation with DESAT clamping enabled         | 58 |

| igure 20 | OCP Function: Principle of Operation                | 59 |

| igure 21 | Power Supply Supervision Function                   | 61 |

| igure 22 | Shoot Through Protection: Principle of Operation    | 63 |

| igure 23 | ASC Strategy Support                                | 65 |

| igure 24 | Idealized Weak Turn-On Sequence                     | 67 |

| igure 25 | Typical Application Example                         | 20 |

| igure 26 | SPI Interface Timing                                | 34 |

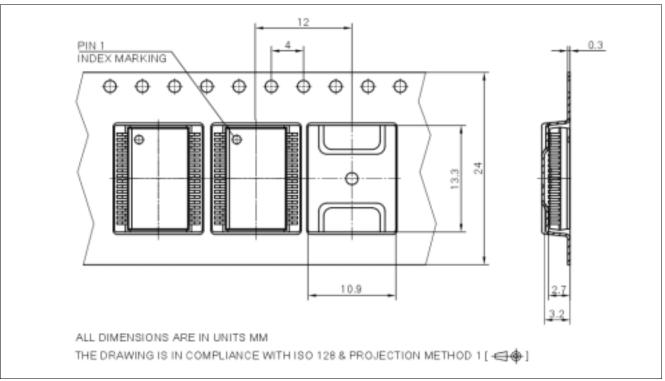

| igure 27 | Package Dimensions                                  | 36 |

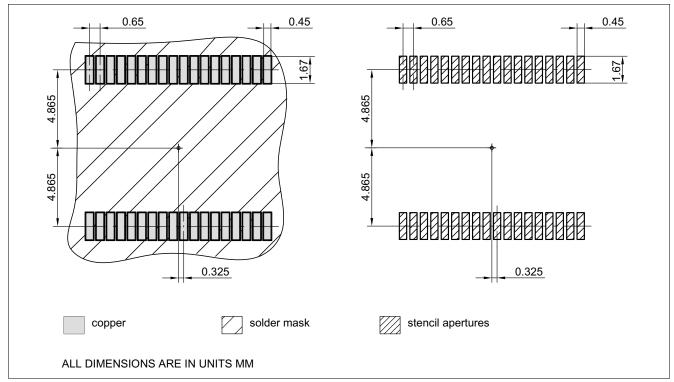

| igure 28 | Recommended Footprint                               | 36 |

| igure 29 | Packing Information (Tape & Reel)                   | 37 |

|          |                                                     |    |

## **List of Tables**

# **List of Tables**

| Table 1  | Pin Configuration                                        | . 11 |

|----------|----------------------------------------------------------|------|

| Table 2  | Internal pull devices                                    | . 15 |

| Table 3  | SPI Command Catalog                                      | . 27 |

| Table 4  | Word Convention                                          | . 28 |

| Table 5  | ENTER_CMODE request and answer messages                  | . 28 |

| Table 6  | ENTER_VMODE request and answer messages                  | . 28 |

| Table 7  | EXIT_CMODE request and answer messages                   | . 29 |

| Table 8  | NOP request and answer messages                          | . 29 |

| Table 9  | READ request and answer messages                         | . 29 |

| Table 10 | WRITEH request and answer messages                       | . 30 |

| Table 11 | WRITEL request and answer messages                       | . 30 |

| Table 12 | Failure Notification Clearing                            | . 45 |

| Table 13 | System Supervision Overview                              | . 47 |

| Table 14 | Failure Events Summary                                   | . 48 |

| Table 15 | Reset Events Summary                                     |      |

| Table 16 | Pin behavior (primary side) in case of reset condition   | . 50 |

| Table 17 | Pin behavior (secondary side) in case of reset condition | . 51 |

| Table 18 | Safety Related Functions                                 | . 54 |

| Table 19 | DESAT Protection Overview                                | . 56 |

| Table 20 | OCP Function Overview                                    | . 58 |

| Table 21 | External Enable Function Overview                        |      |

| Table 22 | Power Supply Voltage Monitoring Overview                 | . 61 |

| Table 23 | STP Overview                                             | . 63 |

| Table 24 | Gate Monitoring Overview                                 | . 64 |

| Table 25 | SPI Error Detection Overview                             |      |

| Table 26 | Active Short Circuit Support Overview                    |      |

| Table 27 | DESAT Supervision Level 1 Overview                       | . 68 |

| Table 28 | DESAT Supervision Level 2 Overview                       |      |

| Table 29 | DESAT Supervision Level 3 Overview                       |      |

| Table 30 | OCP Supervision Level 1 Overview                         |      |

| Table 31 | OCP Supervision Level 3 Overview                         |      |

| Table 32 | Power Supply Monitoring Supervision Overview             |      |

| Table 33 | Primary Clock Supervision Overview                       |      |

| Table 34 | Register Address Space                                   |      |

| Table 35 | Register Overview                                        |      |

| Table 36 | Bit Access Terminology                                   |      |

| Table 37 | Read Access Validity                                     |      |

| Table 38 | Write Access Validity                                    |      |

| Table 39 | Component Values                                         |      |

| Table 40 | Absolute Maximum Ratings                                 |      |

| Table 41 | Operating Conditions                                     |      |

| Table 42 | Thermal Characteristics                                  |      |

| Table 43 | Power Supplies Characteristics                           |      |

| Table 44 | Internal Oscillators                                     |      |

| Table 45 | Electrical Characteristics for Pins: INP, INSTP, EN      |      |

| Table 46 | Electrical Characteristics for Pins: SCLK, SDI, NCS      |      |

| Table 47 | Electrical Characteristics for Pins: NRST/RDY            |      |

| Table 48 | Electrical Characteristics for Pins: SDO                 |      |

| Table 49 | Electrical Characteristics for Pins: NFLTA, NFLTB        | 126  |

## **List of Tables**

| Table 50 | Electrical Characteristics for Pins: TON, TOFF & GATE                           | 127 |

|----------|---------------------------------------------------------------------------------|-----|

| Table 51 | Electrical Characteristics for Pins: OSD, DEBUG                                 | 127 |

| Table 52 | Electrical Characteristics for Pin: NUV2                                        | 127 |

| Table 53 | Electrical Characteristics for Pins: DACLP                                      | 128 |

| Table 54 | Electrical Characteristics for Pins: AMCLP                                      | 128 |

| Table 55 | Electrical Characteristics for Pin: VREG                                        | 129 |

| Table 56 | Switching Characteristics                                                       | 130 |

| Table 57 | DESAT characteristics                                                           | 132 |

| Table 58 | OCP characteristics                                                             | 132 |

| Table 59 | Error Detection Timing                                                          | 133 |

| Table 60 | SPI Interface Characteristics                                                   | 134 |

| Table 61 | Isolation Characteristics referring to DIN EN 60747-5-2 (VDE 0884 - 10):2006-12 | 135 |

| Table 62 | Isolation Characteristics referring to III 1577                                 | 135 |

## **Functional Description**

## 2 Functional Description

### 2.1 Introduction

The 1EDI2004AS is an advanced single channel IGBT driver that can also be used for driving power MOS devices. The device has been developed in order to optimize the design of high performance safety relevant automotive systems.

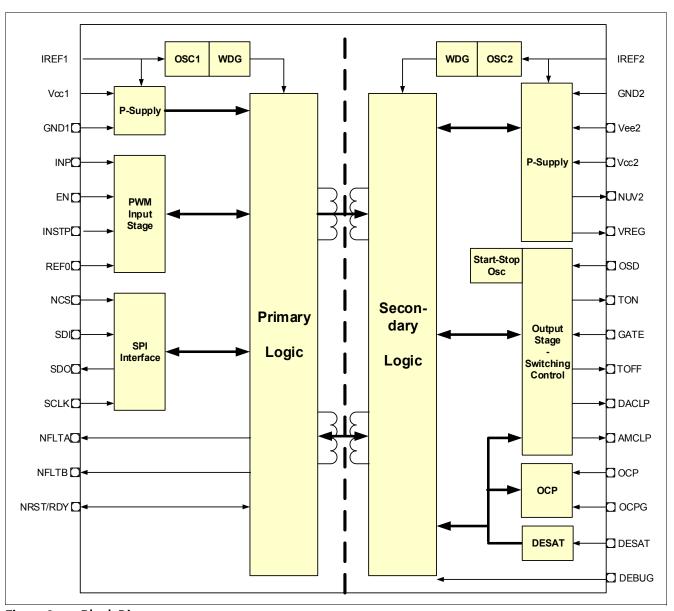

The device is based on Infineon's Coreless Transformer Technology and consist of two chips separated by a galvanic isolation. The low voltage (primary) side can be connected to a standard 5 V logic. The high voltage (secondary) side is in the DC-link voltage domain.

Internally, the data transfers are ensured by two independent communication channels. One channel is dedicated to transferring the ON and OFF information of the PWM input signal only. This channel is unidirectional (from primary to secondary). Because this channel is dedicated to the PWM information, latency time and PWM distortion are minimized. The second channel is bidirectional and is used for all the other data transfers (e.g. status information, etc).

The 1EDI2004AS supports advanced functions in order to optimize the switching behavior of the IGBT. Furthermore, it supports several monitoring and protection functions, making it suitable for systems having to fulfill ASIL requirements (as per ISO 26262).

**Functional Description**

# 2.2 Pin Configuration and Functionality

# 2.2.1 Pin Configuration

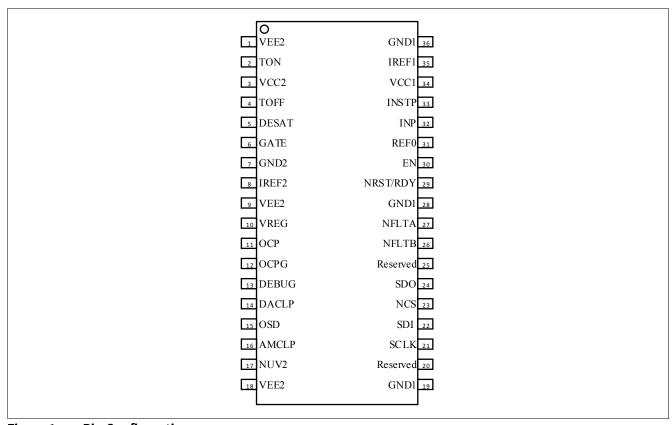

Figure 1 Pin Configuration

Table 1 Pin Configuration

| Pin<br>Number | Symbol | I/O    | Voltage Class | Function                                |

|---------------|--------|--------|---------------|-----------------------------------------|

| 1,9,18        | VEE2   | Supply | Supply        | Negative Power Supply <sup>1)</sup> .   |

| 2             | TON    | Output | 15V Secondary | Turn-On Output. <sup>2)</sup>           |

| 3             | VCC2   | Supply | Supply        | Positive Power Supply.                  |

| 4             | TOFF   | Output | 15V Secondary | Turn-Off Output. <sup>2)</sup>          |

| 5             | DESAT  | Input  | 15V Secondary | Desaturation Protection Input.          |

| 6             | GATE   | Input  | 15V Secondary | Gate Monitoring Input.                  |

| 7             | GND2   | Ground | Ground        | Ground.                                 |

| 8             | IREF2  | Input  | 5V Secondary  | External Reference Input.               |

| 10            | VREG   | Output | 5V Secondary  | Reference Output Voltage. <sup>2)</sup> |

| 11            | ОСР    | Input  | 5V Secondary  | Over Current Protection.                |

| 12            | OCPG   | Ground | Ground        | Ground for the OCP function,            |

| 13            | DEBUG  | Input  | 5V Secondary  | Debug Input.                            |

## **Functional Description**

Table 1

Pin Configuration (cont'd)

| Pin<br>Number | Symbol   | I/O          | Voltage Class | Function                                                                                             |

|---------------|----------|--------------|---------------|------------------------------------------------------------------------------------------------------|

| 14            | DACLP    | Output       | 5V Secondary  | Active Clamping Disable Output.(push-pull) <sup>2)</sup>                                             |

| 15            | OSD      | Input        | 5V Secondary  | Output Stage Disable Input.                                                                          |

| 16            | AMCLP    | Output       | 5V Secondary  | Active Miller Clamping control output. (push-pull) <sup>2)</sup>                                     |

| 17            | NUV2     | Output       | 5V Secondary  | V <sub>CC2</sub> not valid notification output.<br>(open drain) <sup>2)</sup>                        |

| 19, 28, 36    | GND1     | Ground       | Ground        | Ground <sup>3)</sup> .                                                                               |

| 20            | Reserved | Reserved     | Reserved      | Reserved. This pin shall be connected to GND1.                                                       |

| 21            | SCLK     | Input        | 5V Primary    | SPI Serial Clock Input.                                                                              |

| 22            | SDI      | Input        | 5V Primary    | SPI Serial Data Input.                                                                               |

| 23            | NCS      | Input        | 5V Primary    | SPI Chip Select Input (low active).                                                                  |

| 24            | SDO      | Output       | 5V Primary    | SPI Serial Data Output. (push-pull) <sup>2)</sup>                                                    |

| 25            | Reserved | Reserved     | Reserved      | Reserved. This pin shall be connected to GND1.                                                       |

| 26            | NFLTB    | Output       | 5V Primary    | Fault B Output (low active, open drain). <sup>2)</sup>                                               |

| 27            | NFLTA    | Output       | 5V Primary    | Fault A Output (low active, open drain). <sup>2)</sup>                                               |

| 29            | NRST/RDY | Input/Output | 5V Primary    | Reset Input (low active, open drain). This signal notifies that the device is "ready". <sup>2)</sup> |

| 30            | EN       | Input        | 5V Primary    | Enable Input.                                                                                        |

| 31            | REF0     | Ref. Ground  | Ground        | Reference Ground for signals INP, INSTP, EN.                                                         |

| 32            | INP      | Input        | 5V Primary    | Positive PWM Input.                                                                                  |

| 33            | INSTP    | Input        | 5V Primary    | Monitoring PWM Input.                                                                                |

| 34            | VCC1     | Supply Input | Supply        | Positive Power Supply.                                                                               |

| 35            | IREF1    | Input        | 5V Primary    | External Reference Input.                                                                            |

<sup>1)</sup> All VEE2 pins must be connected together.

<sup>2)</sup> Pin is not protected against short circuit to respective supply or ground potential.

<sup>3)</sup> All GND1 pins must be connected together.

## **Functional Description**

## 2.2.2 Pin Functionality

## 2.2.2.1 Primary Side

### **GND1**

Ground connection for the primary side.

### VCC1

5V power supply for the primary side (referring to GND1).

### **INP**

Non-inverting PWM input of the driver. The internal structure of the pad makes the IC robust against glitches. An internal weak pull-down resistor to  $V_{REFO}$  drives this input to Low state in case the pin is floating.

### **INSTP**

Monitoring PWM input for shoot through protection. The internal structure of the pad makes the IC robust against glitches. An internal weak pull-down resistor to  $V_{REF0}$  drives this input to Low state in case the pin is floating.

### REF0

Reference Ground signal for the signals INP, INSTP, EN. This pin should be connected to the ground signal of the logic issuing those signals.

### **EN**

Enable Input Signal. This signal allows the logic on the primary side to turn-off and deactivate the device. An internal weak pull-down resistor to  $V_{REF0}$  drives this input to Low state in case the pin is floating. This pin reacts on logic levels.

### **NFLTA**

Open-Drain Output signal used to report major failure events (Event Class A). In case of an error event, **NFLTA** is driven to Low state. This pin shall be connected externally to  $V_{CC1}$  with a pull-up resistance.

### **NFLTB**

Open-Drain Output signal used to report major failure events (Event Class B) and reset events. In case of an error event, **NFLTB** is driven to Low state. This pin shall be connected externally to  $V_{CC1}$  with a pull-up resistance.

### **SCLK**

Serial Clock Input for the SPI interface. An internal weak pull-up device to V<sub>CC1</sub> drives this input to high state in case the pin is floating.

### **SDO**

Serial Data Output (push-pull) for the SPI interface.

## **Functional Description**

### **SDI**

Serial Data Input for the SPI interface. An internal weak pull-up device to V<sub>CC1</sub> drives this input to high state in case the pin is floating.

### **NCS**

Chip Select input for the SPI interface. This signal is low active. An internal weak pull-up device to V<sub>CC1</sub> drives this input to High state in case the pin is floating.

### IREF1

Reference input of the primary chip. This pin shall be connected to V<sub>GND1</sub> via an external resistor.

### **NRST/RDY**

Open drain reset input. This signal is low-active. When a valid signal is received on this pin, the device is brought in its default state. This signal is also used as a "ready notification". A high level on this pin indicates that the primary chip is functional.

## 2.2.2.2 Secondary Side

### VEE2

Negative power supply for the secondary side, referring to V<sub>GND2</sub>.

### VCC2

Positive power supply for the secondary side, referring to  $V_{GND2}$ .

### **GND2**

Reference ground for the secondary side.

### **DESAT**

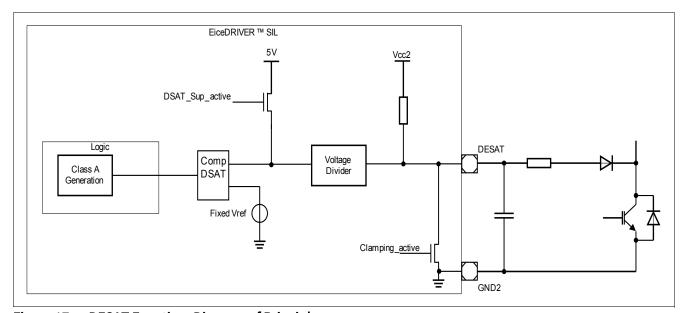

Desaturation Protection input pin. The function associated with this pin monitors the  $V_{CE}$  voltage of the IGBT. An internal pull-up resistor to  $V_{CC2}$  drives this signal to High level in case it is floating.

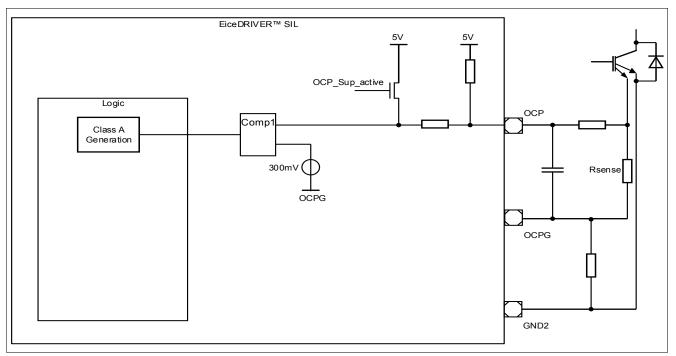

## **OCP**

Over Current Protection input pin. The function associated with this pin monitors the voltage across a sensing resistance located on the auxiliary path of a Current Sense IGBT. An internal weak pull-up resistor to the internal 5V reference drives this input to High state in case the pin is floating.

### **OCPG**

Over Current Protection Ground.

### TON

Output pin for turning on the IGBT.

### **TOFF**

Output pin for turning off the IGBT.

## **Functional Description**

### **GATE**

Input pin used to monitor the IGBT gate voltage.

### **OSD**

Output Stage Disable input. A High Level on this pin tristates the output stage. An internal weak pull-down resistor to  $V_{GND2}$  drives this input to Low state in case the pin is floating.

### **DACLP**

Output pin used to disable the active clamping function of the booster.

### **DEBUG**

Debug input pin. This pin is latched at power-up. When a High level is detected on this pin, the device enters a special mode where it can be operated without SPI interface. This feature is for development purpose only. This pin should normally be tied to  $V_{GND2}$ . An internal weak pull-down resistor to  $V_{GND2}$  drives this input to Low state in case the pin is floating.

### IREF2

Reference input of the secondary chip. This pin shall be connected to V<sub>GND2</sub> via an external resistor.

### **VREG**

Reference Output voltage. This pin shall be connected to an external capacitance to V<sub>GND2</sub>.

### NUV2

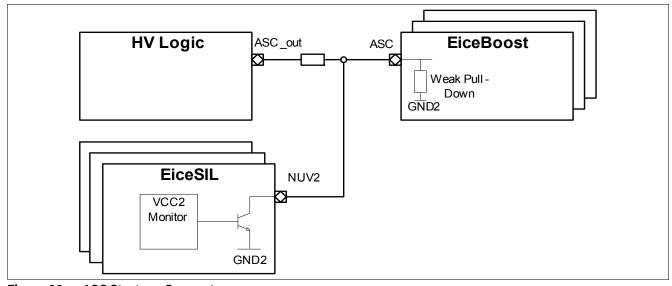

$V_{CC2}$  not valid notification signal (Open Drain). This signal drives a low level when  $V_{CC2}$  is below  $V_{UVLO2L}$  or when the internal 5V digital supply is not valid. When both supplies are valid, this pin is in high impedance state. This pin shall be connected externally to a 5V reference with a pull-up resistance to ensure level read-out over the respective register. The pin can be connected also to respective ground potential (This enables usage together with OSD pin).

### **AMCLP**

Active Miller Clamping External Enable Output. The signal goes to High level when  $V_{GATE}$  is lower than  $V_{GATE1}$  during turn-off.

### 2.2.2.3 Pull Devices

Some of the pins are connected internally to pull-up or pull-down devices. This is summarized in Table 2.

Table 2 Internal pull devices

| Signal | Device                              |

|--------|-------------------------------------|

| INP    | Weak pull down to V <sub>REF0</sub> |

| INSTP  | Weak pull down to V <sub>REF0</sub> |

| EN     | Weak pull down to V <sub>REFO</sub> |

| SCLK   | Weak pull up to V <sub>CC1</sub>    |

| SDI    | Weak pull up to V <sub>CC1</sub>    |

| NCS    | Weak pull up to V <sub>CC1</sub>    |

## **Functional Description**

#### Internal pull devices Table 2

| Signal | Device                                |

|--------|---------------------------------------|

| DESAT  | Weak pull up to V <sub>CC2</sub>      |

| OSD    | Weak pull down to V <sub>GND2</sub>   |

| ОСР    | Weak pull up to 5V internal reference |

| DEBUG  | Weak pull down to V <sub>GND2</sub>   |

**Functional Description**

# 2.3 Block Diagram

Figure 2 Block Diagram

# infineon

## **Functional Description**

## 2.4 Functional Block Description

## 2.4.1 Power Supplies

On the primary side, the 1EDI2004AS needs a single 5Vsupply source V<sub>CC1</sub> for proper operation. This makes the device compatible to most of the microcontrollers available for automotive applications.

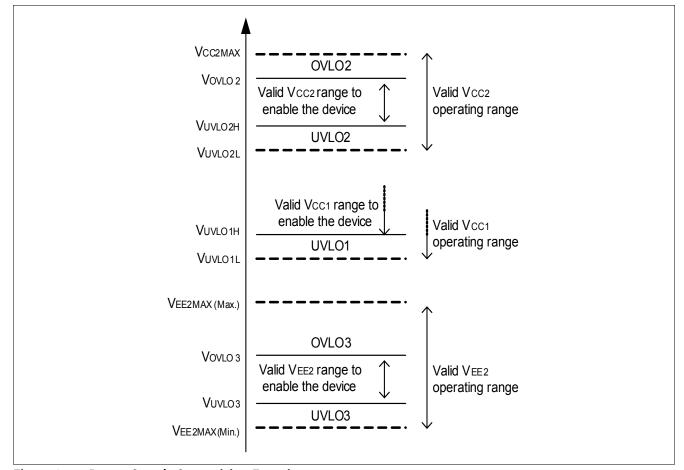

On the secondary side, the 1EDI2004AS needs two power supplies for proper operation.

- The positive power supply  $V_{CC2}$  is typically set to 16.5 V (referring to  $V_{GND2}$ ).

- The negative supply V<sub>EE2</sub> is typically set to -4 V or 0V (referring to V<sub>GND2</sub>).

Under- and over-voltage monitoring is performed continuously during operation of the device (see Chapter 3.3.1).

A 5V supply for the digital domain on the secondary side is generated internally (present at pin VREG).

### 2.4.2 Clock Domains

The clock system of the 1EDI2004AS is based on three oscillators defining each a clock domain:

- One RC oscillator (OSC1) for the primary chip.

- One RC oscillator (OSC2) for the secondary chip excepting the output stage.

- One Start-Stop oscillator (SSOSC2) for the output stage on the secondary side.

The two RC oscillators are running constantly. They are also monitored constantly, and large deviations from the nominal frequency are identified as a system failure (Event Class B, see Chapter 3.3).

The Start Stop oscillator is controlled by the PWM command.

## **Functional Description**

## 2.4.3 PWM Input Stage

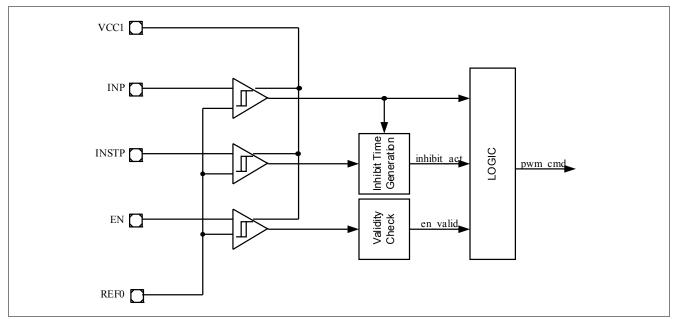

The PWM input stage generates from the external signals INP, INSTP and EN the turn-on and turn-off commands to the secondary side. The general structure of the PWM input block is shown Figure 3.

Figure 3 PWM Input Stage

Signals INP, INSTP and EN are pseudo-differential, in the sense that they are not referenced to the common ground GND1 but to signal REFO. This is intended to make the device more robust against ground bouncing effects.

### Note:

- 1. Glitches shorter than  $t_{INPS1}$  (see Table 45) occurring at signal INP are filtered internally.

- 2. Pulses at INP below  $t_{INPPD}$  (see Table 45) might be distorted or suppressed.

The 1EDI2004AS supports non-inverted PWM signals only. When a High level on pin INP is detected while signals INSTP and EN are valid, a turn-on command is issued to the secondary chip. A Low level at pin INP issues a turn-off command to the secondary chip.

Signal EN can inhibit turn-on commands received at pin INP. A valid signal EN is required in order to have turn-on commands issued to the secondary chip. If an invalid signal is provided, the PWM input stage issues constantly turn-off commands to the secondary chip. The functionality of signal EN is detailed in Chapter 2.4.8.

Note: After an invalid-to valid-transition of signal EN, a minimum delay of t<sub>INPEN</sub> should be inserted before turning INP on.

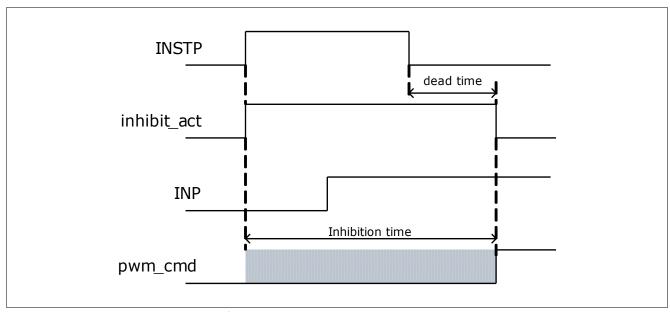

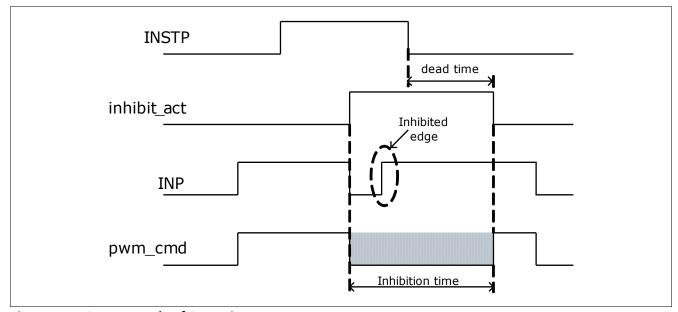

As shown in Figure 4, signal INSTP provides a Shoot-Through Protection (STP) to the system. When signal at pin INSTP is at High level, the internal signal inhibit\_act is activated. The inhibition time is defined as the pulse duration of signal inhibit\_act. It corresponds to the pulse duration of signal INSTP to which a minimum dead time is added. During the inhibition time, rising edges of signal INP are inhibited. Bit PSTAT2.STP is set for the duration of the inhibition time.

# infineon

## **Functional Description**

Figure 4 STP: Inhibition Time Definition

It shall be noted that during the inhibition time, signal pwm\_cmd is not forced to Low. It means that if the device is already turned-on when INSTP is High, it stays turned-on until the signal at pin INP goes Low. This is depicted in Figure 5.

Figure 5 STP: Example of Operation

When a condition occurs where a rising edge of signal INP is inhibited, an error notification is issued. See Chapter 3.4.1 for more details.

Note: If a rising edge shortly after reset occurs at INP may PER.STPER gets set, anyway an immediatly turnon of the secondary is prevented.

# infineon

## **Functional Description**

### 2.4.4 SPI Interface

This chapter describes the functionality of the SPI block.

### 2.4.4.1 Overview

The standard SPI interface implemented on the 1EDI2004AS is compatible with most of the microcontrollers available for automotive and industrial applications. The following features are supported by the SPI interface:

- Full-duplex bidirectional communication link.

- SPI Slave mode (only).

- 16-bit frame format.

- · Daisy chain capability.

- · MSB first.

- Parity Check (optional) and Parity Bit generation (LSB).

The SPI interface of the 1EDI2004AS provides a standardized bidirectional communication interface to the main microcontroller. From the architectural point of view, it fulfills the following functions:

- Initialization of the device.

- Configuration of the device (static and runtime).

- Reading of the status of the device (static and runtime).

- Operation of the verification modes of the device.

The purpose of the SPI interface is to exchange data which have relaxed timing constraints compared to the PWM signals (from the point of view of the motor control algorithm). The IGBT switching behavior is for example controlled directly by the PWM input. Similarly, critical application failures requiring fast reaction are notified on the primary side via the feedback signals NFLTA, NFLTB and NRST/RDY.

In order to minimize the complexity of the end-application and to optimize the microcontroller's resources, the implemented interface has daisy chain capability. Several (typically 6) 1EDI2004AS devices can be combined into a single SPI bus.

# infineon

## **Functional Description**

## 2.4.4.2 General Operation

The SPI interface of the 1EDI2004AS supports full duplex operation. The interface relies on four communication signals:

- NCS: (Not) Chip Select.

- SCLK: Serial Clock.

- SDI: Serial Data In.

- SDO: Serial Data Out.

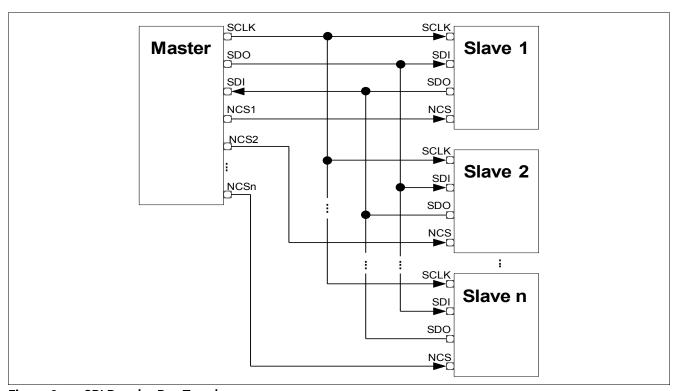

The SPI interface of the 1EDI2004AS supports slave operation only. An SPI master (typically, the main microcontroller) is connected to one or several 1EDI2004AS devices, forming an SPI bus. Several bus topologies are supported.

A regular SPI bus topology can be used where each of the slaves is controlled by an individual chip select signal (**Figure 6**). In this case, the number of slaves on the bus is only limited by the application's constraints.

Figure 6 SPI Regular Bus Topology

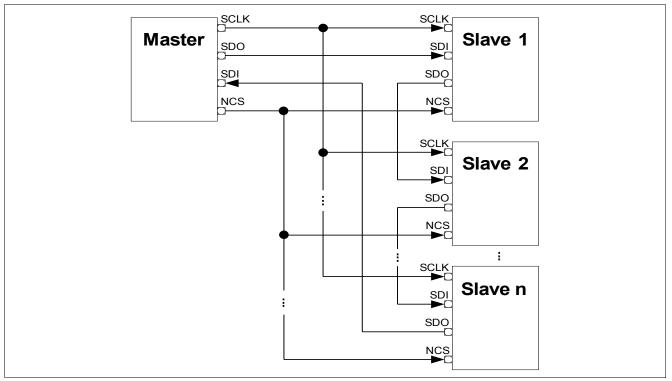

In order to simplify the layout of the PCB and to reduce the number of pins used on the microcontroller's side, a daisy chain topology can also be used. The chain's depth is not limited by the 1EDI2004AS itself. A possible topology is shown Figure 7.

## **Functional Description**

Figure 7 SPI Daisy Chain Bus Topology

### **Physical Layer**

The SPI interface relies on two shift registers:

- A shift output register, reacting on the rising edges of SCLK.

- A shift input register, reacting on the falling edges of SCLK.

When signal NCS is inactive, the signals at pins SCLK and SDI are ignored. The output SDO is in tristate.

When NCS is activated, the shift output register is updated internally with the value requested by the previous SPI access.

At each rising edge of the SCLK signal (while NCS is active), the shift output register is serially shifted out by one bit on the SDO pin (MSB first). At each falling edge of the clock pulse, the data bit available at the input SDI is latched and serially shifted into the shift input register.

At the deactivation of NCS, the SPI logic checks how many rising and falling edges of the SCLK signal have been received. In case both counts differ and / or are not a multiple of 16, an SPI Error is generated. The SPI block then checks the validity of the received 16-bit word. In case of a non valid data, an SPI error is generated. In case no error is detected, the data is decoded by the internal logic.

The NCS signal is active low.

### **Input Debouncing Filters**

The input stages of signals SDI, SCLK, and NCS include each a Debouncing Filter. The input signals are that way filtered from glitches and noise.

The input signals **SDI** and **SCLK** are analyzed at each edge of the internal clock derived from OSC1. If the same external signal value is sampled three times consecutively, the signal is considered as valid and is processed by the SPI logic. Otherwise, the transition is considered as a glitch and is discarded.

## **Functional Description**

The input signal NCS is sampled at a rate corresponding to the period of the internal clock derived from OSC1. If the same external signal value is sampled two times consecutively, the signal is considered as valid and is processed by the SPI logic. Otherwise, the transition is considered as a glitch and is discarded.

### 2.4.4.3 Definitions

### Command

A command is a high-level command issued by the SPI master which aims at generating a specific reaction in the addressed slave. The command is physically translated into a Request Message by the SPI master. The correct reception of the Request Message by the SPI slave leads to a specific action inside the slave and to the emission of an Answer Message by the slave.

Example: the READ command leads to the transfer of the value of the specified register from the device to the SPI master.

### Word

A word is a 16-bit sequence of shifted data bits.

### **Transfer**

A transfer is defined as the SPI data transfers (in both directions) occurring between a falling edge of NCS and the next consecutive rising edge of NCS.

### **Request Message**

A request message is a word issued by the SPI master and addressing a single slave. A request message relates to a specific command.

### **Answer Message**

An answer message is a well-defined word issued by a single SPI slave as a response to a request message.

### **Transmit Frame**

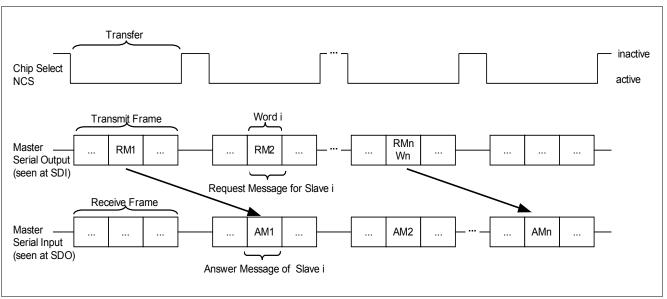

A transmit frame is a sequence of one or several words sent by the SPI Master within one SPI transfer. In regular SPI topologies, a transmit frame is in practice identical to a data word. In daisy chain topologies, a transmit frame is a sequence of data words belonging to different request messages.

### **Receive Frame**

A receive frame is a sequence of one or several words received by the SPI Master within one SPI transfer. In regular SPI topologies, a receive frame is in practice identical to a data word. In daisy chain topologies, a receive frame is a sequence of data words belonging to different Answer Messages.

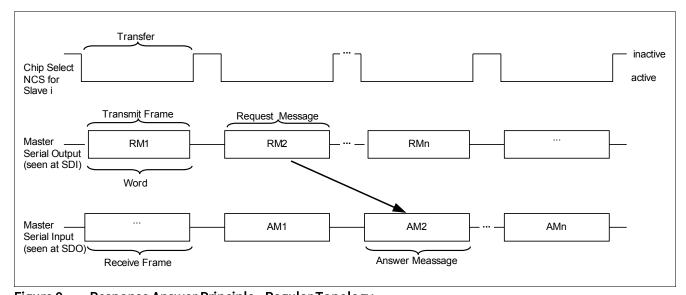

The SPI protocol supported by the 1EDI2004AS is based on the Request / Answer principle. The master sends a defined request message to which the slave answers with the corresponding answer message (**Figure 8**, **Figure 9**). Due to the nature of the SPI interface, the Answer Message is shifted, compared to the Request Message, by one SPI transfer. It means, for example, that the last word of answer message n is transmitted by the slave while the master sends the first word of request message n+1.

## **Functional Description**

Figure 8 Response Answer Principle - Daisy Chain Topology

Figure 9 Response Answer Principle - Regular Topology

The first word transmitted by the device after power-up is the content of register PSTAT.

## **Functional Description**

#### 2.4.4.4 **SPI Data Integrity Support**

#### 2.4.4.4.1 **Parity Bit**

By default, the SPI link relies on an odd parity protection scheme for each transmitted or received 16-bit word of the SPI message. The parity bit corresponds to the LSB of the 16-bit word. Therefore, the effective payload of a 16-bit word is 15 data bit (plus one parity bit). The parity bit check (on the received data) can be disabled by clearing bit PCFG.PAREN. In this case, the parity bit is considered as "don't care". The generation of the parity bit by the driver for transmitted words can not be disabled (but can be considered as "don't care" by the SPI master).

Note:

For fixed value commands (ENTER CMODE, ENTER VMODE, EXIT CMODE, NOP), it has to be ensured that the value of the parity bit is correct even if parity check is disabled. Otherwise, an SPI error will be generated.

#### 2,4,4,4,2 SPI Error

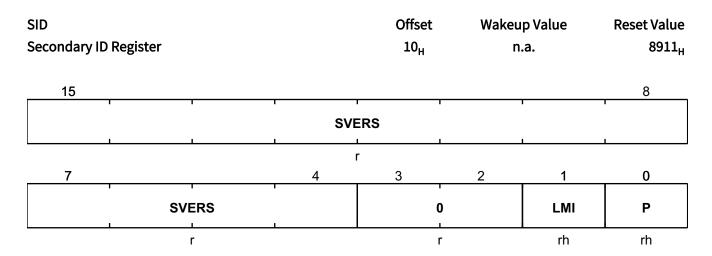

When the device is not able to process an incoming request message, an SPI error is generated: the received message is discarded by the driver, bit PER.SPIER is set and the erroneous message is answered with an error notification (bit LMI set).

Several failures generate an SPI error:

- A parity error is detected on the received word.

- An invalid data word format is received (e.g. not a 16 bit word).

- A word is received, which does not correspond to a valid Request Message.

- A command is received which can not be processed. For example, the driver receives in Active Mode a command which is only valid in other operating modes. Another typical example is a read access to the secondary while the previous read access is not yet completed (device "busy").

- An SPI access to an invalid address.

Note: the content of a frame with LMI bit set is the value of register PSTAT.

Note: In case of permanent LMI error induced by system failures, it is recommended to apply a reset via pin

NRST/RDY.

**Functional Description**

## 2.4.4.5 Protocol Description

## 2.4.4.5.1 Command Catalog

**Table 3** gives an overview of the command catalog supported by the device. The full description of the commands and of the corresponding request and answer messages is provided in the following sections.

Table 3 SPI Command Catalog

| Acronym     | Short Description                                                                                                                                                                    | Valid in Mode           |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| ENTER_CMODE | Enters into Configuration Mode.                                                                                                                                                      | OPM0, OPM1              |

| ENTER_VMODE | Enters into Verification Mode.                                                                                                                                                       | OPM2                    |

| EXIT_CMODE  | Leaves Configuration Mode to enter into Configured Mode.                                                                                                                             | OPM2                    |

| READ        | Reads the register value at the specified address.                                                                                                                                   | All                     |

| NOP         | Triggers no action in the device (equivalent to a "nop").                                                                                                                            | All                     |

| WRITEH      | Update the most significant byte of the internal write buffer.                                                                                                                       | All                     |

| WRITEL      | Updates the least significant byte of the internal write buffer, and copies the contents of the complete buffer into the addressed register. The write buffer is cleared afterwards. | All (with restrictions) |

An overview of the commands is given Figure 10.

| Message     |   | Com | mand |   |    |    |    |     |     | Data |     |     |     |    |    |  |

|-------------|---|-----|------|---|----|----|----|-----|-----|------|-----|-----|-----|----|----|--|

| ENTER_CMODE | 0 | 0   | 0    | 1 | 1  | 0  | 0  | 0   | 1   | 0    | 0   | 0   | 0   | 0  | 0  |  |

| ENTER_VMODE | 0 | 0   | 0    | 1 | 0  | 0  | 0  | 1   | 0   | 1    | 0   | 0   | 0   | 0  | 0  |  |

| EXIT_CMODE  | 0 | 0   | 0    | 1 | 0  | 0  | 1  | 0   | 0   | 0    | 1   | 0   | 0   | 0  | 0  |  |

| NOP         | 0 | 0   | 0    | 1 | 0  | 1  | 0  | 0   | 0   | 0    | 0   | 1   | 0   | 0  | 0  |  |

| READ        | 0 | 0   | 0    | 0 | A4 | A3 | A2 | A1  | A0  | 0    | 1   | 0   | 1   | 0  | 1  |  |

| WRITEH      | 0 | 1   | 0    | 0 | 0  | 1  | 0  | D15 | D14 | D13  | D12 | D11 | D10 | D9 | D8 |  |

| WRITEL      | 1 | 0   | 1    | 0 | A4 | A3 | A2 | A1  | A0  | D7   | D6  | D5  | D4  | D3 | D2 |  |

Figure 10 SPI Commands Overview

## 2.4.4.5.2 Word Convention

In order to simplify the description of the SPI commands, the following conventions are used (Table 4).

## **Functional Description**

Table 4 Word Convention

| Acronym                                                   | Value                                                     |

|-----------------------------------------------------------|-----------------------------------------------------------|

| Va(REGISTER)                                              | Value of register REGISTER                                |

| $\overline{P_B}$                                          | Parity Bit                                                |

| < <n< td=""><td>Left shift operation of n bits.</td></n<> | Left shift operation of n bits.                           |

| $x_H \mid y_H$                                            | Result of the operation: x <sub>H</sub> OR y <sub>H</sub> |

## 2.4.4.5.3 ENTER\_CMODE Command

The goal of this function is to set the device into Configuration Mode. After reception of a valid ENTER\_CMODE command, mode OPM2 is active. This command is only valid in Default Mode (OPM0 and OPM1). In case the request message is received while OPM0 or OPM1 is not active, the complete command is discarded and an SPI error occurs.

**Table 5** describes the request message and the corresponding answer message.

Table 5 ENTER\_CMODE request and answer messages

|                 | Transfer 1        | Transfer 2 |

|-----------------|-------------------|------------|

| Request message | 1880 <sub>H</sub> | N.a.       |

| Answer message  | N.a.              | Va(PSTAT)  |

### 2.4.4.5.4 ENTER\_VMODE Command

The goal of this function is to set the device into Verification Mode. After reception of a valid ENTER\_VMODE command, mode OPM5 is active. This command is only valid in Configuration Mode (OPM2). In case the request message is received while OPM2 is not active, the complete command is discarded and an SPI error occurs.

**Table 6** describes the request message and the corresponding answer message.

Table 6 ENTER\_VMODE request and answer messages

|                 | Transfer 1        | Transfer 2 |

|-----------------|-------------------|------------|

| Request message | 1140 <sub>H</sub> | N.a.       |

| Answer message  | N.a.              | Va(PSTAT)  |

## 2.4.4.5.5 EXIT\_CMODE Command

When a valid EXIT\_CMODE is received by the device, the Configuration Mode is left to Configured Mode (Mode OPM3 active). This command is only valid in Configuration Mode (OPM2). In case the request message is received while OPM2 is not active, the complete command is discarded and an SPI error occurs.

**Table 7** describes the request message and the corresponding answer message.

## **Functional Description**

Table 7 EXIT\_CMODE request and answer messages

|                 | Transfer 1        | Transfer 2 |

|-----------------|-------------------|------------|

| Request message | 1220 <sub>H</sub> | N.a.       |

| Answer message  | N.a.              | Va(PSTAT)  |

## 2.4.4.5.6 **NOP Command**

This command triggers no specific action in the driver (equivalent to a "nop"). However, the mechanisms verifying the validity of the word are active. This command is valid in all operating modes.

**Table 8** describes the request message and the corresponding answer message.

Table 8 NOP request and answer messages

|                 | Transfer 1        | Transfer 2 |

|-----------------|-------------------|------------|

| Request message | 1410 <sub>H</sub> | N.a.       |

| Answer message  | N.a.              | Va(PSTAT)  |

### 2.4.4.5.7 **READ Command**

This command aims at reading the value of the register whose address is specified in the request message. This command is valid in all operating modes. However, in OPM4 and OPM6, the use of the READ command is restricted (see **Table 37**). If an access outside the allowed address range is performed, the access is discarded as invalid and an SPI error occurs.

**Table 9** describes the request message and the corresponding answer message.

Table 9 READ request and answer messages

|                 | Transfer 1 | Transfer 2   |  |  |

|-----------------|------------|--------------|--|--|

| Request message | See below  | N.a.         |  |  |

| Answer message  | N.a.       | Va(Register) |  |  |

### Request message words

Word 1:  $(ADDRESS_5BIT << 7)] \mid 002A_H \mid P_B$ .

### Answer message words

Word 1: Value of REGISTER.

## 2.4.4.5.8 WRITEH

This command aims at writing the upper byte of the internal write buffer with the specified value. This command has no other effect on the functionality of the device. This command is valid in all operating modes.

Table 10 describes the request message and the corresponding answer message.

## **Functional Description**

Table 10 WRITEH request and answer messages

|                 | - <del>-</del> | ~          |

|-----------------|----------------|------------|

|                 | Transfer 1     | Transfer 2 |

| Request message | See below      | N.a.       |

| Answer message  | N.a.           | Va(PSTAT)  |

### Request message words

Word 1:  $4400_{H}$  | ( DATA\_8BIT << 1 ) |  $P_{B}$

### 2.4.4.5.9 WRITEL

This command aims at updating the value of the register whose address is specified in the request message. This command is valid in all operating modes. However, depending on the active operating mode, this command is restricted to a given address range or specific registers (see **Table 38**). If an access outside the allowed address range is performed, the access is discarded as invalid and an SPI error occurs.

At the reception of this command, the least significant byte of the internal buffer is written with the specified value, the contents of the buffer is copied to the register at the specified address and the complete write buffer is cleared.

**Table 11** describes the request message and the corresponding answer message.

Table 11 WRITEL request and answer messages

|                 | Transfer 1 | Transfer 2 |

|-----------------|------------|------------|

| Request message | See below  | N.a.       |

| Answer message  | N.a.       | Va(PSTAT)  |

## Request message words

Word 1:  $A000_{H} | (ADDRESS_5BIT << 7) | (DATA_6BIT << 1) | P_B$ .

## **Functional Description**

## 2.4.5 Operating Modes

## 2.4.5.1 General Operation

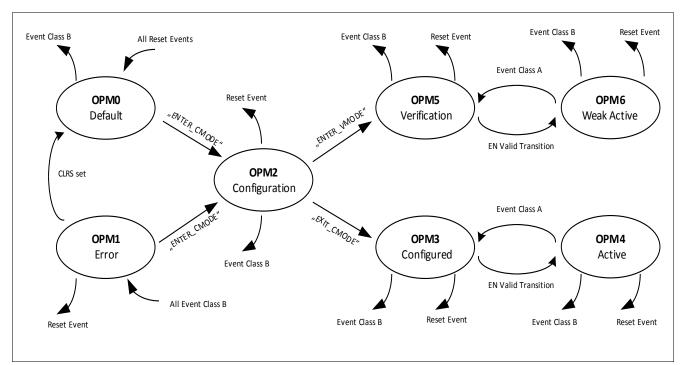

At any time, the driver can be in one out of seven possible operating modes:

- OPM0: Default Mode (default after reset, device is disabled).

- OPM1: Error Mode (reached after Event Class B, device is disabled).

- OPM2: Configuration Mode (device is disabled, configuration of the device can be modified).

- OPM3: Configured Mode (device is configured and disabled).

- OPM4: Active Mode (normal operation).

- OPM5: Verification mode (intrusive diagnostic functions can be triggered).

- OPM6: Weak active mode (the device can be turned on but with restrictions)

The current active mode of the device is given by bit field **SSTAT.OPM**.

The concept of the device is based on the following general ideas:

- The driver can only switch the IGBT on when OPM4 mode is active (exception: weak-turn on in OPM6).

- Starting from Mode OPM0 or OPM1, the Active Mode OPM4 can only be activated through a dedicated SPI command sequence and the activation of the hardware signal EN. As a result, the probability that the device goes to OPM4 mode due to random signals is negligible.

- Differentiations of errors: different classes of errors are defined, leading to different behavior of the device.

The state diagram for the operating modes is given in Figure 11:

Figure 11 Operating Modes State Diagram

# infineon

**Functional Description**

### 2.4.5.2 Definitions

### 2.4.5.2.1 Events and State Transitions

The transitions from one state to the other are based on "events" and / or SPI commands. The following classification is chosen for defining the events.

### **Events Class A**

The following (exhaustive) list of events are defined as Events Class A:

- Occurrence of a DESAT event (leads to a safe turn-off sequence).

- Occurrence of an OCP event (leads to a safe turn-off sequence).

- Valid to Invalid transition on EN signal (leads to a regular turn-off sequence).

When an Event Class A occurs, the output stage initiates either a safe turn-off sequence (DESAT, OCP) or a regular turn-off sequence (EN event). The event is notified via an error bit in the corresponding register.

Note: Contrarily to a reset event, an Event Class A does not affect the contents of the configuration registers.

When an Event Class A occurs, the device may change its operating mode depending on which mode is active when the event occurs:

- If it was in OPM4, it goes in OPM3.

- If it was in OPM6, it goes in OPM5.

In all other cases, the OPM is unaffected. A state transition due to an Event Class A leads to the activation of signal **NFLTA**. If no state transition occurs (if for example the device was not in OPM4 or OPM6), **NFLTA** is not activated.

### **Events Class B**

The following (exhaustive) list of events are defined as Events Class B:

- Occurrence of a UVLO2 event.

- Occurrence of a OVLO2 event.

- Occurrence of a UVLO3 event. (configurable)

- Occurrence of a OVLO3 event. (configurable)

- Verification Mode Time Out Error

Note: Every class B event with state transition triggers a notification via NFLTB signal. But not all notifications on NFLTB signal are class B events (e.g. failures, resets, also see Table 14, Table 15).

When an Event Class B occurs, the output stage initiates a regular turn-off sequence. The event is notified via an error bit in the corresponding register and (possibly) via the signal NFLTB.

Note: Events Class B may affect the contents of the configuration registers.

When an Event Class B occurs, the device may change its operating mode depending on which mode is active when the event occurs: if it was not in OPM1, it goes to OPM1. It is unaffected otherwise

## **Functional Description**

A state transition due to an Event Class B leads to the activation of signal NFLTB. If no state transition occurs (if for example the device was already in OPM1), NFLTB is not activated. See Chapter 2.4.7 for more details on failure notifications.

### **Events Class C**

Generally speaking, Events Class C are error events that do not lead to a change of the operating mode of the device. The following (exhaustive) list of events is comprised within the Event Class C:

- Time Out Error (PER.O2MTO & PER.DBTO)

- Output Stage Tristate (PER.OSTER)

- SPI Error (PER.SPIER).

- Shoot Through Protection Error (PER.STPER).

Note:

For over- and undervoltage errors it is depending on the configuration whether a Event Class B or Event Class C is generated (e.g. SER.OVLO3ER, SER.OVLO2ER)

### **SPI Commands**

The following SPI commands have an impact on the device's operating mode. The SPI commands are described in Chapter 2.4.4.5.

- ENTER\_CMODE.

- ENTER\_VMODE.

- EXIT\_CMODE.

- Setting of bit SCTRL.CLRS (by writing register PCTRL)

### **Reset Events**

A reset sets the device (or part of the device) in its default state. Reset events are described in Chapter 2.4.10.

## 2.4.5.2.2 Emergency Turn-Off Sequence

The denomination "Emergency Turn-Off Sequence" (ETO) is used to describe the sequence of actions executed by the output stage of the device when an Event Class Aand Class B is detected.

An ETO sequence is described by the following set of actions:

- A Turn-Off sequence is initiated. In case of DESAT or OCP event, a safe turn-off sequence is initiated. For the other events, a regular turn-off sequence is initiated.

- The device enters the corresponding OPM mode. As a consequence, the device is disabled.

Once an ETO from Event Class B has been initiated, the device can not be reenabled. Consequently, the user need to reconfigure the device before reenabling the device and sending PWM turn-on command.

## 2.4.5.2.3 Ready, Disabled, Enabled and Active State

The device is said to be in Ready state in case no reset event is active on the primary chip. When the device is Ready, signal NRST/RDY is at High level.

## **Functional Description**

When the device is in Disabled State, the PWM turn-on commands are ignored. This means that whatever the input signal INP is, the output stage (if not tristated) delivers a constant turn-off signal to the IGBT. Unless otherwise stated, all other functions of the device work normally.

When the device is not in Disabled State, it is said to be in Enabled State. In this case, the PWM signal command is processed normally (if the output stage is not tristated). Practically, the device is in Enabled State when either Mode OPM4 or Mode OPM6 is active.

Active State corresponds to the normal operating state of the device. Practically, the device is in Active State when Mode OPM4 is active.

Note: When the device is in Active State, it implicates it is in Enabled state.

## 2.4.5.3 Operation Modes Description

### Default Mode (OPM0)

Mode OPM0 is the default operating mode of the device after power up or after a reset event. In OPM0, the device is in Disabled State.

The following exhaustive list of events bring the device in OPM0 Mode:

- Occurrence of a Reset Event.

- Bit SCTRL.CLRS set while the device was in OPM1.

### Error Mode (OPM1)

Mode OPM1 is the operating mode of the device after an Event Class B.

The following exhaustive list of events bring the device in OPM1 Mode:

· Occurrence of an Event Class B.

In OPM1, when bit SCTRL.CLRS is set via the corresponding SPI command, the device shall normally jump to OPM0. However, in case the conditions for an Event Class B are met at that moment, no state transition occurs and the device stays in OPM1. The operation of bit SCTRL.CLRS on the secondary sticky bits works normally.

In OPM1, when a valid ENTER\_CMODE command is received, the device shall normally jump to OPM2. However, in case the conditions for an Event Class B are met at that moment, no state transition occurs and the device stays in OPM1 for the duration of the event. The state transition to OPM2 is executed as soon as the conditions leading to the Event Class B disappear. It shall be noted that no LMI error notification is issued.

## **Configuration Mode (OPM2)**

Configuration Mode is the mode where the configuration of the device can be modified. When OPM2 is active, the device is in Disabled State.

The following exhaustive list of events bring the device in Configuration Mode:

Reception of a valid ENTER\_CMODE command while Mode OPM0 or OPM1 active.

## **Functional Description**

### **Configured Mode (OPM3)**

Configured Mode is the mode where the device is ready to be enabled. When OPM3 is active, the device is in Disabled State.

The following exhaustive list of events bring the device in Mode OPM3:

- Reception of a valid EXIT\_CMODE command while Mode OPM2 active.

- Event Class A while Mode OPM4 active.

### **Active Mode (OPM4)**

The Active Mode corresponds to the normal operating mode of the device. When OPM4 is active, the device is in Active State. The following exhaustive list of event bring the device in Active Mode:

• Invalid to Valid Transition on signal EN while Mode OPM3 active.

### **Verification Mode (OPM5)**

Verification Mode is the mode where intrusive verification functions can be started. When OPM5 is active, the device is in disabled state.

The following exhaustive list of event bring the device in Verification Mode:

- Reception of a valid ENTER\_VMODE command while Mode OPM2 active.

- Occurrence of an Event Class A while Mode OPM6 active.

After a transition from Mode OPM2 to OPM5, an internal watchdog timer is started. If after time  $t_{VMTO}$ , the device has not left both modes OPM5 or OPM6, a time-out event occurs and an Event Class B is generated.

### Weak Active Mode (OPM6)

Weak Active Mode is the mode where the device can be activated to run diagnosis tests at system level. When OPM6 is active, the device is in Enabled State. A PWM turn-on command issues a Weak Turn-On on the secondary side.

The following exhaustive list of event bring the device in Weak Active Mode:

• Invalid to Valid Transition on signal EN while Mode OPM5 active.

The watchdog counter started when entering Mode OPM5 is not reset when entering OPM6.

## Implementation Notes related to State Transitions

- An Event Class A or Class B detected on the secondary side lead to an immediate reaction of the device's

output stage. Due to the latency of the inter-chip communication, the notification on the primary side is

slightly delayed.

- The activation of signal **NFLTA** or **NFLTB** is simultaneous to the corresponding state transition on the primary side.

- It is possible to change the operating mode while a failure condition is present. This may however lead to a new immediate error notification and state transition.

**Functional Description**

## 2.4.5.4 Activating the device after reset

After a reset event, the device is in Mode OPM0 and disabled. In order to be active, the device needs to enter Configuration Mode with the ENTER\_CMODE command. Once all the configurations have been performed, the Configuration Mode has to be exited with an EXIT\_CMODE command. Once this is done, the device can enter the Active Mode when Invalid to Valid transition on pin EN is detected.

## 2.4.5.5 Activating the device after an Event Class A or B

If during operation, an Event Class A occurs, the device enters the OPM3 (or OPM5). Bit field **SSTAT.OPM** is updated accordingly. In order to reactivate the device, an invalid-to-valid transition has to be applied to signal **EN**. It means that a Low-level and then a High level is applied to **EN**. If no Event Class A event is active, the device will enter OPM4 (respectively OPM6).

If during operation, an Event Class B occurs, the device enters the Default Mode OPM1. Bit field **SSTAT.OPM** is updated accordingly. In order to reactivate the device, the steps defined in **Chapter 2.4.5.4** need to be performed.

## 2.4.5.6 Debug Mode

The **DEBUG** pin gives the possibility to operate the device in the so-called Debug Mode. The goal of the Debug Mode is to operate the device without SPI interface. This mode should be used for development purpose only and is not intended to be used in final applications.

At V<sub>CC2</sub> power-on, the level at pin **DEBUG** is latched. In case a High level is detected, the device enters the Debug Mode. Bit **SSTAT.DBG** is then set.

In Debug Mode, the regular operation of the internal state machine is modified, so that the device can only enter OPM3 or OPM4. As a result Modes OPM0, OPM1, OPM2, OPM5 and OPM6 are completely bypassed. In case of a Reset event, the device goes to OPM3 (instead of OPM0). Besides, in Debug Mode, events leading normally to an Event Class B are replaced an Event Class A, resulting in the activation of signal NFLTA. Event Class B are therefore not generated by the device in Debug Mode (and signal NFLTB shall not be used).

It should be noted that the configuration of the device in Debug Mode corresponds to the default settings and can not be changed (refer to the register reset values to get the default configuration).

In Debug Mode, the operation of the device is otherwise similar to regular operation. It means in particular that the signal **EN** has to be managed properly: when the device is in OPM3, a Low to High level transition has to be applied to the device in order to enter OPM4 (Active Mode).

Note: Once it has been latched at power-on, the level on the pin DEBUG has no impact on the device until the next power-on event on the secondary side.

**Functional Description**

### 2.4.6 Driver Functionality

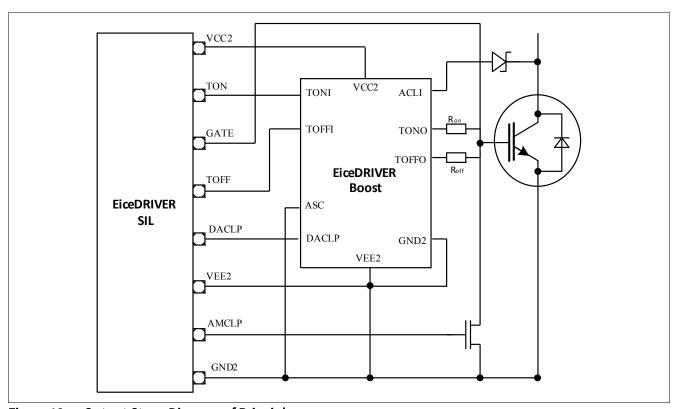

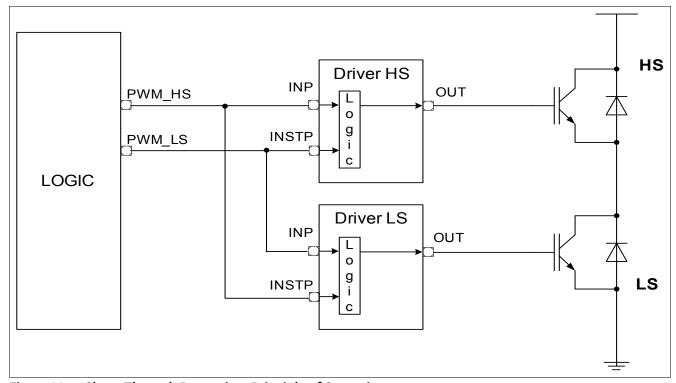

The structure of the output stage and its associated external booster of the device is depicted Figure 12:

Figure 12 Output Stage Diagram of Principle

Note: AMCLP usage is recommended at unipolar supply.

Note: For usage without EiceDRIVER Boost Infineon takes no responsibilities for any cross currents.

### 2.4.6.1 Overview

Two turn-off behaviors are supported by the device, depending on the event causing the turn-off action.

- · Regular Turn-Off.

- · Safe Turn-Off.

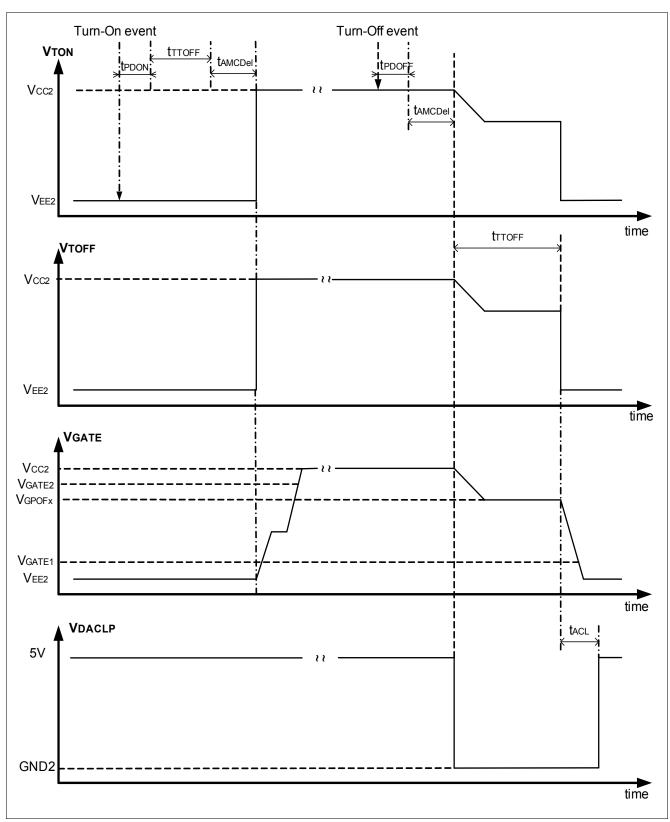

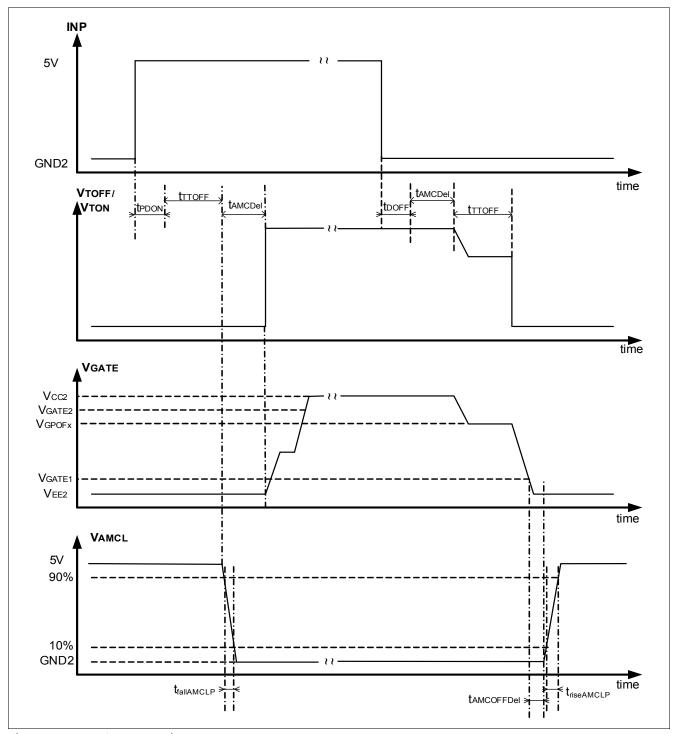

A Safe Turn-Off sequence uses the timing and plateau level parameters defined in register **SSTTOF**. It is triggered by a DESAT or an OCP event only. A turn-off sequence which is not "Safe" is then "Regular". A Regular Turn-Off sequence uses the timing defined in register **SRTTOF**.

### Two Level Turn-Off (TTOFF)

Because a hard turn-off may generate a critical overvoltage on the IGBT leading eventually to its destruction, the 1EDI2004AS supports the Two Level Turn-Off functionality (TTOFF). The TTOFF function consists in switching the IGBT off in three steps in such a way that:

- 1. The IGBT gate voltage is first decreased with a reduced slew rate until a specific (and programmable) voltage is reached by the TOFF signal.

- 2. TOFF (and TON) voltage is stabilized at this level. The IGBT Gate voltage forms thus a plateau.

- 3. Finally, the switch-off sequence is resumed using hard commutation.

### **Functional Description**

The TTOFF delays and plateau voltage are fully programmable using the corresponding SPI commands. Too small delays will not be visible as plateau on the output signal, but may change the slew rate from  $V_{\rm CC2}$  to plateau. For a Regular Turn-Off sequence, the TTOFF delay is defined by bit field SRTTOF.RTVAL. Setting this field to  $00_{\rm H}$  completely disables the TTOFF function for all Regular Turn-Off sequences (but this has no effect on Safe Turn-Off sequences). The plateau level is defined by SRTTOF.GPR. If this function is to be activated, a sufficient value for the delay time has to be programmed.

For a Safe Turn-Off sequence, the TTOFF delay is defined by bit field SSTTOF.STVAL. Setting this field to  $00_H$  completely disables the TTOFF function for all Safe Turn-Off sequences (but this has no effect on Regular Turn-Off sequences). If this function is to be activated, a sufficient value for the delay time has to be programmed. The plateau level is defined by SSTTOF.GPS.

The timing of a Safe Turn-Off event is in the clock domain of the main secondary oscillator (OSC2). The timing of a Regular Turn-Off event is in the clock domain of the Start-Stop Oscillator (SSOSC2), leading to high accuracy and low PWM distortion

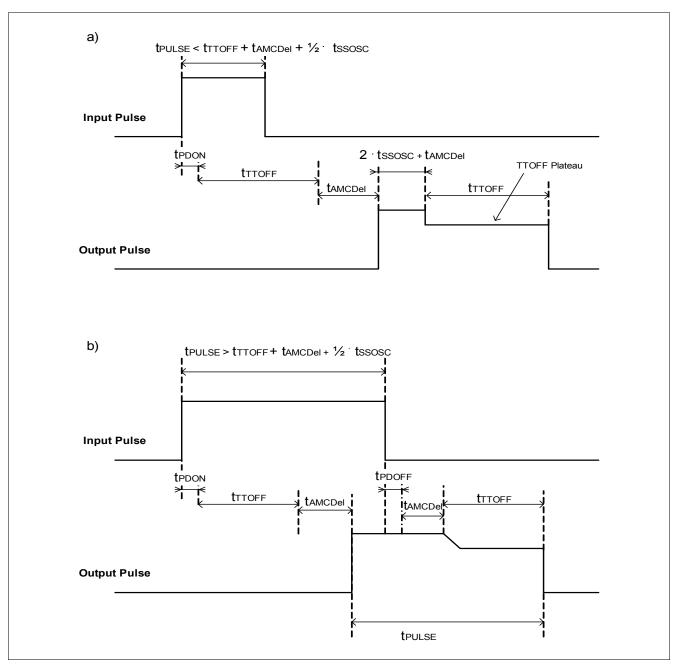

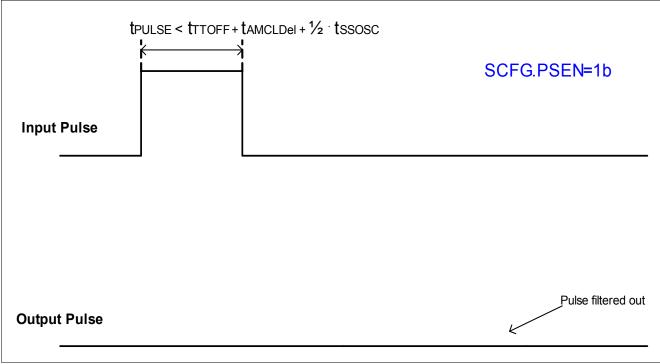

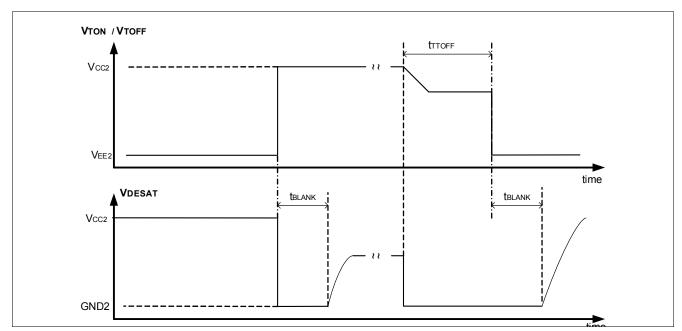

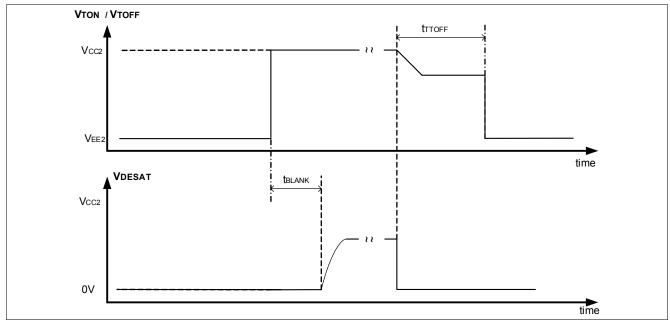

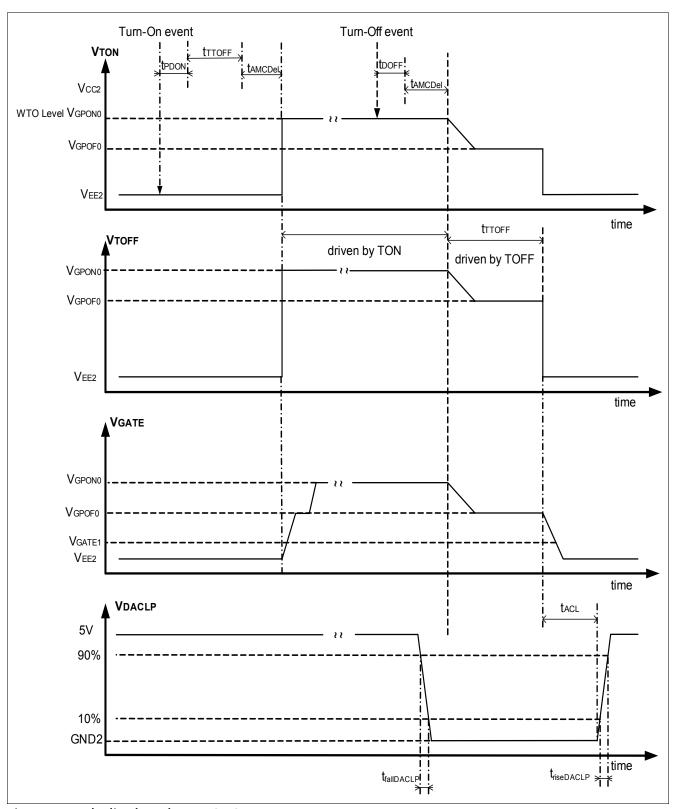

When using the TTOFF function (with a non-zero delay), the PWM command is received on pin INP is delayed by the programmed delay time (Figure 13).

For pulses larger than the TTOFF delay ( $t_{PULSE} > t_{TTOFF} + t_{AMCDel} + 1/2$  SSOSC cycles), the output pulse width is kept identical to the input pulse width.

For smaller pulses ( $t_{PULSE} < t_{TTOFF} + t_{AMCDel} + 1/2$  SSOSC cycles), the output pulse is identical to the programmed delay. The minimum pulse width delivered by the device to the IGBT is therefore the programmed delay time extended by two SSOSC cycles.