#### 1 Features

- Ground Referenced Tachometer Input Interfaces Directly With Variable Reluctance Magnetic Pickups

- Op Amp Has Floating Transistor Output

- 50-mA Sink or Source to Operate Relays, Solenoids, Meters, or LEDs

- Frequency Doubling For Low Ripple

- Tachometer Has Built-In Hysteresis With Either Differential Input or Ground Referenced Input

- ±0.3% Linearity (Typical)

- Ground-Referenced Tachometer is Fully Protected From Damage Due to Swings Above V<sub>CC</sub> and Below Ground

- Output Swings to Ground For Zero Frequency Input

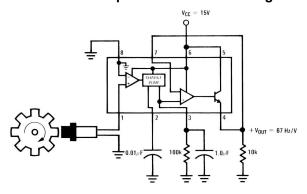

- Easy to Use; V<sub>OUT</sub> = f<sub>IN</sub> x V<sub>CC</sub> x R1 x C1

- Zener Regulator on Chip allows Accurate and Stable Frequency to Voltage or Current Conversion (XD2917)

# 2 Applications

- Over- and Under-Speed Sensing

- Frequency-to-Voltage Conversion (Tachometer)

- Speedometers

- Breaker Point Dwell Meters

- Hand-Held Tachometers

- Speed Governors

- Cruise Control

- Automotive Door Lock Control

- Clutch Control

- Horn Control

- Touch or Sound Switches

# 3 Description

The XD2907 and XD2917 devices are monolithic frequency-to-voltage converters with a high gain op amp designed to operate a relay, lamp, or other load when the input frequency reaches or exceeds a selected rate. The tachometer uses a charge pump technique and offers frequency doubling for low-ripple, full-input protection in two versions (8-pin XD2907 and XD2917), and its output swings to ground for a zero frequency input.

The op amp is fully compatible with the tachometer and has a floating transistor as its output. This feature allows either a ground or supply referred load of up to 50 mA. The collector may be taken above  $V_{CC}$  up to a maximum  $V_{CE}$  of 28 V.

The two basic configurations offered include an 8-pin device with a *ground-referenced tachometer* input and an internal connection between the tachometer output and the op amp noninverting input. This version is well suited for single speed or frequency switching or fully buffered frequency-to-voltage conversion applications.

### 4 Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |

|-------------|-----------|---------------------|

|             | PDIP (8)  | 6.35 mm × 9.81 mm   |

| 2917 2907   | PDIP (14) | 6.35 mm × 19.177 mm |

| 2917 2907   | SOIC (8)  | 3.91 mm × 4.90 mm   |

|             | SOIC (14) | 3.91 mm × 8.65 mm   |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Minimum Component Tachometer Diagram**

# 5 Description (continued)

The more versatile configurations provide differential tachometer input and uncommitted op amp inputs. With this version the tachometer input may be floated and the op amp becomes suitable for active filter conditioning of the tachometer output.

Both of these configurations are available with an active shunt regulator connected across the power leads. The regulator clamps the supply such that stable frequency-to-voltage and frequency-to-current operations are possible with any supply voltage and a suitable resistor.

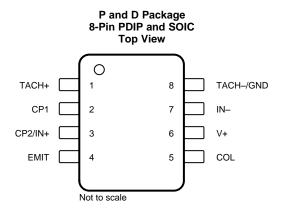

# 6 Pin Configuration and Functions

**Pin Functions: 8 Pins**

| PIN       |     |     |                                                                                                                                                                                                                                                                                                              |  |  |

|-----------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|           |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                  |  |  |

| NAME      | NO. |     |                                                                                                                                                                                                                                                                                                              |  |  |

| COL       | 5   | I   | The collector of the bipolar junction transistor                                                                                                                                                                                                                                                             |  |  |

| CP1       | 2   | 0   | A capacitor placed on this pin will be charged up to $V_{\rm CC}/2$ by a constant current source of 180 $\mu$ A typical at the start of every positive half cycle. At the beginning of negative half cycles this capacitor is discharged the same amount at the same rate.                                   |  |  |

| CP2/IN+   | 3   | I/O | See pins CP1 and IN+. On 8-pin devices (8-pin XD2907 and XD2917) these two nodes share a pin and are internally connected.                                                                                                                                                                                   |  |  |

| EMIT      | 4   | 0   | The emitter of the bipolar junction transistor                                                                                                                                                                                                                                                               |  |  |

| GND       | _   | G   | Ground                                                                                                                                                                                                                                                                                                       |  |  |

| IN+       | _   | I   | The noninverting input to the high gain op amp                                                                                                                                                                                                                                                               |  |  |

| IN-       | 7   | I   | The inverting input to the high gain op amp                                                                                                                                                                                                                                                                  |  |  |

| NC        | _   | _   | No connect                                                                                                                                                                                                                                                                                                   |  |  |

| TACH+     | 1   | ı   | Positive terminal for the input signal that leads to the noninverting terminal of the internal Schmitt-Trigger comparator.                                                                                                                                                                                   |  |  |

| TACH-/GND | 8   | I   | Negative terminal for the input signal that leads to the noninverting terminal of the internal Schmitt-<br>Trigger comparator. (NOTE: On 8-pin devices, XD2907 and XD2917, this pin is internally connected to ground and must be tied to ground externally to provide the reference voltage of the device). |  |  |

| V+        | 6   | 1   | Supply voltage                                                                                                                                                                                                                                                                                               |  |  |

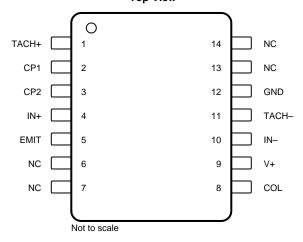

#### NFF and D Package 14-Pin PDIP and SOIC Top View

**Pin Functions: 14 Pins**

| PIN   |              | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                |  |  |  |  |

|-------|--------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME  | NO.          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                |  |  |  |  |

| COL   | 8            | I   | The collector of the bipolar junction transistor                                                                                                                                                                                                                           |  |  |  |  |

| CP1   | 2            | 0   | A capacitor placed on this pin will be charged up to $V_{\rm CC}/2$ by a constant current source of 180 $\mu$ A typical at the start of every positive half cycle. At the beginning of negative half cycles this capacitor is discharged the same amount at the same rate. |  |  |  |  |

| CP2   | 3            | 0   | The charge pump sources current out of this pin equal to the absolute value of the capacitor current on CP1. A resistor and capacitor in parallel connected to this pin filters the current pulses into the output voltage.                                                |  |  |  |  |

| EMIT  | 5            | 0   | The emitter of the bipolar junction transistor                                                                                                                                                                                                                             |  |  |  |  |

| GND   | 12           | G   | Ground                                                                                                                                                                                                                                                                     |  |  |  |  |

| IN+   | 4            | I   | The noninverting input to the high gain op amp                                                                                                                                                                                                                             |  |  |  |  |

| IN-   | 10           | I   | The inverting input to the high gain op amp                                                                                                                                                                                                                                |  |  |  |  |

| NC    | 6, 7, 13, 14 | _   | No connect                                                                                                                                                                                                                                                                 |  |  |  |  |

| TACH+ | 1            | I   | Positive terminal for the input signal that leads to the noninverting terminal of the internal Schmitt-<br>Trigger comparator.                                                                                                                                             |  |  |  |  |

| TACH- | 11           | I   | Negative terminal for the input signal that leads to the noninverting terminal of the internal Schmitt-<br>Trigger comparator.                                                                                                                                             |  |  |  |  |

| V+    | 9            | I   | Supply voltage                                                                                                                                                                                                                                                             |  |  |  |  |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                       |                         |                          | MIN | MAX  | UNIT |

|---------------------------------------|-------------------------|--------------------------|-----|------|------|

| Supply voltage                        |                         |                          |     | 28   | V    |

| Supply current (Zener options)        |                         |                          |     | 25   | mA   |

| Collector voltage                     |                         |                          |     | 28   | V    |

| Differential input voltage            | Tachometer, op amp, and | l comparator             |     | 28   | V    |

|                                       | Took a market           | XD2907 (8), XD2917 (8)   | -28 | 28   | V    |

| Input voltage                         | Tachometer              | XD2907 (14), XD2917 (14) | 0   | 28   |      |

|                                       | Op amp and comparator   |                          | 0   | 28   | Ī    |

| Dower discipation                     | XD29x7 (8)              |                          |     | 1200 | m\\\ |

| Power dissipation                     | XD29x7 (14)             | XD29x7 (14)              |     | 1580 | mW   |

|                                       | PDIP package            | Soldering (10 s)         |     | 260  |      |

| Soldering information                 | 5010                    | Vapor phase (60 s)       |     | 215  | °C   |

|                                       | SOIC package            | Infrared (15 s)          |     | 220  | ĺ    |

| Operating temperature, T <sub>J</sub> |                         |                          | -40 | 85   | °C   |

| Storage temperature, T <sub>stg</sub> |                         |                          |     | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|       |                                            |                                                                     | VALUE | UNIT     |

|-------|--------------------------------------------|---------------------------------------------------------------------|-------|----------|

| \/    | V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JESD22-A114 <sup>(1)</sup>    | ±1000 | V        |

| V(ESD |                                            | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | <b>v</b> |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                     |                          | MIN | NOM MAX | UNIT |

|---------------------|--------------------------|-----|---------|------|

| Input voltage       | XD2907 (8), XD2917 (8)   | -28 | 28      | ٧    |

|                     | XD2907 (14), XD2917 (14) | 0   | 28      | ٧    |

| Output sink current | •                        |     | 50      | mA   |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.4 Thermal Information

|                      |                                              | XD2907, XD2917 |          |            |          |      |

|----------------------|----------------------------------------------|----------------|----------|------------|----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | P (PDIP)       | D (SOIC) | NFF (PDIP) | D (SOIC) | UNIT |

|                      |                                              | 8 PINS         | 8 PINS   | 14 PINS    | 14 PINS  |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 77.6           | 110      | 69.1       | 83.7     | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 80.5           | 53.9     | 64.8       | 42.1     | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 54.8           | 50.4     | 49.1       | 38       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 37.6           | 9.1      | 35.1       | 7.7      | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 54.8           | 49.9     | 49         | 37.7     | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | _              | _        | _          | _        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

## 7.5 Electrical Characteristics

$V_{CC} = 12 V_{DC}$ ,  $T_A = 25$ °C, see test circuit

|                                 | PARAMETER                 | TEST CONDITIONS                                                    | MIN | TYP  | MAX                  | UNIT  |

|---------------------------------|---------------------------|--------------------------------------------------------------------|-----|------|----------------------|-------|

| ТАСНО                           | METER                     | ·                                                                  |     |      |                      |       |

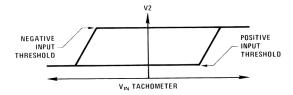

|                                 | Input thresholds          | V <sub>IN</sub> = 250 mVp-p at 1 kHz <sup>(1)</sup>                | ±10 | ±25  | ±40                  | mV    |

|                                 | Hysteresis                | V <sub>IN</sub> = 250 mVp-p at 1 kHz <sup>(1)</sup>                |     | 30   |                      | mV    |

|                                 | VD00-7 -#                 | V <sub>IN</sub> = 250 mVp-p at 1 kHz <sup>(1)</sup>                |     | 3.5  | 10                   |       |

|                                 | XD29x7 offset voltage     | V <sub>IN</sub> = 250 mVp-p at 1 kHz (8-pin XD29x7) <sup>(1)</sup> |     | 5    | 15                   | mV    |

|                                 | Input bias current        | $V_{IN} = \pm 50 \text{ mV}_{DC}$                                  |     | 0.1  | 1                    | μΑ    |

| V <sub>OH</sub>                 | High level output voltage | For CP1, V <sub>IN</sub> = 125 mV <sub>DC</sub> <sup>(2)</sup>     |     | 8.3  |                      | V     |

| V <sub>OL</sub>                 | Low level output voltage  | For CP1, $V_{IN} = -125 \text{ mV}_{DC}^{(2)}$                     |     | 2.3  |                      | V     |

| I <sub>2</sub> , I <sub>3</sub> | Output current            | V2 = V3 = 6 V <sup>(3)</sup>                                       | 140 | 180  | 240                  | μА    |

| l <sub>3</sub>                  | Leakage current           | I2 = 0, V3 = 0                                                     |     |      | 0.1                  | μА    |

| K                               | Gain constant             | See <sup>(2)</sup>                                                 | 0.9 | 1    | 1.1                  |       |

|                                 | Linearity                 | f <sub>IN</sub> = 1 kHz, 5 kHz, or 10 kHz <sup>(4)</sup>           | -1% | 0.3% | 1%                   |       |

| OP AME                          | AND COMPARATOR            | ,                                                                  |     |      | '                    |       |

| Vos                             | Input offset voltage      | V <sub>IN</sub> = 6 V                                              |     | 3    | 10                   | mV    |

| I <sub>BIAS</sub>               | Bias current              | V <sub>IN</sub> = 6 V                                              |     | 50   | 500                  | nA    |

|                                 | Input common-mode voltage |                                                                    | 0   |      | V <sub>CC</sub> -1.5 | V     |

|                                 | Voltage gain              |                                                                    |     | 200  |                      | V/mV  |

|                                 | Output sink current       | V <sub>C</sub> = 1                                                 | 40  | 50   |                      | mA    |

|                                 | Output source current     | $V_E = V_{CC} - 2$                                                 |     | 10   |                      | mA    |

|                                 |                           | I <sub>SINK</sub> = 5 mA                                           |     | 0.1  | 0.5                  | V     |

|                                 | Saturation voltage        | I <sub>SINK</sub> = 20 mA                                          |     |      | 1                    | V     |

|                                 |                           | I <sub>SINK</sub> = 50 mA                                          |     | 1    | 1.5                  | V     |

| ZENER                           | REGULATOR                 |                                                                    | •   |      | ,                    |       |

|                                 | Regulator voltage         | $R_{DROP} = 470 \Omega$                                            |     | 7.56 |                      | V     |

|                                 | Series resistance         |                                                                    |     | 10.5 | 15                   | Ω     |

|                                 | Temperature stability     |                                                                    |     | 1    |                      | mV/°C |

|                                 | Total supply current      |                                                                    |     | 3.8  | 6                    | mA    |

|                                 |                           |                                                                    |     |      |                      |       |

<sup>(1)</sup> Hysteresis is the sum V<sub>TH</sub> - (-V<sub>TH</sub>), offset voltage is their difference. See test circuit.

(2) V<sub>OH</sub> = 0.75 x V<sub>CC</sub> - 1 V<sub>BE</sub> and V<sub>OL</sub> = 0.25 x V<sub>CC</sub> - 1 V<sub>BE</sub>, therefore V<sub>OH</sub> - V<sub>OL</sub> = V<sub>CC</sub> / 2. The difference (V<sub>OH</sub> - V<sub>OL</sub>) and the mirror gain (I<sub>2</sub> / I<sub>3</sub>) are the two factors that cause the tachometer gain constant to vary from 1.

Ensure that when choosing the time constant R1 x C1 that the maximum anticipated output voltage at CP2/IN+ can be reached with I<sub>3</sub> x R1. The maximum value for R1 is limited by the output resistance of CP2/IN+ which is greater than 10 M $\Omega$  typically.

Nonlinearity is defined as the deviation of  $V_{OUT}$  (at  $\dot{C}P2/IN+$ ) for  $f_{IN}=5$  kHz from a straight line defined by the  $V_{OUT}$  at 1 kHz and  $V_{OUT}$ at 10 kHz. C1 = 1000 pF, R1 = 68 k $\Omega$  and C2 = 0.22  $\mu$ F.

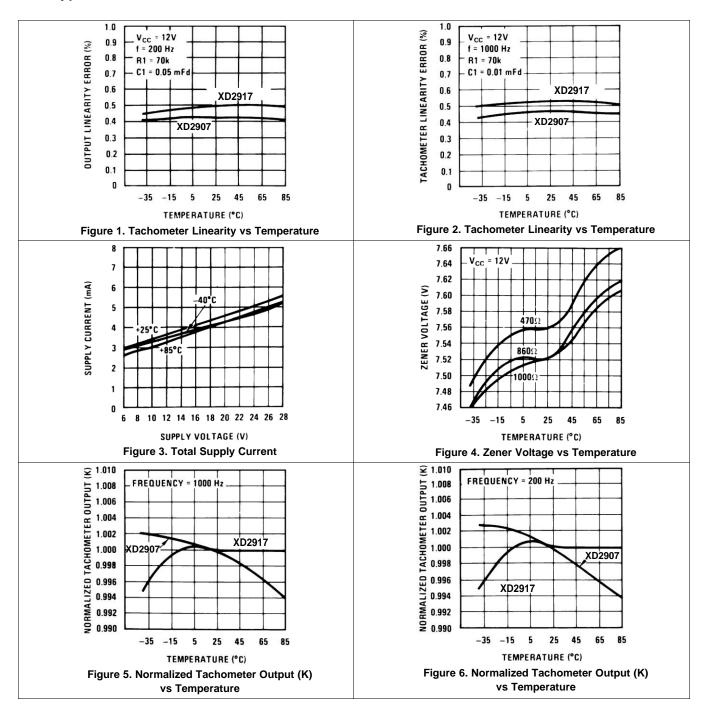

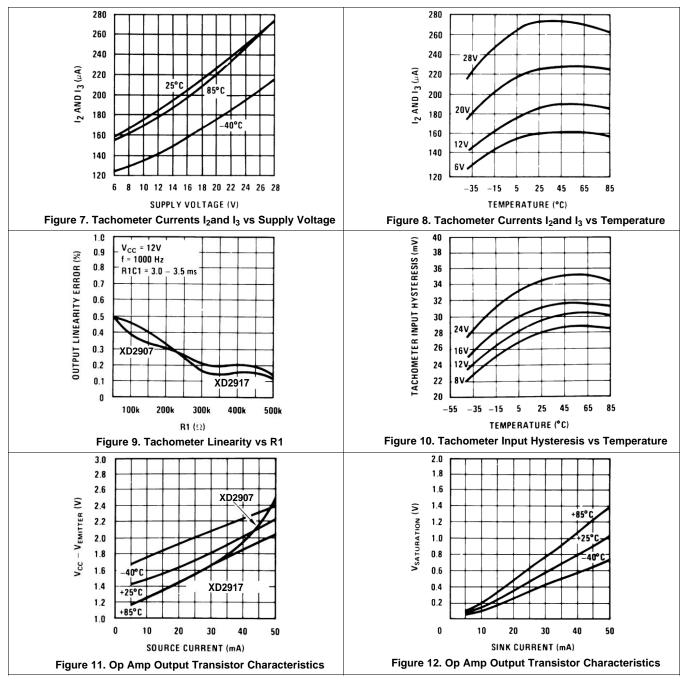

# 7.6 Typical Characteristics

# **Typical Characteristics (continued)**

# 8 Parameter Measurement Information

Figure 13. Test Circuit

Figure 14. Tachometer Input Threshold Measurement

# 9 Detailed Description

#### 9.1 Overview

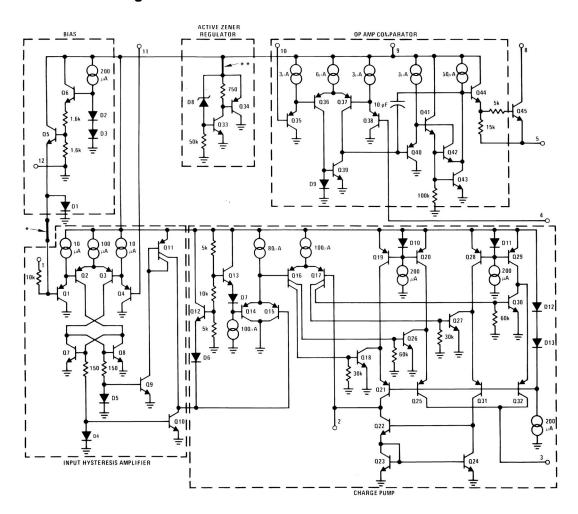

The XD29x7 frequency-to-voltage converter features two separate inputs to monitor the signal. In the 8-pin devices, one of these inputs is internally grounded and therefore it monitors the remaining input for zero crossings. In the 14-pin devices, both of these inputs are open and it instead detects whenever the differential voltage switches polarity. Therefore, the input comparator outputs a square wave of equal frequency to the input.

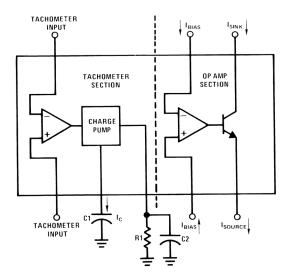

A charge pump system is used to translate the frequency of this square wave to a voltage. At the start of every positive half cycle of the input signal a 180- $\mu$ A constant current charges C1 until its voltage has increased by V<sub>CC</sub>/2. The capacitor is held at that voltage until the input signal begins a negative half cycle. Then the 180- $\mu$ A constant current discharges capacitor C1 until its voltage has dropped by V<sub>CC</sub>/2. This voltage is held until the next positive half cycle and the process repeats. This generates pulses of current flowing into and out of capacitor C1 at the same frequency as the input signal. For every full cycle, the charge pump mirrors both current pulses as positive current pulses into the parallel combination of resistor R1 and capacitor C2. Therefore every full cycle, the amount of charge leaving pin 3 is equal to the sum of the charge entering C1 and leaving C1. Because the voltage at pin 3 is equal to I3(avg) × R1, I(avg) is calculated in Equation 1.

$$I3(avg) = Q/t = (Qcharge + Qdischarge) / (1 / f) = 2 \times Q \times f = 2 \times C1 \times (V_{CC}/2) \times f = C1 \times V_{CC} \times f$$

(1)

This average current will be flowing across R1, giving the output voltage in Equation 2.

$$Vo = R1 \times C1 \times V_{CC} \times f \tag{2}$$

C2 acts as a filter to smooth the pulses of current and does not affect the output voltage. However, the size of C2 determines both the output response time for changes in frequency and the amount of output voltage ripple.

The voltage generated is then fed in a high gain op amp. This op amp drives a bipolar transistor whose collector and emitter are each broken out to a pin. The XD29x7 has the flexibility to be configured a variety of ways to meet system requirements including voltage output, driving loads, operating a relay, and more.

### 9.2 Functional Block Diagram

# 9.3 Feature Description

#### 9.3.1 Differential Input

This device features a Schmitt-Trigger comparator that is the first stage in converting the input signal. Every time the output of the comparator flips between high and low correlates to a half cycle elapsing on the input signal. On the XD29x7-8 devices, one terminal of this comparator is internally connected to ground. This requires that the input signal cross zero volts in order for device to detect the frequency. On the XD29x7 devices, the input terminals to the Schmitt-Trigger comparator are both available for use. This open terminal allows the potential at which the comparator's output is flipped to be applied externally. This allows the device to accept signals with DC offset or compare differential inputs.

### 9.3.2 Configurable

While the ratio of output voltage to input frequency is dependent on supply voltage, it is easily adjusted through the combination of one resistor and one capacitor, R1 and C1. The formula for calculating the expected output voltage is in Equation 3.

$$V_{OUT} = V_{CC} \times f \times C1 \times R1.$$

(3)

The sizes of R1 and C1 have other effects on the system such as maximum frequency and output linearity. See *Choosing R1 and C1* for detailed instructions on sizing components.

# **Feature Description (continued)**

### 9.3.3 Output Stage

The output voltage generated by the charge pump is fed in the noninverting terminal of a high gain op amp. This op amp then drives and uncommitted bipolar junction transistor. This allows the XD2907 to be configured a variety of ways to meet system needs. The output voltage can be buffered and used to drive a load (see Figure 15) or an output threshold can be given to trigger a load switch (see Figure 18).

#### 9.4 Device Functional Modes

### 9.4.1 Grounded Input Devices (8-Pin XD2907 and XD2917)

These devices have one of the two Schmitt-Trigger comparator inputs internally grounded and must be externally connected to the system ground as well. This configuration monitors the remaining terminal for zero crossings.

# 9.4.2 Differential Input Devices XD2907 and XD2917

These devices have both inputs to the Schmitt-Trigger comparator available and broken out to pins 1 and 11. This configuration allows a new switching threshold provided in the case of signals with DC offset or to intake a differential pair and switch based on voltage difference.

以上信息仅供参考. 如需帮助联系客服人员。谢谢 XINLUDA