### Filterless 2x8W Class- F Stereo Audio Amplifier

### **General Description**

The LPA2153 is a 2×8W, class-F audio amplifier with EQ function for both channel. It offers low THD+N, allowing it to achieve high-quality Power Supply sound reproduction. The new filterless architecture allows the device to drive the speaker directly requiring no low-pass output filters, thus to save the system cost and PCB area.

LPA2153 can display 2×8W output at 10% THD with 2  $\Omega$  load. When it provides 5V DC voltage, it can provide 2×3.4W output at 10% THD with 4  $\Omega$  load. The efficiency of LPA2153 is much better than that of class-AB cousins with the same numbers of external components. The LPA2153 is available in ESOP-16.

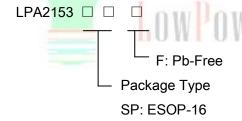

#### **Order Information**

### **Applications**

- ♦ Portable Bluetooth Speaker

- ♦ Cellular and Smart mobile phone

- ♦ Square Speaker

#### **Features**

- ◆ 500KHz fixed frequency switching for amplifier

- 2×3.3W Output at 10% THD with a 4 Ω Load and 5V PVDD for amplifier

- 2×4.8W Output at 10% THD with a 4 Ω Load and 6.0V PVDD for amplifier

- 2×8W Output at 10% THD with a 2 Ω Load and 6.0V

PVDD for amplifier

- Filterless, Low Quiescent Current and Low EMI

- ◆ Amplifier Efficiency up to 85%

- Free LC filter digital modulation, direct-drive speakers

- Thermal Shutdown

- Few external components to save the space and cost

- Pb-Free Package

## **Marking Information**

| Device          | Marking                                 | Package        | Shipping     |

|-----------------|-----------------------------------------|----------------|--------------|

| LPA2153         | LPS                                     | ESOP-16        | 3K/REEL      |

|                 | LPA2153                                 |                |              |

|                 | YWX                                     |                |              |

| V. V. ia vaar a | ada \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | alcanda V. Via | ariaa numbar |

Y: Y is year code. W: W is week code. X: X is series number.

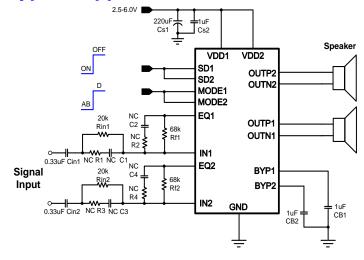

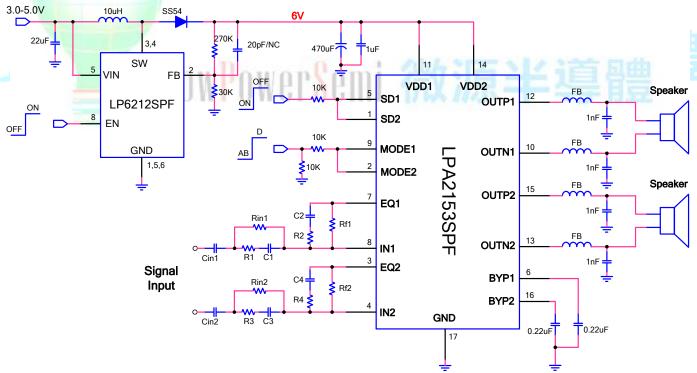

### **Typical Application Circuit**

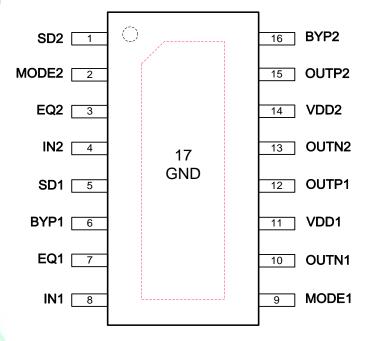

# **Pin Configuration**

**Functional Pin Description**

| Pin   | PIN No. | DESCRIPTION                                                                                                                                  |

|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

| SD2   | 1       | Channel 2 Shutdown pin (active high).                                                                                                        |

| MODE2 | 2       | Channel 2 Mode control pin (High voltage with Class_D mode and low voltage with Class_AB mode).                                              |

| EQ2   | 3       | Channel 2 EQ function pin(With resistor R4 and capacitor C4 in series between IN2 and EQ, the high frequencies could be attenuated).         |

| IN2   | 4       | Channel 2 Input of amplifier.( With resistor R3 and capacitor C3 in series between IN2 and signal, the low frequencies could be attenuated). |

| SD1   | 5       | Channel 1 Shutdown pin (active high).                                                                                                        |

| BYP1  | 6       | Channel 1 Bypass pin (Connect a 0.22uF capacitor between this pin and GND).                                                                  |

| EQ1   | 7       | Channel 1 EQ function pin(With resistor R2 and capacitor C2 in series between VIN and EQ, the high frequencies could be attenuated).         |

| IN1   | 8       | Channel 1 Input of amplifier.( With resistor R1 and capacitor C1 in series between IN1 and signal, the low frequencies could be attenuated). |

| MODE1 | 9       | Channel 1 Mode control pin (High voltage with Class_D mode and low voltage with Class_AB mode).                                              |

| OUTN1 | 10      | Channel 1 Negative output of signal.                                                                                                         |

| VDD1  | 11      | Channel 1 Voltage supply pin.                                                                                                                |

| OUTP1 | 12      | Channel 1 Positive output of signal.                                                                                                         |

| OUTN2 | 13      | Channel 2 Negative output of signal.                                                                                                         |

| VDD2  | 14      | Channel 2 Voltage supply pin.                                                                                                                |

| OUTP2 | 15      | Channel 2 Positive output of signal.                                                                                                         |

| BYP2  | 16      | Channel 2 Bypass pin (Connect a 0.22uF capacitor between this pin and GND).                                                                  |

| GND   | 17      | Ground pin.                                                                                                                                  |

# **Absolute Maximum Ratings**

| Maximum Junction Temperature Range    | 150°C          |

|---------------------------------------|----------------|

| Operation Ambient Temperature Range   | −40°C to 85°C  |

| Operation Junction Temperature Range  | −40°C to 125°C |

| Storage Temperature Range             | −65°C to 150°C |

| Lead Temperature (Soldering, 10 sec.) | 260°C          |

| Input voltage                         | 0.3V to 6.5V   |

### **Recommended Operating Conditions**

| Supply Input Voltage range               | 2.5V to 6.0V |

|------------------------------------------|--------------|

| Operation Ambient Temperature Range      |              |

| Operation Junction Temperature Range     |              |

| Thermal resistance (junction to ambient) | 110°C/W      |

LowPowerSemi 微源半導體

### **Electrical Characteristics For Both Channel**

(VDD = 5V, RL=4 $\Omega$  , TA = 25 $^{\circ}$  C, unless otherwise specified)

| Parameter             | Symbol            | Test Condition                              | Min      | Typ(RL) |         | Max      | Units |        |  |

|-----------------------|-------------------|---------------------------------------------|----------|---------|---------|----------|-------|--------|--|

| Parameter             | Syllibol          | rest Condition                              | 15       | IVIII   | Class-D | Class-AB | IVIAX | Ullits |  |

| Supply power          | VIN               |                                             |          | 2.5     |         |          | 6.0   | V      |  |

|                       |                   |                                             | VDD=6.0V |         | 4.8     | 4.7      |       |        |  |

|                       |                   | TUD: N. 400/                                | VDD=5.5V |         | 4.0     | 3.9      |       |        |  |

|                       |                   | THD+N=10%,<br>f=1KHz,RL=4Ω                  | VDD=5.0V |         | 3.3     | 3.3      |       |        |  |

|                       |                   |                                             | VDD=4.2V |         | 2.3     | 2.3      |       |        |  |

|                       |                   |                                             | VDD=3.6V |         | 1.7     | 1.7      |       |        |  |

|                       |                   |                                             | VDD=6.0V |         | 3.9     | 3.6      |       |        |  |

|                       |                   | TUD . N. 40/                                | VDD=5.5V |         | 3.3     | 3.1      |       |        |  |

| Output power          | Po                | THD+N=1%,<br>f=1KHz,RL=4Ω                   | VDD=5.0V |         | 2.7     | 2.5      |       | W      |  |

|                       |                   |                                             | VDD=4.2V |         | 1.9     | 1.8      |       |        |  |

| 150                   |                   |                                             | VDD=3.6V |         | 1.4     | 1.4      |       |        |  |

|                       |                   |                                             | VDD=6.0V |         | 8       | 8        |       | •      |  |

|                       | wer               | THD+N=10%,<br>f=1KHz,RL=2Ω                  | VDD=5.5V |         | 6.8     | 6.7      |       |        |  |

| 1                     |                   |                                             | VDD=5.0V |         | 5.6     | 5.6      |       |        |  |

| 1                     |                   |                                             | VDD=4.2V |         | 3.3     | 3.9      |       |        |  |

|                       | 17                | 112211                                      | VDD=3.6V |         | 2.3     | 2.9      |       |        |  |

| Power supply          | DCDD              | INPUT ac-grounded with                      | f=100HZ  | 77 9    | É       | 75       |       | 40     |  |

| ripple<br>rejection   | PSRR              | CIN=0.47uF, VDD=6.0V                        | f=1KHz   | W. II   | 131     | 50       |       | dB     |  |

| Signal-to-nois        | SNR               | VDD=5V,Class_AB                             | f=1KHz   |         |         | 91       |       | dB     |  |

| e ratio               | ONIX              | VDD=5V,Class_D                              | f=1KHz   |         | 90      |          |       | ub_    |  |

| Output noise          | V <sub>N</sub>    | INPUT ac-grounded with CIN=0.47uF, VDD=6.0V |          |         | 1       | 00       |       | μV     |  |

| Efficiency            | η                 | RL=4Ω, Po=3.2W                              | f=1KHz   |         | 84      |          |       | %      |  |

| Switching frequency   | f <sub>SW</sub>   | VDD=2.5V to 5.5V                            |          |         | 500     |          |       | kHz    |  |

| Output offset voltage | V <sub>os</sub>   | V <sub>SD</sub> =0V,VDD=5.0V                |          |         | 1.1     | 2.5      |       | mV     |  |

| Shutdown current      | I <sub>LEAK</sub> | V <sub>SD</sub> =VDD=5.0V                   |          |         |         | 2        |       | uA     |  |

| Quiescent current     | IQ                | VDD=5.0V                                    | No load  |         | 4       | 6.8      |       | mA     |  |

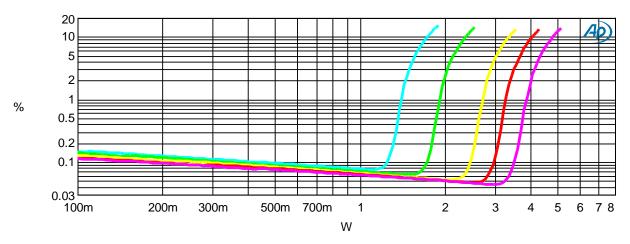

# **Typical Operating Characteristic For Both Channel**

**Audio Precision**

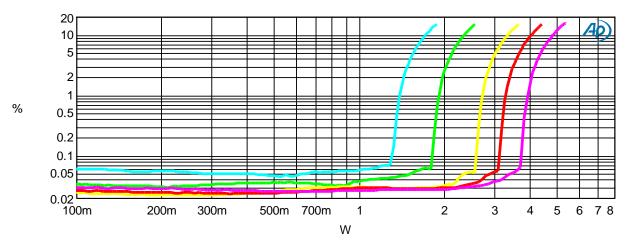

| Sweep | Trace  | Color         | Line Style     | Thick  | Data                                             | Axis | Comment           |

|-------|--------|---------------|----------------|--------|--------------------------------------------------|------|-------------------|

| 1 2   | 1      | Cyan<br>Green | Solid<br>Solid | 3      | Analyzer.THD+N Ratio A<br>Analyzer.THD+N Ratio A | Left | VDD=4.2V Class AB |

| 3     | 1<br>1 | Yellow<br>Red | Solid<br>Solid | 3<br>3 | Analyzer.THD+N Ratio A<br>Analyzer.THD+N Ratio A |      |                   |

| 5     | 1      | Magenta       | Solid          | 3      | Analyzer.THD+N Ratio A                           |      |                   |

PO VS THD(4ohm AB).ats2

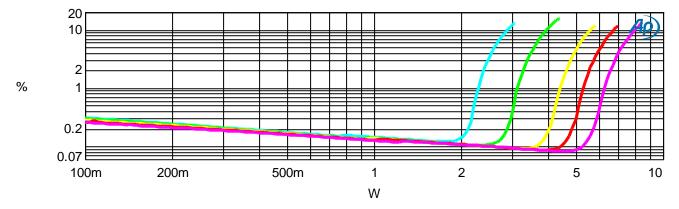

#### **Audio Precision**

| Sweep | Trace | Color   | Line Style | Thick | Data                   | Axis | Comment          |

|-------|-------|---------|------------|-------|------------------------|------|------------------|

| 1     | 1     | Cyan    | Solid      | 3     | Analyzer.THD+N Ratio A | Left | VDD=3.6V Class D |

| 2     | 1     | Green   | Solid      | 3     | Analyzer.THD+N Ratio A | Left | VDD=4.2V Class D |

| 3     | 1     | Yellow  | Solid      | 3     | Analyzer.THD+N Ratio A | Left | VDD=5.0V Class D |

| 4     | 1     | Red     | Solid      | 3     | Analyzer.THD+N Ratio A | Left | VDD=5.5V Class D |

| 5     | 1     | Magenta | Solid      | 3     | Analyzer.THD+N Ratio A | Left | VDD=6.0V Class D |

PO VS THD(4ohm D).ats2

### **Audio Precision**

| Sweep                 | Trace            | Color                                     | Line Style                                | Thick                 | Data                                                                                                                           | Axis                 | Comment                                                     |

|-----------------------|------------------|-------------------------------------------|-------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5 | 1<br>1<br>1<br>1 | Cyan<br>Green<br>Yellow<br>Red<br>Magenta | Solid<br>Solid<br>Solid<br>Solid<br>Solid | 3<br>3<br>3<br>3<br>3 | Analyzer.THD+N Ratio A<br>Analyzer.THD+N Ratio A<br>Analyzer.THD+N Ratio A<br>Analyzer.THD+N Ratio A<br>Analyzer.THD+N Ratio A | Left<br>Left<br>Left | VDD=4.2V Class AB<br>VDD=5.0V Class AB<br>VDD=5.5V Class AB |

P0 VS THD(2ohm AB).ats2

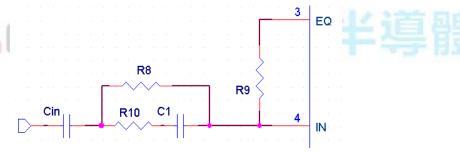

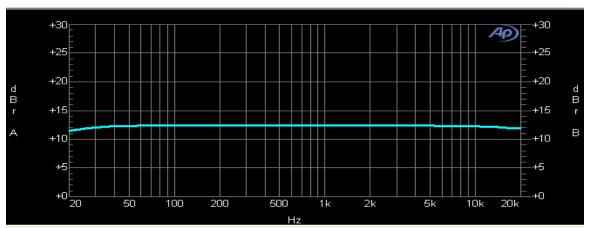

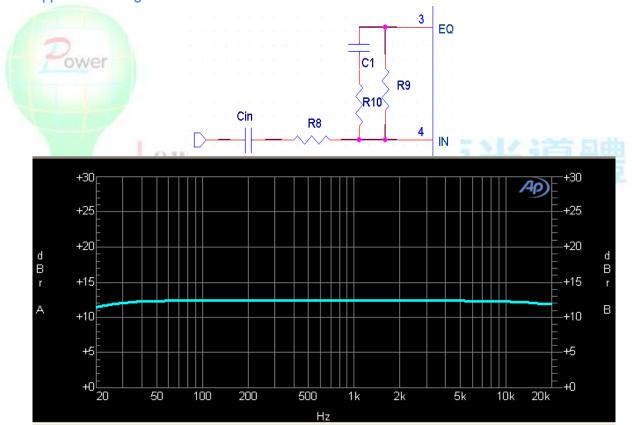

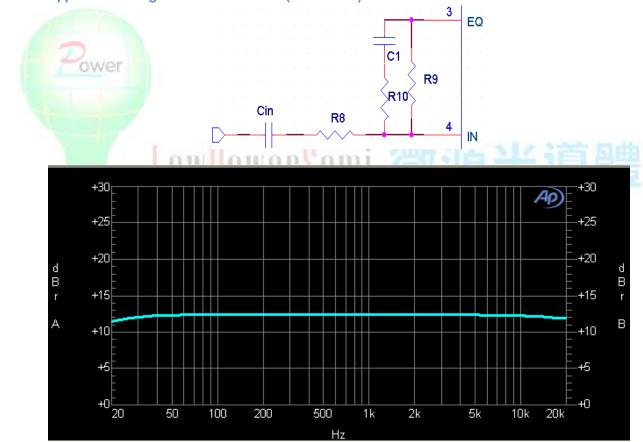

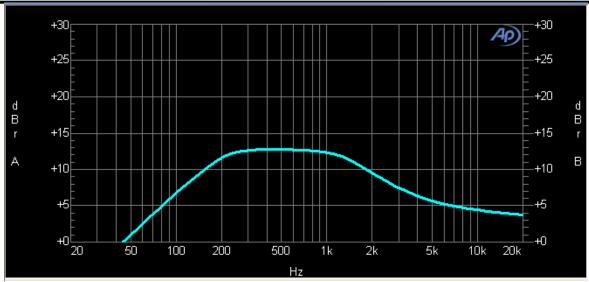

C1=NC, R10=NC, R8=18K, R9=33K, Cin=0.22uF

# LowPowerSemi 微源半導體

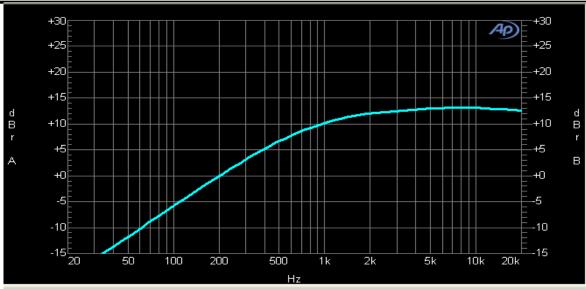

C1=10nF, R10=20K, R8=18K, R9=47K, Cin=0.1uF

#### Classical Application 2: High Restraint

C1=NC, R10=NC, R8=18K, R9=33K, Cin=0.22uF

# LowPowerSemi 微源半導體

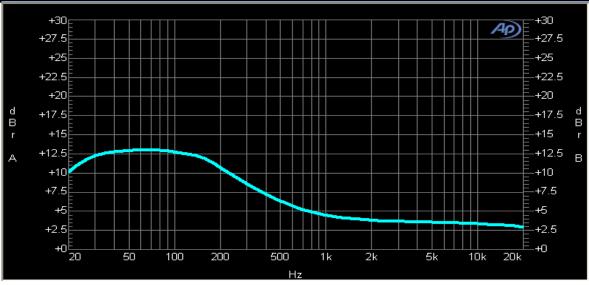

C1=33nF, R10=10K,R9=47K,R8=10K,Cin=1uF

C1=NC, R10=NC, R8=18K, R9=33K, Cin=0.22uF

# **Preliminary Datasheet**

C1=10nF, R10=10K,R9=47K,R8=12K,Cin=0.047uF

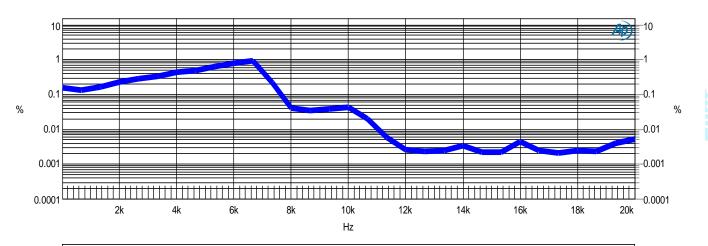

#### **Audio Precision**

#### A-A THD+N vs FREQUENCY

| Sweep | Trace | Color        | Line Style     | Thick  | Data                                             | Axis | Comment |

|-------|-------|--------------|----------------|--------|--------------------------------------------------|------|---------|

| 1     | 1 2   | Cyan<br>Blue | Solid<br>Solid | 1<br>7 | Analyzer.THD+N Ratio B<br>Analyzer.THD+N Ratio B |      |         |

A single sweeps produces a stereo THD+N sweep of Ch A and Ch B when data 1 is set for THD+N and the Stereo box is checked. The upper Analyzer bandwidth is 20kHz. At a 6kHz fundamental only the 2nd and 3rd harmonics are included, above 10kHz only the noise is included in the measurement bandwidth. For band-limited systems IMD testing is better.

A-A THD+N VS FREQ @4ohm PO=3W CLASS D VDD=6V.ats2

LPA2153-00 May.-2014 Email: <a href="marketing@lowpowersemi.com">marketing@lowpowersemi.com</a> <a href="marketing@lowpowersemi.com">www.lowpowersemi.com</a> Page 9 of 13

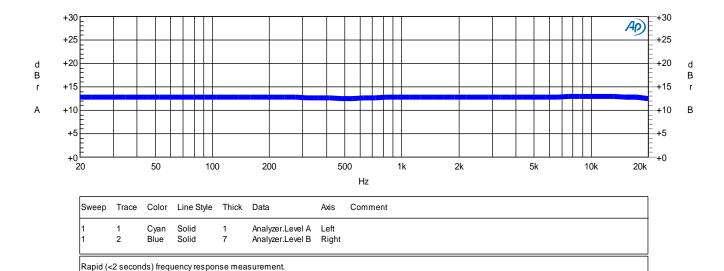

**Audio Precision**

A-A FREQ RESP FAST @ 4ohm PO=4.8W CLASS AB VDD=6V.ats 2

# **Applications Information For Both Channel**

Optimize for a detailed view.

Can be even faster if the lowest frequencies are not included Press F4 to set the 1kHz dbr A and dBr B reference.

#### **Maximum Gain**

The LPA2153 has two internal amplifier stages. The first stage's gain is externally configurable, while the second stage's is internally fixed. The closed-loop gain of the first stage is set by selecting the ratio of Rf to Rin while the second stage's gain is fixed at 1.5x. The output of amplifier serves as the input to amplifier 2, thus the two amplifiers produce signals identical in magnitude, but different in phase by 180°. Consequently, the differential gain for the IC is: Av=2\*1.5\*Rf / Rin (for class\_AB & class\_D)

#### **Shutdown operation**

In order to reduce power consumption while not in use, the LPA2153 contains shutdown circuitry to turn off the amplifier's bias circuitry. This shutdown feature turns the amplifier off when logic high is applied to the SD pin. By switching the SD pin pull up to VDD, the LPA2153 supply current draw will be minimized in idle mode.

#### Power supply decoupling

The LPA2153 is a high performance CMOS audio amplifier that requires adequate power supply decoupling to ensure the output THD and PSRR a low as possible. Optimum decoupling is achieved by using two capacitors of different types targeting to different types of noise on the power supply leads. For higher frequency transients, spikes, or digital the line, low hash on а good equivalent-series-resistance(ESR) ceramic capacitor, typically 1.0µF, works best, placing it as close as possible to the device VDD terminal. For filtering lower-frequency noise signals, a large capacitor of 20µF(ceramic) or greater is recommended, placing it near the audio power amplifier.

#### Signal Frequency suppress

The LPA2153 has a EQ pin which is the negative output of amplifier as show below. With R2 and C2, we can suppress high frequency part of signal. And the low frequency part of signal could be attenuated by R1 and C1.

#### **Preliminary Datasheet** LPA2153

into the output drive signal. This noise is from the internal analog reference to the amplifier, which appears as degraded PSRR and THD+N.

# $f_L = \frac{1}{2\pi R_2 C_2}$ EQ Rin **€** R3 IN Cin R1 C1

#### **Over Temperature Protection**

Thermal protection on the LPA2153 prevents the device from damage when the internal temperature exceeds 150°C. There is a 15 degree tolerance on this trip point from device to device. Once the die temperature exceeds the thermal set point, the device outputs are disabled. This is not a latched fault. The thermal fault is cleared once the temperature of the die is reduced by 30°C. This large hysteresis will prevent motor boating sound well and the device begins normal operation at this point without external system intervention. Semi 微源半

#### Analog Reference Bypass Capacitor (CBYP)

In addition to system cost and size, click and pop performance is affected by the size of the input coupling capacitor, CBYP. A larger input coupling capacitor requires more charge to reach its quiescent DC voltage (nominally 1/2 VDD). This charge comes from the internal circuit via the feedback and is apt to create pops upon device enable. Thus, by minimizing the capacitor size based on necessary low frequency response, turn-on pops can be minimized.

The Analog Reference Bypass Capacitor (CBYP) is the most critical capacitor and serves several important functions. During start-up or recovery from shutdown mode, CBYP determines the rate at which the amplifier starts up. The second function is to reduce noise caused by the power supply coupling

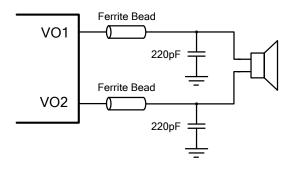

#### How to reduce EMI

A simple solution is to put an additional capacitor 220pF at power supply terminal for power line. The traces from amplifier to speakers should design as short as we can.

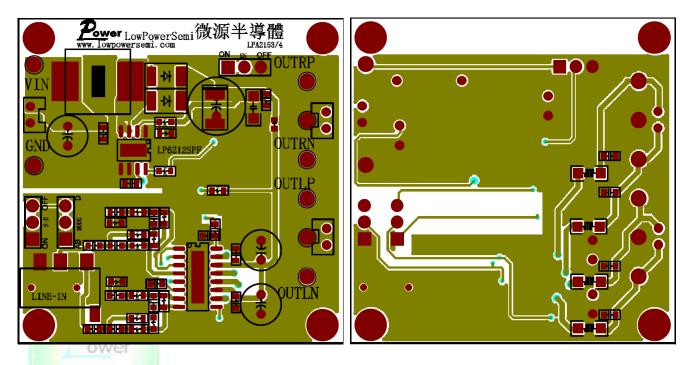

#### **PCB LAYOUT**

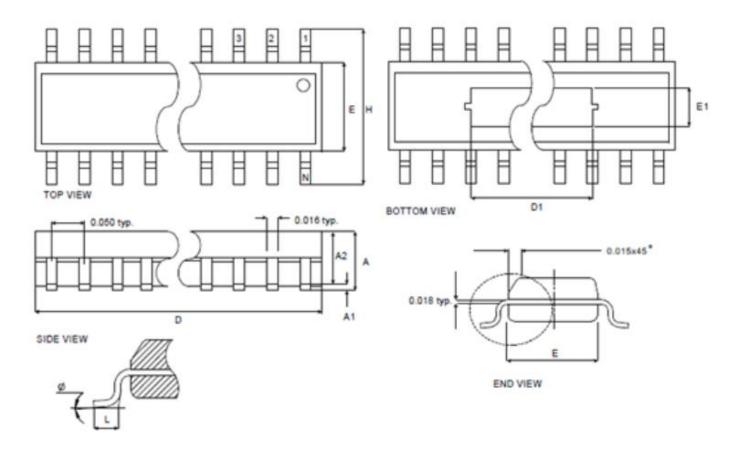

# **Packaging Information**

#### ESOP16

| Dim | Millim | neters | Inches    |       |  |

|-----|--------|--------|-----------|-------|--|

| Dim | Min.   | Max.   | Min.      | Max.  |  |

| Α   | 1.35   | 1.75   | 0.053     | 0.069 |  |

| A1  | 0.10   | 0.25   | 0.004     | 0.010 |  |

| ۵   | 9.80   | 10.0   | 0.386     | 0.394 |  |

| D1  | 4.115  | REF    | 0.162 REF |       |  |

| E   | 3.81   | 3.99   | 0.150     | 0.157 |  |

| E1  | 2.184  | REF    | 0.086 REF |       |  |

| Н   | 5.79   | 6.20   | 0.228     | 0.244 |  |

| L   | 0.41   | 1.27   | 0.016     | 0.050 |  |

| ф   | 0°     | 8°     | 0°        | 8°    |  |