**TPS7A52-Q1**

SBVS296B - SEPTEMBER 2017-REVISED JUNE 2018

# TPS7A52-Q1 2-A, High-Accuracy, Automotive-Grade, Low-Noise, LDO Voltage Regulator

#### **Features**

- **Qualified for Automotive Applications**

- AEC-Q100 Qualified for Automotive Applications:

- Temperature Grade 1: –40°C ≤ T<sub>A</sub> ≤ +125°C

- HBM ESD Classification Level 2

- CDM ESD Classification Level C4A

- Extended Junction Temperature (T<sub>1</sub>) Range: -40°C to +150°C

- Input Voltage Range:

- Without BIAS: 1.4 V to 6.5 V

- With BIAS: 1.1 V to 6.5 V

- Adjustable Output Voltage Range: 0.8 V to 5.2 V

- Low Dropout: 115 mV (max) at 2 A With BIAS

- Output Voltage Noise: 4.4 µV<sub>RMS</sub>

- 1% (max) Accuracy Over Line, Load, and Temperature With BIAS

- Power-Supply Ripple Rejection:

- 40 dB at 500 kHz

- Adjustable Soft-Start Inrush Control

- Open-Drain, Power-Good (PG) Output

- Packages:

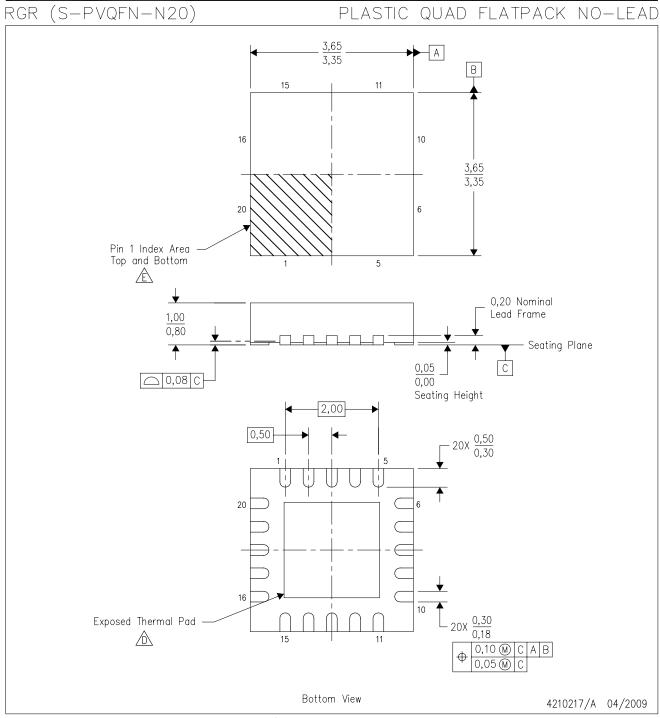

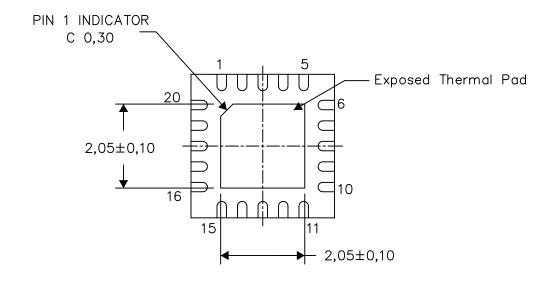

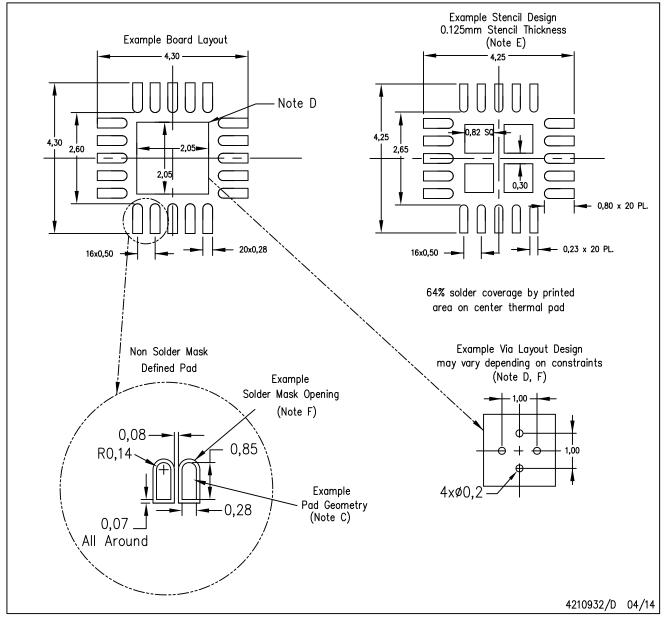

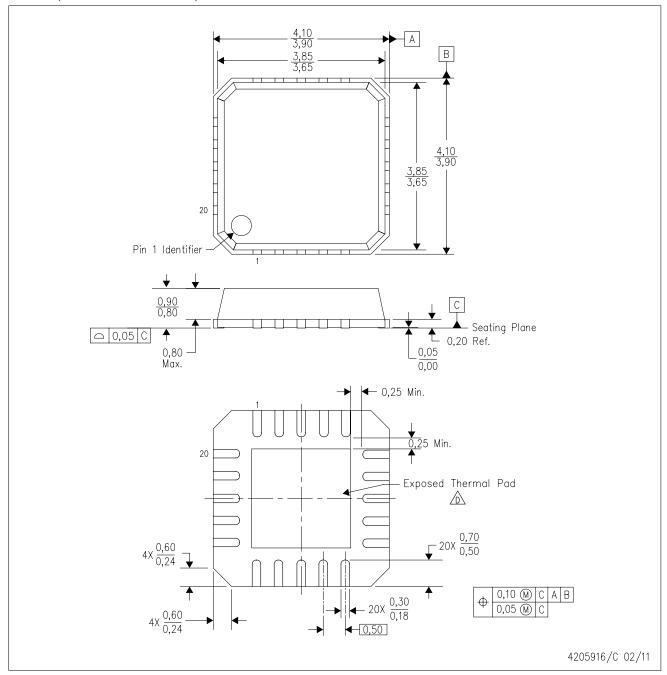

- 3.5-mm × 3.5-mm, 20-Pin VQFN

- 4-mm x 4-mm, 20-Pin VQFNP With Wettable Flanks and High CTE (12 ppm/°C) Mold Compound

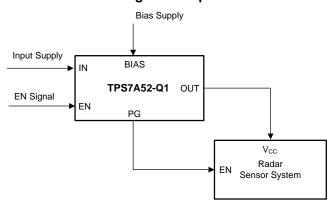

# 2 Applications

- **Telematic Control Units**

- Infotainment and Clusters

- High-Speed Interfaces (PLL and VCO)

## 3 Description

The TPS7A52-Q1 device is a low-noise (4.4 µV<sub>RMS</sub>), low-dropout linear regulator (LDO) capable of sourcing 2 A with only 115 mV of maximum dropout. The device output voltage is adjustable from 0.8 V to 5.2 V using an external resistor divider.

The combination of low-noise (4.4 µV<sub>RMS</sub>), high-PSRR, and high output current capability makes the TPS7A52-Q1 ideal to power noise-sensitive components such as those found in radar power and infotainment applications. The high performance of this device limits power-supply-generated phase noise and clock jitter, making this device ideal for powering RF amplifiers, radar sensors, and chipsets. Specifically, RF amplifiers benefit from the highperformance and 5.0-V output capability of the device.

For digital loads [such as application-specific integrated circuits (ASICs), field-programmable gate arrays (FPGAs), and digital signal processors (DSPs)] requiring low-input voltage, low-output (LILO) voltage operation, the exceptional accuracy (1% over load and temperature), remote sensing, excellent transient performance, and soft-start capabilities of TPS7A52-Q1 provides optimal performance.

The versatility of the TPS7A52-Q1 makes the device a component of choice for many demanding applications.

#### Device Information<sup>(1)</sup>

| PART<br>NUMBER | PACKAGE                   | BODY SIZE (NOM)   |

|----------------|---------------------------|-------------------|

| TPS7A52-Q1     | VQFN (20)                 | 3.50 mm × 3.50 mm |

|                | Wettable flank VQFNP (20) | 4.00 mm x 4.00 mm |

(1) For all available packages, see the package option addendum at the end of the datasheet.

#### **Powering RF Components**

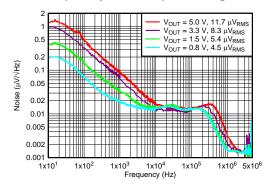

#### **Output Voltage Noise vs** Frequency and Output Voltage

# **Table of Contents**

| 1 | Features 1                           | 8  | Application and Implementation                      | 20                  |

|---|--------------------------------------|----|-----------------------------------------------------|---------------------|

| 2 | Applications 1                       |    | 8.1 Application Information                         | 20                  |

| 3 | Description 1                        |    | 8.2 Typical Application                             | 28                  |

| 4 | Revision History2                    | 9  | Power Supply Recommendations                        | 29                  |

| 5 | Pin Configuration and Functions 3    | 10 | Layout                                              | 30                  |

| 6 | Specifications4                      |    | 10.1 Layout Guidelines                              | 30                  |

|   | 6.1 Absolute Maximum Ratings 4       |    | 10.2 Layout Example                                 | 3                   |

|   | 6.2 ESD Ratings 4                    | 11 | Device and Documentation Support                    | 32                  |

|   | 6.3 Recommended Operating Conditions |    | 11.1 Device Support                                 | 32                  |

|   | 6.4 Thermal Information5             |    | 11.2 Documentation Support                          | 32                  |

|   | 6.5 Electrical Characteristics5      |    | 11.3 Receiving Notification of Documentation Update | es <mark>3</mark> 3 |

|   | 6.6 Typical Characteristics          |    | 11.4 Community Resources                            | 33                  |

| 7 | Detailed Description 14              |    | 11.5 Trademarks                                     | 33                  |

|   | 7.1 Overview                         |    | 11.6 Electrostatic Discharge Caution                | 33                  |

|   | 7.2 Functional Block Diagram         |    | 11.7 Glossary                                       | 33                  |

|   | 7.3 Feature Description              |    | Mechanical, Packaging, and Orderable                | 2                   |

|   | 7.4 Device Functional Modes          |    | Information                                         | 3.                  |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С        | changes from Revision A (February 2018) to Revision B                                                                                    | Page           |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| •        | Added new RTK (VQFNP) package and associated content                                                                                     | 1              |

| •        | Changed plots at I <sub>OUT</sub> > 2 A in <i>Typical Characteristics</i> section to match values shown in <i>Specifications</i> section | 7              |

| •        | Changed all I <sub>OUT</sub> test conditions from 3 A to 2 A to match values shown in <i>Specifications</i> section                      | <mark>7</mark> |

| •        | Changed all plots to use default C <sub>OUT</sub> = 22 μF                                                                                | <mark>7</mark> |

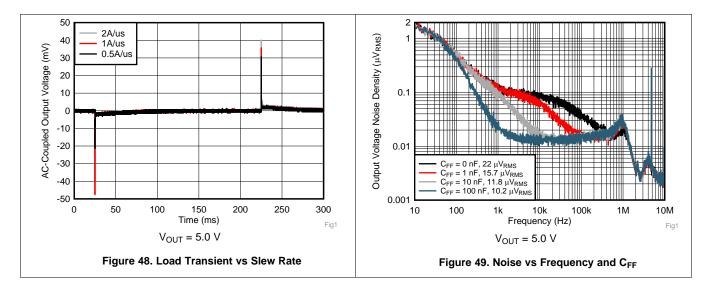

| •        | Changed Figure 48 to load transient plot                                                                                                 | 29             |

| <u>•</u> | Changed Figure 49 to noise plot                                                                                                          | 29             |

| С        | Changes from Original (September 2017) to Revision A                                                                                     | Page           |

| •        | Changed from product preview to production data (active)                                                                                 | 1              |

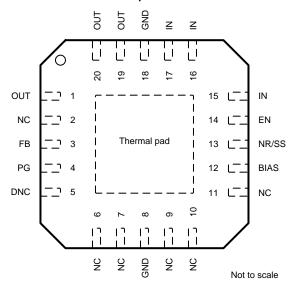

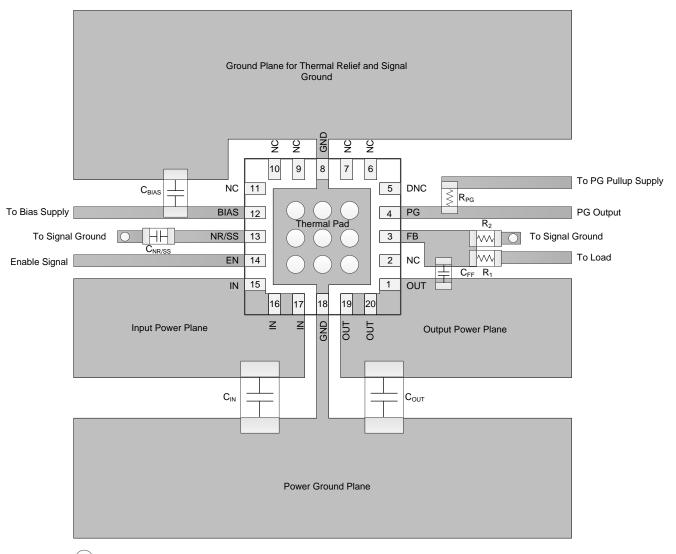

# 5 Pin Configuration and Functions

RGR Package 3.5-mm × 3.5-mm, 20-Pin VQFN **Top View** GND PUO OUT z Z ا∟ 20 18 17 16 OUT 15 IN NC ΕN Thermal FΒ NR/SS Pad PG BIAS DNC NC GND 2 2 2 2 Not to scale

RTK Package 4-mm × 4-mm, 20-Pin VQFNP With Wettable Flanks Top View

## **Pin Functions**

|             | PIN                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.                   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BIAS        | 12                    | I   | BIAS supply voltage. This pin enables the use of low-input voltage, low-output (LILO) voltage conditions (that is, $V_{IN} = 1.2 \text{ V}$ , $V_{OUT} = 1 \text{ V}$ ) to reduce power dissipation across the die. The use of a BIAS voltage improves dc and ac performance for $V_{IN} \leq 2.2 \text{ V}$ . A 10- $\mu$ F capacitor or larger must be connected between this pin and ground. If not used, this pin must be left floating or tied to ground. |

| DNC         | 5                     | _   | Do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| EN          | 14                    | I   | Enable pin. Driving this pin to logic high enables the device; driving this pin to logic low disables the device. If enable functionality is not required, this pin must be connected to IN or BIAS.                                                                                                                                                                                                                                                           |

| FB          | 3                     | I   | Feedback pin connected to the error amplifier. Although not required, a 10-nF feed-forward capacitor from FB to OUT (as close to the device as possible) is recommended to maximize ac performance. The use of a feed-forward capacitor can disrupt PG (power good) functionality.                                                                                                                                                                             |

| GND         | 8, 18                 | _   | Ground pin. These pins must be connected to ground, the thermal pad, and each other with a low-impedance connection.                                                                                                                                                                                                                                                                                                                                           |

| IN          | 15-17                 | I   | Input supply voltage pin. A 10-μF or larger ceramic capacitor (5 μF or greater of capacitance) from IN to ground is recommended to reduce the impedance of the input supply. Place the input capacitor as close to the input as possible.                                                                                                                                                                                                                      |

| NC          | 2, 6, 7, 9,<br>10, 11 | _   | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NR/SS       | 13                    | _   | Noise-reduction and soft-start pin. Connecting an external capacitor between this pin and ground reduces reference voltage noise and also enables the soft-start function. Although not required, a 10-nF or larger capacitor is recommended to be connected from NR/SS to GND (as close to the pin as possible) to maximize ac performance.                                                                                                                   |

| OUT         | 1, 19, 20             | 0   | Regulated output pin. A 22- $\mu$ F or larger ceramic capacitor (10 $\mu$ F or greater of capacitance) from OUT to ground is required for stability and must be placed as close to the output as possible. Minimize the impedance from the OUT pin to the load.                                                                                                                                                                                                |

| PG          | 4                     | 0   | Active-high, power-good pin. An open-drain output indicates when the output voltage reaches $V_{\text{IT}(PG)}$ of the target. The use of a feed-forward capacitor may disrupt PG (power good) functionality.                                                                                                                                                                                                                                                  |

| Thermal pad | Thermal pad           | _   | Connect the thermal pad to a large-area ground plane. The thermal pad is internally connected to GND.                                                                                                                                                                                                                                                                                                                                                          |

Copyright © 2017–2018, Texas Instruments Incorporated

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over junction temperature range (unless otherwise noted)(1)

|             |                                                           | MIN         | MAX                   | UNIT |

|-------------|-----------------------------------------------------------|-------------|-----------------------|------|

| Voltage     | IN, BIAS, PG, EN                                          | -0.3        | 7.0                   |      |

|             | IN, BIAS, PG, EN (5% duty cycle, pulse duration = 200 μs) | -0.3        | 7.5                   | .,   |

|             | OUT <sup>(2)</sup>                                        | -0.3        | V <sub>IN</sub> + 0.3 | V    |

|             | NR/SS, FB                                                 | -0.3        | 3.6                   |      |

| Comment     | OUT                                                       | Interna     | Illy limited          | Α    |

| Current     | PG (sink current into device)                             |             | 5                     | mA   |

| Temperature | Operating junction, T <sub>J</sub>                        | <b>-</b> 55 | 150                   | ۰.   |

|             | Storage, T <sub>stg</sub>                                 | <b>-</b> 55 | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                                            |                                              |                                                         | VALUE | UNIT |

|--------------------------------------------|----------------------------------------------|---------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Floatroatatio diasharas                      | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 |      |

|                                            | Charged-device model (CDM), per AEC Q100-011 | ±500                                                    | V     |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions

over junction temperature range (unless otherwise noted)

|                    |                                                                                | MIN | NOM  | MAX      | UNIT |

|--------------------|--------------------------------------------------------------------------------|-----|------|----------|------|

| $V_{IN}$           | Input supply voltage range                                                     | 1.1 |      | 6.5      | V    |

| $V_{BIAS}$         | Bias supply voltage range <sup>(1)</sup>                                       | 3.0 |      | 6.5      | V    |

| V <sub>OUT</sub>   | Output voltage range (2)                                                       | 0.8 |      | 5        | V    |

| $V_{EN}$           | Enable voltage range                                                           | 0   |      | $V_{IN}$ | V    |

| I <sub>OUT</sub>   | Output current                                                                 | 0   |      | 2        | Α    |

| C <sub>IN</sub>    | Input capacitor                                                                | 10  | 22   |          | μF   |

| C <sub>BIAS</sub>  | Bias capacitor                                                                 | 10  |      |          | μF   |

| $R_{PG}$           | Power-good pullup resistance                                                   | 10  |      | 100      | kΩ   |

| C <sub>NR/SS</sub> | NR/SS capacitor                                                                |     | 10   |          | nF   |

| $C_{FF}$           | Feed-forward capacitor                                                         |     | 10   |          | nF   |

| R <sub>1</sub>     | Top resistor value in feedback network for adjustable operation <sup>(3)</sup> |     | 12.1 |          | kΩ   |

| R <sub>2</sub>     | Bottom resistor value in feedback network for adjustable operation             |     | 160  |          | kΩ   |

| TJ                 | Operating junction temperature                                                 | -40 | ·    | 150      | °C   |

<sup>(1)</sup> BIAS supply is required when the  $V_{IN}$  supply is below 1.4 V. Conversely, no BIAS supply is required when the  $V_{IN}$  supply is higher than or equal to 1.4 V. A BIAS supply helps improve dc and ac performance for  $V_{IN} \le 2.2$  V.

<sup>(2)</sup> The absolute maximum rating is  $V_{\rm IN}$  + 0.3 V or 7.0 V, whichever is smaller.

<sup>(2)</sup> This output voltage range does not include device accuracy or accuracy of the feedback resistors.

<sup>(3)</sup> The 12.1-k $\Omega$  resistor is selected to optimize PSRR and noise by matching the internal R<sub>1</sub> value.

#### 6.4 Thermal Information

|                      |                                              | TPS7/      | TPS7A52-Q1  |      |  |  |

|----------------------|----------------------------------------------|------------|-------------|------|--|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | RGR (VQFN) | RTK (VQFNP) | UNIT |  |  |

|                      |                                              | 20 PINS    | 20 PINS     |      |  |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 43.4       | 39.9        | °C/W |  |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 36.8       | 32.1        | °C/W |  |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 17.6       | 16.9        | °C/W |  |  |

| $\Psi_{\text{JT}}$   | Junction-to-top characterization parameter   | 0.8        | 0.4         | °C/W |  |  |

| $Y_{JB}$             | Junction-to-board characterization parameter | 17.6       | 16.9        | °C/W |  |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 3.4        | 1.6         | °C/W |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

## 6.5 Electrical Characteristics

over operating junction temperature range (T $_J$  =  $-40^{\circ}$ C to +150°C),  $V_{IN}$  = 1.4 V or  $V_{IN}$  =  $V_{OUT(nom)}$  + 0.4 V (whichever is greater),  $V_{BIAS}$  = open,  $V_{OUT(nom)}$  = 0.8  $V^{(1)}$ , OUT connected to 50  $\Omega$  to GND $^{(2)}$ ,  $V_{EN}$  = 1.1 V,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 22  $\mu$ F,  $C_{NR/SS}$  without  $C_{FF}$ , and PG pin pulled up to  $V_{IN}$  with 100  $k\Omega$  (unless otherwise noted); typical values are at  $T_J$  = 25°C

|                                   | PARAMETER                        |                    | TEST CONDITIONS                                                                                                                                                                                                          | MIN                                                                                                                                                                 | TYP    | MAX   | UNIT  |  |

|-----------------------------------|----------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|--|

| V <sub>FB</sub>                   | Feedback voltage                 |                    |                                                                                                                                                                                                                          |                                                                                                                                                                     | 0.8    |       | V     |  |

| V <sub>NR/SS</sub>                | NR/SS pin voltage                |                    |                                                                                                                                                                                                                          |                                                                                                                                                                     | 0.8    |       | V     |  |

| V <sub>UVLO1+(IN)</sub>           | Rising input supply              | UVLO with BIAS     | V <sub>IN</sub> rising with V <sub>BIAS</sub> = 3.0 V                                                                                                                                                                    |                                                                                                                                                                     | 1.02   | 1.09  | V     |  |

| V <sub>HYS1(IN)</sub>             | V <sub>UVLO1(IN)</sub> hysteresi | S                  | V <sub>BIAS</sub> = 3.0 V                                                                                                                                                                                                |                                                                                                                                                                     | 320    |       | mV    |  |

| V <sub>UVLO1-(IN)</sub>           | Falling input supply             | UVLO with BIAS     | $V_{IN}$ falling with $V_{BIAS} = 3.0 \text{ V}$                                                                                                                                                                         | 0.55                                                                                                                                                                | 0.711  |       | V     |  |

| V <sub>UVLO2+(IN)</sub>           | Rising input supply              | UVLO without BIAS  | V <sub>IN</sub> rising                                                                                                                                                                                                   |                                                                                                                                                                     | 1.31   | 1.39  | V     |  |

| V <sub>HYS2(IN)</sub>             | V <sub>UVLO2(IN)</sub> hysteresi | s                  |                                                                                                                                                                                                                          |                                                                                                                                                                     | 253    |       | mV    |  |

| V <sub>UVLO2-(IN)</sub>           | Falling input supply             | UVLO without BIAS  | V <sub>IN</sub> falling                                                                                                                                                                                                  | 0.65                                                                                                                                                                | 1.064  |       | V     |  |

| V <sub>UVLO+(BIAS)</sub>          | Rising bias supply               | UVLO               | V <sub>BIAS</sub> rising, V <sub>IN</sub> = 1.1 V                                                                                                                                                                        |                                                                                                                                                                     | 2.83   | 2.9   | V     |  |

| V <sub>UVLO-(BIAS)</sub>          | Falling bias supply              | UVLO               | V <sub>BIAS</sub> falling, V <sub>IN</sub> = 1.1 V                                                                                                                                                                       | 2.45                                                                                                                                                                | 2.531  |       | V     |  |

| V <sub>HYS(BIAS)</sub>            | V <sub>UVLO(BIAS)</sub> hysteres | sis                | V <sub>IN</sub> = 1.1 V                                                                                                                                                                                                  |                                                                                                                                                                     | 290    |       | mV    |  |

|                                   |                                  | Range              |                                                                                                                                                                                                                          | 0.8                                                                                                                                                                 |        | 5.2   | V     |  |

| V <sub>оит</sub>                  |                                  | Accuracy           | $0.8 \text{ V} \le \text{V}_{\text{OUT}} \le 5.15 \text{ V}, 5 \text{ mA} \le \text{I}_{\text{OUT}} \le 2 \text{ A, over}$<br>$\text{V}_{\text{IN}}$ , $-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}$ | -2.0%                                                                                                                                                               |        | 1.0%  |       |  |

|                                   | Output voltage                   | Output voltage     | Accuracy with BIAS                                                                                                                                                                                                       | $V_{IN} = 1.1 \text{ V}, 5 \text{ mA} \le I_{OUT} \le 2 \text{ A}, 3.0 \text{ V} \le V_{BIAS} \le 6.5 \text{ V}, -40^{\circ}\text{C} < T_{J} < 150^{\circ}\text{C}$ | -1.75% |       | 0.75% |  |

|                                   |                                  | Accuracy           | $0.8 \text{ V} \le \text{V}_{\text{OUT}} \le 5.15 \text{ V}, 5 \text{ mA} \le \text{I}_{\text{OUT}} \le 2 \text{ A, over}$<br>$\text{V}_{\text{IN}}, -40^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}$    | -1%                                                                                                                                                                 |        | 1%    |       |  |

|                                   |                                  | Accuracy with BIAS | $V_{IN} = 1.1 \text{ V, 5 mA} \le I_{OUT} \le 2 \text{ A, } 3.0 \text{ V} \le V_{BIAS} \le 6.5 \text{ V, } -40^{\circ}\text{C} < T_{J} < 125^{\circ}\text{C}$                                                            | -0.75%                                                                                                                                                              |        | 0.75% |       |  |

| $\Delta V_{OUT} / \Delta V_{IN}$  | Line regulation                  |                    | I <sub>OUT</sub> = 5 mA, 1.4 V ≤ V <sub>IN</sub> ≤ 6.5 V                                                                                                                                                                 |                                                                                                                                                                     | 0.03   |       | mV/V  |  |

|                                   |                                  |                    | $5 \text{ mA} \le I_{OUT} \le 2 \text{ A}, 3.0 \text{ V} \le V_{BIAS} \le 6.5 \text{ V},$<br>$V_{IN} = 1.1 \text{ V}$                                                                                                    |                                                                                                                                                                     | 0.07   |       |       |  |

| $\Delta V_{OUT} / \Delta I_{OUT}$ | Load regulation                  |                    | 5 mA ≤ I <sub>OUT</sub> ≤ 2 A                                                                                                                                                                                            |                                                                                                                                                                     | 0.08   |       | mV/A  |  |

|                                   |                                  |                    | 5 mA ≤ I <sub>OUT</sub> ≤ 2 A, V <sub>OUT</sub> = 5.2 V                                                                                                                                                                  |                                                                                                                                                                     | 0.04   |       |       |  |

|                                   |                                  |                    | V <sub>IN</sub> = 1.4 V, I <sub>OUT</sub> = 2 A, V <sub>FB</sub> = 0.8 V – 3%                                                                                                                                            |                                                                                                                                                                     | 103    | 190   |       |  |

|                                   |                                  |                    | V <sub>IN</sub> = 5.3 V, I <sub>OUT</sub> = 2 A, V <sub>FB</sub> = 0.8 V – 3%                                                                                                                                            |                                                                                                                                                                     | 135    | 220   |       |  |

|                                   |                                  | RGR package        | V <sub>IN</sub> = 5.5 V, I <sub>OUT</sub> = 2 A, V <sub>FB</sub> = 0.8 V – 3%                                                                                                                                            |                                                                                                                                                                     | 157    | 300   | mV    |  |

|                                   |                                  |                    | $V_{IN} = 1.1 \text{ V}, 3.0 \text{ V} \le V_{BIAS} \le 6.5 \text{ V},$<br>$I_{OUT} = 2 \text{ A}, V_{FB} = 0.8 \text{ V} - 3\%$                                                                                         |                                                                                                                                                                     | 73     | 120   |       |  |

| $V_{DO}$                          | Dropout voltage                  |                    | V <sub>IN</sub> = 1.4 V, I <sub>OUT</sub> = 2 A, V <sub>FB</sub> = 0.8 V – 3%                                                                                                                                            |                                                                                                                                                                     |        | 215   |       |  |

|                                   |                                  |                    | V <sub>IN</sub> = 5.3 V, I <sub>OUT</sub> = 2 A, V <sub>FB</sub> = 0.8 V – 3%                                                                                                                                            |                                                                                                                                                                     |        | 265   |       |  |

|                                   |                                  | RTK package        | V <sub>IN</sub> = 5.5 V, I <sub>OUT</sub> = 2 A, V <sub>FB</sub> = 0.8 V – 3%                                                                                                                                            |                                                                                                                                                                     |        | 340   | mV    |  |

|                                   |                                  |                    | $V_{IN} = 1.1 \text{ V}, 3.0 \text{ V} \le V_{BIAS} \le 6.5 \text{ V},$ $I_{OUT} = 2 \text{ A}, V_{FB} = 0.8 \text{ V} - 3\%$                                                                                            |                                                                                                                                                                     |        | 145   |       |  |

$V_{OUT(nom)}$  is the expected  $V_{OUT}$  value set by the external feedback resistors. This  $50-\Omega$  load is disconnected when the test conditions specify an  $I_{OUT}$  value.

## **Electrical Characteristics (continued)**

over operating junction temperature range (T $_J$  = -40°C to +150°C), V $_{IN}$  = 1.4 V or V $_{IN}$  = V $_{OUT(nom)}$  + 0.4 V (whichever is greater), V $_{BIAS}$  = open, V $_{OUT(nom)}$  = 0.8 V $^{(1)}$ , OUT connected to 50  $\Omega$  to GND $^{(2)}$ , V $_{EN}$  = 1.1 V, C $_{IN}$  = 10  $\mu$ F, C $_{OUT}$  = 22  $\mu$ F, C $_{NR/SS}$  without C $_{FF}$ , and PG pin pulled up to V $_{IN}$  with 100 k $\Omega$  (unless otherwise noted); typical values are at T $_{J}$  = 25°C

|                      | PARAMETER                                       | TEST CONDIT                                                                                                                                                                                                                                                                                                                                                     | ,, ,,                                                                  | MIN                  | TYP                  | MAX                  | UNIT          |

|----------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------|----------------------|----------------------|---------------|

| I <sub>LIM</sub>     | Output current limit                            | V <sub>OUT</sub> forced at 0.9 × V <sub>OUT(non</sub><br>V <sub>IN</sub> = V <sub>OUT(nom)</sub> + 0.4 V                                                                                                                                                                                                                                                        | n),                                                                    | 2.7                  | 3.3                  | 4                    | А             |

| I <sub>SC</sub>      | Short-circuit current limit                     | $R_{LOAD} = 20 \text{ m}\Omega$                                                                                                                                                                                                                                                                                                                                 |                                                                        |                      | 1.0                  |                      | А             |

|                      |                                                 | V <sub>IN</sub> = 6.5 V, I <sub>OUT</sub> = 5 mA                                                                                                                                                                                                                                                                                                                |                                                                        |                      | 3                    | 4                    |               |

| $I_{GND}$            | GND pin current                                 | V <sub>IN</sub> = 1.4 V, I <sub>OUT</sub> = 2 A                                                                                                                                                                                                                                                                                                                 |                                                                        |                      | 3.7                  | 5                    | mA            |

|                      |                                                 | Shutdown, PG = open, V <sub>IN</sub> =                                                                                                                                                                                                                                                                                                                          | 6.5 V, V <sub>EN</sub> = 0.5 V                                         |                      |                      | 25                   | μA            |

| I <sub>EN</sub>      | EN pin current                                  | V <sub>IN</sub> = 6.5 V, V <sub>EN</sub> = 0 V and 6                                                                                                                                                                                                                                                                                                            | .5 V                                                                   | -0.5                 |                      | 0.5                  | μA            |

| I <sub>BIAS</sub>    | BIAS pin current                                | V <sub>IN</sub> = 1.1 V, V <sub>BIAS</sub> = 6.5 V,<br>V <sub>OUT(nom)</sub> = 0.8 V, I <sub>OUT</sub> = 2 A                                                                                                                                                                                                                                                    |                                                                        |                      | 2.3                  | 3.5                  | mA            |

| V <sub>IL(EN)</sub>  | EN pin low-level input voltage (disable device) |                                                                                                                                                                                                                                                                                                                                                                 |                                                                        |                      |                      | 0.5                  | V             |

| V <sub>IH(EN)</sub>  | EN pin high-level input voltage (enable device) |                                                                                                                                                                                                                                                                                                                                                                 |                                                                        | 1.1                  |                      |                      | V             |

| V <sub>IT-(PG)</sub> | PG pin threshold                                | For falling V <sub>OUT</sub>                                                                                                                                                                                                                                                                                                                                    |                                                                        | 0.82V <sub>OUT</sub> | 0.88V <sub>OUT</sub> | 0.93V <sub>OUT</sub> | V             |

| V <sub>HYS(PG)</sub> | PG pin hysteresis                               |                                                                                                                                                                                                                                                                                                                                                                 |                                                                        |                      | 0.02V <sub>OUT</sub> |                      | V             |

| V <sub>IT+(PG)</sub> | PG pin threshold                                | For rising V <sub>OUT</sub>                                                                                                                                                                                                                                                                                                                                     |                                                                        | 0.84V <sub>OUT</sub> | 0.90V <sub>OUT</sub> | 0.95V <sub>OUT</sub> | V             |

| $V_{OL(PG)}$         | PG pin low-level output voltage                 | V <sub>OUT</sub> < V <sub>IT(PG)</sub> , I <sub>PG</sub> = -1 mA<br>(current into device)                                                                                                                                                                                                                                                                       |                                                                        |                      |                      | 0.4                  | V             |

| I <sub>lkg(PG)</sub> | PG pin leakage current                          | $V_{OUT} > V_{IT(PG)}$ , $V_{PG} = 6.5 \text{ V}$                                                                                                                                                                                                                                                                                                               |                                                                        |                      |                      | 1                    | μA            |

| I <sub>NR/SS</sub>   | NR/SS pin charging current                      | $V_{NR/SS} = GND, V_{IN} = 6.5 V$                                                                                                                                                                                                                                                                                                                               |                                                                        | 4.0                  | 6.5                  | 10                   | μA            |

| I <sub>FB</sub>      | FB pin leakage current                          | V <sub>IN</sub> = 6.5 V                                                                                                                                                                                                                                                                                                                                         |                                                                        | -100                 |                      | 100                  | nA            |

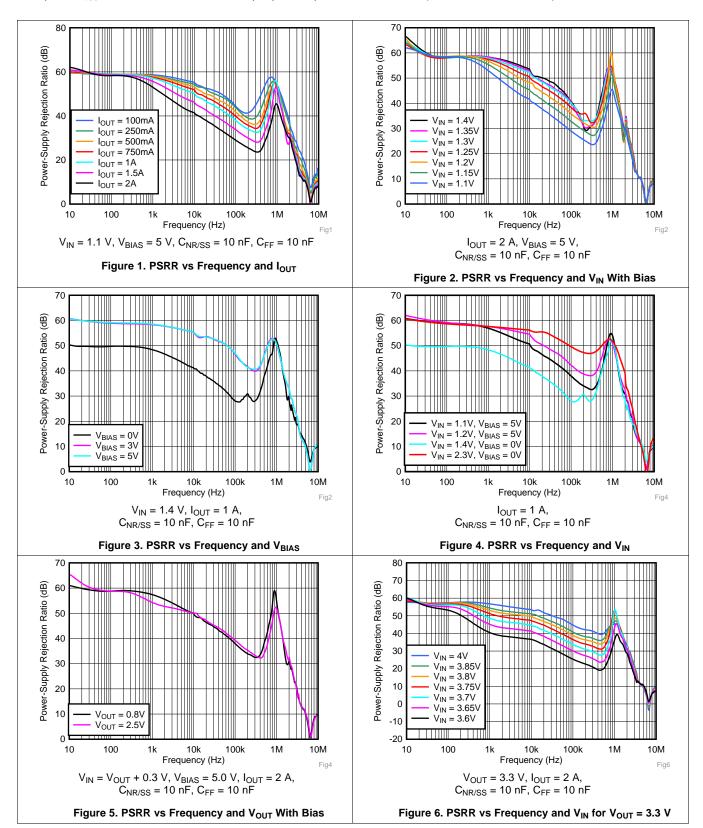

|                      |                                                 |                                                                                                                                                                                                                                                                                                                                                                 | f = 10 kHz,<br>V <sub>OUT</sub> = 0.8 V,<br>V <sub>BIAS</sub> = 5.0 V  |                      | 42                   |                      |               |

| PSRR                 | Power-supply ripple rejection                   | $V_{IN} - V_{O~UT} = 0.4~V,$<br>$I_{OUT} = 2~A,~C_{NR/SS} = 100~nF,$<br>$C_{FF} = 10~nF,$                                                                                                                                                                                                                                                                       | f = 500 kHz,<br>V <sub>OUT</sub> = 0.8 V,<br>V <sub>BIAS</sub> = 5.0 V |                      | 39                   |                      | dB            |

|                      |                                                 | C <sub>OUT</sub> = 22 μF                                                                                                                                                                                                                                                                                                                                        | f = 10 kHz,<br>V <sub>OUT</sub> = 5.0 V                                |                      | 40                   |                      |               |

|                      |                                                 |                                                                                                                                                                                                                                                                                                                                                                 | f = 500 kHz,<br>V <sub>OUT</sub> = 5.0 V                               |                      | 25                   |                      |               |

| V <sub>n</sub>       | Output noise voltage                            | $\begin{split} BW &= 10 \text{ Hz to } 100 \text{ kHz}, \text{ V}_{\text{IN}} = 1.1 \text{ V}, \\ \text{V}_{\text{OUT}} &= 0.8 \text{ V}, \text{V}_{\text{BIAS}} = 5.0 \text{ V}, \text{I}_{\text{OUT}} = 2 \text{ A}, \\ \text{C}_{\text{NR/SS}} &= 100 \text{ nF}, \text{C}_{\text{FF}} = 10 \text{ nF}, \text{C}_{\text{OUT}} = 22  \mu\text{F} \end{split}$ |                                                                        |                      | 4.4                  | _                    | $\mu V_{RMS}$ |

| vn                   | Surput Holse Vollage                            | $\label{eq:bw} \begin{split} BW &= 10 \text{ Hz to } 100 \text{ kHz}, \\ V_{OUT} &= 5.0 \text{ V}, I_{OUT} = 2 \text{ A}, C_{NF} \\ C_{FF} &= 10 \text{ nF}, C_{OUT} = 22  \mu\text{F} \end{split}$                                                                                                                                                             | <sub>R/SS</sub> = 100 nF,                                              |                      | 7.7                  |                      | PVRMS         |

| _                    | The group object decine to manage the con-      | Shutdown, temperature incre                                                                                                                                                                                                                                                                                                                                     | easing                                                                 |                      | 160                  |                      | ۰.            |

| T <sub>SD</sub>      | Thermal shutdown temperature                    | Reset, temperature decreasi                                                                                                                                                                                                                                                                                                                                     | ng                                                                     |                      | 140                  |                      | °C            |

Product Folder Links: TPS7A52-Q1

## 6.6 Typical Characteristics

at  $T_A = 25^{\circ}C$ ,  $V_{IN} = 1.4$  V or  $V_{IN} = V_{OUT(NOM)} + 0.4$  V (whichever is greater),  $V_{BIAS} = open$ ,  $V_{OUT(NOM)} = 0.8$  V,  $V_{EN} = 1.1$  V,  $C_{OUT} = 22 \mu F$ ,  $C_{NR/SS} = 0$  nF,  $C_{FF} = 0$  nF, and PG pin pulled up to  $V_{IN}$  with 100 k $\Omega$  (unless otherwise noted)

# **NSTRUMENTS**

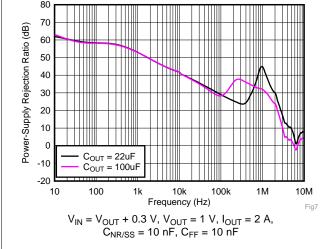

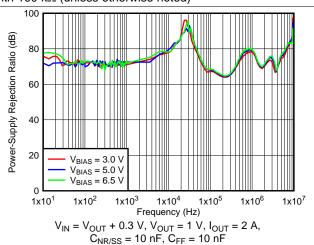

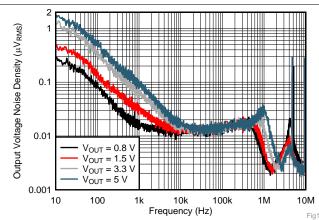

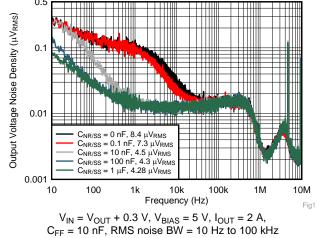

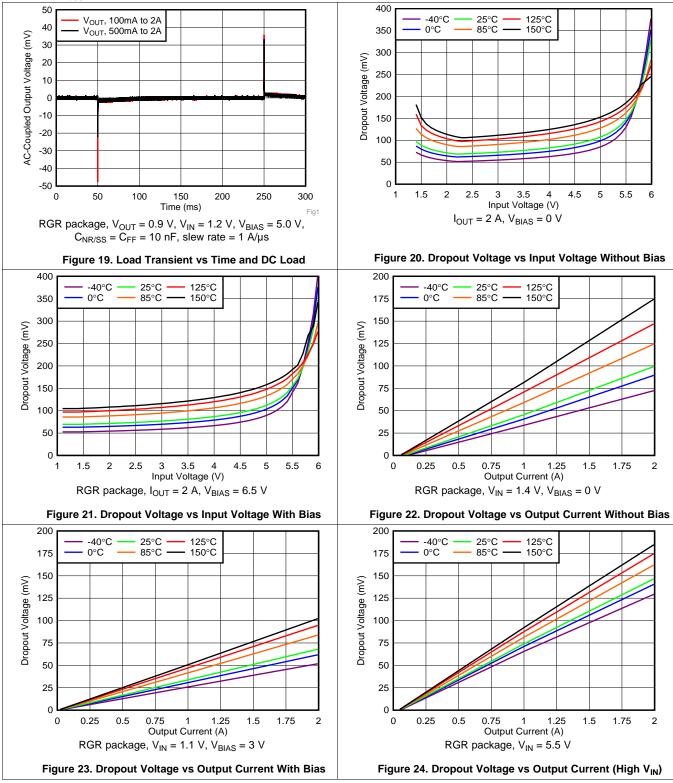

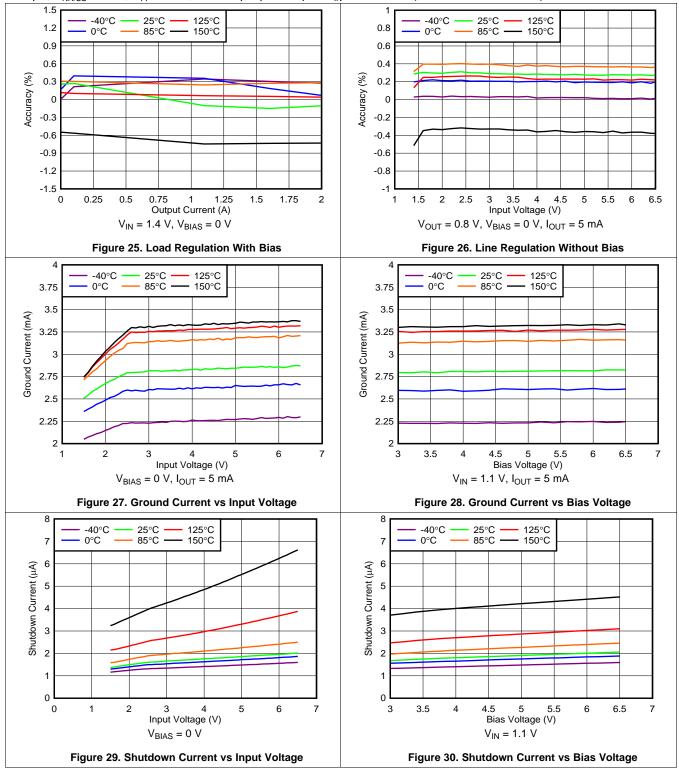

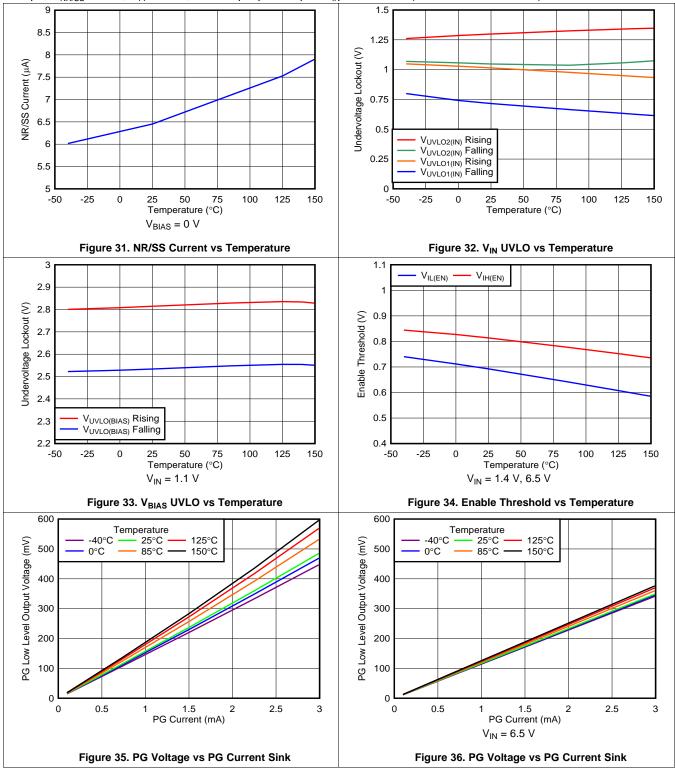

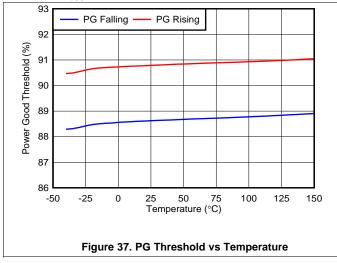

## Typical Characteristics (continued)

at  $T_A = 25^{\circ}C$ ,  $V_{IN} = 1.4$  V or  $V_{IN} = V_{OUT(NOM)} + 0.4$  V (whichever is greater),  $V_{BIAS} =$  open,  $V_{OUT(NOM)} = 0.8$  V,  $V_{EN} = 1.1$  V,  $C_{OUT} = 22$   $\mu$ F,  $C_{NR/SS} = 0$  nF,  $C_{FF} = 0$  nF, and PG pin pulled up to  $V_{IN}$  with 100  $k\Omega$  (unless otherwise noted)

Figure 7. PSRR vs Frequency and Cout

Figure 8. V<sub>BIAS</sub> PSRR vs Frequency and V<sub>BIAS</sub>

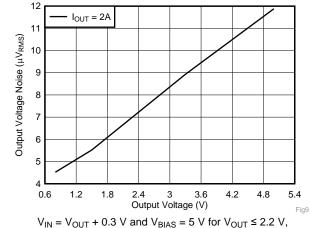

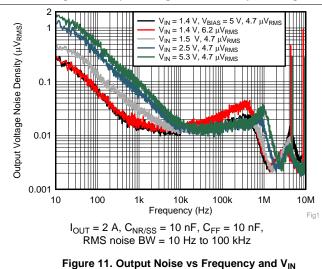

$C_{NR/SS} = 10 \text{ nF}, C_{FF} = 10 \text{ nF},$ RMS noise BW = 10 Hz to 100 kHz

$V_{IN} = V_{OUT} + 0.3 \text{ V}$  and  $V_{BIAS} = 5 \text{ V}$  for  $V_{OUT} \le 2.2 \text{ V}$ ,  $I_{OUT} = 2 \text{ A}$ ,  $C_{NR/SS} = 10 \text{ nF}, C_{FF} = 10 \text{ nF},$ RMS noise BW = 10 Hz to 100 kHz

Figure 12. Output Noise vs Frequency and CNR/SS

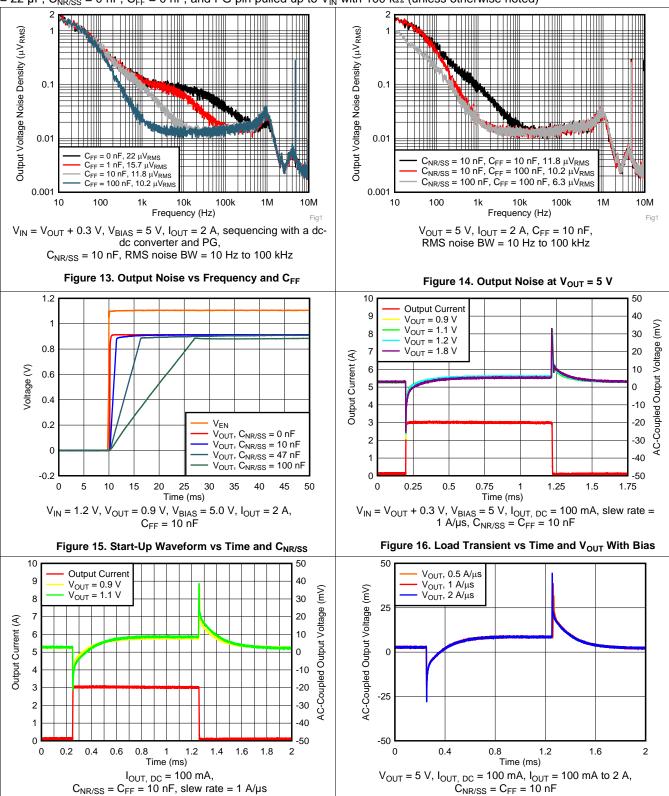

at  $T_A = 25^{\circ}C$ ,  $V_{IN} = 1.4$  V or  $V_{IN} = V_{OUT(NOM)} + 0.4$  V (whichever is greater),  $V_{BIAS} =$  open,  $V_{OUT(NOM)} = 0.8$  V,  $V_{EN} = 1.1$  V,  $C_{OUT} = 22$   $\mu$ F,  $C_{NR/SS} = 0$  nF,  $C_{FF} = 0$  nF, and PG pin pulled up to  $V_{IN}$  with 100  $k\Omega$  (unless otherwise noted)

Copyright © 2017–2018, Texas Instruments Incorporated

Figure 17. Load Transient vs Time and V<sub>OUT</sub> Without Bias

Submit Documentation Feedback

Figure 18. Load Transient vs Time and Slew Rate

at  $T_A = 25^{\circ}C$ ,  $V_{IN} = 1.4$  V or  $V_{IN} = V_{OUT(NOM)} + 0.4$  V (whichever is greater),  $V_{BIAS} =$  open,  $V_{OUT(NOM)} = 0.8$  V,  $V_{EN} = 1.1$  V,  $C_{OUT} = 22$   $\mu$ F,  $C_{NR/SS} = 0$  nF,  $C_{FF} = 0$  nF, and PG pin pulled up to  $V_{IN}$  with 100  $k\Omega$  (unless otherwise noted)

Submit Documentation Feedback

Copyright © 2017–2018, Texas Instruments Incorporated

at  $T_A = 25^{\circ}C$ ,  $V_{IN} = 1.4$  V or  $V_{IN} = V_{OUT(NOM)} + 0.4$  V (whichever is greater),  $V_{BIAS} =$  open,  $V_{OUT(NOM)} = 0.8$  V,  $V_{EN} = 1.1$  V,  $C_{OUT} = 22$   $\mu$ F,  $C_{NR/SS} = 0$  nF,  $C_{FF} = 0$  nF, and PG pin pulled up to  $V_{IN}$  with 100  $k\Omega$  (unless otherwise noted)

Copyright © 2017–2018, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

at  $T_A = 25^{\circ}C$ ,  $V_{IN} = 1.4$  V or  $V_{IN} = V_{OUT(NOM)} + 0.4$  V (whichever is greater),  $V_{BIAS} =$  open,  $V_{OUT(NOM)} = 0.8$  V,  $V_{EN} = 1.1$  V,  $C_{OUT} = 22$   $\mu$ F,  $C_{NR/SS} = 0$  nF,  $C_{FF} = 0$  nF, and PG pin pulled up to  $V_{IN}$  with 100  $k\Omega$  (unless otherwise noted)

Submit Documentation Feedback

Copyright © 2017–2018, Texas Instruments Incorporated

at  $T_A$  = 25°C,  $V_{IN}$  = 1.4 V or  $V_{IN}$  =  $V_{OUT(NOM)}$  + 0.4 V (whichever is greater),  $V_{BIAS}$  = open,  $V_{OUT(NOM)}$  = 0.8 V,  $V_{EN}$  = 1.1 V,  $C_{OUT}$  = 22  $\mu$ F,  $C_{NR/SS}$  = 0 nF,  $C_{FF}$  = 0 nF, and PG pin pulled up to  $V_{IN}$  with 100  $k\Omega$  (unless otherwise noted)

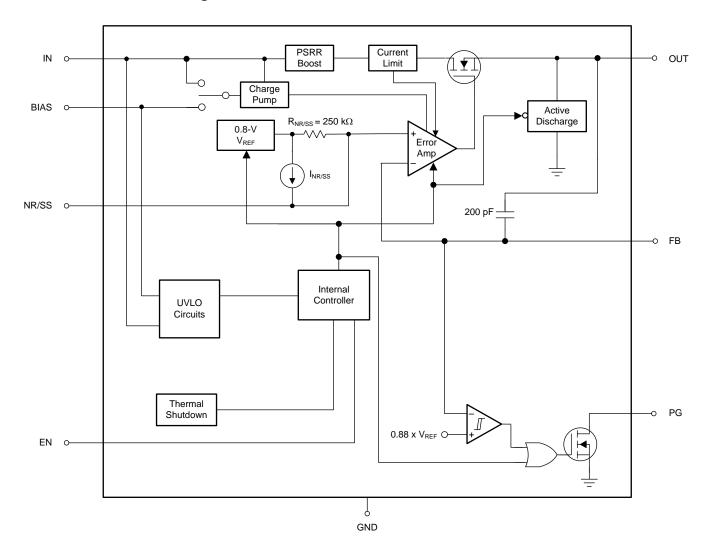

## 7 Detailed Description

#### 7.1 Overview

The TPS7A52-Q1 is a high-current (2 A), low-noise (4.4  $\mu V_{RMS}$ ), high accuracy (1%) low-dropout linear voltage regulator with an input range of 1.1 V to 6.5 V, an output voltage range of 0.8 V to 5.2 V. The TPS7A52-Q1 has an integrated charge pump for ease of use, and an external bias rail to allow for the lowest dropout across the entire output voltage range. Table 1 categorizes the functions shown in the *Functional Block Diagram* section. These features make the TPS7A52-Q1 a robust solution to solve many challenging problems by generating a clean, accurate power supply in a variety of applications.

**Table 1. Device Features**

| VOLTAGE REGULATION          | SYSTEM START-UP                                    | INTERNAL PROTECTION    |

|-----------------------------|----------------------------------------------------|------------------------|

| High accuracy               | Programmable soft start                            | Foldback current limit |

| Low-noise, high-PSRR output | No sequencing requirement between BIAS, IN, and EN |                        |

| Foot transient reasons      | Power-good output                                  | Thermal shutdown       |

| Fast transient response     | Start-up with negative bias on OUT                 |                        |

## 7.2 Functional Block Diagram

#### 7.3 Feature Description

## 7.3.1 Voltage Regulation Features

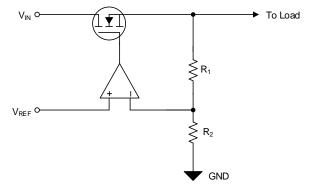

## 7.3.1.1 DC Regulation

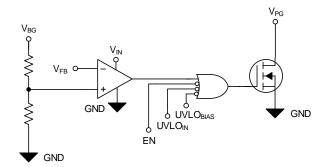

As shown in Figure 39, an LDO functions as a class-B amplifier in which the input signal is the internal reference voltage ( $V_{REF}$ ).  $V_{REF}$  is designed to have a very low bandwidth at the input to the error amplifier through the use of a low-pass filter ( $V_{NR/SS}$ ).

As such, the reference can be considered as a pure dc input signal. The low output impedance of an LDO comes from the combination of the output capacitor and pass element. The pass element also presents a high input impedance to the source voltage when operating as a current source. A positive LDO can only source current because of the class-B architecture.

This device achieves a maximum of 1% output voltage accuracy primarily because of the high-precision band-gap voltage ( $V_{BG}$ ) that creates  $V_{REF}$ . The low dropout voltage ( $V_{DO}$ ) reduces the thermal power dissipation required by the device to regulate the output voltage at a given current level, thereby improving system efficiency. These features combine to make this device a good approximation of an ideal voltage source.

NOTE:  $V_{OUT} = V_{REF} \times (1 + R_1 / R_2)$ .

Figure 39. Simplified Regulation Circuit

#### 7.3.1.2 AC and Transient Response

The LDO responds quickly to a transient (large-signal response) on the input supply (line transient) or the output current (load transient) resulting from the LDO high-input impedance and low output-impedance across frequency. This same capability also means that the LDO has a high power-supply rejection ratio (PSRR) and, when coupled with a low internal noise-floor  $(V_n)$ , the LDO approximates an ideal power supply in ac (small-signal) and large-signal conditions.

The choice of external component values optimizes the small- and large-signal response. The NR/SS capacitor  $(C_{NR/SS})$  and feed-forward capacitor  $(C_{FF})$  easily reduce the device noise floor and improve PSRR.

Copyright © 2017–2018, Texas Instruments Incorporated

#### **Feature Description (continued)**

#### 7.3.2 System Start-Up Features

In many different applications, the power-supply output must turn on within a specific window of time to either provide proper operation of the load or to minimize the loading on the input supply or other sequencing requirements. The LDO start-up is well-controlled and user-adjustable, solving the demanding requirements faced by many power-supply design engineers in a simple fashion.

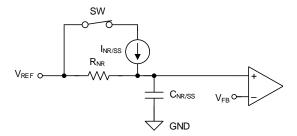

#### 7.3.2.1 Programmable Soft Start (NR/SS Pin)

Soft start directly controls the output start-up time and indirectly controls the output current during start-up (inrush current).

The external capacitor at the NR/SS pin ( $C_{NR/SS}$ ), as shown in Figure 40, sets the output start-up time by setting the rise time of the internal reference ( $V_{NR/SS}$ ).

Figure 40. Simplified Soft-Start Circuit

#### 7.3.2.2 Internal Sequencing

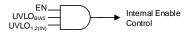

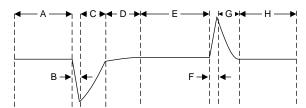

Controlling when a single power supply turns on can be difficult in a power distribution network (PDN) because of the high power levels inherent in a PDN, and the variations between all of the supplies. Figure 41 and Table 2 show that the LDO turnon and turnoff time is set by the enable circuit (EN) and undervoltage lockout circuits (UVLO<sub>1,2(IN)</sub> and UVLO<sub>BIAS</sub>).

Figure 41. Simplified Turnon Control

**Table 2. Internal Sequencing Functionality Table**

| INPUT VOLTAGE                                 | BIAS VOLTAGE                                                        | ENABLE<br>STATUS | LDO<br>STATUS | ACTIVE<br>DISCHARGE | POWER<br>GOOD                                 |

|-----------------------------------------------|---------------------------------------------------------------------|------------------|---------------|---------------------|-----------------------------------------------|

|                                               | V <sub>BIAS</sub> ≥ V <sub>UVLO(BIAS)</sub>                         | EN = 1           | On            | Off                 | $PG = 1 \text{ when } V_{OUT} \ge V_{IT(PG)}$ |

| $V_{IN} \ge V_{UVLO_{1,2}(IN)}$               | 22                                                                  | EN = 0           | Off           | On                  |                                               |

|                                               | V <sub>BIAS</sub> < V <sub>UVLO(BIAS)</sub> +V <sub>HYS(BIAS)</sub> |                  | Off           |                     | PG = 0                                        |

| $V_{IN} < V_{UVLO\_1,2(IN)} - V_{HYS1,2(IN)}$ | BIAS = don't care                                                   | EN = don't care  | Off           | On <sup>(1)</sup>   | PG = 0                                        |

| IN = don't care                               | $V_{BIAS} \ge V_{UVLO(BIAS)}$                                       |                  | Off           |                     |                                               |

(1) The active discharge remains on as long as  $V_{IN}$  or  $V_{BIAS}$  provides enough headroom for the discharge circuit to function.

#### 7.3.2.2.1 Enable (EN)

The enable signal  $(V_{EN})$  is an active-high digital control that enables the LDO when the enable voltage is past the rising threshold  $(V_{EN} \ge V_{IH(EN)})$  and disables the LDO when the enable voltage is below the falling threshold  $(V_{EN} \le V_{IL(EN)})$ . The exact enable threshold is between  $V_{IH(EN)}$  and  $V_{IL(EN)}$  because EN is a digital control. Connect EN to  $V_{IN}$  if enable functionality is not desired.

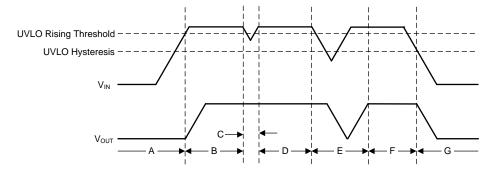

#### 7.3.2.2.2 Undervoltage Lockout (UVLO) Control

The UVLO circuits respond quickly to glitches on IN or BIAS and attempts to disable the output of the device if either of these rails collapse.

#### 7.3.2.2.3 Active Discharge

When either EN or UVLO is low, the device connects a resistor of several hundred ohms from  $V_{OUT}$  to GND, discharging the output capacitance.

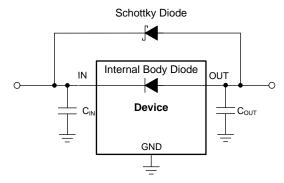

Do not rely on the active discharge circuit for discharging large output capacitors when the input voltage drops below the targeted output voltage. Current flows from the output to the input (reverse current) when  $V_{OUT} > V_{IN}$ , which can cause damage to the device (when  $V_{OUT} > V_{IN} + 0.3 \text{ V}$ ).

## 7.3.2.3 Power-Good Output (PG)

The PG signal provides an easy solution to meet demanding sequencing requirements because PG signals when the output nears its nominal value. PG can be used to signal other devices in a system when the output voltage is near, at, or above the set output voltage (V<sub>OUT(nom)</sub>). Figure 42 shows a simplified schematic.

The PG signal is an open-drain digital output that requires a pullup resistor to a voltage source and is active high. The PG circuit sets the PG pin into a high-impedance state to indicate that the power is good.

Using a large feed-forward capacitor (C<sub>FF</sub>) delays the output voltage and, because the PG circuit monitors the FB pin, the PG signal can indicate a false positive.

Figure 42. Simplified PG Circuit

Copyright © 2017–2018, Texas Instruments Incorporated

#### 7.3.3 Internal Protection Features

In many applications, fault events can occur that damage devices in the system. Short circuits and excessive heat are the most common fault events for power supplies. The TPS7A52-Q1 implements circuitry to protect the device and its load during these events. Continuously operating in these fault conditions or above a junction temperature of 140°C is not recommended because the long-term reliability of the device is reduced.

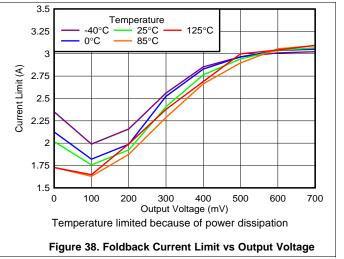

#### 7.3.3.1 Foldback Current Limit ( $I_{Cl}$ )

The internal current limit circuit is used to protect the LDO against high load-current faults or shorting events. During a current-limit event, the LDO sources constant current; therefore, the output voltage falls with decreased load impedance. Thermal shutdown can activate during a current limit event because of the high power dissipation typically found in these conditions. For proper operation of the current limit, minimize the inductances to the input and load. Continuous operation in current limit is not recommended.

#### 7.3.3.2 Thermal Protection $(T_{sd})$

The thermal shutdown circuit protects the LDO against excessive heat in the system, either resulting from current limit or high ambient temperature.

The output of the LDO turns off when the LDO temperature (junction temperature,  $T_J$ ) exceeds the rising thermal shutdown temperature. The output turns on again after  $T_J$  decreases below the falling thermal shutdown temperature.

A high power dissipation across the device, combined with a high ambient temperature ( $T_A$ ), can cause  $T_J$  to be greater than or equal to  $T_{sd}$ , triggering the thermal shutdown and causing the output to fall to 0 V. The LDO can cycle on and off when thermal shutdown is reached under these conditions.

#### 7.4 Device Functional Modes

Table 3 provides a quick comparison between the regulation and disabled operation.

**Table 3. Device Functional Modes Comparison**

| OPERATING               | PARAMETER                        |                                             |                       |                                    |                          |  |  |  |  |  |  |

|-------------------------|----------------------------------|---------------------------------------------|-----------------------|------------------------------------|--------------------------|--|--|--|--|--|--|

| MODE                    | V <sub>IN</sub>                  | V <sub>IN</sub> V <sub>BIAS</sub> EN        |                       | I <sub>OUT</sub>                   | TJ                       |  |  |  |  |  |  |

| Regulation (1)          | $V_{IN} > V_{OUT(nom)} + V_{DO}$ | $V_{BIAS} \ge V_{UVLO(BIAS)}^{(2)}$         | $V_{EN} > V_{IH(EN)}$ | I <sub>OUT</sub> < I <sub>CL</sub> | $T_J \le T_{J(maximum)}$ |  |  |  |  |  |  |

| Disabled <sup>(3)</sup> | $V_{IN} < V_{UVLO_{1,2(IN)}}$    | V <sub>BIAS</sub> < V <sub>UVLO(BIAS)</sub> | $V_{EN} < V_{IL(EN)}$ | _                                  | $T_J > T_{sd}$           |  |  |  |  |  |  |

- (1) All table conditions must be met.

- (2) V<sub>BIAS</sub> is only required for V<sub>IN</sub> < 1.4 V.

- (3) The device is disabled when any condition is met.

## 7.4.1 Regulation

The device regulates the output to the nominal output voltage when all the conditions in Table 3 are met.

#### 7.4.2 Disabled

When disabled, the pass device is turned off, the internal circuits are shut down, and the output voltage is actively discharged to ground by an internal resistor from the output to ground. See the *Active Discharge* section for additional information.

#### 7.4.3 Current Limit Operation

During a current-limit event, the LDO regulates the output current instead of the output voltage; therefore, the output voltage falls with decreased load impedance.

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

Successfully implementing an LDO in an application depends on the application requirements. This section discusses key device features and how to best implement them to achieve a reliable design.

## 8.1.1 Recommended Capacitor Types

The TPS7A52-Q1 is designed to be stable using low equivalent series resistance (ESR) ceramic capacitors at the input, output, and noise-reduction pin (NR, pin 13). Multilayer ceramic capacitors have become the industry standard for these types of applications and are recommended, but must be used with good judgment. Ceramic capacitors that employ X7R-, X5R-, and COG-rated dielectric materials provide relatively good capacitive stability across temperature. The use of Y5V-rated capacitors is discouraged because of large variations in capacitance.

Regardless of the ceramic capacitor type selected, ceramic capacitance varies with operating voltage and temperature. Make sure to derate ceramic capacitors by at least 50%. The input and output capacitors recommended herein account for a capacitance derating of approximately 50%, but at high  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  conditions ( $V_{\text{IN}} = 5.5 \text{ V}$  to  $V_{\text{OUT}} = 5.0 \text{ V}$ ), the derating can be greater than 50%, and must be taken into consideration.

#### 8.1.1.1 Input and Output Capacitor Requirements ( $C_{IN}$ and $C_{OUT}$ )

The TPS7A52-Q1 is designed and characterized for operation with ceramic capacitors of 22  $\mu$ F or greater (10  $\mu$ F or greater of capacitance) at the output and 10  $\mu$ F or greater (5  $\mu$ F or greater of capacitance) at the input. Use at least a 22- $\mu$ F capacitor at the input to minimize input impedance. Place the input and output capacitors as near as practical to the respective input and output pins in order to minimize trace parasitics. If the trace inductance from the input supply to the TPS7A52-Q1 is high, a fast current transient can cause  $V_{IN}$  to ring above the absolute maximum voltage rating and damage the device. This situation can be mitigated by additional input capacitors to dampen and keep the ringing below the device absolute maximum ratings.

#### Application Information (continued)

#### 8.1.1.2 Noise-Reduction and Soft-Start Capacitor ( $C_{NR/SS}$ )

The TPS7A52-Q1 features a programmable, monotonic, voltage-controlled soft start that is set with an external capacitor ( $C_{NR/SS}$ ). Use an external  $C_{NR/SS}$  to minimize inrush current into the output capacitors. This soft-start feature eliminates power-up initialization problems when powering field-programmable gate arrays (FPGAs), digital signal processors (DSPs), or other processors. The controlled voltage ramp of the output also reduces peak inrush current during start-up, minimizing start-up transients to the input power bus.

To achieve a monotonic start-up, the TPS7A52-Q1 error amplifier tracks the voltage ramp of the external soft-start capacitor until the voltage approaches the internal reference. The soft-start ramp time depends on the soft-start charging current ( $I_{NR/SS}$ ), the soft-start capacitance ( $C_{NR/SS}$ ), and the internal reference ( $V_{NR/SS}$ ). Equation 1 calculates soft-start ramp time:

$$t_{SS} = (V_{NR/SS} \times C_{NR/SS}) / I_{NR/SS}$$

(1)

I<sub>NR/SS</sub> is provided in the *Electrical Characteristics* table and has a typical value of 6.2 μA.

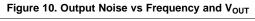

The noise-reduction capacitor, in conjunction with the noise-reduction resistor, forms a low-pass filter (LPF) that filters out the noise from the reference before being gained up with the error amplifier, thereby reducing the device noise floor. The LPF is a single-pole filter and Equation 2 calculates the cutoff frequency. The typical value of  $R_{NR}$  is 250 k $\Omega$ . Increasing the  $C_{NR/SS}$  capacitor has a greater affect because the output voltage increases when the noise from the reference is gained up even more at higher output voltages. For low-noise applications, a 10-nF to 1- $\mu$ F  $C_{NR/SS}$  is recommended.

$$f_{\text{cutoff}} = 1/\left(2 \times \pi \times R_{\text{NR}} \times C_{\text{NR/SS}}\right) \tag{2}$$

#### 8.1.1.3 Feed-Forward Capacitor ( $C_{FF}$ )

Although a feed-forward capacitor ( $C_{FF}$ ) from the FB pin to the OUT pin is not required to achieve stability, a 10-nF external feed-forward capacitor optimizes the transient, noise, and PSRR performance. A higher capacitance  $C_{FF}$  can be used; however, the start-up time is longer and the power-good signal can incorrectly indicate that the output voltage is settled. For a detailed description, see *Pros and Cons of Using a Feed-Forward Capacitor with a Low Dropout Regulator*.

#### 8.1.2 Soft-Start and Inrush Current

Soft start refers to the ramp-up characteristic of the output voltage during LDO turnon after EN and UVLO achieve threshold voltage. The noise-reduction capacitor serves a dual purpose of both governing output noise reduction and programming the soft-start ramp during turnon.

Inrush current is defined as the current into the LDO at the IN pin during start-up. Inrush current then consists primarily of the sum of load current and the current used to charge the output capacitor. This current is difficult to measure because the input capacitor must be removed, which is not recommended. However, Equation 3 can be used to estimate this soft-start current:

$$I_{OUT(t)} = \left[\frac{C_{OUT} \times dV_{OUT}(t)}{dt}\right] + \left[\frac{V_{OUT}(t)}{R_{LOAD}}\right]$$

#### where:

- V<sub>OUT</sub>(t) is the instantaneous output voltage of the turnon ramp

- $dV_{OUT}(t)$  / dt is the slope of the  $V_{OUT}$  ramp

- R<sub>LOAD</sub> is the resistive load impedance

(3)

## **Application Information (continued)**

#### 8.1.3 Optimizing Noise and PSRR

Improve the ultra-low noise floor and PSRR of the device by careful selection of:

- C<sub>NR/SS</sub> for the low-frequency range

- C<sub>FF</sub> in the midband frequency range

- C<sub>OUT</sub> for the high-frequency range

- V<sub>IN</sub> V<sub>OUT</sub> for all frequencies, and

- V<sub>BIAS</sub> at lower input voltages

A larger noise-reduction capacitor improves low-frequency PSRR by filtering any noise coupling from the input into the reference. To improve midband PSRR, use the feed-forward capacitor to place pole-zero pair near the edge of the loop bandwidth and push out the loop bandwidth. Use larger output capacitors to improve high-frequency PSRR.

A higher input voltage improves the PSRR by giving the device more headroom to respond to noise on the input. A bias rail also improves PSRR at lower input voltages because greater headroom is provided for the internal circuits.

The noise-reduction capacitor filters out low-frequency noise from the reference, and the feed-forward capacitor reduces output voltage noise by filtering out the midband frequency noise. However, a large feed-forward capacitor can create new issues that are discussed in *Pros and Cons of Using a Feed-Forward Capacitor with a Low Dropout Regulator*.

Use a large output capacitor to reduce high-frequency output voltage noise. Additionally, a bias rail or higher input voltage improves the noise because greater headroom is provided for the internal circuits.

Table 4 lists the output voltage noise for the 10-Hz to 100-kHz band at a 5.0-V output for a variety of conditions with an input voltage of 5.5 V, an  $R_1$  of 12.1 k $\Omega$ , and a load current of 2 A. The 5.0-V output was used because this output is the worst-case condition for output voltage noise.

**OUTPUT VOLTAGE NOISE** C<sub>NR/SS</sub> (nF) C<sub>FF</sub> (nF) C<sub>OUT</sub> (µF)  $(\mu V_{RMS})$ 11.7 10 10 22 7.7 100 10 22 6 100 100 22 7.4 10 100 1000 5.8 100 100 1000

Table 4. Output Noise Voltage at a 5.0-V Output

## 8.1.4 Charge Pump Noise

The device internal charge pump generates a minimal amount of noise. Use a bias rail to minimize the internal charge pump noise when the internal voltage is clamped, thereby reducing the overall output noise floor.

The high-frequency components of the output voltage noise density curves are filtered out in most applications by using 10-nF to 100-nF bypass capacitors close to the load. Using a ferrite bead between the LDO output and the load input capacitors forms a pi-filter, further reducing the high-frequency noise contribution.

#### 8.1.5 Current Sharing

Current sharing is possible through the use of external operational amplifiers. For more details, see the TI Design *Current-Sharing Dual LDOs* and the verified reference design *6 A Current-Sharing Dual LDO*.

#### 8.1.6 Adjustable Operation

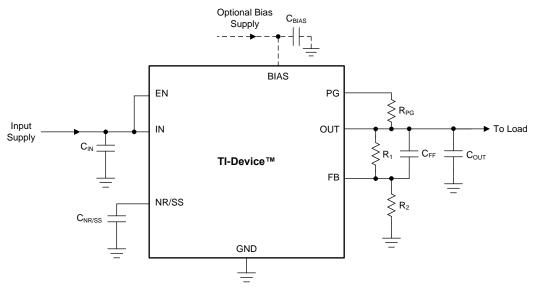

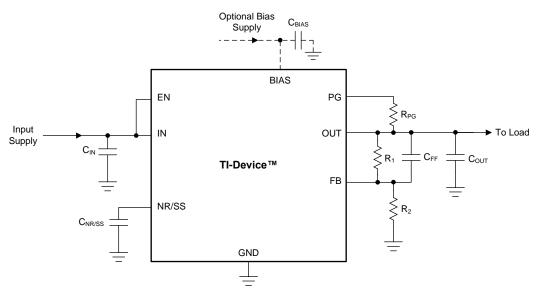

As shown in Figure 43, the output voltage of the TPS7A52-Q1 is set using external resistors.

Figure 43. Adjustable Operation

Use Equation 4 to calculate  $R_1$  and  $R_2$  for any output voltage range. This resistive network must provide a current equal to or greater than 5  $\mu$ A for dc accuracy. To optimize the noise and PSRR, use an  $R_1$  of 12.1  $k\Omega$ .

$$V_{OUT} = V_{NR/SS} \times (1 + R_1 / R_2)$$

(4)

Table 5 shows the resistor combinations required to achieve several common rails using standard 1%-tolerance resistors.

Table 5. Recommended Feedback-Resistor Values

| TARGETED OUTPUT | FEEDBACK RESI       | CALCULATED OUTPUT         |                |

|-----------------|---------------------|---------------------------|----------------|