# CY8CMBR3002, CY8CMBR3102 CY8CM-BR3106S, CY8CMBR3108 CY8CMBR3110, CY8CMBR3116 Datasheet

CapSense<sup>®</sup> Express™ Controllers with SmartSense™ Auto-tuning - 16 Buttons, 2 Sliders, Proximity Sensors

## **General Description**

The CY8CMBR3xxx CapSense<sup>®</sup> Express™ controllers enable advanced, yet easy-to-implement, capacitive touch sensing user interface solutions. This register-configurable family, which supports up to 16 capacitive sensing inputs, eliminates time-consuming firmware development. These controllers are ideal for implementing capacitive buttons, sliders, and proximity sensing solutions with minimal development-cycle times.

The CY8CMBR3xxx family features an advanced analog sensing channel and the Capacitive Sigma Delta PLUS (CSD PLUS) sensing algorithm, which delivers a signal-to-noise ratio (SNR) of greater than 100:1 to ensure touch accuracy even in extremely noisy environments. These controllers are enabled with Cypress's SmartSense™ Auto-tuning algorithm, which compensates for manufacturing variations and dynamically monitors and maintains optimal sensor performance in all environmental conditions. In addition, SmartSense Auto-tuning enables a faster time-to-market by eliminating the time-consuming manual tuning efforts during development and production ramp-up.

Advanced features, such as LED brightness control, proximity sensing, and system diagnostics, save development time. These controllers enable robust liquid-tolerant designs by eliminating false touches due to mist, water droplets, or streaming water. The CY8CMBR3xxx controllers are offered in a variety of small form factor industry-standard packages.

The ecosystem for the CY8CMBR3xxx family includes development tools—software and hardware—to enable rapid user interface designs. For example, the EZ-Click Customizer tool is a simple graphical user interface software for configuring the device features through the I<sup>2</sup>C interface. This tool also supports CapSense data viewing to monitor system performance and support validation and debugging. Another tool, the Design Toolbox, simplifies circuit board layout by providing design guidelines and layout recommendations to optimize sensor size, trace lengths, and parasitic capacitance. To quickly evaluate the CY8CMBR3xxx family features, use the CY3280-MBR3 Evaluation Kit.

#### **Features**

- Register-configurable CapSense Express controller

- □ No firmware development required

- □ Patented CSD sensing algorithm

- ☐ High sensitivity (0.1 pF)

- Overlay thickness of up to 15 mm for glass and 5 mm for plastic

- · Proximity solutions

- · Sensitivity up to 2 fF per count

- ☐ Best-in-class >100:1 SNR performance

- Superior noise-immunity performance against conducted and radiated noise

- · Ultra-low radiated emissions

- □ SmartSense Auto-tuning

- Sets and maintains optimal sensor performance during run time

- Eliminates manual tuning during development and production

- Low-power CapSense

- □ Average current consumption of 22 µA per sensor at 120-ms refresh interval

- □ Wide parasitic capacitance (C<sub>P</sub>) range: 5–45 pF

- Advanced user interface features

- □ Liquid tolerance

- □ User-configurable LED brightness for visual touch feedback

- · Up to eight high-sink current GPOs to drive LEDs

- Buzzer signal output for audible touch feedback

- Flanking Sensor Suppression (FSS) to eliminate false touches in closely spaced buttons

- □ Analog voltage output

- □ Attention line interrupt to the host to indicate any change in sensor status

- System diagnostics to detect

- □ Improper value of the modulating capacitor (CMOD)

- □ Out of range sensor parasitic capacitance (C<sub>P</sub>)

- □ Sensor shorts

- EZ-Click™ Customizer tool

- □ Simple GUI for device configuration

- □ Data viewing and monitoring for CapSense buttons, sliders, and proximity sensors

- □ System diagnostics for rapid debug

- I<sup>2</sup>C slave

- □ Supports up to 400 kHz

- □ Wake-on-hardware address match

- □ No bus-stalling or clock-stretching during transactions

- Low-power 1.71-V to 5.5-V operation

- $\ \square$  Deep Sleep mode with wake-up on interrupt and I $^2$ C address detect

- Industrial temperature range: -40 °C to +85 °C

- Package options

- □ 8-pin SOIC (150 mil)

- □ 16-pin SOIC (150 mil)

- □ 16-pin QFN (3 × 3 × 0.6 mm)

- $\square$  24-pin QFN (4 × 4 × 0.6 mm)

#### More Information

Cypress provides a wealth of data at <a href="www.cypress.com">www.cypress.com</a> to help you to select the right CapSense device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA92181, Resources Available for CapSense® Controllers. Following is an abbreviated list for CapSense devices:

- Overview: CapSense Portfolio, CapSense Roadmap

- Product Selectors: Refer to the "CapSense Selector Guide" chapter in the Getting Started with CapSense design guide.

## CY8CMBR3xxx Ecosystem

Cypress provides a complete ecosystem to enable a quick development cycle with the CY8CMBR3xxx CapSense controller family. This ecosystem includes simple tools for device configuration, design validation, and diagnostics.

#### **Documentation**

#### Design Guides

Design guides are an excellent introduction to a variety of possible CapSense-based designs. They provide an introduction to the solution and complete system design guidelines. Refer to the following design guides for CY8CMBR3xxx:

- Getting Started with CapSense an ideal starting point for all CapSense users

- CY8CMBR3xxx CapSense Design Guide provides complete system design guidelines for CY8CMBR3xxx

You can download these design guides from our website: www.cypress.com/go/capsense.

#### Registers TRM

The CY8CMBR3xxx Registers TRM lists and details all the registers of the CY8CMBR3xxx family of controllers in order of their addresses. These registers may be accessed through an I<sup>2</sup>C interface with the host.

#### **Software Utility**

#### EZ-Click Customizer Tool

The EZ-Click Customizer Tool is a simple, GUI-based software utility that can be used to customize the CY8CMBR3xxx device configurations.

Use this GUI-based tool to do the following:

- Select the appropriate part number based on an end-application requirement using the Product Selector

- 2. Configure the device features

- 3. Observe CapSense data for button and proximity sensors

- Use the System Diagnostics and built-in test self-test (BIST) features for debug and production-line testing

art page CapSense sensor configuration Global configuration CapSense output System diagnostics LEDs Shield Part number Sliders: 0 🔻 Median filter Advanced low-pass filter: lumber of proximity sensors: - CapSense Express 0 -Buttons 500 -- CY8CMBR2110 10 LEDs: 0 Ė- CY8CMBR3xxx Sensitivity (fF) Finger Threshold Initial Response Time (ms) FSS - CY8CMBR3002 | 2 CS0/PS0 (1) - CY8CMBR3102 2 True True CY8CMBR3108 8 Dimming effects - CY8CMBR3110 10 True LED intensity control CS6 (18) art page | CapSense sensor configuration | Global configuration CapSense output | System diagnostics S9/GPO1 (15) lect view: Displayed Samples: 1000 BTN1 Button status: Off Start > ger threshold: 128 Cp (pF): 🚺 0 Errors 🚺 0 Warnings 🕕 0 Notes ile Configuration Help 🚰 🔒 📓 🗗 🗵 🖺 🏈 🤣 Start page | CapSense sensor configuration | Global configuration | CapSense output | System diagnostics Test configuration: Stop 🔳 Test mode: Calibrated Cp: 11 Calibrated SNR: 1 Calculate SNR for: Prototype • Tolerance: - 1 + 14 BTN2 Power on self test Tolerance: - 11 Cmod test: No faults detected Status SNR Ср System diagnostics result BTN1 Off N/A Pass BTN2 On 10 12 Pass BTN3 Off N/A 10 Pass Pass N/A 14 500 Time

Figure 1. Configuring CY8CMBR3xxx using Ez-Click

## CY8CMBR3002, CY8CMBR3102 CY8CM-BR3106S, CY8CMBR3108 CY8CMBR3110, CY8CMBR3116 Datasheet

#### **Tools**

## **Design Toolbox**

The Design Toolbox is an interactive spreadsheet tool that provides application-specific design guidelines for capacitive buttons. It is used to configure and validate the CapSense system.

The Design Toolbox:

- Provides general layout guidelines for a CapSense PCB

- Estimates button dimensions based on end-application requirements

- Calculates power consumption based on button dimensions

- Validates layout design

#### **Evaluation Kits**

The CY3280-MBR3 Evaluation Kit can be used to quickly evaluate the various features of the CY8CMBR3xxx solution. The kit also functions as an Arduino shield, making it compatible with the various Arduino-based controllers in the market. You can purchase this kit at the Cypress online store.

#### Online

In addition to print documentation, there are abundant web resources. The dedicated web page for the CY8CMBR3xxx family has all the current information.

#### **Training**

Free PSoC and CapSense technical training (on-demand, webinars, and workshops) is available online at www.cypress.com/training. The training covers a wide variety of topics and supports different skill levels to assist you in your designs.

#### **Technical Support**

For assistance with technical issues, search the Knowledge Base articles and forums at <a href="https://www.cypress.com/support">www.cypress.com/support</a>. If you cannot find an answer to your question, create a technical support case or call technical support at 1-800-541-4736.

# CY8CMBR3002, CY8CMBR3102 CY8CM-BR3106S, CY8CMBR3108 CY8CMBR3110, CY8CMBR3116 Datasheet

### **Contents**

| System Overview                          | 5  |

|------------------------------------------|----|

| Features Overview                        | 6  |

| CapSense Sensors                         | 6  |

| Sliders                                  | 6  |

| Proximity Sensors                        |    |

| SmartSense Auto-tuning                   |    |

| Liquid Tolerance                         | 6  |

| Noise Immunity                           |    |

| Flanking Sensor Suppression (FSS)        |    |

| Touch Feedback                           |    |

| General-Purpose Outputs (GPOs)           | 6  |

| Buzzer Drive                             | 6  |

| Register Configurability                 |    |

| Communication to Host                    |    |

| System Diagnostics                       |    |

| Ultra-Low Power Consumption              |    |

| MPN versus Features Summary              | 8  |

| Pinouts                                  |    |

| CY8CMBR3116 (16 Sensing Inputs)          | 9  |

| CY8CMBR3106S (16 Sensing Inputs;         |    |

| Sliders Supported)                       | 11 |

| CY8CMBR3108 (8 Sensing Inputs)           |    |

| CY8CMBR3110 (10 Sensing Inputs)          |    |

| CY8CMBR3102 (2 Sensing Inputs)           |    |

| CY8CMBR3002 (2 Sensing Inputs)           |    |

| Unused SPO Pin Connection                | 15 |

| Unused SPO Pin Connection for AXRES pins |    |

| Unused GPO Pin Connection                |    |

| Device Feature Details                   |    |

| Automatic Threshold                      |    |

| Sensitivity Control                      |    |

| Sensor Auto Reset                        |    |

| Noise Immunity                           |    |

| Flanking Sensor Suppression              |    |

| General-Purpose Outputs                  |    |

| LED ON Time                              |    |

| Toggle                                   |    |

| Buzzer Signal Output                     |    |

| Host Interrupt                           |    |

| Latch Status Output                      | 19 |

| Analog Voltage Output                    | 19 |

|------------------------------------------|----|

| System Diagnostics                       | 20 |

| Register Configurability                 | 20 |

| Example Application Schematics           | 21 |

| Power Supply Information                 |    |

| Electrical Specifications                |    |

| Absolute Maximum Ratings                 | 24 |

| Operating Temperature                    | 24 |

| DC Electrical Characteristics            | 24 |

| AC Electrical Specifications             | 25 |

| I2C Specifications                       | 26 |

| System Specifications                    |    |

| Power Consumption and Operational States | 29 |

| Response Time                            |    |

| CY8CMBR3xxx Resets                       |    |

| Host Communication Protocol              |    |

| I2C Slave Address                        |    |

| I2C Communication Guidelines             |    |

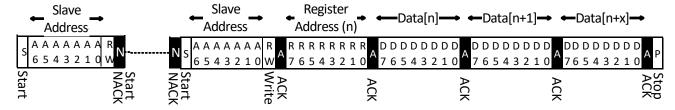

| Write Operation                          |    |

| Setting the Device Data Pointer          | 32 |

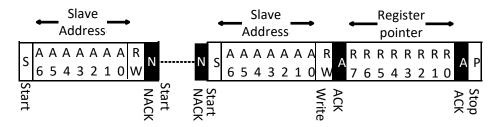

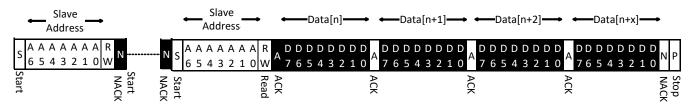

| Read Operation                           |    |

| Layout Guidelines and Best Practices     |    |

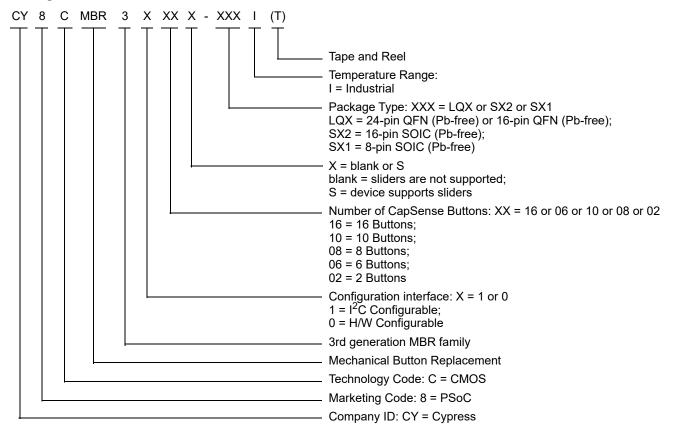

| Ordering Information                     | 34 |

| Ordering Code Definitions                |    |

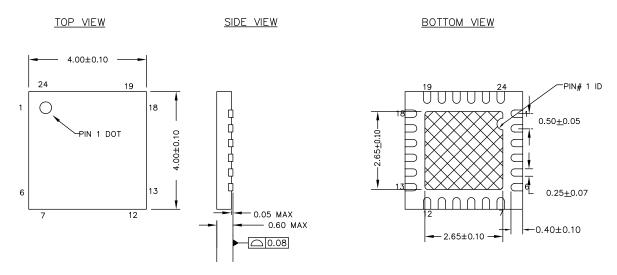

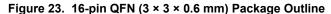

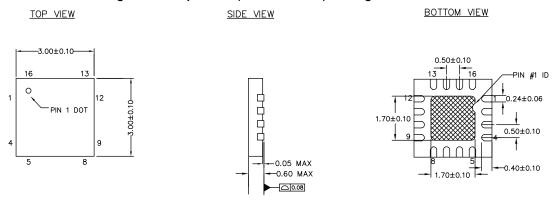

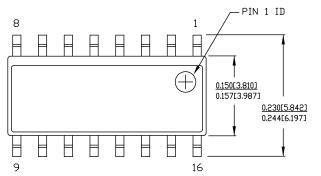

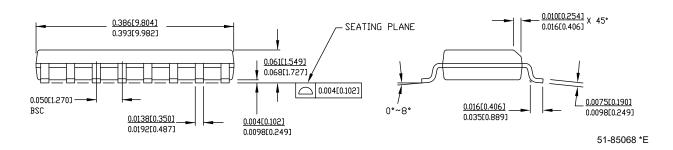

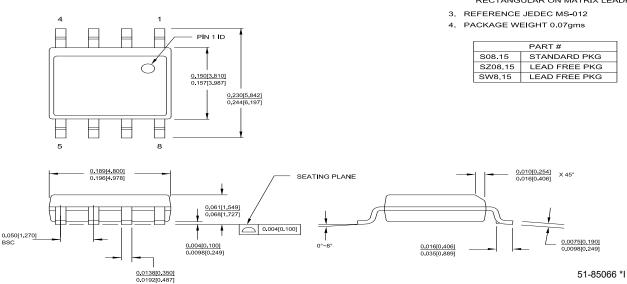

| Packaging Dimensions                     | 35 |

| Thermal Impedances                       |    |

| Solder Reflow Specifications             | 37 |

| Document Conventions                     |    |

| Units of Measure                         |    |

| Glossary                                 |    |

| Reference Documents                      |    |

| Document History Page                    | 40 |

| Sales, Solutions, and Legal Information  |    |

| Worldwide Sales and Design Support       |    |

| Products                                 |    |

| PSoC® Solutions                          |    |

| Cypress Developer Community              | 42 |

| Technical Support                        | 42 |

#### System Overview

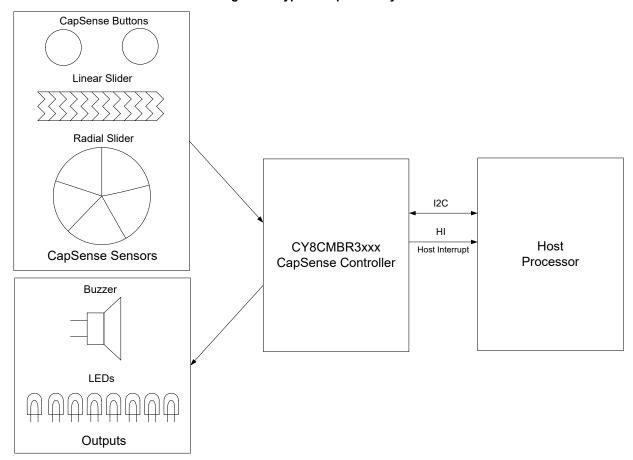

A capacitive sensor detects changes in capacitance to determine the presence of a touch or proximity to conductive objects. The capacitive sensor can be a capacitive button that replaces the traditional mechanical buttons, a capacitive slider that replaces mechanical knobs, or a proximity sensor that replaces an infrared sensor in a user interface solution. A typical capacitive user interface system consists of the following:

- A capacitive sensor

- An audio-visual output, such as a buzzer or an LED

- A capacitive sensing controller connected to the sensor

- A host processor

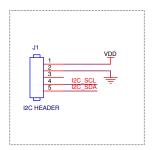

The capacitive controller connects the sensor and the output to the host processor through a communication interface, such as an I<sup>2</sup>C or a GPO.

The capacitive user interface system serves as a human-machine interface that takes the user's touch inputs and provides audio-visual feedback through a buzzer or an LED. CY8CMBR3xxx is a family of capacitive sensing controllers,

which senses the change in capacitance based on touch or proximity, and controls the user interface system accordingly. The sensing algorithm, built in the controllers, determines the presence of touch and drives the outputs or sends signals to the host processor. This algorithm can distinguish between the signal (based on touch or proximity) and noise, which can be caused by environmental or electrical conditions.

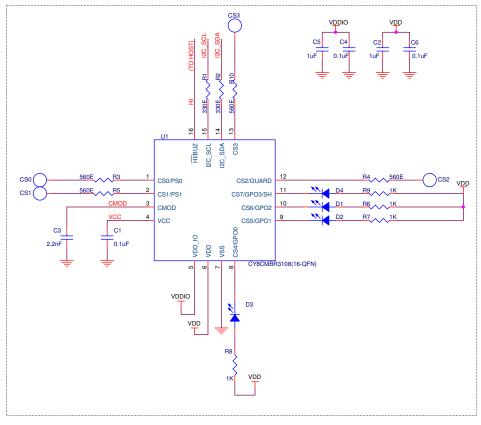

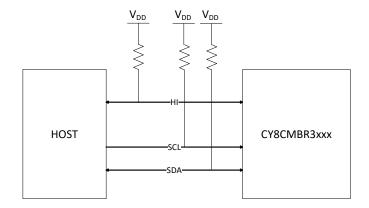

Figure 2 shows a typical user interface system with capacitive buttons connected to a CY8CMBR3xxx CapSense Express controller, which controls the system and also communicates with the host processor through I<sup>2</sup>C.

Traditionally, capacitive sensing controllers require firmware development to perform specific user interface functions and manual system tuning to achieve optimal performance. However, the CY8CMBR3xxx CapSense Express family of controllers does not require any firmware development, accelerating time-to-market. These devices feature SmartSense Auto-tuning, which eliminates the need for manual tuning, providing optimal performance even under extremely noisy conditions.

Figure 2. Typical CapSense System

# CY8CMBR3002, CY8CMBR3102 CY8CM-BR3106S, CY8CMBR3108 CY8CMBR3110, CY8CMBR3116 Datasheet

#### Features Overview

#### CapSense Sensors

The CY8CMBR3xxx family of controllers supports up to 16 capacitive sensors. These can be configured as follows:

- Up to 16 CapSense buttons

- Up to two sliders: Configurable as linear or radial sliders

- Up to two proximity sensors that can detect up to 30-cm proximity distance

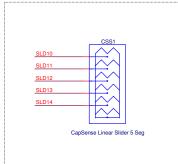

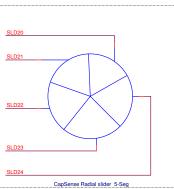

#### Sliders

- Supports up to two 5-segment sliders

- Configures each slider individually as linear or radial

- Combines both sliders to form one 10-segment slider

- Slider resolution is user-configurable

#### **Proximity Sensors**

- The CY8CMBR3xxx family supports up to two proximity sensors with a detection range of up to 30 cm. These proximity sensors are capable of detecting both proximity and touch events.

- The wake-on-approach feature wakes the devices from a low-power state to Active mode on a proximity event.

- The device also features driven shield, which enhances the proximity sensing range in the presence of metal objects.

- The device supports proximity sensors with C<sub>P</sub> ranging from 8 pF to 45 pF.

#### SmartSense Auto-tuning

The CY8CMBR3xxx family features SmartSense Auto-tuning, Cypress's patented CapSense algorithm, which continuously compensates for system and environmental changes during run time. SmartSense Auto-tuning has the following advantages:

- Reduces design effort by eliminating manual tuning

- Adapts to variations in PCB, overlay, paint, and manufacturing that degrade touch-sensing performance

- Eliminates manual tuning in production

- Adapts to changes in the system environment due to noise

- Allows a platform design approach with different overlays, button shapes, and trace lengths

#### **Liquid Tolerance**

The CY8CMBR3xxx family delivers water-tolerant designs that eliminate false touches due to wet conditions, such as water droplets, moisture, mist, steam, or even wet hands. The CapSense controller locks up the user interface in firmware to prevent touch inputs in streaming water.

The CY8CMBR3xxx family offers liquid-tolerance to liquids such as water, ketchup, oil, and blood.

Enable the shield electrode through the register map, using EZ-Click, to prevent false touches under wet conditions and enable both the shield electrode and guard sensor to prevent false touches in streaming water conditions. The shield electrode and guard sensor consume a port pin each in the CapSense controller. Refer to the CY8CMBR3xxx CapSense Design Guide for best practices and design guidelines for implementing liquid-tolerant designs.

#### **Noise Immunity**

The CY8CMBR3xxx family features the robust CSD PLUS capacitive sensing algorithm. Additionally, it implements the advanced noise immunity algorithm, EMC, for stable operation in extremely noisy conditions.

The EMC algorithm has higher average power consumption. For low-power applications, where noise conditions are not extreme, you can disable this feature through the I<sup>2</sup>C interface.

#### Flanking Sensor Suppression (FSS)

This feature distinguishes between signals from closely spaced buttons, eliminating false touches. It ensures that the system recognizes only the first button touched.

#### **Touch Feedback**

The CY8CMBR3xxx family has pins that you can configure for audio-visual feedback through a buzzer or an LED.

### **General-Purpose Outputs (GPOs)**

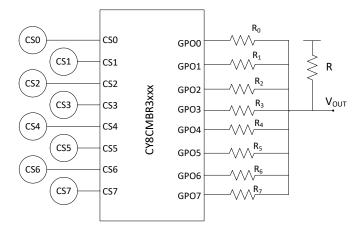

The GPOs are high-sink current outputs that can drive most LEDs. The GPO status can be controlled directly by the CapSense sensors so that a sensor 'ON' status automatically turns ON a corresponding LED. Alternatively, GPOs can be controlled by the host through the I<sup>2</sup>C interface.

The GPOs also support advanced features, such as:

- CSx to GPOx Direct Drive: Directly control the GPOs upon button touch or proximity event.

- Pulse width modulation (PWM): Controls LED brightness.

- Toggle: The GPO status is toggled upon every touch event on the button sensors, and proximity event on proximity sensors, to mimic the functionality of the mechanical toggle switch.

- Voltage output: Analog voltage that represents the button status.

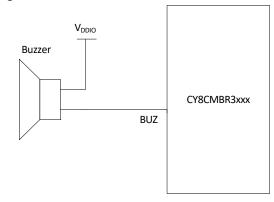

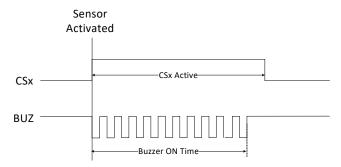

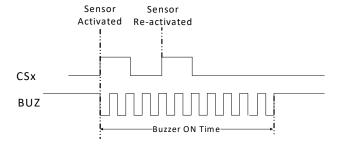

#### **Buzzer Drive**

The output pins of the CY8CMBR3xxx controllers can be configured for driving a single-input DC Piezo-electric buzzer through a PWM. The PWM frequency and buzzer activation duration are configurable. The buzzer output is activated for a finite amount of time when a finger touch is detected.

## CY8CMBR3002, CY8CMBR3102 CY8CM-BR3106S, CY8CMBR3108 CY8CMBR3110, CY8CMBR3116 Datasheet

#### Register Configurability

The CY8CMBR3xxx registers may be configured through the I<sup>2</sup>C interface. Device features may be enabled, disabled, or modified by writing appropriate values to the I<sup>2</sup>C configurable register map. This register map also provides various status outputs to indicate the touch/release status and system performance and debug parameters.

You can access the register map of the device through the I<sup>2</sup>C interface by a host controller, such as a microcontroller or the EZ-Click Customizer.

The CY8CMBR3xxx devices feature a safe register map update mechanism to overcome configuration data corruption, which can occur due to power failure during flash writes or any other spurious events. If the configuration data is corrupted during a register map update, the devices reconfigure themselves to the last known valid configuration.

#### **Communication to Host**

The CY8CMBR3xxx family communicates to a host processor through the following methods:

- The I<sup>2</sup>C interface allows the host to configure parameters and receive status information on touch events

- The host interrupt alerts the host when a new touch event occurs. This helps to build effective communication between the host and the CapSense controller. Alternatively, the CPU can poll the device status by reading through I<sup>2</sup>C.

- The GPO provides the ON or OFF sensor status to the host. The GPO ports can also be used to implement analog voltage and DC output (DCO) using an external resistor network.

#### System Diagnostics

The CY8CMBR3xxx devices are equipped with a system diagnostics feature to detect system-level fault conditions and to

avoid failure of the user interface design. The system diagnostic features also help to monitor system-level parameters to debug the design during development.

The built-in system diagnostics detects the following fault conditions at power-up and helps to monitor the following:

- Improper value of the modulating capacitor (C<sub>MOD</sub>)

- C<sub>P</sub> value out of range

- Sensor shorts

#### **Ultra-Low Power Consumption**

For low-power applications, such as those operated by a battery, select a capacitive sensing controller that has ultra-low average power consumption.

The CY8CMBR3xxx controllers draw an average current of  $22 \mu A$  per sensor at 1.8 V.

The CY8CMBR3xxx family supports two operating modes:

- Active: The sensors are scanned periodically for power optimization.

- Deep Sleep: The sensors are not scanned until a command from the host is received to resume sensor scanning.

In the Active mode, CY8CMBR3xxx family implements additional techniques, such as optimizing the average power consumption and providing a smooth user interface experience without increasing the refresh interval.

In addition to these modes, the device has a wake-on approach feature, which uses proximity sensing to reduce the average power consumption, ensuring power saving when the system is inactive.

Details of all features are documented in Device Feature Details on page 16.

Document Number: 001-85330 Rev. \*O Page 7 of 42

### **MPN versus Features Summary**

The CY8CMBR3xxx family consists of six MPNs, each MPN supporting a different feature set. The following table lists all MPNs and a summary of the features supported by each.

| #  | Feature                                  | CY8CMBR3116              | CY8CMBR3106S          | CY8CMBR3110              | CY8CMBR3108              | CY8CMBR3102              | CY8CMBR3002 |

|----|------------------------------------------|--------------------------|-----------------------|--------------------------|--------------------------|--------------------------|-------------|

| 1  | Maximum number of buttons                | 16                       | 11                    | 10                       | 8                        | 2                        | 2           |

| 2  | Maximum number of sliders                | ×                        | 2                     | ×                        | ×                        | ×                        | ×           |

| 3  | Maximum number of proximity sensors      | 2                        | 2                     | 2                        | 2                        | 2                        | ×           |

| 4  | Shield electrode                         | <b>V</b>                 | ~                     | ~                        | <b>V</b>                 | ~                        | ×           |

| 5  | Guard Sensor                             | V                        | ×                     | ~                        | ~                        | ×                        | ×           |

| 6  | Wake-on-approach                         | <b>V</b>                 | ~                     | ~                        | <b>V</b>                 | ~                        | ×           |

| 7  | Liquid tolerance                         | <b>V</b>                 | ×                     | ~                        | <b>V</b>                 | ~                        | ×           |

| 8  | Automatic threshold                      | <b>✓</b><br>Configurable | <b>✓</b> Configurable | <b>✓</b><br>Configurable | <b>✓</b><br>Configurable | <b>✓</b><br>Configurable | ~           |

| 9  | Threshold Override                       | ×                        | ~                     | ×                        | V                        | ~                        | ×           |

| 10 | Sensitivity Control                      | <b>V</b>                 | ~                     | ~                        | <b>V</b>                 | ~                        | ×           |

| 11 | Sensor auto-reset                        | V                        | ~                     | ~                        | V                        | ~                        | <b>2</b> 0s |

| 12 | Median & IIR filter                      | V                        | ~                     | ~                        | V                        | ~                        | ~           |

| 13 | Advanced-Low-Pass<br>Filter              | V                        | ×                     | ~                        | V                        | ~                        | ×           |

| 14 | Electromagnetic<br>Compatibility (EMC)   | V                        | ~                     | ~                        | V                        | ~                        | ×           |

| 15 | FSS                                      | V                        | ~                     | ~                        | V                        | ~                        | ×           |

| 16 | Maximum number of GPOs/LED drive outputs | 8                        | 0                     | 5                        | 4                        | 1                        | 2           |

| 17 | GPO/LED Sink and<br>Source Drive Support | <b>✓</b><br>Configurable | ×                     | <b>✓</b><br>Configurable | <b>✓</b><br>Configurable | <b>✓</b> Configurable    | Sink        |

| 18 | LED brightness control                   | V                        | ×                     | ~                        | V                        | ~                        | ×           |

| 19 | LED ON time                              | V                        | ×                     | ~                        | V                        | ~                        | ×           |

| 20 | Toggle                                   | V                        | ×                     | ~                        | V                        | ~                        | ×           |

| 21 | Buzzer Signal Output                     | V                        | ~                     | ~                        | V                        | ×                        | ×           |

| 22 | Host interrupt                           | V                        | ~                     | ~                        | V                        | ×                        | ×           |

| 23 | Latch Status Output                      | V                        | ~                     | ~                        | V                        | ~                        | ×           |

| 24 | Analog Voltage Output                    | V                        | ×                     | V                        | V                        | ~                        | ~           |

| 25 | System diagnostics                       | ~                        | ~                     | ~                        | ~                        | ~                        | ~           |

| 26 | I <sup>2</sup> C Interface               | V                        | ~                     | V                        | V                        | ~                        | ×           |

Document Number: 001-85330 Rev. \*O

## **Pinouts**

## CY8CMBR3116 (16 Sensing Inputs)

### Table 1. Pin Diagram and Definitions - CY8CMBR3116

| Pin# | Pin Name   | Туре  | Description If unused C                                                                                                             |                                                     | Default<br>Configuration | Pin Diagram                                                                                               |

|------|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------|

| 1    | CS0/PS0    | -     | CapSense button / proximity sensor, controls GPO0                                                                                   | Ground/Ground                                       | CS0                      | 70                                                                                                        |

| 2    | CS1/PS1    | -     | CapSense button / proximity sensor, controls GPO1                                                                                   | Ground/Ground                                       | CS1                      | XRES Hirbuz/GPO7 IZC SCL IZC SDA CS4 CS5                                                                  |

| 3    | CS2/GUARD  | -     | CapSense button / guard sensor, controls GPO2                                                                                       | Ground/Ground                                       | CS2                      |                                                                                                           |

| 4    | CS3        | -     | CapSense button, controls GPO3                                                                                                      | Ground                                              | CS3                      | CS0/PS0 = 1 18 CS6                                                                                        |

| 5    | CMOD       | -     | External modulator capacitor. Connect 2.2 nF/5 V/X7R or NPO capacitor                                                               | NA                                                  | CMOD                     | CS1/PS1 = 2 17 = CS7<br>CS2/GUARD = 3 <b>QFN</b> 16 = CS8/GP00<br>CS3 = 4 <b>(Top View)</b> 15 = CS9/GP01 |

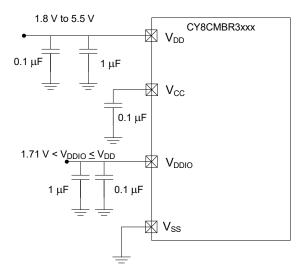

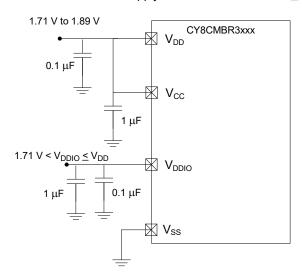

| 6    | VCC        | Power | Internal regulator output. Connect a 0.1-µF decoupling capacitor if VDD > 1.8 V. If VDD is 1.71 V to 1.89 V, short this pin to VDD. | NA                                                  | VCC                      | CMOD = 5 14                                                                                               |

| 7    | VDD        | Power | Power                                                                                                                               | NA                                                  | VDD                      | VDD                                                                                                       |

| 8    | VSS        | Power | Ground                                                                                                                              | NA                                                  | VSS                      | 15/St<br>14/Gf<br>12/Gf                                                                                   |

| 9    | CS15/SH/HI | I/DO  | CapSense button / shield electrode/ Host Interrupt (SPO1 in the register map)                                                       | Refer to Unused<br>SPO Pin Connection<br>on page 15 | Ħ                        | CS1.2<br>CS1.2<br>CS1.2<br>CS1.2                                                                          |

Table 1. Pin Diagram and Definitions - CY8CMBR3116 (continued)

| Pin# | Pin Name                  | Туре  | Description                                                                                | If unused                                                     | Default<br>Configuration | Pin Diagram |

|------|---------------------------|-------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------|-------------|

| 10   | CS14/GPO6                 | I/DO  | CapSense button / general purpose output (GPO)                                             | Ground/Refer to<br>Unused GPO Pin<br>Connection on<br>page 15 | GPO6                     |             |

| 11   | CS13/GPO5                 | I/DO  | CapSense button / GPO                                                                      | Ground/Refer to<br>Unused GPO Pin<br>Connection on<br>page 15 | GPO5                     |             |

| 12   | CS12/GPO4                 | I/DO  | CapSense button / GPO                                                                      | Ground/Refer to<br>Unused GPO Pin<br>Connection on<br>page 15 | GPO4                     |             |

| 13   | CS11/GPO3                 | I/DO  | CapSense button / GPO                                                                      | Ground/Refer to<br>Unused GPO Pin<br>Connection on<br>page 15 | GPO3                     |             |

| 14   | CS10/GPO2                 | I/DO  | CapSense button / GPO                                                                      | Ground/Refer to<br>Unused GPO Pin<br>Connection on<br>page 15 | GPO2                     |             |

| 15   | CS9/GPO1                  | I/DO  | CapSense button / GPO                                                                      | Ground/Refer to<br>Unused GPO Pin<br>Connection on<br>page 15 | GPO1                     |             |

| 16   | CS8/GPO0                  | I/DO  | CapSense button / GPO                                                                      | Ground/Refer to<br>Unused GPO Pin<br>Connection on<br>page 15 | GPO0                     |             |

| 17   | CS7                       | -     | CapSense button, controls GPO7                                                             | Ground                                                        | CS7                      |             |

| 18   | CS6 <sup>[2]</sup>        | -     | CapSense button, controls GPO6                                                             | Connect to VDD                                                | CS6                      |             |

| 19   | CS5                       | -     | CapSense button, controls GPO5                                                             | Ground                                                        | CS5                      |             |

| 20   | CS4                       | -     | CapSense button, controls GPO4                                                             | Ground                                                        | CS4                      |             |

| 21   | I2C SDA                   | DIO   | I2C data                                                                                   | Pull up                                                       | I2C SDA                  |             |

| 22   | I2C SCL                   | DIO   | I2C clock                                                                                  | Pull up                                                       | I2C SCL                  |             |

| 23   | HI/BUZ/<br>GPO7           | DO    | Host Interrupt / buzzer output / GPO (SPO0 in the register map)                            | Refer to Unused<br>SPO Pin Connection<br>on page 15           | GPO7                     |             |

| 24   | XRES                      | XRES  | Active Low external reset (an active low pulse on this pin resets the CapSense Controller) | Leave open                                                    | XRES                     |             |

| 25   | Center Pad <sup>[1]</sup> | E-pad | Connect to VSS for best mechanical, thermal, and electrical performance                    | Floating, not connected to any other signal                   | E-pad                    |             |

Legend: I = Analog Input, O = Analog Output, DIO = Digital Input/Output, DO = Digital Output, CS = CapSense Button, PS = Proximity Sensor SH = Shield Electrode, BUZ = Buzzer Output, GPO = General Purpose Output, GUARD = Guard Sensor, SPO = Special purpose output.

Document Number: 001-85330 Rev. \*O Page 10 of 42

<sup>1.</sup> The center pad on the QFN package should be connected to ground (VSS) for best mechanical, thermal, and electrical performance. If it is not connected to ground, it should be left floating without being connected to any other signal.

2. This I/O functions as reset (AXRES) pin during boot-up. Make certain that this pin is not grounded during power-up for the device to boot up properly. After boot-up, this I/O functions as indicated by the pin name.

#### CY8CMBR3106S (16 Sensing Inputs; Sliders Supported)

### Table 2. Pin Diagram and Definitions - CY8CMBR3106S

| Pin# | Pin Name                  | Туре  | Description                                                                                                                         | If unused                                        | Default<br>Configuration | Pin Diagram                                                                                                          |

|------|---------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------|

| 1    | CS0/PS0                   | -     | CapSense button / proximity sensor                                                                                                  | Ground/Ground                                    | CS0                      | I <del>-</del>                                                                                                       |

| 2    | CS1/PS1                   | ı     | CapSense button / proximity sensor                                                                                                  | Ground/Ground                                    | CS1                      | XRES<br>HI/BUZ<br>I2C SCL<br>I2C SDA<br>CS4<br>CS5/SH/HI                                                             |

| 3    | CS2                       | -     | CapSense button                                                                                                                     | Ground                                           | CS2                      |                                                                                                                      |

| 4    | CS3                       | -     | CapSense button                                                                                                                     | Ground                                           | CS3                      | CS0/PS0 = 1                                                                                                          |

| 5    | CMOD                      | ı     | External modulator capacitor.<br>Connect 2.2 nF/ 5 V/X7R or<br>NPO capacitor                                                        | NA                                               | CMOD                     | CS1/PS1 = 2 17 CS14/SLD23<br>CS2 = 3 QFN 16 CS13/SLD22<br>CS3 = 4 (Top View) 15 CS12/SLD21<br>CMOD = 5 14 CS11/SLD20 |

| 6    | VCC                       | Power | Internal regulator output. Connect a 0.1-µF decoupling capacitor if VDD > 1.8 V. If VDD is 1.71 V to 1.89 V, short this pin to VDD. | NA                                               | VCC                      | VCC = 6                                                                                                              |

| 7    | VDD                       | Power | Power                                                                                                                               | NA                                               | VDD                      |                                                                                                                      |

| 8    | VSS                       | Power | Ground                                                                                                                              | NA                                               | VSS                      |                                                                                                                      |

| 9    | SLD10                     | -     | Slider1, segment0                                                                                                                   | Ground                                           | SLD10                    |                                                                                                                      |

| 10   | SLD11                     | -     | Slider1, segment1                                                                                                                   | Ground                                           | SLD11                    |                                                                                                                      |

| 11   | SLD12                     | -     | Slider1, segment2                                                                                                                   | Ground                                           | SLD12                    |                                                                                                                      |

| 12   | SLD13                     | _     | Slider1, segment3                                                                                                                   | Ground                                           | SLD13                    |                                                                                                                      |

| 13   | SLD14                     | -     | Slider1, segment4                                                                                                                   | Ground                                           | SLD14                    |                                                                                                                      |

| 14   | CS11/SLD20                | -     | CapSense button / Slider2, segment0                                                                                                 | Ground/Ground                                    | SLD20                    |                                                                                                                      |

| 15   | CS12/SLD21                | ı     | CapSense button / Slider2, segment1                                                                                                 | Ground/Ground                                    | SLD21                    |                                                                                                                      |

| 16   | CS13/SLD22                | ı     | CapSense button / Slider2, segment2                                                                                                 | Ground/Ground                                    | SLD22                    |                                                                                                                      |

| 17   | CS14/SLD23                | ı     | CapSense button / Slider2, segment3                                                                                                 | Ground/Ground                                    | SLD23                    |                                                                                                                      |

| 18   | CS15/SLD24 <sup>[4]</sup> | ı     | CapSense button / Slider2, segment4                                                                                                 | Connect to VDD/Connect to VDD                    | SLD24                    |                                                                                                                      |

| 19   | CS5/SH/HI                 | -     | CapSense button / shield electrode/host interrupt. (SPO1 in the register map)                                                       | Refer to Unused SPO Pin<br>Connection on page 15 | CS5                      |                                                                                                                      |

| 20   | CS4                       | -     | CapSense Button                                                                                                                     | Ground                                           | CS4                      |                                                                                                                      |

| 21   | I2C SDA                   | DIO   | I2C Data                                                                                                                            | Pull up                                          | I2C SDA                  |                                                                                                                      |

| 22   | I2C SCL                   | DIO   | I2C Clock                                                                                                                           | Pull up                                          | I2C SCL                  |                                                                                                                      |

| 23   | HI/BUZ                    | 0     | Host interrupt / buzzer output.<br>This pin acts as SPO0 for this<br>device (SPO0 in register map).                                 | Refer to Unused SPO Pin<br>Connection on page 15 | HI                       |                                                                                                                      |

| 24   | XRES                      | XRES  | External reset                                                                                                                      | Leave open                                       | XRES                     |                                                                                                                      |

| 25   | Center Pad <sup>[3]</sup> | E-pad | Connect to VSS for best mechanical, thermal and electrical performance                                                              | Floating, not connected to any other signal      | E-pad                    |                                                                                                                      |

**Legend**: I = Analog Input, O = Analog Output, DIO = Digital Input/Output, CS = CapSense Button, PS = Proximity Sensor, SH = Shield Electrode, BUZ = Buzzer Output, SPO = Special Purpose Output.

#### Notes

- The center pad on the QFN package should be connected to ground (VSS) for best mechanical, thermal, and electrical performance. If it is not connected to ground, it should be left floating without being connected to any other signal.

This I/O functions as reset (AXRES) pin during boot-up. Make certain that this pin is not grounded during power-up for the device to boot up properly. After boot-up, this I/O functions as indicated by the pin name.

Document Number: 001-85330 Rev. \*O Page 11 of 42

#### CY8CMBR3108 (8 Sensing Inputs)

#### Table 3. Pin Diagram and Definitions - CY8CMBR3108

| Pin# | Pin Name                  | Туре  | Description                                                                                                                                                  | If unused                                                  | Default<br>Configuration | Pin Diagram                                             |

|------|---------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------|---------------------------------------------------------|

| 1    | CS0/PS0                   | -     | CapSense button / proximity sensor, controls GPO0                                                                                                            | Ground/Ground                                              | CS0                      |                                                         |

| 2    | CS1/PS1                   | _     | CapSense button / proximity sensor, controls GPO1                                                                                                            | Ground/Ground                                              | CS1                      | HIBUZ<br>12C SCL<br>12C SDA<br>CS3                      |

| 3    | CMOD                      | -     | External modulator capacitor.<br>Connect 2.2 nF/5 V/X7R or<br>NPO capacitor                                                                                  | NA                                                         | CMOD                     | CS0/PS0 = 1 12 CS2/GUARD CS1/PS1 = 2 QFN 11 CS7/GP03/SH |

| 4    | VCC                       | Power | Internal regulator output. Connect a 0.1-µF decoupling capacitor if VDD > 1.8 V. If VDD is 1.71 V to 1.89 V, short this pin to VDD                           | NA                                                         | vcc                      | CMOD 3 (Top View) 10 CS6/GPO2 9 CS5/GPO1                |

| 5    | VDDIO                     | Power | Power for I2C and HI lines                                                                                                                                   | Connect to VDD                                             | VDDIO                    | N 284/C                                                 |

| 6    | VDD                       | Power | Power                                                                                                                                                        | NA                                                         | VDD                      |                                                         |

| 7    | VSS                       | Power | Ground                                                                                                                                                       | NA                                                         | VSS                      |                                                         |

| 8    | CS4/GPO0                  | I/DO  | CapSense button / GPO                                                                                                                                        | Ground/Refer to Unused<br>GPO Pin Connection on<br>page 15 | GPO0                     |                                                         |

| 9    | CS5/GPO1                  | -     | CapSense button / GPO                                                                                                                                        | Ground/Refer to Unused<br>GPO Pin Connection on<br>page 15 | GPO1                     |                                                         |

| 10   | CS6/GPO2                  | I/DO  | CapSense button / GPO                                                                                                                                        | Ground/Refer to Unused<br>GPO Pin Connection on<br>page 15 | GPO2                     |                                                         |

| 11   | CS7/GPO3/<br>SH           | I/DO  | CapSense button / GPO/ shield electrode. (SPO1 in the register map)                                                                                          | Refer to Unused SPO Pin<br>Connection on page 15           | GPO3                     |                                                         |

| 12   | CS2/GUARD <sup>[6]</sup>  | _     | CapSense button, controls<br>GPO2 / guard sensor                                                                                                             | Connect to VDD/Connect to VDD                              | CS2                      |                                                         |

| 13   | CS3                       | -     | CapSense button, controls GPO3                                                                                                                               | Ground                                                     | CS3                      |                                                         |

| 14   | I2C SDA                   | DIO   | I2C data                                                                                                                                                     | Pull up                                                    | I2C SDA                  |                                                         |

| 15   | I2C SCL                   | DIO   | I2C clock                                                                                                                                                    | Pull up                                                    | I2C SCL                  |                                                         |

| 16   | HI/BUZ                    | DO    | Host interrupt / buzzer output<br>Supply voltage for <u>bu</u> zzer and<br>pull-up resistor on HI should be<br>equal to VDDIO<br>(SPO0 in the register map). | Refer to Unused SPO Pin<br>Connection on page 15           | Ή                        |                                                         |

| 17   | Center Pad <sup>[5]</sup> | E-pad | Connect to VSS for best mechanical, thermal and electrical performance                                                                                       | Floating, not connected to any other signal                | E-pad                    |                                                         |

Legend: I = Analog Input, O = Analog Output, DIO = Digital Input/Output, CS = CapSense Button, PS = Proximity Sensor SH = Shield Electrode, BUZ = Buzzer Output, GPO = General Purpose Output, GUARD = Guard Sensor, SPO = Special Purpose Output.

Document Number: 001-85330 Rev. \*O Page 12 of 42

The center pad on the QFN package should be connected to ground (VSS) for best mechanical, thermal, and electrical performance. If it is not connected to ground, it should be left floating without being connected to any other signal.

This I/O functions as reset (AXRES) pin during boot-up. Make certain that this pin is not grounded during power-up for the device to boot up properly. After boot-up, this I/O functions as indicated by the pin name.

#### CY8CMBR3110 (10 Sensing Inputs)

### Table 4. Pin Diagram and Definitions - CY8CMBR3110

|      |                                    |       |                                                                                                                                                | 16-SOIC                                                            |                          |                                                            |

|------|------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------|------------------------------------------------------------|

| Pin# | Pin Name                           | Туре  | Description                                                                                                                                    | If unused                                                          | Default<br>Configuration | Pin Diagram                                                |

| 1    | I2C SDA                            | DIO   | I2C data                                                                                                                                       | Pull up                                                            | I2C SDA                  |                                                            |

| 2    | I2C SCL                            | DIO   | I2C clock                                                                                                                                      | Pull up                                                            | I2C SCL                  | 12C SDA 1 16 CS4/SH                                        |

| 3    | CS0/PS0                            | _     | CapSense button / proximity sensor, controls GPO0                                                                                              | Ground/Ground                                                      | CS0                      | 12C SCL                                                    |

| 4    | CS1/PS1                            | ı     | CapSense button / proximity sensor, controls GPO1                                                                                              | Ground/Ground                                                      | CS1                      | CS1/PS1 4 SOIC 13 CS2/GUARD CMOD 5 12 CS8/GPO3             |

| 5    | CMOD                               | _     | External modulator capacitor.<br>Connect 2.2 nF/5 V/X7R or<br>NPO capacitor                                                                    | NA                                                                 | CMOD                     | VCC 6 11 CS7/GP02<br>VDD 7 10 CS5/GP01<br>VSS 8 9 CS5/GP00 |

| 6    | VCC                                | Power | Internal regulator output.<br>Connect a 0.1-µF decoupling<br>capacitor if VDD > 1.8 V. If<br>VDD is 1.71 V to 1.89 V, short<br>this pin to VDD | NA                                                                 | VCC                      |                                                            |

| 7    | VDD                                | Power | Power                                                                                                                                          | NA                                                                 | VDD                      |                                                            |

| 8    | VSS                                | Power | Ground                                                                                                                                         | NA                                                                 | VSS                      |                                                            |

| 9    | CS5/GPO0                           | I/DO  | CapSense button / GPO                                                                                                                          | Ground/Refer to<br>Unused GPO Pin<br>Connection on<br>page 15      | GPO0                     |                                                            |

| 10   | CS6/GPO1                           | I/DO  | CapSense button / GPO                                                                                                                          | Ground/Refer to<br>Unused GPO Pin<br>Connection on<br>page 15      | GPO1                     |                                                            |

| 11   | CS7/GPO2                           | I/DO  | CapSense button / GPO                                                                                                                          | Ground/Refer to<br>Unused GPO Pin<br>Connection on<br>page 15      | GPO2                     |                                                            |

| 12   | CS8/GPO3                           | I/DO  | CapSense button / GPO                                                                                                                          | Ground/Refer to<br>Unused GPO Pin<br>Connection on<br>page 15      | GPO3                     |                                                            |

| 13   | CS2/GUARD                          | _     | CapSense button, controls<br>GPO2 / guard sensor                                                                                               | Ground/Ground                                                      | CS2                      |                                                            |

| 14   | CS9/GPO4/HI/<br>BUZ <sup>[7]</sup> | I/DO  | CapSense button / GPO / host interrupt / buzzer output. (SPO1 in the register map)                                                             | Refer Unused SPO<br>Pin Connection for<br>AXRES pins on<br>page 15 | GPO4                     |                                                            |

| 15   | CS3                                | 1     | CapSense button, controls GPO3                                                                                                                 | Ground                                                             | CS3                      |                                                            |

| 16   | CS4/SH                             | I/O   | CapSense button, controls GPO4 / shield electrode (SPO0 in the register map).                                                                  | Refer to Unused<br>SPO Pin<br>Connection on<br>page 15             | CS4                      |                                                            |

Legend: I = Analog Input, O = Analog Output, DIO = Digital Input/Output, CS = CapSense Button, PS = Proximity Sensor SH = Shield Electrode, BUZ = Buzzer Output, GPO = General Purpose Output, GUARD = Guard Sensor, SPO = Special Purpose Output.

Document Number: 001-85330 Rev. \*O Page 13 of 42

This I/O functions as reset (AXRES) pin during boot-up. Make certain that this pin is not grounded during power-up for the device to boot up properly. After boot-up, this I/O functions as indicated by the pin name.

#### CY8CMBR3102 (2 Sensing Inputs)

#### Table 5. Pin Diagram and Definitions - CY8CMBR3102

|      | 8-SOIC                 |        |                                                                                                                                     |                                                     |                          |                                                               |  |

|------|------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------|---------------------------------------------------------------|--|

| Pin# | Pin Name               | Type   | Description                                                                                                                         | If unused                                           | Default<br>Configuration | Pin Diagram                                                   |  |

| 1    | I2C SCL                | DIO    | I2C clock                                                                                                                           | Pull up                                             | I2C SCL                  |                                                               |  |

| 2    | CMOD                   | -      | External modulator capacitor.<br>Connect 2.2 nF/5 V/X7R or NPO<br>capacitor                                                         | NA                                                  | CMOD                     | 12C SCL 1 8 12C SDA                                           |  |

| 3    | VCC                    | Power  | Internal regulator output. Connect a 0.1-µF decoupling capacitor if VDD > 1.8 V. If VDD is 1.71 V to 1.89 V, short this pin to VDD. | NA                                                  | VCC                      | CMOD 2 2 SOIC 7 CSÖ/PS0 VCC 3 3 6 CS1/PS1/GPO0/SH VDD 4 5 VSS |  |

| 4    | VDD                    | Power  | Power                                                                                                                               | NA                                                  | VDD                      |                                                               |  |

| 5    | VSS                    | Power  | Ground                                                                                                                              | NA                                                  | VSS                      |                                                               |  |

| 6    | CS1/PS1/<br>GPO0/SH    | I/DO/O | CapSense button / proximity sensor/<br>GPO/ shield electrode (SPO0 in the<br>register map).                                         | Refer to Unused<br>SPO Pin Connection<br>on page 15 | GPO0                     |                                                               |  |

| 7    | CS0/PS0 <sup>[8]</sup> | -      | CapSense button / proximity sensor, controls GPO0                                                                                   | Connect to VDD/<br>Connect to VDD                   | CS0                      |                                                               |  |

| 8    | I2C SDA                | DIO    | I2C data                                                                                                                            | Pull up                                             | I2C SDA                  |                                                               |  |

Legend: I = Analog Input, O = Analog Output, DIO = Digital Input/Output, CS = CapSense Button, PS = Proximity Sensor, SH = Shield Electrode, GPO = General Purpose Output, SPO = Special Purpose Output.

#### CY8CMBR3002 (2 Sensing Inputs)

#### Table 6. Pin Diagram and Definitions - CY8CMBR3002

|      | 8-SOIC             |       |                                                                                                                                              |                |                                   |  |  |

|------|--------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------|--|--|

| Pin# | Pin Name           | Туре  | Description                                                                                                                                  | If unused      | Pin Diagram                       |  |  |

| 1    | GPO1               | DO    | Active-low GPO with open-drain-low drive mode                                                                                                | Ground         |                                   |  |  |

| 2    | CMOD               | I/O   | External modulator capacitor.<br>Connect 2.2 nF/5 V/X7R or NPO<br>capacitor                                                                  | NA             | GPO1                              |  |  |

| 3    | VCC                | Power | Internal regulator output. Connect<br>a 0.1-µF decoupling capacitor if<br>VDD > 1.8 V. If VDD is 1.71 V to<br>1.89 V, short this pin to VDD. | NA             | VCC = 3 SOIC 6 CS1  VDD = 4 5 VSS |  |  |

| 4    | VDD                | Power | Power                                                                                                                                        | NA             |                                   |  |  |

| 5    | VSS                | Power | Ground                                                                                                                                       | NA             | 1                                 |  |  |

| 6    | CS1                | _     | CapSense button, controls GPO1                                                                                                               | Ground         | 1                                 |  |  |

| 7    | CS0 <sup>[8]</sup> | -     | CapSense button, controls GPO0                                                                                                               | Connect to VDD | 1                                 |  |  |

| 8    | GPO0               | DO    | Active-low GPO with open-drain-low drive mode                                                                                                | Ground         |                                   |  |  |

Legend: I = Analog Input, DO = Digital Output, CS = CapSense Button, GPO = General Purpose Output

#### Note

Document Number: 001-85330 Rev. \*O Page 14 of 42

<sup>8.</sup> This I/O functions as reset (AXRES) pin during boot-up. Make certain that this pin is not grounded during power-up for the device to boot up properly. After boot-up, this I/O functions as indicated by the pin name.

#### **Unused SPO Pin Connection**

The following table lists the recommended pin connections for different configurations of SPO pins if an SPO pin is unused. Note that this table is not applicable to SPO pins which act as AXRES during boot up.

Table 7. Unused SPO Pin Connection

| SPO Pin Configuration | Recommended pin connection if unused       |

|-----------------------|--------------------------------------------|

| CS                    | Connect to Ground                          |

| HI                    | Leave Open                                 |

| SH                    | Leave Open                                 |

| GPO                   | Refer to "Unused GPO Pin Connection" Table |

| BUZ                   | Leave Open                                 |

| Disabled              | Leave Open                                 |

## Unused SPO Pin Connection for AXRES pins

Unused SPO pins which act as AXRES during boot up should be left open and should be disabled through the I2C configurable register map (using Ez-Click or any other configuration tool mentioned in section "Configuring CY8CMBR3xxx" of CY8CMBR3xxx CapSense Design Guide).

#### **Unused GPO Pin Connection**

The following table lists the recommended pin connections for different drive modes of GPO pins if a GPO pin is unused. Note that this table is not applicable to GPO pins which act as AXRES during boot up.

Table 8. Unused GPO Pin Connection

| GPO drive mode | Recommended pin connection if unused |

|----------------|--------------------------------------|

| Open Drain Low | Connect to Ground                    |

| Strong         | Leave Open                           |

Document Number: 001-85330 Rev. \*O Page 15 of 42

#### **Device Feature Details**

#### Table 9. Device Feature Benefits

| Feature                                  | Benefits                                                                                                                                                                                                                                          |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Automatic Threshold                      | Automatically tunes all the threshold parameters of the sensors for different noise settings                                                                                                                                                      |

| Sensitivity Control                      | Maintains optimal button performance for different overlay and noise conditions                                                                                                                                                                   |

| Sensor Auto Reset                        | Recalibrates the sensor when a stuck-sensor (fault) condition occurs, and avoids invalid sensor output status to host                                                                                                                             |

| Noise Immunity                           | Provides immunity against external noise and the ability to detect touches without false trigger in noisy environments                                                                                                                            |

| Flanking Sensor<br>Suppression (FSS)     | Avoids multiple button triggers in a design with closely spaced buttons                                                                                                                                                                           |

| Host Controlled GPOs                     | GPO pins, which can be controlled by the host processor through I <sup>2</sup> C                                                                                                                                                                  |

| LED On time                              | GPO output status stays ON for a set duration after the touch is released to provide better visual feedback to the user                                                                                                                           |

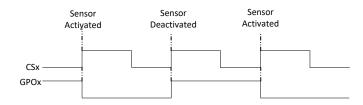

| Toggle                                   | Sensor output status toggles on<br>every sensor activation to mimic the<br>mechanical toggle button<br>functionality                                                                                                                              |

| Buzzer Signal Output                     | Provides audio feedback on button touch                                                                                                                                                                                                           |

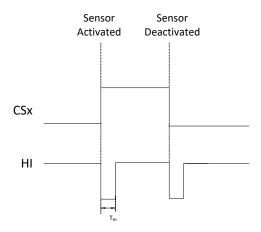

| Host Interrupt                           | Provides interrupt to host when there is a change in sensor status                                                                                                                                                                                |

| Latch Status Output                      | Latches the sensor status changes in the register until the host reads the activated sensor status; this ensures that the sensor status is always read by the host even if the host is late to service the host interrupt signal from CY8CMBR3xxx |

| Analog Voltage Output                    | Indicates the button status through voltage levels                                                                                                                                                                                                |

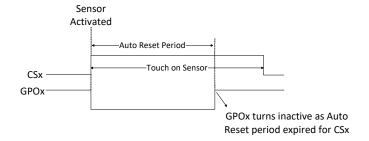

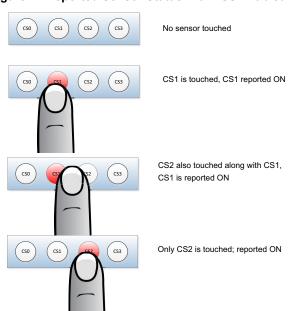

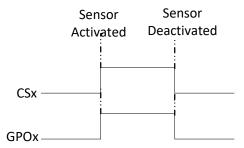

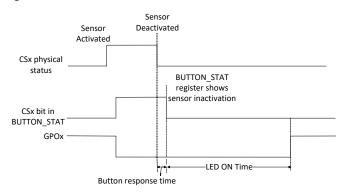

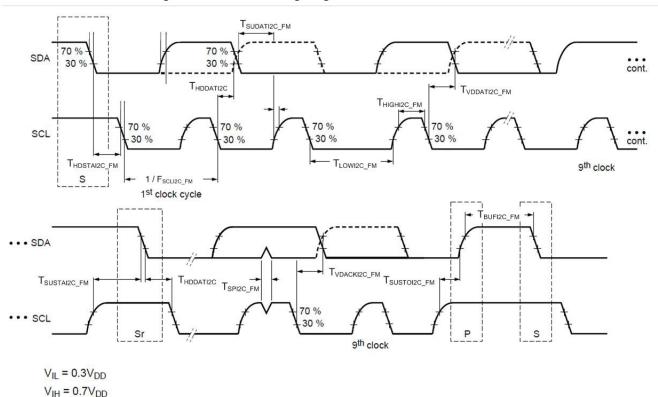

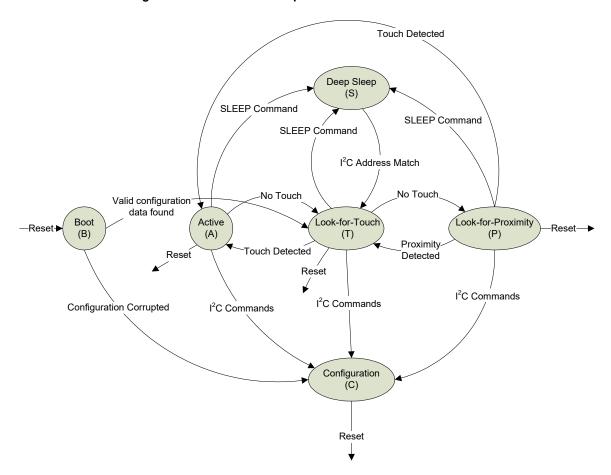

| System Diagnostics                       | Supports production testing and debugging                                                                                                                                                                                                         |