#### **Data Sheet**

# Dual, 12-/14-/16-Bit,1 GSPS Digital-to-Analog Converters

# AD9776A/AD9778A/AD9779A

#### **FEATURES**

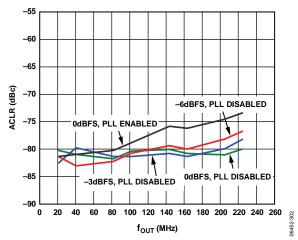

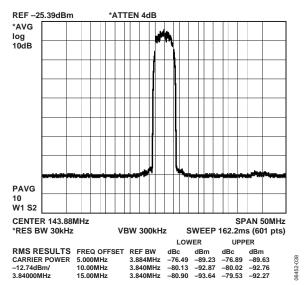

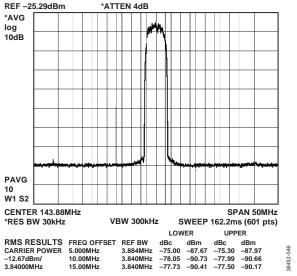

Low power: 1.0 W @ 1 GSPS, 600 mW @ 500 MSPS, full operating conditions Single carrier W-CDMA ACLR = 80 dBc @ 80 MHz IF Analog output: adjustable 8.7 mA to 31.7 mA,  $R_L = 25 \Omega$  to 50  $\Omega$

Novel 2×, 4×, and 8× interpolator/coarse complex modulator allows carrier placement anywhere in DAC bandwidth Auxiliary DACs allow control of external VGA and offset control Multiple chip synchronization interface High performance, low noise PLL clock multiplier Digital inverse sinc filter 100-lead, exposed paddle TQFP

#### **APPLICATIONS**

Wireless infrastructure

W-CDMA, CDMA2000, TD-SCDMA, WiMax, GSM, LTE

Digital high or low IF synthesis

Internal digital upconversion capability

Transmit diversity

Wideband communications: LMDS/MMDS, point-to-point

#### **GENERAL DESCRIPTION**

The AD9776A/AD9778A/AD9779A are dual, 12-/14-/16-bit, high dynamic range digital-to-analog converters (DACs) that provide a sample rate of 1 GSPS, permitting a multicarrier generation up to the Nyquist frequency. They include features optimized for direct conversion transmission applications, including complex digital modulation and gain and offset compensation. The DAC outputs are optimized to interface seamlessly with analog quadrature modulators such as the ADL537x FMOD series from Analog Devices, Inc. A 3-wire interface provides for programming/readback of many internal parameters. Full-scale output current can be programmed over a range of 10 mA to 30 mA. The devices are manufactured on an advanced 0.18 µm CMOS process and operate on 1.8 V and 3.3 V supplies for a total power consumption of 1.0 W. They are enclosed in a 100-lead thin quad flat package (TQFP).

#### **PRODUCT HIGHLIGHTS**

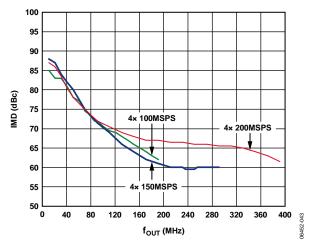

- 1. Ultralow noise and intermodulation distortion (IMD) enable high quality synthesis of wideband signals from baseband to high intermediate frequencies.

- 2. A proprietary DAC output switching technique enhances dynamic performance.

- 3. The current outputs are easily configured for various single-ended or differential circuit topologies.

- 4. CMOS data input interface with adjustable setup and hold.

- 5. Novel 2×, 4×, and 8× interpolator/coarse complex modulator allows carrier placement anywhere in DAC bandwidth.

# TYPICAL SIGNAL CHAIN COMPLEX I AND Q DC DIGITAL INTERPOLATION FILTERS FPGA/ASIC/DSP AD9776A/AD9778A/AD9779A TYPICAL SIGNAL CHAIN QUADRATURE MODULATOR/ MIXER/ AMPLIFIER POST DAC ANALOG FILTER A AD9776A/AD9778A/AD9779A

Figure 1.

# **Data Sheet**

# AD9776A/AD9778A/AD9779A

# **TABLE OF CONTENTS**

| Features                                                              | 1  |

|-----------------------------------------------------------------------|----|

| Applications                                                          | 1  |

| General Description                                                   | 1  |

| Product Highlights                                                    | 1  |

| Typical Signal Chain                                                  | 1  |

| Revision History                                                      | 3  |

| Functional Block Diagram                                              | 4  |

| Specifications                                                        | 5  |

| DC Specifications                                                     | 5  |

| Digital Specifications                                                | 6  |

| Digital Input Data Timing Specifications                              | 7  |

| AC Specifications                                                     | 8  |

| Absolute Maximum Ratings                                              | 9  |

| Thermal Resistance                                                    | 9  |

| ESD Caution                                                           | 9  |

| Pin Configurations and Function Descriptions                          | 10 |

| Typical Performance Characteristics                                   | 16 |

| Terminology                                                           | 24 |

| Theory of Operation                                                   | 25 |

| Differences Between AD9776/AD9778/ AD9779 and AD9776A/AD9778A/AD9779A | 25 |

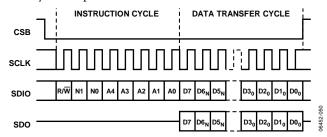

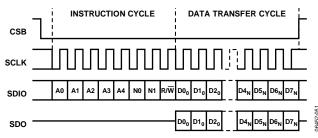

| 3-Wire Interface                                                      | 26 |

| General Operation of the Serial Interface                             | 26 |

| Instruction Byte                                                      | 26 |

| Serial Interface Port Pin Descriptions                                | 27 |

| MSB/LSB Transfers                                                     | 27 |

| 3-Wire Interface Register Map                                         | 28 |

| Interpolation Filter Architecture                                     | 33 |

| Interpolation Filter Bandwidth Limits                                 | 37 |

| Inverse Sinc Filter                     |

|-----------------------------------------|

| Sourcing the DAC Sample Clock           |

| Direct Clocking                         |

| Clock Multiplication                    |

| Driving the REFCLK Input                |

| Full-Scale Current Generation           |

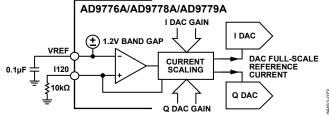

| Internal Reference                      |

| Gain and Offset Correction44            |

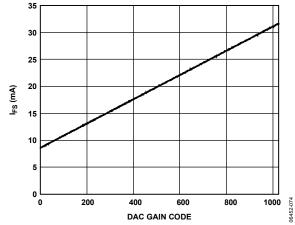

| I/Q Channel Gain Matching44             |

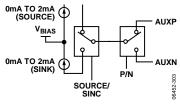

| Auxiliary DAC Operation                 |

| LO Feedthrough Compensation             |

| Results of Gain and Offset Correction45 |

| Input Data Ports                        |

| Single Port Mode                        |

| Dual Port Mode                          |

| Input Data Referenced to DATACLK        |

| Input Data Referenced to REFCLK         |

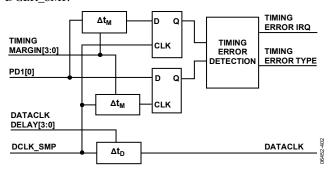

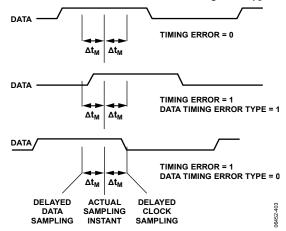

| Optimizing the Data Input Timing        |

| Device Synchronization                  |

| Synchronization Logic Overview          |

| Synchronizing Devices to a System Clock |

| Interrupt Request Operation 50          |

| Power Dissipation51                     |

| Power-Down and Sleep Modes52            |

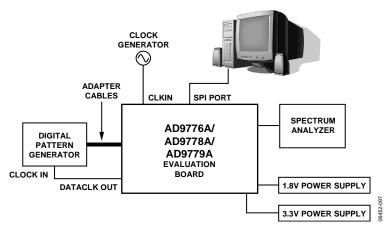

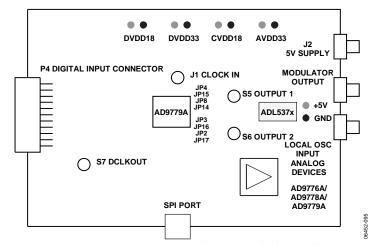

| Evaluation Board Overview53             |

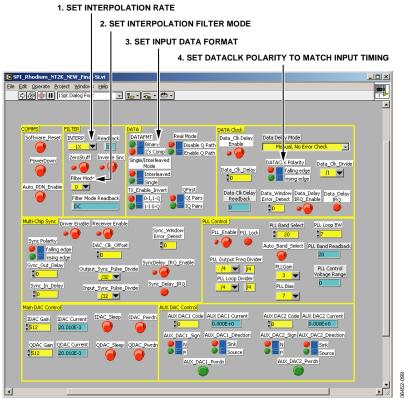

| Evaluation Board Operation53            |

| Outline Dimensions                      |

| Ordering Guide55                        |

#### **REVISION HISTORY**

| 9/2017—Rev. B to Rev. C                                       |   |

|---------------------------------------------------------------|---|

| Deleted Input Data Delay Line, Manual, and Automatic          |   |

| Connection Modes Section                                      | 5 |

| Changes to Hex 0x03, Bit 6, Table 132                         | 8 |

| Changes to Hex 0x03, Bit 7 and Hex 0x09, Bits 6:5, Table 143  | 0 |

| Changes to Optimizing the Data Input Timing Section4          | 8 |

| Deleted Automatic Timing Optimization Section4                | 8 |

| · ·                                                           |   |

| 9/2008—Rev. A to Rev. B                                       |   |

| Changed Serial Peripheral Interface (SPI) to 3-Wire Interface |   |

| Throughout                                                    | 1 |

| Change to Features Section                                    | 1 |

| Change to Applications Section                                | 1 |

| Changes to Integral Nonlinearity (INL) Parameter, Table 1     | 5 |

| Changes to DAC Clock Input (REFCLK+, REFCLK-)                 |   |

| Parameter, Table 2                                            | 6 |

| Changes to Input Data Parameter, Table 3                      | 7 |

| Changes to Hold Time Parameters, Table 3                      |   |

| Added 3-Wire Interface Parameter, Table 3                     |   |

| Added Reset Parameter, Table 3                                | 7 |

| Changes to Endnotes, Table 3                                  | 7 |

| Added Exposed Pad Notation to Figure 3, Changes to Table 7 1  |   |

| Added Exposed Pad Notation to Figure 4, Changes to Table 8 1  |   |

| Added Exposed Pad Notation to Figure 5, Changes to Table 9 1  |   |

| Changes to DATACLK Delay Range Section2                       |   |

| Changes to Version Register Section2                          | 5 |

| Changes to Table 102                                          |   |

| Changes to Table 122                                          | 6 |

| Changes to Table 132                                          | 8 |

| Changes to Table 142                                          | 9 |

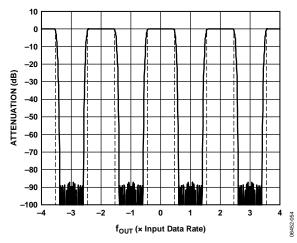

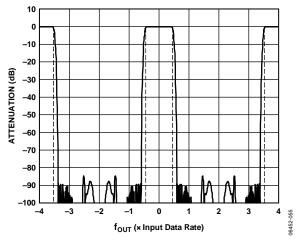

| Changes to Interpolation Filter Architecture Section3         | 3 |

| Changes to Figure 60                                          | 4 |

| Changes to Table 193                                          |   |

| Changes to Interpolation Filter Bandwidth Limits Section3     | 7 |

| Changes to Figure 703                                         | 7 |

| Added Digital Modulation Section3                             | 7 |

| Added Table 20 and Table 21; Renumbered Sequentially3         | 8 |

| Added Inverse Sinc Filter Section3                            | 8 |

| Added Figure 71; Renumbered Sequentially3                     | 8 |

| Changes to Clock Multiplication Section3                      | 9 |

| Changes to Figure 723                                         | 9 |

| Changes to Configuring the PLL Band Select Value Section3     | 9 |

| Changes to Configuring the PLL Band Select with Temperature   | • |

| Sensing Section4                                              | 1 |

| Changes to Known Temperature Calibration with Memory          |   |

| Section4                                                      | 1 |

| Changes to Set-and-Forget Device Option Section4              | 1 |

| Added Table 264                                               | 1 |

| Changes to Internal Reference Section                     | 43    |

|-----------------------------------------------------------|-------|

| Changed Transmit Path Gain and Offset Correction Headir   | ng to |

| Gain and Offset Correction                                | 44    |

| Changes to I/Q Channel Gain Matching Section              | 44    |

| Changes to Auxiliary DAC Operation Section                | 44    |

| Replaced Figure 79                                        |       |

| Deleted Figure 79; Renumbered Sequentially                | 41    |

| Changes to LO Feedthrough Compensation Section            | 45    |

| Changes to Table 28                                       | 47    |

| Changes to Optimizing the Data Input Timing Section       | 48    |

| Change to Synchronization Logic Overview Section          | 49    |

| Changes to Figure 88                                      | 49    |

| Changes to Figure 101                                     | 53    |

| Deleted Using the ADL5372 Quadrature Modulator Section    | and   |

| Figure 104                                                | 51    |

| Deleted Evaluation Board Schematics Section and Figure 10 | )5;   |

| Renumbered Sequentially                                   | 52    |

| Deleted Figure 106                                        | 53    |

| Deleted Figure 107                                        | 54    |

| Deleted Figure 108                                        | 55    |

| Deleted Figure 109                                        | 56    |

| Deleted Figure 110                                        | 57    |

| Deleted Figure 111                                        | 58    |

| Deleted Figure 112                                        | 59    |

| Updated Outline Dimensions                                | 60    |

|                                                           |       |

| 3/2008—Rev. 0 to Rev. A                                   |       |

| Changes to Features                                       | 1     |

| Added Note 2                                              | 4     |

| Changes to Table 2                                        | 5     |

| Changes to Table 3                                        | 6     |

| Changes to Thermal Resistance Section                     | 7     |

| Inserted Table 6                                          | 8     |

| Changes to Pin 39 Description, Table 7                    | 9     |

| Changes to Pin 39 Description, Table 8                    | 10    |

| Changes to Pin 39 Description, Table 9                    |       |

| Changes to Theory of Operation Section                    |       |

| Changes to Table 10                                       | 23    |

| Changes to Table 13                                       | 26    |

| Changes to Table 14                                       | 27    |

| Changes to Interpolation Filter Architecture Section      | 33    |

| Replaced Sourcing the DAC Sample Clock Section            | 36    |

| Replaced Transmit Path Gain and Offset Correction Section | 40    |

| Replaced Input Data Ports Section                         |       |

| Replaced Device Synchronization Section                   |       |

| Deleted Figure 112 to Figure 117                          | 58    |

8/2007—Revision 0: Initial Version

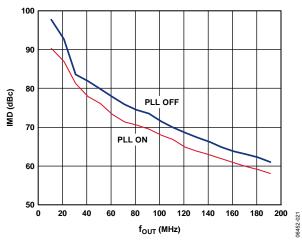

06452-001

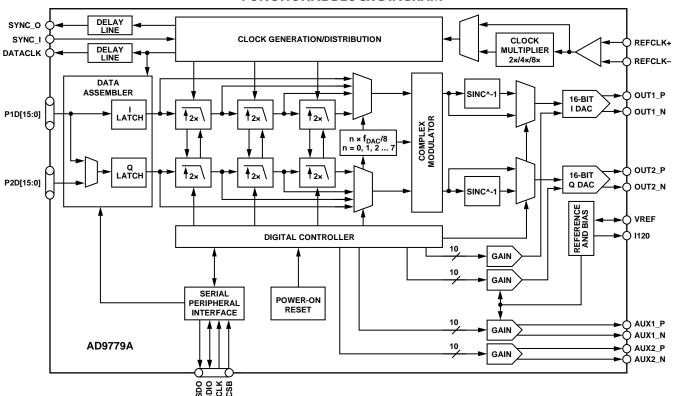

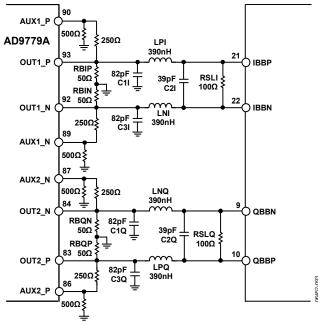

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. AD9779A Functional Block Diagram

# **SPECIFICATIONS**

#### **DC SPECIFICATIONS**

$T_{\text{MIN}} \text{ to } T_{\text{MAX}}, AVDD33 = 3.3 \text{ V}, DVDD33 = 3.3 \text{ V}, DVDD18 = 1.8 \text{ V}, CVDD18 = 1.8 \text{ V}, I_{\text{OUTFs}} = 20 \text{ mA}, \text{maximum sample rate, unless } T_{\text{MIN}} = 1.8 \text{ V}, T_{\text{OUTFs}} = 1.8 \text{ V}, T_{\text{$ otherwise noted.

Table 1.

|                                                                                                    |        | AD9776   | A      |        | AD9778   | Α      | P      | AD9779  | Α      |         |

|----------------------------------------------------------------------------------------------------|--------|----------|--------|--------|----------|--------|--------|---------|--------|---------|

| Parameter                                                                                          | Min    | Тур      | Max    | Min    | Тур      | Max    | Min    | Тур     | Max    | Unit    |

| RESOLUTION                                                                                         |        | 12       |        |        | 14       |        |        | 16      |        | Bits    |

| ACCURACY                                                                                           |        |          |        |        |          |        |        |         |        |         |

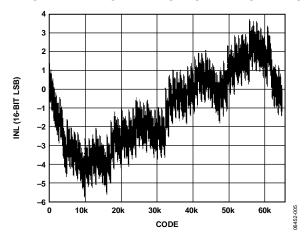

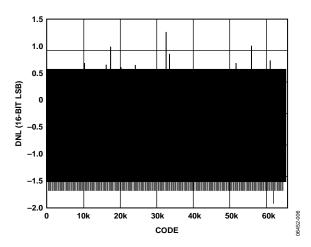

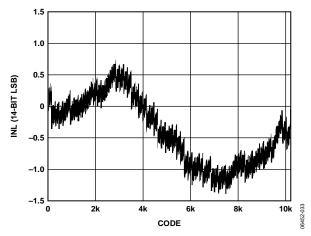

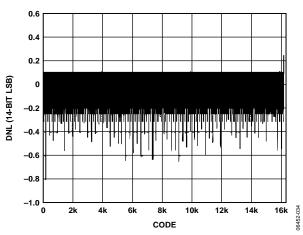

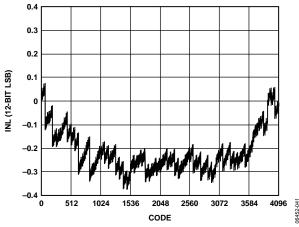

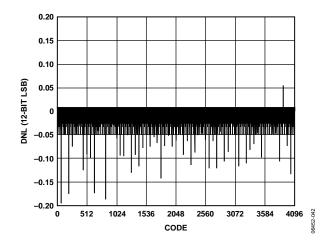

| Differential Nonlinearity (DNL)                                                                    |        | ±0.1     |        |        | ±0.65    |        |        | ±2.1    |        | LSB     |

| Integral Nonlinearity (INL)                                                                        |        | ±0.86    |        |        | ±1.5     |        |        | ±6.0    |        | LSB     |

| MAIN DAC OUTPUTS                                                                                   |        |          |        |        |          |        |        |         |        |         |

| Offset Error                                                                                       | -0.001 | 0        | +0.001 | -0.001 | 0        | +0.001 | -0.001 | 0       | +0.001 | % FSR   |

| Gain Error (with Internal Reference)                                                               |        | ±2       |        |        | ±2       |        |        | ±2      |        | % FSR   |

| Full-Scale Output Current <sup>1</sup>                                                             | 8.66   | 20.2     | 31.66  | 8.66   | 20.2     | 31.66  | 8.66   | 20.2    | 31.66  | mA      |

| Output Compliance Range                                                                            | -1.0   |          | +1.0   | -1.0   |          | +1.0   | -1.0   |         | +1.0   | V       |

| Output Resistance                                                                                  |        | 10       |        |        | 10       |        |        | 10      |        | ΜΩ      |

| Gain DAC Monotonicity                                                                              |        | Guarante | ed     |        | Guarante | ed     | G      | uarante | ed     |         |

| MAIN DAC TEMPERATURE DRIFT                                                                         |        |          |        |        |          |        |        |         |        |         |

| Offset                                                                                             |        | 0.04     |        |        | 0.04     |        |        | 0.04    |        | ppm/°C  |

| Gain                                                                                               |        | 100      |        |        | 100      |        |        | 100     |        | ppm/°C  |

| Reference Voltage                                                                                  |        | 30       |        |        | 30       |        |        | 30      |        | ppm/°C  |

| AUXILIARY DAC OUTPUTS                                                                              |        |          |        |        |          |        |        |         |        |         |

| Resolution                                                                                         |        | 10       |        |        | 10       |        |        | 10      |        | Bits    |

| Full-Scale Output Current1                                                                         | -1.998 |          | +1.998 | -1.998 |          | +1.998 | -1.998 |         | +1.998 | mA      |

| Output Compliance Range (Source)                                                                   | 0      |          | 1.6    | 0      |          | 1.6    | 0      |         | 1.6    | V       |

| Output Compliance Range (Sink)                                                                     | 0.8    |          | 1.6    | 0.8    |          | 1.6    | 0.8    |         | 1.6    | V       |

| Output Resistance                                                                                  |        | 1        |        |        | 1        |        |        | 1       |        | ΜΩ      |

| Auxiliary DAC Monotonicity                                                                         |        | Guarante | ed     |        | Guarante | ed     | G      | uarante | ed     |         |

| REFERENCE                                                                                          |        |          |        |        |          |        |        |         |        |         |

| Internal Reference Voltage                                                                         |        | 1.2      |        |        | 1.2      |        |        | 1.2     |        | V       |

| Output Resistance                                                                                  |        | 5        |        |        | 5        |        |        | 5       |        | kΩ      |

| ANALOG SUPPLY VOLTAGES                                                                             |        |          |        |        |          |        |        |         |        |         |

| AVDD33                                                                                             | 3.13   | 3.3      | 3.47   | 3.13   | 3.3      | 3.47   | 3.13   | 3.3     | 3.47   | V       |

| CVDD18                                                                                             | 1.70   | 1.8      | 2.05   | 1.70   | 1.8      | 2.05   | 1.70   | 1.8     | 2.05   | V       |

| DIGITAL SUPPLY VOLTAGES                                                                            |        |          |        |        |          |        |        |         |        |         |

| DVDD33                                                                                             | 3.13   | 3.3      | 3.47   | 3.13   | 3.3      | 3.47   | 3.13   | 3.3     | 3.47   | V       |

| DVDD18                                                                                             | 1.70   | 1.8      | 2.05   | 1.70   | 1.8      | 2.05   | 1.70   | 1.8     | 2.05   | V       |

| POWER CONSUMPTION <sup>2</sup>                                                                     |        |          |        |        |          |        |        |         |        |         |

| $1 \times Mode$ , $f_{DAC} = 100 MSPS$ , $IF = 1 MHz$                                              |        | 250      | 300    |        | 250      | 300    |        | 250     | 300    | mW      |

| $2 \times$ Mode, $f_{DAC} = 320$ MSPS, IF = 16 MHz, PLL Off                                        |        | 498      |        |        | 498      |        |        | 498     |        | mW      |

| $2 \times$ Mode, $f_{DAC} = 320$ MSPS, IF = 16 MHz, PLL On                                         |        | 588      |        |        | 588      |        |        | 588     |        | mW      |

| 4× Mode, f <sub>DAC</sub> /4 Modulation, f <sub>DAC</sub> = 500 MSPS,<br>IF = 137.5 MHz, Q DAC Off |        | 572      |        |        | 572      |        |        | 572     |        | mW      |

| $8 \times$ Mode, $f_{DAC}/4$ Modulation, $f_{DAC} = 1$ GSPS, IF = 262.5 MHz                        |        | 980      |        |        | 980      |        |        | 980     |        | mW      |

| Power-Down Mode                                                                                    |        | 2.5      | 9.8    |        | 2.5      | 9.8    |        | 2.5     | 9.8    | mW      |

| Power Supply Rejection Ratio, AVDD33                                                               | -0.3   |          | +0.3   | -0.3   |          | +0.3   | -0.3   |         | +0.3   | % FSR/V |

| OPERATING RANGE                                                                                    | -40    | +25      | +85    | -40    | +25      | +85    | -40    | +25     | +85    | °C      |

$<sup>^1</sup>$  Based on a 10  $k\Omega$  external resistor.  $^2$  See the Power Dissipation section for more details.

#### **DIGITAL SPECIFICATIONS**

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V,  $I_{\text{OUTFs}}$  = 20 mA, maximum sample rate, unless otherwise noted. LVDS driver and receiver are compliant to the IEEE-1596 reduced range link, unless otherwise noted.

Table 2.

| Parameter                                      | Conditions                                                                                               | Min   | Тур | Max  | Unit |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------|-----|------|------|

| CMOS INPUT LOGIC LEVEL                         |                                                                                                          |       |     |      |      |

| Input V <sub>IN</sub> Logic High               |                                                                                                          | 2.0   |     |      | V    |

| Input V <sub>IN</sub> Logic Low                |                                                                                                          |       |     | 0.8  | V    |

| Maximum Input Data Rate at Interpolation       |                                                                                                          |       |     |      |      |

| 1×                                             |                                                                                                          | 300   |     |      | MSPS |

| 2×                                             |                                                                                                          | 250   |     |      | MSPS |

| 4×                                             |                                                                                                          | 200   |     |      | MSPS |

| 8×                                             | DVDD18, CVDD18 = 1.8 V ± 5%                                                                              | 112.5 |     |      | MSPS |

|                                                | DVDD18, CVDD18 = 1.9 V ± 5%                                                                              | 125   |     |      | MSPS |

|                                                | DVDD18, CVDD18 = 2.0 V ± 2%                                                                              | 137.5 |     |      | MSPS |

| CMOS OUTPUT LOGIC LEVEL (DATACLK, PIN 37)1     |                                                                                                          |       |     |      |      |

| Output Vout Logic High                         |                                                                                                          | 2.4   |     |      | V    |

| Output V <sub>OUT</sub> Logic Low              |                                                                                                          |       |     | 0.4  | V    |

| DATACLK Output Duty Cycle                      | At 250 MHz, into 5 pF load                                                                               | 40    | 50  | 60   | %    |

| LVDS RECEIVER INPUTS (SYNC_I+, SYNC_I-)        | $SYNC_I + = V_{IA}, SYNC_I - = V_{IB}$                                                                   |       |     |      |      |

| Input Voltage Range, VIA or VIB                |                                                                                                          | 825   |     | 1575 | mV   |

| Input Differential Threshold, VIDTH            |                                                                                                          | -100  |     | +100 | mV   |

| Input Differential Hysteresis, VIDTHH – VIDTHL |                                                                                                          |       | 20  |      | mV   |

| Receiver Differential Input Impedance, RIN     |                                                                                                          | 80    |     | 120  | Ω    |

| LVDS Input Rate                                | Additional limits on f <sub>SYNC_1</sub> apply; see description of Register 0x05, Bits[3:1], in Table 14 |       |     | 250  | MSPS |

| Setup Time, SYNC_I to REFCLK                   |                                                                                                          | 0.4   |     |      | ns   |

| Hold Time, SYNC_I to REFCLK                    |                                                                                                          | 0.55  |     |      | ns   |

| LVDS DRIVER OUTPUTS (SYNC_O+, SYNC_O-)         | SYNC_O+ = $V_{OA}$ , SYNC_O- = $V_{OB}$ , 100 $\Omega$ termination                                       |       |     |      |      |

| Output Voltage High, VOA or VOB                |                                                                                                          |       |     | 1375 | mV   |

| Output Voltage Low, VOA or VOB                 |                                                                                                          | 1025  |     |      | mV   |

| Output Differential Voltage,  VoD              |                                                                                                          | 150   | 200 | 250  | mV   |

| Output Offset Voltage, Vos                     |                                                                                                          | 1150  |     | 1250 | mV   |

| Output Impedance, R <sub>0</sub>               | Single-ended                                                                                             | 80    | 100 | 120  | Ω    |

| DAC CLOCK INPUT (REFCLK+, REFCLK-)             |                                                                                                          |       |     |      |      |

| Differential Peak-to-Peak Voltage              |                                                                                                          | 400   | 800 | 2000 | mV   |

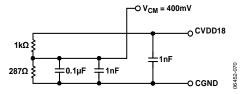

| Common-Mode Voltage                            |                                                                                                          | 300   | 400 | 500  | mV   |

| Maximum Clock Rate                             | DVDD18, CVDD18 = $1.8 \text{ V} \pm 5\%$ , PLL off                                                       | 900   |     |      | MHz  |

|                                                | DVDD18, CVDD18 = $1.9 \text{ V} \pm 5\%$ , PLL off                                                       | 1000  |     |      | MHz  |

|                                                | DVDD18, CVDD18 = 2.0 V ± 2%, PLL off                                                                     | 1100  |     |      | MHz  |

|                                                | DVDD18, CVDD18 = $2.0 \text{ V} \pm 2\%$ , PLL on                                                        | 250   |     |      | MHz  |

<sup>&</sup>lt;sup>1</sup> Specification is at a DATACLK frequency of 100 MHz into a 1 k $\Omega$  load, with maximum drive capability of 8 mA. At higher speeds or greater loads, best practice suggests using an external buffer for this signal.

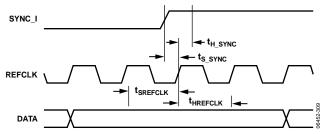

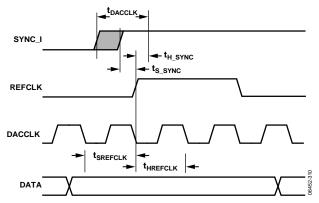

#### **DIGITAL INPUT DATA TIMING SPECIFICATIONS**

All modes, -40°C to +85°C.

Table 3.

| Parameter                                  | Conditions                 | Min   | Тур | Max  | Unit          |

|--------------------------------------------|----------------------------|-------|-----|------|---------------|

| INPUT DATA <sup>1</sup>                    |                            |       |     |      |               |

| Setup Time                                 | Input data to DATACLK      | 3.0   |     |      | ns            |

| Hold Time                                  | Input data to DATACLK      | -0.05 |     |      | ns            |

| Setup Time                                 | Input data to REFCLK       | -0.80 |     |      | ns            |

| Hold Time                                  | Input data to REFCLK       | 3.80  |     |      | ns            |

| LATENCY                                    |                            |       |     |      |               |

| 1× Interpolation                           | With or without modulation |       | 25  |      | DACCLK cycles |

| 2× Interpolation                           | With or without modulation |       | 70  |      | DACCLK cycles |

| 4× Interpolation                           | With or without modulation |       | 146 |      | DACCLK cycles |

| 8× Interpolation                           | With or without modulation |       | 297 |      | DACCLK cycles |

| Inverse Sync                               |                            |       | 18  |      | DACCLK cycles |

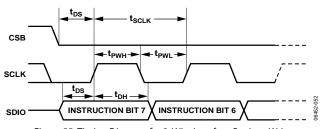

| 3-WIRE INTERFACE                           |                            |       |     |      |               |

| Maximum Clock Rate (SCLK)                  |                            | 40    |     |      | MHz           |

| Minimum Pulse Width High, t <sub>PWH</sub> |                            |       |     | 12.5 | ns            |

| Minimum Pulse Width Low, t <sub>PWL</sub>  |                            |       |     | 12.5 | ns            |

| Setup Time, t <sub>DS</sub>                | SDIO to SCLK               | 2.8   |     |      | ns            |

| Hold Time, t <sub>DH</sub>                 | SDIO to SCLK               | 0.0   |     |      | ns            |

| Setup Time, t <sub>DS</sub>                | CSB to SCLK                | 2.8   |     |      | ns            |

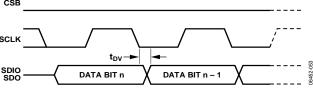

| Data Valid, t <sub>DV</sub>                | SDO to SCLK                | 2.0   |     |      | ns            |

| POWER-UP TIME <sup>2</sup>                 |                            |       | 260 |      | ms            |

| RESET                                      |                            |       |     |      |               |

| Minimum Pulse Width, High                  |                            |       |     | 2    | DACCLK cycles |

<sup>1</sup> Specified values are with PLL disabled. Timing vs. temperature and data valid keep out windows (that is, the minimum amount of time valid data must be presented to the device to ensure proper sampling) are delineated in Table 28.

Measured from CSB rising edge when Register 0x00, Bit 4, is written from 1 to 0 with the VREF decoupling capacitor equal to 0.1 μF.

#### **AC SPECIFICATIONS**

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V,  $I_{\text{OUTFs}}$  = 20 mA, maximum sample rate, unless otherwise noted.

Table 4.

|                                                                     |     | AD9776A |     |     | AD9778A |     |     | AD9779A |     |        |

|---------------------------------------------------------------------|-----|---------|-----|-----|---------|-----|-----|---------|-----|--------|

| Parameter                                                           | Min | Тур     | Max | Min | Тур     | Max | Min | Тур     | Max | Unit   |

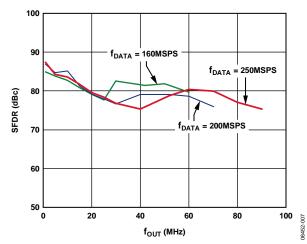

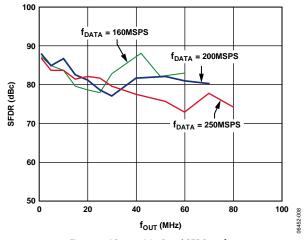

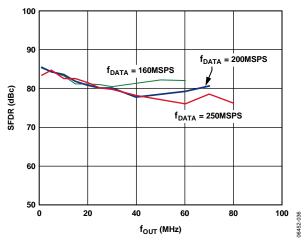

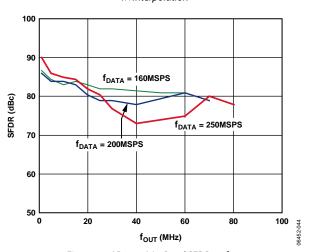

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)                                  |     |         |     |     |         |     |     |         |     |        |

| $f_{DAC} = 100 \text{ MSPS}, f_{OUT} = 20 \text{ MHz}$              |     | 82      |     |     | 82      |     |     | 82      |     | dBc    |

| $f_{DAC} = 200 \text{ MSPS}, f_{OUT} = 50 \text{ MHz}$              |     | 81      |     |     | 81      |     |     | 82      |     | dBc    |

| $f_{DAC} = 400 \text{ MSPS}, f_{OUT} = 70 \text{ MHz}$              |     | 80      |     |     | 80      |     |     | 80      |     | dBc    |

| $f_{DAC} = 800 \text{ MSPS}, f_{OUT} = 70 \text{ MHz}$              |     | 85      |     |     | 85      |     |     | 87      |     | dBc    |

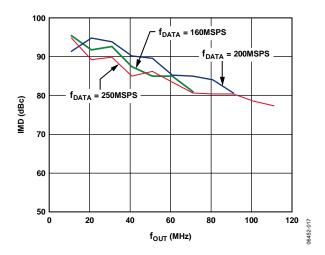

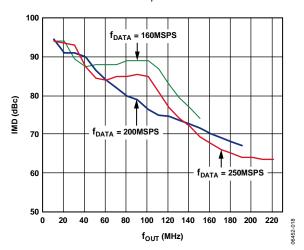

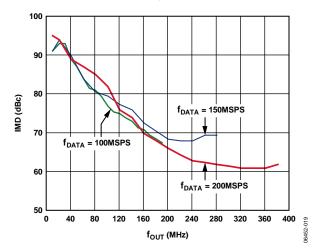

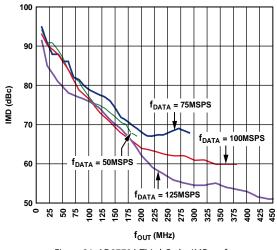

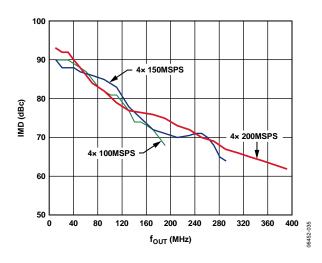

| TWO-TONE INTERMODULATION DISTORTION (IMD)                           |     |         |     |     |         |     |     |         |     |        |

| $f_{DAC} = 200 \text{ MSPS}, f_{OUT} = 50 \text{ MHz}$              |     | 87      |     |     | 87      |     |     | 91      |     | dBc    |

| $f_{DAC} = 400 \text{ MSPS}, f_{OUT} = 60 \text{ MHz}$              |     | 80      |     |     | 85      |     |     | 85      |     | dBc    |

| $f_{DAC} = 400 \text{ MSPS}, f_{OUT} = 80 \text{ MHz}$              |     | 75      |     |     | 81      |     |     | 81      |     | dBc    |

| $f_{DAC} = 800 \text{ MSPS}, f_{OUT} = 100 \text{ MHz}$             |     | 75      |     |     | 80      |     |     | 81      |     | dBc    |

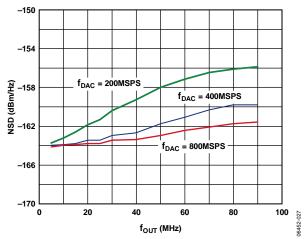

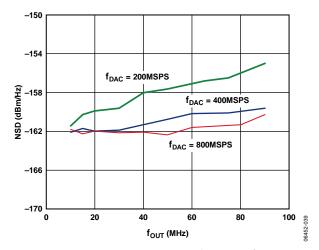

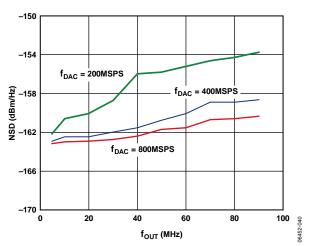

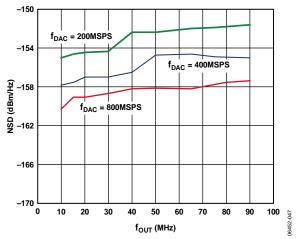

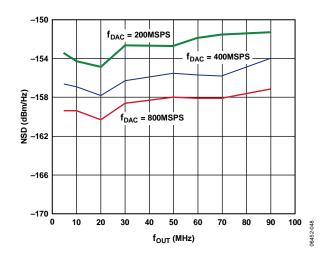

| NOISE SPECTRAL DENSITY (NSD), EIGHT-TONE, 500 kHz<br>TONE SPACING   |     |         |     |     |         |     |     |         |     |        |

| $f_{DAC} = 200 \text{ MSPS}, f_{OUT} = 80 \text{ MHz}$              |     | -152    |     |     | -155    |     |     | -158    |     | dBm/Hz |

| $f_{DAC} = 400 \text{ MSPS}, f_{OUT} = 80 \text{ MHz}$              |     | -155    |     |     | -159    |     |     | -160    |     | dBm/Hz |

| $f_{DAC} = 800 \text{ MSPS}, f_{OUT} = 80 \text{ MHz}$              |     | -157.5  |     |     | -160    |     |     | -161    |     | dBm/Hz |

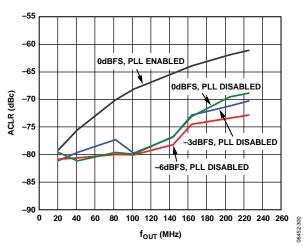

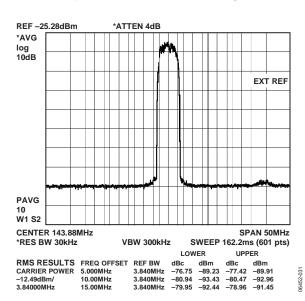

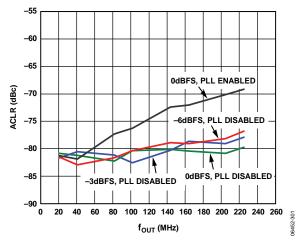

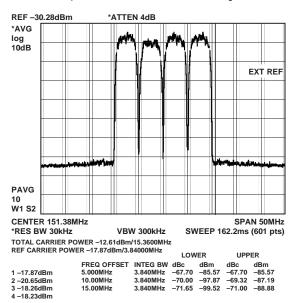

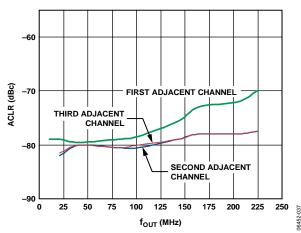

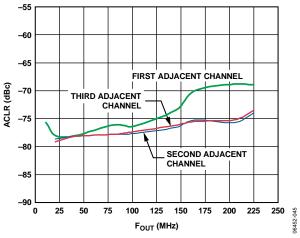

| W-CDMA ADJACENT CHANNEL LEAKAGE RATIO (ACLR),<br>SINGLE CARRIER     |     |         |     |     |         |     |     |         |     |        |

| $f_{DAC} = 491.52 \text{ MSPS}, f_{OUT} = 100 \text{ MHz}$          |     | 76      |     |     | 78      |     |     | 79      |     | dBc    |

| $f_{DAC} = 491.52 \text{ MSPS, } f_{OUT} = 200 \text{ MHz}$         |     | 69      |     |     | 73      |     |     | 74      |     | dBc    |

| W-CDMA SECOND ADJACENT CHANNEL LEAKAGE RATIO (ACLR), SINGLE CARRIER |     |         |     |     |         |     |     |         |     |        |

| $f_{DAC} = 491.52 \text{ MSPS, } f_{OUT} = 100 \text{ MHz}$         |     | 77.5    |     |     | 80      |     |     | 81      |     | dBc    |

| $f_{DAC} = 491.52 \text{ MSPS, } f_{OUT} = 200 \text{ MHz}$         |     | 76      |     |     | 78      |     |     | 78      |     | dBc    |

#### **ABSOLUTE MAXIMUM RATINGS**

Table 5.

| Table 3.                                                                                |                     |                             |

|-----------------------------------------------------------------------------------------|---------------------|-----------------------------|

| Parameter                                                                               | With Respect To     | Rating                      |

| AVDD33, DVDD33                                                                          | AGND, DGND,<br>CGND | -0.3 V to +3.6 V            |

| DVDD18, CVDD18                                                                          | AGND, DGND,<br>CGND | -0.3 V to +2.1 V            |

| AGND                                                                                    | DGND, CGND          | -0.3 V to +0.3 V            |

| DGND                                                                                    | AGND, CGND          | -0.3 V to +0.3 V            |

| CGND                                                                                    | AGND, DGND          | -0.3 V to +0.3 V            |

| I120, VREF, IPTAT                                                                       | AGND                | -0.3 V to<br>AVDD33 + 0.3 V |

| OUT1_P, OUT1_N,<br>OUT2_P, OUT2_N,<br>AUX1_P, AUX1_N,<br>AUX2_P, AUX2_N                 | AGND                | -1.0 V to<br>AVDD33 + 0.3 V |

| P1D[15:0], P2D[15:0]                                                                    | DGND                | -0.3 V to<br>DVDD33 + 0.3 V |

| DATACLK, TXENABLE                                                                       | DGND                | -0.3 V to<br>DVDD33 + 0.3 V |

| REFCLK+, REFCLK-                                                                        | CGND                | -0.3 V to<br>CVDD18 + 0.3 V |

| RESET, IRQ, PLL_LOCK,<br>SYNC_O+, SYNC_O-,<br>SYNC_I+, SYNC_I-,<br>CSB, SCLK, SDIO, SDO | DGND                | -0.3 V to<br>DVDD33 + 0.3 V |

| Junction Temperature                                                                    |                     | +125°C                      |

| Storage Temperature<br>Range                                                            |                     | −65°C to +150°C             |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

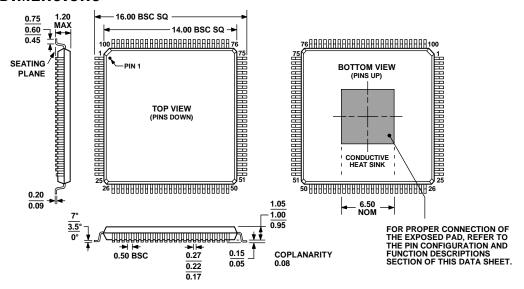

#### THERMAL RESISTANCE

For optimal thermal performance, the exposed paddle (EPAD) should be soldered to the ground plane for the 100-lead, thermally enhanced TQFP package.

Typical  $\theta_{JA}$  and  $\theta_{JC}$  are specified for a 4-layer board in still air. Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$ .

**Table 6. Thermal Resistance**

| Package Type      | θја  | $\theta_{JB}$ | θ <sub>JC</sub> | Unit |

|-------------------|------|---------------|-----------------|------|

| 100-Lead TQFP     |      |               |                 |      |

| EPAD Soldered     | 19.1 | 12.4          | 7.1             | °C/W |

| EPAD Not Soldered | 27.4 |               |                 | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

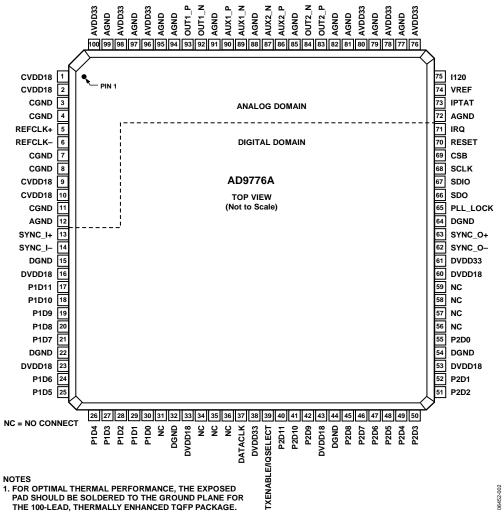

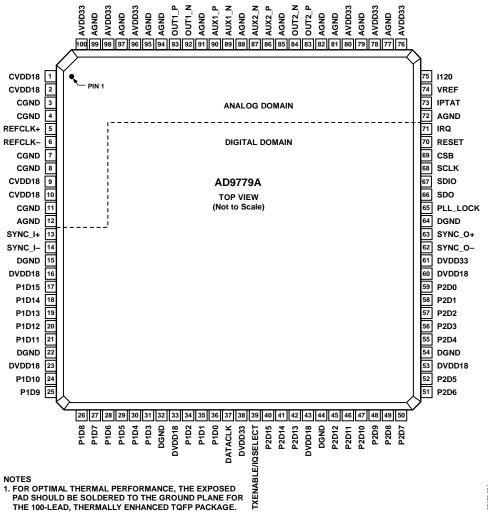

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. AD9776A Pin Configuration

Table 7. AD9776A Pin Function Descriptions

|     | / . AD3//UA | Fill Function Descriptions          |          |          | Γ                            |

|-----|-------------|-------------------------------------|----------|----------|------------------------------|

| Pin |             |                                     | Pin      |          |                              |

| No. | Mnemonic    | Description                         | No.      | Mnemonic | Description                  |

| 1   | CVDD18      | 1.8 V Clock Supply.                 | 18       | P1D10    | Port 1, Data Input D10.      |

| 2   | CVDD18      | 1.8 V Clock Supply.                 | 19       | P1D9     | Port 1, Data Input D9.       |

| 3   | CGND        | Clock Ground.                       | 20       | P1D8     | Port 1, Data Input D8.       |

| 4   | CGND        | Clock Ground.                       | 21       | P1D7     | Port 1, Data Input D7.       |

| 5   | REFCLK+     | Differential Clock Input.           | 22       | DGND     | Digital Ground.              |

| 6   | REFCLK-     | Differential Clock Input.           | 23       | DVDD18   | 1.8 V Digital Supply.        |

| 7   | CGND        | Clock Ground.                       | 24       | P1D6     | Port 1, Data Input D6.       |

| 8   | CGND        | Clock Ground.                       | 25       | P1D5     | Port 1, Data Input D5.       |

| 9   | CVDD18      | 1.8 V Clock Supply.                 | 26       | P1D4     | Port 1, Data Input D4.       |

| 10  | CVDD18      | 1.8 V Clock Supply.                 | 27       | P1D3     | Port 1, Data Input D3.       |

| 11  | CGND        | Clock Ground.                       | 28       | P1D2     | Port 1, Data Input D2.       |

| 12  | AGND        | Analog Ground.                      | 29       | P1D1     | Port 1, Data Input D1.       |

| 13  | SYNC_I+     | Differential Synchronization Input. | 30       | P1D0     | Port 1, Data Input D0 (LSB). |

| 14  | SYNC_I-     | Differential Synchronization Input. | 31       | NC       | No Connect.                  |

| 15  | DGND        | Digital Ground.                     | 32       | DGND     | Digital Ground.              |

| 16  | DVDD18      | 1.8 V Digital Supply.               | 33       | DVDD18   | 1.8 V Digital Supply.        |

| 17  | P1D11       | Port 1, Data Input D11 (MSB).       | 34       | NC       | No Connect.                  |

|     |             | Rev C Page                          | 10 of 55 |          |                              |

Rev. C | Page 10 of 55

RESET

70

# AD9776A/AD9778A/AD9779A

|            | Ī                     |                                                                            |

|------------|-----------------------|----------------------------------------------------------------------------|

| Pin<br>No. | Mnemonic              | Docavintion                                                                |

|            | NC                    | Description No Compact                                                     |

| 35         |                       | No Connect.                                                                |

| 36         | NC                    | No Connect.                                                                |

| 37         | DATACLK               | Data Clock Output.                                                         |

| 38         | DVDD33                | 3.3 V Digital Supply.                                                      |

| 39         | TXENABLE/<br>IQSELECT | Transmit Enable. In single port mode, this pin also functions as IQSELECT. |

| 40         | P2D11                 | Port 2, Data Input D11 (MSB).                                              |

| 41         | P2D10                 | Port 2, Data Input D10.                                                    |

| 42         | P2D9                  | Port 2, Data Input D9.                                                     |

| 43         | DVDD18                | 1.8 V Digital Supply.                                                      |

| 44         | DGND                  | Digital Ground.                                                            |

| 45         | P2D8                  | Port 2, Data Input D8.                                                     |

| 46         | P2D7                  | Port 2, Data Input D7.                                                     |

| 47         | P2D6                  | Port 2, Data Input D6.                                                     |

| 48         | P2D5                  | Port 2, Data Input D5.                                                     |

| 49         | P2D4                  | Port 2, Data Input D4.                                                     |

| 50         | P2D3                  | Port 2, Data Input D3.                                                     |

| 51         | P2D2                  | Port 2, Data Input D2.                                                     |

| 52         | P2D1                  | Port 2, Data Input D1.                                                     |

| 53         | DVDD18                | 1.8 V Digital Supply.                                                      |

| 54         | DGND                  | Digital Ground.                                                            |

| 55         | P2D0                  | Port 2, Data Input D0 (LSB).                                               |

| 56         | NC                    | No Connect.                                                                |

| 57         | NC                    | No Connect.                                                                |

| 58         | NC                    | No Connect.                                                                |

| 59         | NC                    | No Connect.                                                                |

| 60         | DVDD18                | 1.8 V Digital Supply.                                                      |

| 61         | DVDD33                | 3.3 V Digital Supply.                                                      |

| 62         | SYNC_O-               | Differential Synchronization Output.                                       |

| 63         | SYNC_O+               | Differential Synchronization Output.                                       |

| 64         | DGND                  | Digital Ground.                                                            |

| 65         | PLL_LOCK              | PLL Lock Indicator.                                                        |

| 66         | SDO                   | 3-Wire Interface Port Data Output.                                         |

| 67         | SDIO                  | 3-Wire Interface Port Data Input/Output.                                   |

| 68         | SCLK                  | 3-Wire Interface Port Clock.                                               |

| 69         | CSB                   | 3-Wire Interface Port Chip Select Bar.                                     |

|            | 1                     | <u>'</u>                                                                   |

Reset, Active High.

| Pin |          | <b>.</b>                                                                  |

|-----|----------|---------------------------------------------------------------------------|

| No. | Mnemonic | Description                                                               |

| 71  | IRQ      | Interrupt Request.                                                        |

| 72  | AGND     | Analog Ground.                                                            |

| 73  | IPTAT    | Factory Test Pin. Output current is                                       |

|     |          | proportional to absolute temperature,<br>approximately 14 μA at 25°C with |

|     |          | approximately 14 µA at 25 € with approximately 20 nA/°C slope. This pin   |

|     |          | should remain floating.                                                   |

| 74  | VREF     | Voltage Reference Output.                                                 |

| 75  | I120     | 120 μA Reference Current.                                                 |

| 76  | AVDD33   | 3.3 V Analog Supply.                                                      |

| 77  | AGND     | Analog Ground.                                                            |

| 78  | AVDD33   | 3.3 V Analog Supply.                                                      |

| 79  | AGND     | Analog Ground.                                                            |

| 80  | AVDD33   | 3.3 V Analog Supply.                                                      |

| 81  | AGND     | Analog Ground.                                                            |

| 82  | AGND     | Analog Ground.                                                            |

| 83  | OUT2_P   | Differential DAC Current Output, Channel 2.                               |

| 84  | OUT2_N   | Differential DAC Current Output, Channel 2.                               |

| 85  | AGND     | Analog Ground.                                                            |

| 86  | AUX2_P   | Auxiliary DAC Current Output, Channel 2.                                  |

| 87  | AUX2_N   | Auxiliary DAC Current Output, Channel 2.                                  |

| 88  | AGND     | Analog Ground.                                                            |

| 89  | AUX1_N   | Auxiliary DAC Current Output, Channel 1.                                  |

| 90  | AUX1_P   | Auxiliary DAC Current Output, Channel 1.                                  |

| 91  | AGND     | Analog Ground.                                                            |

| 92  | OUT1_N   | Differential DAC Current Output, Channel 1.                               |

| 93  | OUT1_P   | Differential DAC Current Output, Channel 1.                               |

| 94  | AGND     | Analog Ground.                                                            |

| 95  | AGND     | Analog Ground.                                                            |

| 96  | AVDD33   | 3.3 V Analog Supply.                                                      |

| 97  | AGND     | Analog Ground.                                                            |

| 98  | AVDD33   | 3.3 V Analog Supply.                                                      |

| 99  | AGND     | Analog Ground.                                                            |

| 100 | AVDD33   | 3.3 V Analog Supply.                                                      |

|     |          |                                                                           |

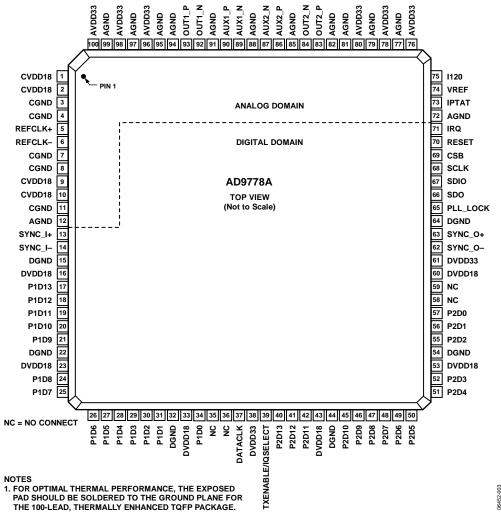

Figure 4. AD9778A Pin Configuration

**Table 8. AD9778A Pin Function Descriptions**

| 1 4010 | 00.112000001 | 1 III Tunction Descriptions         |     |          |                              |

|--------|--------------|-------------------------------------|-----|----------|------------------------------|

| Pin    |              |                                     | Pin |          |                              |

| No.    | Mnemonic     | Description                         | No. | Mnemonic | Description                  |

| 1      | CVDD18       | 1.8 V Clock Supply.                 | 19  | P1D11    | Port 1, Data Input D11.      |

| 2      | CVDD18       | 1.8 V Clock Supply.                 | 20  | P1D10    | Port 1, Data Input D10.      |

| 3      | CGND         | Clock Ground.                       | 21  | P1D9     | Port 1, Data Input D9.       |

| 4      | CGND         | Clock Common.                       | 22  | DGND     | Digital Ground.              |

| 5      | REFCLK+      | Differential Clock Input.           | 23  | DVDD18   | 1.8 V Digital Supply.        |

| 6      | REFCLK-      | Differential Clock Input.           | 24  | P1D8     | Port 1, Data Input D8.       |

| 7      | CGND         | Clock Ground.                       | 25  | P1D7     | Port 1, Data Input D7.       |

| 8      | CGND         | Clock Ground.                       | 26  | P1D6     | Port 1, Data Input D6.       |

| 9      | CVDD18       | 1.8 V Clock Supply.                 | 27  | P1D5     | Port 1, Data Input D5.       |

| 10     | CVDD18       | 1.8 V Clock Supply.                 | 28  | P1D4     | Port 1, Data Input D4.       |

| 11     | CGND         | Clock Ground.                       | 29  | P1D3     | Port 1, Data Input D3.       |

| 12     | AGND         | Analog Ground.                      | 30  | P1D2     | Port 1, Data Input D2.       |

| 13     | SYNC_I+      | Differential Synchronization Input. | 31  | P1D1     | Port 1, Data Input D1.       |

| 14     | SYNC_I-      | Differential Synchronization Input. | 32  | DGND     | Digital Ground.              |

| 15     | DGND         | Digital Ground.                     | 33  | DVDD18   | 1.8 V Digital Supply.        |

| 16     | DVDD18       | 1.8 V Digital Supply.               | 34  | P1D0     | Port 1, Data Input D0 (LSB). |

| 17     | P1D13        | Port 1, Data Input D13 (MSB).       | 35  | NC       | No Connect.                  |

| 18     | P1D12        | Port 1, Data Input D12.             | 36  | NC       | No Connect.                  |

| Pin<br>No. | Mnemonic  | Description                                |

|------------|-----------|--------------------------------------------|

| 37         | DATACLK   | Data Clock Output.                         |

| 38         | DVDD33    | 3.3 V Digital Supply.                      |

| 39         | TXENABLE/ | Transmit Enable. In single port mode, this |

|            | IQSELECT  | pin also functions as IQSELECT.            |

| 40         | P2D13     | Port 2, Data Input D13 (MSB).              |

| 41         | P2D12     | Port 2, Data Input D12.                    |

| 42         | P2D11     | Port 2, Data Input D11.                    |

| 43         | DVDD18    | 1.8 V Digital Supply.                      |

| 44         | DGND      | Digital Ground.                            |

| 45         | P2D10     | Port 2, Data Input D10.                    |

| 46         | P2D9      | Port 2, Data Input D9.                     |

| 47         | P2D8      | Port 2, Data Input D8.                     |

| 48         | P2D7      | Port 2, Data Input D7.                     |

| 49         | P2D6      | Port 2, Data Input D6.                     |

| 50         | P2D5      | Port 2, Data Input D5.                     |

| 51         | P2D4      | Port 2, Data Input D4.                     |

| 52         | P2D3      | Port 2, Data Input D3.                     |

| 53         | DVDD18    | 1.8 V Digital Supply.                      |

| 54         | DGND      | Digital Ground.                            |

| 55         | P2D2      | Port 2, Data Input D2.                     |

| 56         | P2D1      | Port 2, Data Input D1.                     |

| 57         | P2D0      | Port 2, Data Input D0 (LSB).               |

| 58         | NC        | No Connect.                                |

| 59         | NC        | No Connect.                                |

| 60         | DVDD18    | 1.8 V Digital Supply.                      |

| 61         | DVDD33    | 3.3 V Digital Supply.                      |

| 62         | SYNC_O-   | Differential Synchronization Output.       |

| 63         | SYNC_O+   | Differential Synchronization Output.       |

| 64         | DGND      | Digital Ground.                            |

| 65         | PLL_LOCK  | PLL Lock Indicator.                        |

| 66         | SDO       | 3-Wire Interface Port Data Output.         |

| 67         | SDIO      | 3-Wire Interface Port Data Input/Output.   |

| 68         | SCLK      | 3-Wire Interface Port Clock.               |

| 69         | CSB       | 3-Wire Interface Port Chip Select Bar.     |

| 70         | RESET     | Reset, Active High.                        |

| 71         | IRQ       | Interrupt Request.                         |

| 72 AGND Analog Ground. 73 IPTAT Factory Test Pin. Output current is proportional to absolute temperature, approximately 14 μA at 25°C with approximately 20 nA/°C slope. This pin should remain floating. 74 VREF Voltage Reference Output. 75 I120 120 μA Reference Current. 76 AVDD33 3.3 V Analog Supply. 77 AGND Analog Ground. 78 AVDD33 3.3 V Analog Supply. 79 AGND Analog Ground. 80 AVDD33 3.3 V Analog Supply. 81 AGND Analog Ground. 82 AGND Analog Ground. 83 OUT2_P Differential DAC Current Output, Channel 2. 84 OUT2_N Differential DAC Current Output, Channel 2. 85 AGND Analog Ground. 86 AUX2_P Auxiliary DAC Current Output, Channel 2. 87 AUX2_N Auxiliary DAC Current Output, Channel 2. 88 AGND Analog Ground. 89 AUX1_N Auxiliary DAC Current Output, Channel 1. 90 AUX1_P Auxiliary DAC Current Output, Channel 1. 91 AGND Analog Ground. 92 OUT1_N Differential DAC Current Output, Channel 1. 93 OUT1_P Differential DAC Current Output, Channel 1. 94 AGND Analog Ground. 95 AGND Analog Ground. 96 AVDD33 3.3 V Analog Supply. 97 AGND Analog Ground. 98 AVDD33 3.3 V Analog Supply. 99 AGND Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin<br>No. | Mnemonic | Description                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| proportional to absolute temperature, approximately 14 μA at 25°C with approximately 20 nA/°C slope. This pin should remain floating.  VREF Voltage Reference Output.  1120 120 μA Reference Current.  AVDD33 3.3 V Analog Supply.  AGND Analog Ground.  AVDD33 3.3 V Analog Supply.  AGND Analog Ground.  AVDD33 3.3 V Analog Supply.  AGND Analog Ground.  AUX2_P Auxiliary DAC Current Output, Channel 2.  AGND Analog Ground.  AUX2_N Auxiliary DAC Current Output, Channel 2.  AGND Analog Ground.  AUX1_N Auxiliary DAC Current Output, Channel 1.  AUX1_P Auxiliary DAC Current Output, Channel 1.  AUX1_P Auxiliary DAC Current Output, Channel 1.  AUX1_P Auxiliary DAC Current Output, Channel 1.  Auxiliary DAC Current Output, Channel 3.  Auxiliary DAC Cu | 72         | AGND     |                                                                                                                                                   |

| 120 μA Reference Current.  AVDD33 3.3 V Analog Supply.  AGND Analog Ground.  AGND Differential DAC Current Output, Channel 2.  AGND Analog Ground.  AUX2_P Auxiliary DAC Current Output, Channel 2.  AGND Analog Ground.  AUX1_N Auxiliary DAC Current Output, Channel 2.  AUX1_N Auxiliary DAC Current Output, Channel 1.  AUX1_P Auxiliary DAC Current Output, Channel 1.  AGND Analog Ground.  AUX1_P Differential DAC Current Output, Channel 1.  AGND Analog Ground.  Differential DAC Current Output, Channel 1.  AGND Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73         | IPTAT    | Factory Test Pin. Output current is proportional to absolute temperature, approximately 14 µA at 25°C with approximately 20 nA/°C slope. This pin |

| 76AVDD333.3 V Analog Supply.77AGNDAnalog Ground.78AVDD333.3 V Analog Supply.79AGNDAnalog Ground.80AVDD333.3 V Analog Supply.81AGNDAnalog Ground.82AGNDAnalog Ground.83OUT2_PDifferential DAC Current Output, Channel 2.84OUT2_NDifferential DAC Current Output, Channel 2.85AGNDAnalog Ground.86AUX2_PAuxiliary DAC Current Output, Channel 2.87AUX2_NAuxiliary DAC Current Output, Channel 2.88AGNDAnalog Ground.89AUX1_NAuxiliary DAC Current Output, Channel 1.90AUX1_PAuxiliary DAC Current Output, Channel 1.91AGNDAnalog Ground.92OUT1_NDifferential DAC Current Output, Channel 1.93OUT1_PDifferential DAC Current Output, Channel 1.94AGNDAnalog Ground.95AGNDAnalog Ground.96AVDD333.3 V Analog Supply.97AGNDAnalog Ground.98AVDD333.3 V Analog Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74         | VREF     | Voltage Reference Output.                                                                                                                         |

| AGND Analog Ground.  AGND Analog Supply.  AGND Analog Ground.  AGND Analog Supply.  AGND Analog Supply.  AGND Analog Ground.  AGND Differential DAC Current Output, Channel 2.  AGND Analog Ground.  AUX2_P Auxiliary DAC Current Output, Channel 2.  AGND Analog Ground.  AUX1_N Auxiliary DAC Current Output, Channel 2.  AGND Analog Ground.  AUX1_P Auxiliary DAC Current Output, Channel 1.  AGND Analog Ground.  AUX1_P Auxiliary DAC Current Output, Channel 1.  AGND Analog Ground.  Differential DAC Current Output, Channel 1.  AGND Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75         | l120     | 120 μA Reference Current.                                                                                                                         |

| 78AVDD333.3 V Analog Supply.79AGNDAnalog Ground.80AVDD333.3 V Analog Supply.81AGNDAnalog Ground.82AGNDAnalog Ground.83OUT2_PDifferential DAC Current Output, Channel 2.84OUT2_NDifferential DAC Current Output, Channel 2.85AGNDAnalog Ground.86AUX2_PAuxiliary DAC Current Output, Channel 2.87AUX2_NAuxiliary DAC Current Output, Channel 2.88AGNDAnalog Ground.89AUX1_NAuxiliary DAC Current Output, Channel 1.90AUX1_PAuxiliary DAC Current Output, Channel 1.91AGNDAnalog Ground.92OUT1_NDifferential DAC Current Output, Channel 1.93OUT1_PDifferential DAC Current Output, Channel 1.94AGNDAnalog Ground.95AGNDAnalog Ground.96AVDD333.3 V Analog Supply.97AGNDAnalog Ground.98AVDD333.3 V Analog Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76         | AVDD33   | 3.3 V Analog Supply.                                                                                                                              |

| AGND Analog Ground.  AVDD33 3.3 V Analog Supply.  AGND Analog Ground.  AGND Analog Ground.  AGND Analog Ground.  OUT2_P Differential DAC Current Output, Channel 2.  AGND Analog Ground.  AGND Analog Ground.  AUX2_P Auxiliary DAC Current Output, Channel 2.  AGND Analog Ground.  AUX2_N Auxiliary DAC Current Output, Channel 2.  AGND Analog Ground.  AUX1_N Auxiliary DAC Current Output, Channel 1.  AGND Analog Ground.  AUX1_P Auxiliary DAC Current Output, Channel 1.  AGND Analog Ground.  OUT1_N Differential DAC Current Output, Channel 1.  AGND Analog Ground.  OUT1_P Differential DAC Current Output, Channel 1.  AGND Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77         | AGND     | Analog Ground.                                                                                                                                    |

| 3.3 V Analog Supply. AGND Analog Ground. CUT2_P Differential DAC Current Output, Channel 2. AGND Analog Ground. CUT2_N Differential DAC Current Output, Channel 2. AGND Analog Ground. AUX2_P Auxiliary DAC Current Output, Channel 2. AGND Analog Ground. Auxiliary DAC Current Output, Channel 2. AUX2_N Auxiliary DAC Current Output, Channel 2. AGND Analog Ground. AUX1_N Auxiliary DAC Current Output, Channel 1. AGND Analog Ground. CUT1_N Differential DAC Current Output, Channel 1. CUT1_P Differential DAC Current Output, Channel 1. AGND Analog Ground. ANDD33 3.3 V Analog Supply. AGND Analog Ground. ANDD33 3.3 V Analog Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 78         | AVDD33   | 3.3 V Analog Supply.                                                                                                                              |

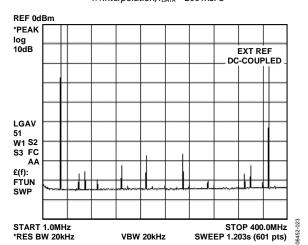

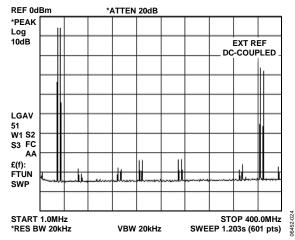

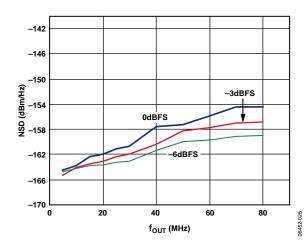

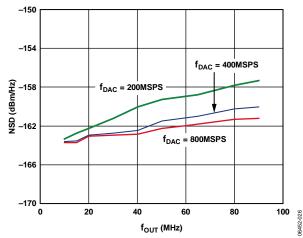

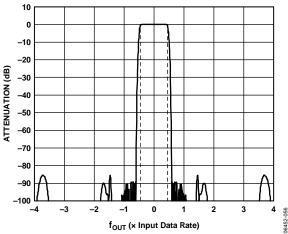

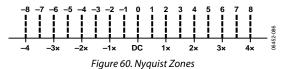

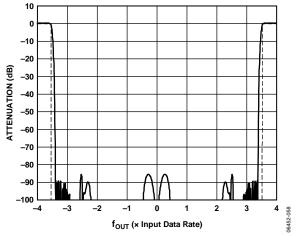

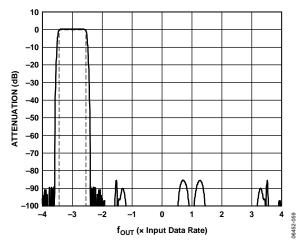

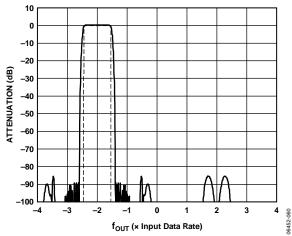

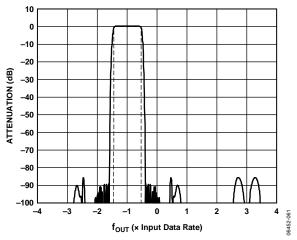

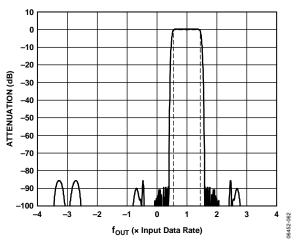

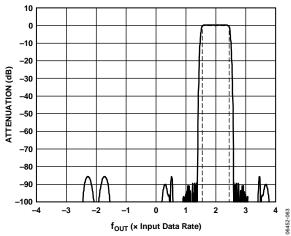

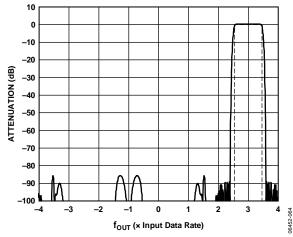

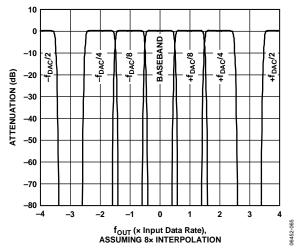

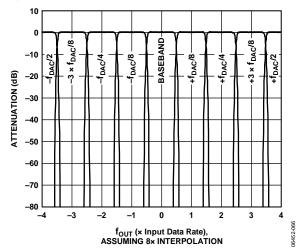

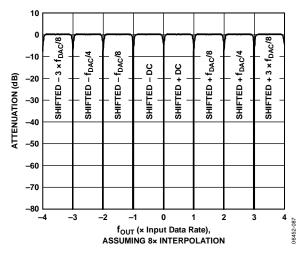

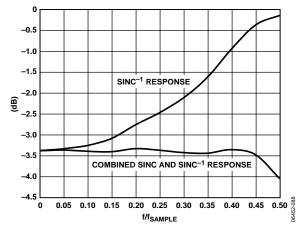

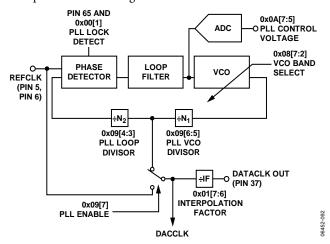

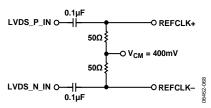

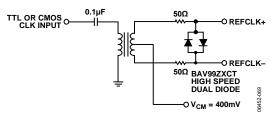

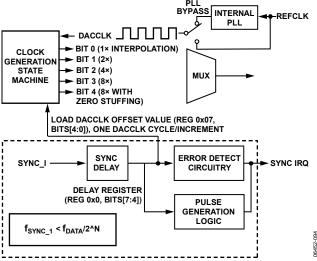

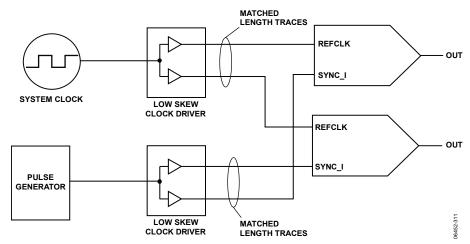

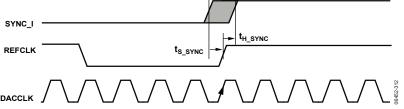

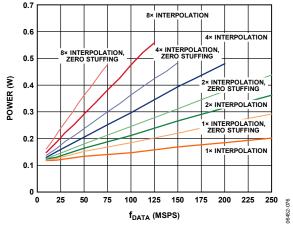

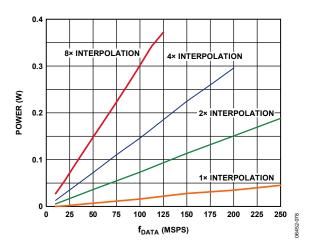

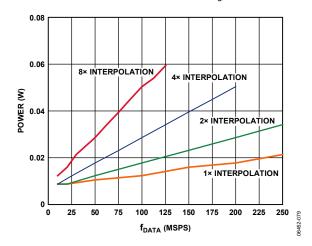

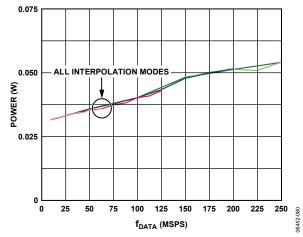

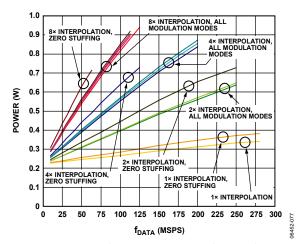

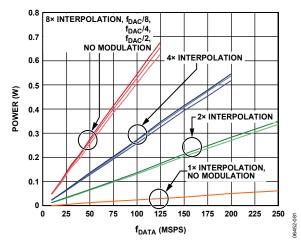

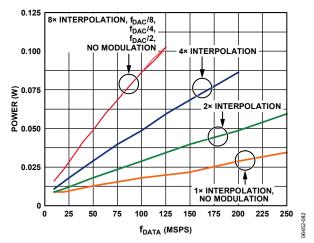

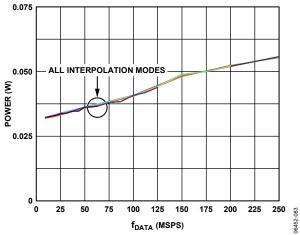

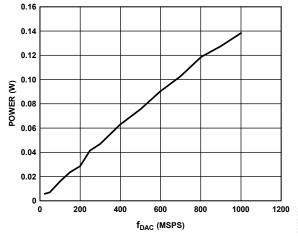

| AGND Analog Ground.  AGND Analog Ground.  AGND Analog Ground.  Auxiliary DAC Current Output, Channel 2.  AUX2_N Auxiliary DAC Current Output, Channel 2.  AGND Analog Ground.  Auxiliary DAC Current Output, Channel 1.  AUX1_N Auxiliary DAC Current Output, Channel 1.  AUX1_P Auxiliary DAC Current Output, Channel 1.  AGND Analog Ground.  OUT1_N Differential DAC Current Output, Channel 1.  AGND Analog Ground.  ANDD33 3.3 V Analog Supply.  AGND Analog Ground.  ANDD33 3.3 V Analog Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79         | AGND     | Analog Ground.                                                                                                                                    |