# FS6500, FS4500

# Safety Power System Basis Chip with CAN FD and LIN Transceivers

Rev. 1.0 — 14 December 2017

Short data sheet: advance information

### 1 General description

The FS6500/FS4500 SMARTMOS devices are a multi-output, power supply, integrated circuit, including CAN Flexible Data (FD) and/or LIN transceivers, dedicated to the automotive market.

Multiple switching and linear voltage regulators, including low-power mode (32  $\mu$ A) are available with various wake-up capabilities. An advanced power management scheme is implemented to maintain high efficiency over a wide range of input voltages (down to 2.7 V) and output current ranges (up to 2.2 A).

The FS6500/FS4500 includes configurable fail-safe/fail silent safety behavior and features, with two fail-safe outputs, becoming a full part of a safety oriented system partitioning, to reach a high integrity safety level (up to ASIL D).

The built-in CAN FD interface fulfills the ISO 11898-2 and -5 standards. The LIN interface fulfills LIN protocol specifications 2.0, 2.1, 2.2, and SAEJ2602-2.

#### 2 Features

- Battery voltage sensing and MUX output pin

- Highly flexible SMPS pre-regulator, allowing two topologies: non-inverting buck-boost and standard buck

- Family of devices to supply MCU core from 1.0 V to 5.0 V, with SMPS (0.8 A, 1.5 A or 2.2 A) or LDO (0.5 A)

- 36 V maximum input operating voltage

- Linear voltage regulator dedicated to auxiliary functions, or to sensor supply (V<sub>CCA</sub> tracker or independent), 5.0 V or 3.3 V

- Linear voltage regulator dedicated to MCU A/D reference voltage or I/Os supply ( $V_{CCA}$ ), 5.0 V or 3.3 V

- 3.3 V keep alive memory supply available in low-power mode

- Long duration timer, counting up to 6 months with 1.0 s resolution

- Multiple wake-up sources in low-power mode: CAN, LIN, IOs, LDT

- Five configurable I/Os

## 3 Applications

- Drive train electrification (BMS, hybrid EV and HEV, inverter, DCDC, alterno starter)

- Drive train chassis and safety (active suspension, steering, safety domain gateway)

- Power train (EMS, TCU, gear box)

- ADAS (LDW, Radar, sensor fusion safety area)

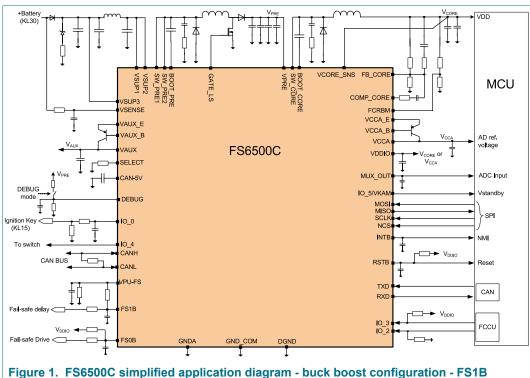

#### Simplified application diagram 4

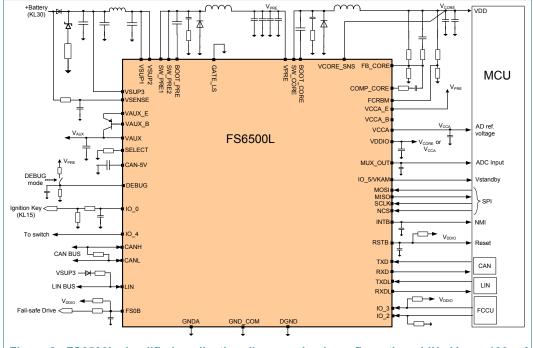

Figure 2. FS6500L simplified application diagram - buck configuration - LIN - V<sub>CCA</sub> =100 mA

## 5 Ordering information

#### 5.1 Part numbers definition

# MC33FS $\underline{c}$ 5 $\underline{x}$ $\underline{y}$ $\underline{z}$ AE/R2

Table 1. Part number breakdown

| Code | Option   | Variable                  | Description             |

|------|----------|---------------------------|-------------------------|

| С    | 4 series | V typo                    | Linear                  |

|      | 6 series | V <sub>CORE</sub> type    | DCDC                    |

| х    | 0        |                           | 0.5 A or 0.8 A          |

|      | 1        | V <sub>CORE</sub> current | 1.5 A                   |

|      | 2        |                           | 2.2 A                   |

| у    | 0        |                           | none                    |

|      | 1        |                           | FS1B                    |

|      | 2        | Functions                 | LDT                     |

|      | 3        |                           | FS1B, LDT               |

|      | 4        |                           | LDT, VKAM ON by default |

| z    | N        |                           | none                    |

|      | С        | Physical interface        | CAN FD                  |

|      | L        |                           | CAN FD and LIN          |

FS6500-FS4500SDS

All information provided in this document is subject to legal disclaimers.

#### 5.2 Part numbers list

Table 2. Orderable part variations

| Part number   | Temperature (T <sub>A</sub> ) | Package                    | FS1B | LDT | VCORE | VCORE<br>type | VKAM on    | CAN FD | LIN | Notes   |

|---------------|-------------------------------|----------------------------|------|-----|-------|---------------|------------|--------|-----|---------|

| MC33FS4500CAE |                               |                            | 0    | 0   | 0.5 A | Linear        | by SPI     | 1      | 0   |         |

| MC33FS4500LAE |                               |                            | 0    | 0   | 0.5 A | Linear        | by SPI     | 1      | 1   | 1       |

| MC33FS4500NAE |                               |                            | 0    | 0   | 0.5 A | Linear        | by SPI     | 0      | 0   |         |

| MC33FS4501CAE |                               |                            | 1    | 0   | 0.5 A | Linear        | by SPI     | 1      | 0   |         |

| MC33FS4501NAE |                               |                            | 1    | 0   | 0.5 A | Linear        | by SPI     | 0      | 0   | 1       |

| MC33FS4502CAE |                               |                            | 0    | 1   | 0.5 A | Linear        | by SPI     | 1      | 0   | 1       |

| MC33FS4502LAE |                               |                            | 0    | 1   | 0.5 A | Linear        | by SPI     | 1      | 1   |         |

| MC33FS4502NAE |                               |                            | 0    | 1   | 0.5 A | Linear        | by SPI     | 0      | 0   | 1       |

| MC33FS4503CAE |                               |                            | 1    | 1   | 0.5 A | Linear        | by SPI     | 1      | 0   | 1       |

| MC33FS4503NAE |                               |                            | 1    | 1   | 0.5 A | Linear        | by SPI     | 0      | 0   |         |

| MC33FS6500CAE |                               |                            | 0    | 0   | 0.8 A | DC DC         | by SPI     | 1      | 0   | 1       |

| MC33FS6500LAE |                               |                            | 0    | 0   | 0.8 A | DC DC         | by SPI     | 1      | 1   | 1       |

| MC33FS6500NAE |                               |                            | 0    | 0   | 0.8 A | DC DC         | by SPI     | 0      | 0   | 1       |

| MC33FS6501CAE |                               |                            | 1    | 0   | 0.8 A | DC DC         | by SPI     | 1      | 0   |         |

| MC33FS6501NAE |                               |                            | 1    | 0   | 0.8 A | DC DC         | by SPI     | 0      | 0   | 1       |

| MC33FS6502CAE |                               |                            | 0    | 1   | 0.8 A | DC DC         | by SPI     | 1      | 0   | 1       |

| MC33FS6502LAE |                               |                            | 0    | 1   | 0.8 A | DC DC         | by SPI     | 1      | 1   |         |

| MC33FS6502NAE |                               | 48-pin LQFP<br>exposed pad | 0    | 1   | 0.8 A | DC DC         | by SPI     | 0      | 0   |         |

| MC33FS6503CAE |                               |                            | 1    | 1   | 0.8 A | DC DC         | by SPI     | 1      | 0   |         |

| MC33FS6503NAE |                               |                            | 1    | 1   | 0.8 A | DC DC         | by SPI     | 0      | 0   |         |

| MC33FS6504LAE | 40 °C to 125 °C               |                            | 0    | 1   | 0.8 A | DC DC         | by default | 1      | 1   | [1] [2] |

| MC33FS6510CAE | -40 °C to 125 °C              |                            | 0    | 0   | 1.5 A | DC DC         | by SPI     | 1      | 0   | 1777    |

| MC33FS6510LAE |                               |                            | 0    | 0   | 1.5 A | DC DC         | by SPI     | 1      | 1   | 1       |

| MC33FS6510NAE |                               |                            | 0    | 0   | 1.5 A | DC DC         | by SPI     | 0      | 0   | 1       |

| MC33FS6511CAE |                               |                            | 1    | 0   | 1.5 A | DC DC         | by SPI     | 1      | 0   | 1       |

| MC33FS6511NAE |                               |                            | 1    | 0   | 1.5 A | DC DC         | by SPI     | 0      | 0   | 1       |

| MC33FS6512CAE |                               |                            | 0    | 1   | 1.5 A | DC DC         | by SPI     | 1      | 0   | 1       |

| MC33FS6512LAE |                               |                            | 0    | 1   | 1.5 A | DC DC         | by SPI     | 1      | 1   |         |

| MC33FS6512NAE |                               |                            | 0    | 1   | 1.5 A | DC DC         | by SPI     | 0      | 0   | 1       |

| MC33FS6513CAE |                               |                            | 1    | 1   | 1.5 A | DC DC         | by SPI     | 1      | 0   |         |

| MC33FS6513NAE |                               |                            | 1    | 1   | 1.5 A | DC DC         | by SPI     | 0      | 0   |         |

| MC33FS6514LAE |                               |                            | 0    | 1   | 1.5 A | DC DC         | by default | 1      | 1   |         |

| MC33FS6520CAE |                               |                            | 0    | 0   | 2.2 A | DC DC         | by SPI     | 1      | 0   |         |

| MC33FS6520LAE |                               |                            | 0    | 0   | 2.2 A | DC DC         | by SPI     | 1      | 1   |         |

| MC33FS6520NAE |                               |                            | 0    | 0   | 2.2 A | DC DC         | by SPI     | 0      | 0   |         |

| MC33FS6521CAE |                               |                            | 1    | 0   | 2.2 A | DC DC         | by SPI     | 1      | 0   |         |

| MC33FS6521NAE |                               |                            | 1    | 0   | 2.2 A | DC DC         | by SPI     | 0      | 0   | 1       |

| MC33FS6522CAE |                               |                            | 0    | 1   | 2.2 A | DC DC         | by SPI     | 1      | 0   |         |

| MC33FS6522LAE |                               |                            | 0    | 1   | 2.2 A | DC DC         | by SPI     | 1      | 1   |         |

| MC33FS6522NAE |                               |                            | 0    | 1   | 2.2 A | DC DC         | by SPI     | 0      | 0   | 1       |

| MC33FS6523CAE |                               |                            | 1    | 1   | 2.2 A | DC DC         | by SPI     | 1      | 0   | 1       |

| MC33FS6523NAE |                               |                            | 1    | 1   | 2.2 A | DC DC         | by SPI     | 0      | 0   | 1       |

<sup>[1]</sup> To order parts in tape and reel, add the R2 suffix to the part number.

FS6500-FS4500SDS

LIN and FS1B functions are exclusive. The differentiation is made by part numbers. When LIN is available, FS1B is not, and vice versa. VKAM on by default is available on certain part numbers only.

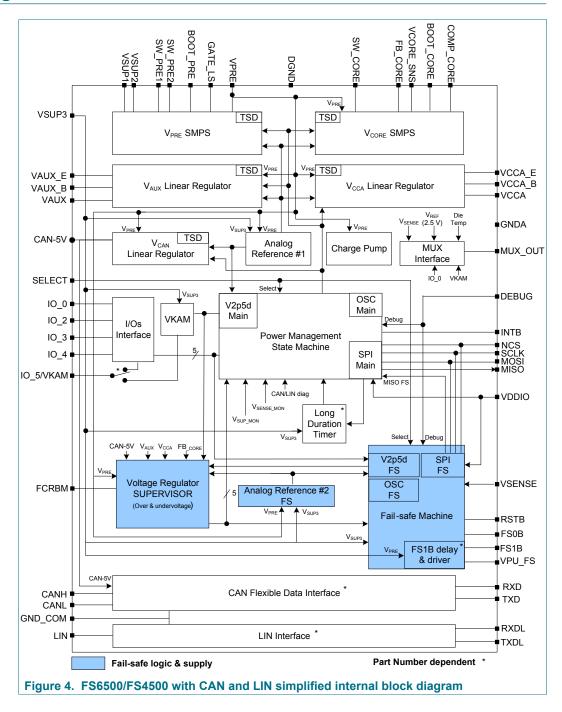

## 6 Block diagram

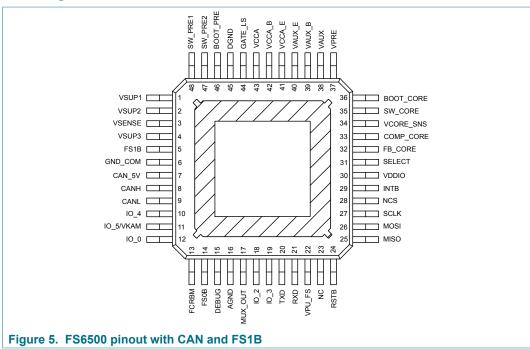

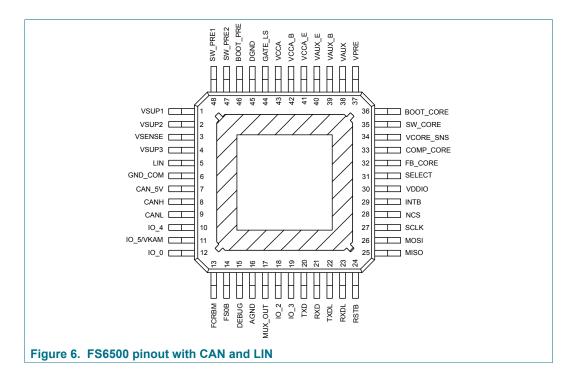

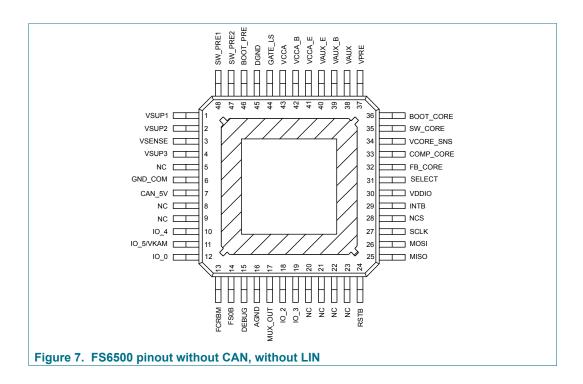

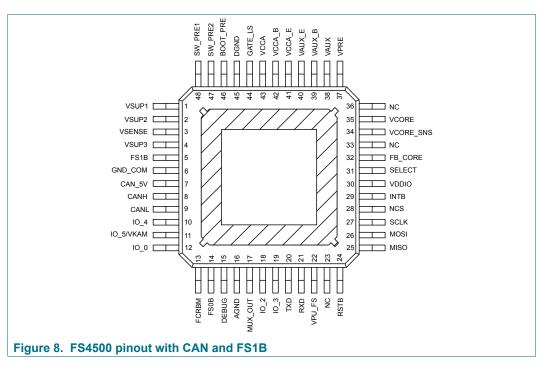

## 7 Pinning information

#### 7.1 Pinning

#### 7.2 Pin description

Table 3. FS6500/FS4500 pin definition

| Pin | Symbol | Туре | Definition                                                                                       |

|-----|--------|------|--------------------------------------------------------------------------------------------------|

| 1   | VSUP1  | A_IN | Power supply of the device. An external reverse battery protection diode in series is mandatory. |

FS6500-FS4500SDS

All information provided in this document is subject to legal disclaimers.

| Pin      | Symbol      | Туре                  | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | VSUP2       | A_IN                  | Second power supply. Protected by the external reverse battery protection diode used for VSUP1. VSUP1 and VSUP2 must be connected together externally.                                                                                                                                                                                                                                                                                                                                                                 |

| 3        | VSENSE      | A_IN                  | Sensing of the battery voltage. Must be connected prior to the reverse battery protection diode.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4        | VSUP3       | A_IN                  | Third power supply dedicated to the device supply. Protected by the external reverse battery protection diode used for VSUP1. Must be connected between the reverse protection diode and the input PI filter.                                                                                                                                                                                                                                                                                                          |

|          | LIN         | A_IN/OUT              | LIN single-wire bus transmitter and receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5        | or FS1B     | D_OUT                 | Second output of the safety block (active low). The pin is asserted low at start-up and when a fault condition is detected, with a configurable delay or duration versus FS0B output terminal. Open drain structure.                                                                                                                                                                                                                                                                                                   |

|          |             |                       | cclusive. The differentiation is made by part numbers. When LIN is available, FS1B is not, nor FS1B functions are used, this pin must be left open.                                                                                                                                                                                                                                                                                                                                                                    |

| 6        | GND_COM     | GROUND                | Dedicated ground for physical layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7        | CAN_5V      | A_OUT                 | Output voltage for the embedded CAN FD interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8        | CANH        | A_IN/OUT              | CAN output high. If CAN function is not used, this pin must be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9        | CANL        | A_IN/OUT              | CAN output low. If CAN function is not used, this pin must be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10       | IO_4        | D_IN<br>A_OUT         | Can be used as digital input (load dump proof) with wake-up capability or as an output gate driver  Digital input: Pin status can be read through the SPI. Can be used to monitor error signals from another IC for safety purposes (when used in conjunction with IO_5).                                                                                                                                                                                                                                              |

|          |             |                       | Wake-up capability: Can be selectable to wake-up on edges or levels  Output gate driver: Can drive a logic level low-side NMOS transistor. Controlled by the SPI.                                                                                                                                                                                                                                                                                                                                                      |

| 11       | IO_5/VKAM   | A_IN<br>D_IN<br>A_OUT | Can be used as digital input with wake-up capability or as an analog output providing keep alive memory supply in low-power mode.  Analog input: Pin status can be read through the MUX output terminal  Digital input: Pin status can be read through the SPI. Can be used to monitor error signals from another IC for safety purposes (when used in conjunction with IO_4).  Wake-up capability: Can be selectable to wake-up on edges or levels  Supply output: Provide keep alive memory supply in low-power mode |

|          | VKAM can be | enabled or disal      | oled by default at power up. The differentiation is made by part numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12       | 10_0        | A_IN<br>D_IN          | Can be used as analog or digital input (load dump proof) with wake-up capability (selectable)  Analog input: Pin status can be read through the MUX output terminal  Digital input: Pin status can be read through the SPI  Wake-up capability: Can be selectable to wake-up on edges or levels                                                                                                                                                                                                                        |

| 13       | FCRBM       | A_IN                  | Feedback core resistor bridge monitoring: For safety purposes, this pin is used to monitor the middle point of a redundant resistor bridge connected on $V_{CORE}$ (in parallel to the one used to set the $V_{CORE}$ voltage). If not used, this pin must be connected directly to FB_CORE.                                                                                                                                                                                                                           |

| 14       | FS0B        | D_OUT                 | First output of the safety block (active low). The pin is asserted low at start-up and when a fault condition is detected. Open drain structure.                                                                                                                                                                                                                                                                                                                                                                       |

| 15       | DEBUG       | D_IN                  | Debug mode entry input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 16       | AGND        | GROUND                | Analog ground connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 17       | MUX_OUT     | A_OUT                 | Multiplexed output to be connected to a MCU ADC. Selection of the analog parameter is available at MUX-OUT through the SPI.                                                                                                                                                                                                                                                                                                                                                                                            |

| 18<br>19 | IO_2:3      | D_IN                  | Digital input pin with wake-up capability (logic level compatible)  Digital input: Pin status can be read through the SPI. Can be used to monitor FCCU error signals from MCU for safety purposes.  Wake-up capability: Can be selectable to wake-up on edges or levels                                                                                                                                                                                                                                                |

FS6500-FS4500SDS

All information provided in this document is subject to legal disclaimers.

| Pin | Symbol        | Туре     | Definition                                                                                                                                                                                                                     |

|-----|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | TXD           | D_IN     | Transceiver input from the MCU which controls the state of the CAN bus. Internal pull-<br>up to VDDIO.  If CAN function is not used, this pin must be left open.                                                               |

| 21  | RXD           | D_OUT    | Receiver output which reports the state of the CAN bus to the MCU                                                                                                                                                              |

|     |               |          | If CAN function is not used, this pin must be left open                                                                                                                                                                        |

| 22  | TXDL          | D_IN     | Transceiver input from the MCU controlling the state of the LIN bus. Internal pull-up to VDDIO.                                                                                                                                |

|     | or VPU_FS     | A_OUT    | Pull-up output for FS1B function                                                                                                                                                                                               |

|     |               |          | exclusive. The differentiation is made by part numbers. When LIN is available, FS1B is not, nor FS1B functions are used, this pin must be left open.                                                                           |

| 23  | RXDL          | D_OUT    | Receiver output reporting the state of the LIN bus to the MCU.  If LIN function is not used, this pin must be left open.                                                                                                       |

| 24  | RSTB          | D_OUT    | This output is asserted low when the safety block reports a failure. The main function is to reset the MCU. Reset input voltage is also monitored in order to detect external reset and fault condition. Open drain structure. |

| 25  | MISO          | D_OUT    | SPI bus. Master input slave output                                                                                                                                                                                             |

| 26  | MOSI          | D_IN     | SPI bus. Master output slave input                                                                                                                                                                                             |

| 27  | SCLK          | D_IN     | SPI Bus. Serial clock                                                                                                                                                                                                          |

| 28  | NCS           | D_IN     | Not chip select (active low)                                                                                                                                                                                                   |

| 29  | INTB          | D_OUT    | This output pin generates a low pulse when an Interrupt condition occurs. Pulse duration is configurable. Internal pull-up to VDDIO.                                                                                           |

| 30  | VDDIO         | A_IN     | Input voltage for MISO output buffer. Allows voltage compatibility with MCU I/Os.                                                                                                                                              |

| 31  | SELECT        | D_IN     | Hardware selection pin for VAUX and VCCA output voltages                                                                                                                                                                       |

| 32  | FB_CORE       | A_IN     | VCORE voltage feedback. Input of the error amplifier.                                                                                                                                                                          |

| 33  | COMP_COR<br>E | A_OUT    | Compensation network. Output of the error amplifier. For FS4500 series, this pin must be left open (NC).                                                                                                                       |

| 34  | VCORE_SNS     | A_IN     | VCORE input voltage sense                                                                                                                                                                                                      |

| 35  | SW_CORE       | A_OUT    | VCORE output switching point for FS6500 series                                                                                                                                                                                 |

|     | or VCORE      | A_OUT    | VCORE output voltage for FS4500 series                                                                                                                                                                                         |

| 36  | BOOT_COR<br>E | A_IN/OUT | Bootstrap capacitor for VCORE internal NMOS gate drive. For FS4500 series, this pin must be left open (NC).                                                                                                                    |

| 37  | VPRE          | A_IN     | VPRE input voltage sense                                                                                                                                                                                                       |

| 38  | VAUX          | A_OUT    | VAUX output voltage. External PNP ballast transistor. Collector connection                                                                                                                                                     |

| 39  | VAUX_B        | A_OUT    | VAUX voltage regulator. External PNP ballast transistor. Base connection                                                                                                                                                       |

| 40  | VAUX_E        | A_OUT    | VAUX voltage regulator. External PNP ballast transistor. Emitter connection                                                                                                                                                    |

| 41  | VCCA_E        | A_OUT    | VCCA voltage regulator. External PNP ballast transistor. Emitter connection                                                                                                                                                    |

| 42  | VCCA_B        | A_OUT    | VCCA voltage regulator. External PNP ballast transistor. Base connection                                                                                                                                                       |

| 43  | VCCA          | A_OUT    | VCCA output voltage. External PNP ballast transistor. Collector connection                                                                                                                                                     |

| 44  | GATE_LS       | A_OUT    | Low-side MOSFET gate drive for non-inverting buck-boost configuration                                                                                                                                                          |

| 45  | DGND          | GROUND   | Digital ground connection                                                                                                                                                                                                      |

| 46  | BOOT_PRE      | A_IN/OUT | Bootstrap capacitor for the VPRE internal NMOS gate drive                                                                                                                                                                      |

| 47  | SW_PRE2       | A_OUT    | Second pre-regulator output switching point                                                                                                                                                                                    |

| 48  | SW_PRE1       | A_OUT    | First pre-regulator output switching point                                                                                                                                                                                     |

## 8 Maximum ratings

#### Table 4. Maximum ratings

All voltages are with respect to ground, unless otherwise specified. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                  | Ratings                                                                             | Value       | Unit | Notes |

|-------------------------|-------------------------------------------------------------------------------------|-------------|------|-------|

| Electrical ratin        | ngs                                                                                 |             |      |       |

| V <sub>SUP1/2/3</sub>   | DC voltage at power supply pins                                                     | -1.0 to 40  | V    | [1]   |

| V <sub>SENSE</sub>      | DC voltage at battery sense pin (with ext R in series mandatory)                    | -14 to 40   | V    |       |

| V <sub>SW1,2</sub>      | DC voltage at SW_PRE1 and SW_PRE2 pins                                              | -1.0 to 40  | V    |       |

| $V_{PRE}$               | DC voltage at VPRE pin                                                              | -0.3 to 8   | V    |       |

| V <sub>GATE_LS</sub>    | DC voltage at Gate_LS pin                                                           | -0.3 to 8   | V    |       |

| V <sub>BOOT_PRE</sub>   | DC voltage at BOOT_PRE pin                                                          | -1.0 to 50  | V    |       |

| V <sub>SW_CORE</sub>    | DC voltage at SW_CORE pin                                                           | -1.0 to 8   | V    |       |

| V <sub>CORE_SNS</sub>   | DC voltage at VCORE_SNS pin                                                         | 0.0 to 8    | V    |       |

| V <sub>BOOT_CORE</sub>  | DC voltage at BOOT_CORE pin                                                         | 0.0 to 15   | V    |       |

| V <sub>FB_CORE</sub>    | DC voltage at FB_CORE pin                                                           | -0.3 to 2.5 | V    |       |

| V <sub>COMP_CORE</sub>  | DC voltage at COMP_CORE pin                                                         | -0.3 to 2.5 | V    |       |

| V <sub>FCRBM</sub>      | DC voltage at FCRBM pin                                                             | -0.3 to 8   | V    |       |

| V <sub>AUX_B,E</sub>    | DC voltage at VAUX_B, VAUX_E pins                                                   | -0.3 to 40  | V    |       |

| V <sub>AUX</sub>        | DC voltage at VAUX pin                                                              | -2.0 to 40  | V    |       |

| V <sub>CCA_B,E</sub>    | DC voltage at VCCA_B, VCCA_E pins                                                   | -0.3 to 8   | V    |       |

| V <sub>CCA</sub>        | DC voltage at VCCA pin                                                              | -0.3 to 8   | V    |       |

| $V_{\rm DDIO}$          | DC voltage at VDDIO pin                                                             | -0.3 to 8   | V    |       |

| V <sub>CAN_5V</sub>     | DC voltage on CAN_5V pin                                                            | -0.3 to 8   | V    |       |

| V <sub>PU_FS</sub>      | DC voltage at VPU_FS pin                                                            | -0.3 to 8   | V    |       |

| $V_{FSxB}$              | DC voltage at FS0B, FS1B pins (with ext R in series mandatory)                      | -0.3 to 40  | V    |       |

| V <sub>DEBUG</sub>      | DC voltage at DEBUG pin                                                             | -0.3 to 40  | V    |       |

| V <sub>IO_0,4</sub>     | DC voltage at IO_0, IO_4 pins (with ext R in series mandatory)                      | -0.3 to 40  | V    |       |

| V <sub>IO_5</sub>       | DC voltage at IO_5 pin                                                              | -0.3 to 20  | V    |       |

| $V_{KAM}$               | DC voltage at VKAM pin                                                              | -0.3 to 8   | V    |       |

| $V_{DIG}$               | DC voltage at INTB, RSTB, MISO, MOSI, NCS, SCLK, MUX_OUT, RXD, TXD, IO_2, IO_3 pins | -0.3 to 8   | V    |       |

| V <sub>SELECT</sub>     | DC voltage at SELECT pin                                                            | -0.3 to 8   | V    |       |

| V <sub>BUS_CAN</sub>    | DC voltage on CANL, CANH pins                                                       | -27 to 40   | V    |       |

| V <sub>BUS_LIN</sub>    | DC voltage on LIN pin                                                               | -18 to 40   | V    |       |

| I_I <sub>SENSE</sub>    | V <sub>SENSE</sub> maximum current capability                                       | -5.0 to 5.0 | mA   |       |

| I IO <sub>0, 4, 5</sub> | IOs maximum current capability (IO_0, IO_4, IO_5)                                   | -5.0 to 5.0 | mA   |       |

| Symbol                                                                                           | Ratings                                                                                                                                                                            | Value                        | Unit           | Notes    |

|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|----------|

| ESD voltage                                                                                      |                                                                                                                                                                                    |                              |                | <u> </u> |

| V <sub>ESD-HBM1</sub><br>V <sub>ESD-HBM2</sub><br>V <sub>ESD-HBM3</sub><br>V <sub>ESD-HBM4</sub> | <ul> <li>Human body model (JESD22/A114) – 100 pF, 1.5 kΩ</li> <li>All pins</li> <li>VSUP1,2,3, VSENSE, VAUX, IO_0,4, FS0B, FS1B, DEBUG</li> <li>CANH, CANL</li> <li>LIN</li> </ul> | ±2.0<br>±4.0<br>±6.0<br>±8.0 | kV<br>kV<br>kV | [2]      |

| V <sub>ESD-CDM1</sub><br>V <sub>ESD-CDM2</sub>                                                   | Charge device model (JESD22/C101):  • All pins  • Corner pins  System level ESD (gun test)                                                                                         | ±500<br>±750                 | V              |          |

| V <sub>ESD-GUN1</sub>                                                                            | • VSUP1, 2, 3, VSENSE, VAUX, IO_0, 4, 5, FS0B, FS1B  330 Ω/150 pF unpowered according to IEC61000-4-2                                                                              | ±8.0                         | kV             |          |

| V <sub>ESD-GUN2</sub>                                                                            | 330 Ω/150 pF unpowered according to OEM LIN, CAN, FLexray Conformance                                                                                                              | ±8.0                         | kV             |          |

| V <sub>ESD-GUN3</sub>                                                                            | 2.0 kΩ/150 pF unpowered according to ISO10605.2008                                                                                                                                 | ±8.0                         | kV             |          |

| V <sub>ESD-GUN4</sub>                                                                            | <ul><li>2.0 kΩ/330 pF powered according to ISO10605.2008</li><li>CANH, CANL</li></ul>                                                                                              | ±8.0                         | kV             |          |

| V <sub>ESD-GUN5</sub>                                                                            | 330 $\Omega/150$ pF unpowered according to IEC61000-4-2                                                                                                                            | ±15.0                        | kV             |          |

| V <sub>ESD-GUN6</sub>                                                                            | 330 $\Omega$ /150 pF unpowered according to OEM LIN, CAN, FLexray conformance                                                                                                      | ±12.0                        | kV             |          |

| V <sub>ESD-GUN7</sub>                                                                            | 2.0 kΩ/150 pF unpowered according to ISO10605.2008                                                                                                                                 | ±15.0                        | kV             |          |

| V <sub>ESD-GUN8</sub>                                                                            | 2.0 kΩ/330 pF powered according to ISO10605.2008 • LIN                                                                                                                             | ±12.0                        | kV             |          |

| V <sub>ESD-GUN9</sub>                                                                            | 330 $\Omega/150$ pF unpowered according to IEC61000-4-2:                                                                                                                           | ±12.0                        | kV             |          |

| V <sub>ESD-GUN10</sub>                                                                           | 330 $\Omega$ /150 pF unpowered according to OEM LIN, CAN, flexray conformance                                                                                                      | ±12.0                        | kV             |          |

| V <sub>ESD-GUN11</sub>                                                                           | 2.0 kΩ/150 pF unpowered according to ISO10605.2008                                                                                                                                 | ±12.0                        | kV             |          |

| V <sub>ESD-GUN12</sub>                                                                           | 2.0 kΩ/330 pF powered according to ISO10605.2008                                                                                                                                   | ±12.0                        | kV             |          |

| Thermal rating                                                                                   | gs                                                                                                                                                                                 |                              |                |          |

| T <sub>A</sub>                                                                                   | Ambient temperature                                                                                                                                                                | -40 to 125                   | °C             |          |

| TJ                                                                                               | Junction temperature                                                                                                                                                               | -40 to 150                   | °C             |          |

| T <sub>STG</sub>                                                                                 | Storage temperature                                                                                                                                                                | -55 to 150                   | °C             |          |

| Thermal resis                                                                                    | tance                                                                                                                                                                              |                              |                |          |

| $R_{\theta JA}$                                                                                  | Thermal resistance junction to ambient                                                                                                                                             | 30                           | °C/W           | [3]      |

| R <sub>0JCTOP</sub>                                                                              | Thermal resistance junction to case top                                                                                                                                            | 23.8                         | °C/W           | [4]      |

| R <sub>θ</sub> ЈСВОТТОМ                                                                          | Thermal resistance junction to case bottom                                                                                                                                         | 0.9                          | °C/W           | [5]      |

All VSUPs (V $_{\rm SUP1/2/3}$ ) must be connected to the same supply Compared to AGND Per JEDEC JESD51-6 with the board (JESD51-7) horizontal

<sup>[2]</sup> [3]

<sup>[4]</sup> [5]

Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC - 883 Method 1012.1). Thermal resistance between the die and the solder pad on the bottom of the packaged based on simulation without any interface resistance.

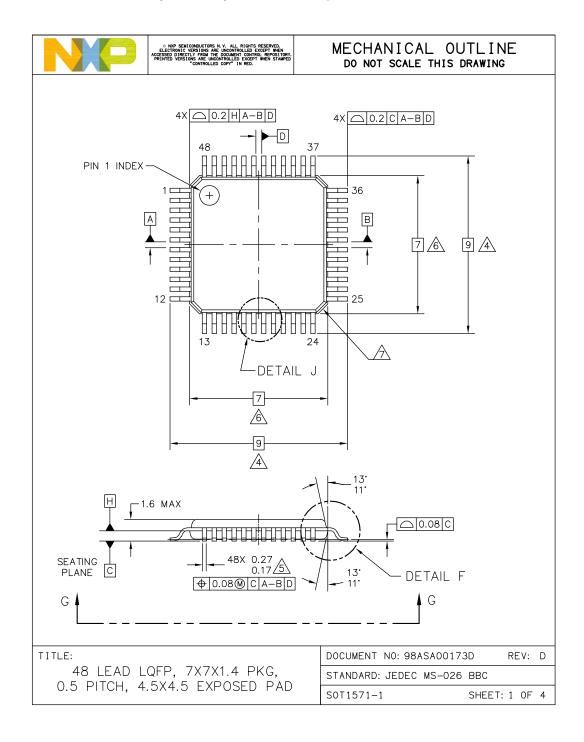

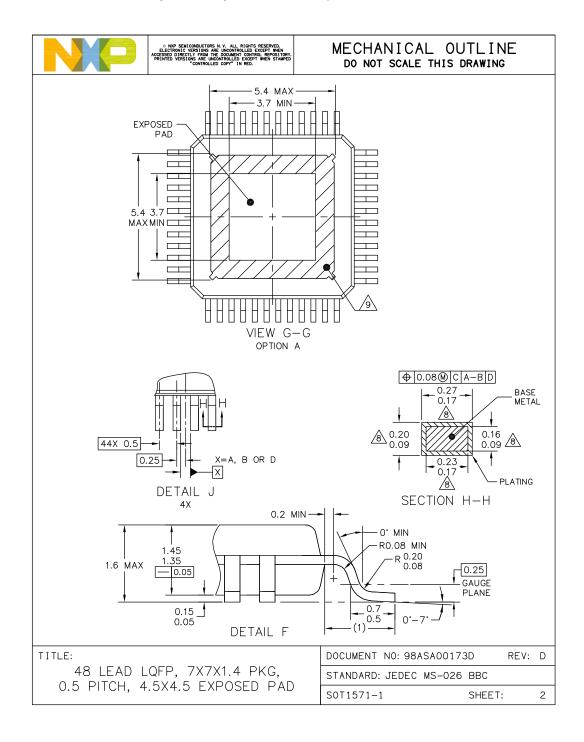

## 9 Packaging

## 9.1 Package mechanical dimensions

Package dimensions are provided in package drawings. To find the most current package outline drawing, go to www.nxp.com and perform a keyword search for the drawing's document number.

Table 5. Package mechanical dimensions

| Package                                                                                    | Suffix | Package outline drawing number |

|--------------------------------------------------------------------------------------------|--------|--------------------------------|

| $7.0 \times 7.0$ , 48–Pin LQFP exposed pad, with 0.5 mm pitch, and a 4.5 × 4.5 exposed pad | AE     | 98ASA00173D                    |

# MECHANICAL OUTLINE DO NOT SCALE THIS DRAWING

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

- A. DIMENSION TO BE DETERMINED AT SEATING PLANE C.

- THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT BY MORE THAN 0.08MM AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07MM.

- THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25MM PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

- A EXACT SHAPE OF EACH CORNER IS OPTIONAL.

- \*\* THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1MM AND 0.25MM FROM THE LEAD TIP.

- A HATCHED AREA TO BE KEEP OUT ZONE FOR PCB ROUTING.

TITLE:

48 LEAD LQFP, 7X7X1.4 PKG, 0.5 PITCH, 4.5X4.5 EXPOSED PAD

DOCUMENT NO: 98ASA00173D REV: D

STANDARD: JEDEC MS-026 BBC

SOT1571-1 SHEET: 3

#### 10 References

The following are URLs where you can obtain information on related NXP products and application solutions.

| NXP.com support pages                  | Description                                                                    | URL                                                                                            |  |  |

|----------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| AN5238                                 | Hardware design and product guidelines                                         | http://www.nxp.com/AN5238-DOWNLOAD                                                             |  |  |

| AN4388                                 | Quad flat package (QFP)                                                        | http://www.nxp.com/files/analog/doc/app_note/AN4388.pdf                                        |  |  |

| Power dissipation tool (Excel          | file)                                                                          | http://www.nxp.com/files/analog/software_tools/FS6500-FS4500-power-dissipation-calculator.xlsx |  |  |

| V <sub>CORE</sub> compensation network | simulation tool (CNC)                                                          | Upon demand                                                                                    |  |  |

| FMEDA                                  | FS6500/FS4500 FMEDA                                                            | Upon demand                                                                                    |  |  |

| FS6500-FS4500SMUG                      | FS6500/FS4500 Safety Manual – user guide                                       | https://www.nxp.com/webapp/Download?colCode=FS6500-FS4500SMUG                                  |  |  |

| FS6500-FS4500                          | Power System Basis Chip with CAN Flexible Data and LIN Transceivers data sheet | https://www.nxp.com/webapp/Download?colCode=FS6500-FS4500                                      |  |  |

| KITFS6522LAEEVM                        | FS6500 evaluation board with LIN (no FS1B)                                     | http://www.nxp.com/KITFS6522LAEEVM                                                             |  |  |

| KITFS4503CAEEVM                        | FS4500 evaluation board with FS1B (no LIN)                                     | http://www.nxp.com/KITFS4503CAEEVM                                                             |  |  |

| KITFS6523CAEEVM                        | FS6500 evaluation board with FS1B (no LIN)                                     | http://www.nxp.com/KITFS6523CAEEVM                                                             |  |  |

| FS6500 product summary pa              | ge                                                                             | http://www.nxp.com/FS6500                                                                      |  |  |

| FS4500 product summary pa              | ge                                                                             | http://www.nxp.com/FS4500                                                                      |  |  |

| Analog power management h              | ome page                                                                       | http://www.nxp.com/products/power-management                                                   |  |  |

## 11 Revision history

#### Table 6. Revision history

| Document ID            | Release date | Data sheet status               | Change notice | Supersedes |

|------------------------|--------------|---------------------------------|---------------|------------|

| FS6500-FS4500SDS v.1.0 | 20171214     | Data sheet: advance information | _             | _          |

### 12 Legal information

#### 12.1 Data sheet status

| Document status <sup>[1][2]</sup>       | Product status <sup>[3]</sup> | Definition                                                                                                                                                                                           |

|-----------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [short] Data sheet: product preview     | Development                   | This document contains certain information on a product under development. NXP reserves the right to change or discontinue this product without notice.                                              |

| [short] Data sheet: advance information | Qualification                 | This document contains information on a new product. Specifications and information herein are subject to change without notice.                                                                     |

| [short] Data sheet: technical data      | Production                    | This document contains the product specification. NXP Semiconductors reserves the right to change the detail specifications as may be required to permit improvements in the design of its products. |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 12.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a technical data data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the technical data data sheet.

#### 12.3 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without

limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

Suitability for use in automotive applications — This NXP Semiconductors product has been qualified for use in automotive applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental

FS6500-FS4500SDS

All information provided in this document is subject to legal disclaimers.

damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### 12.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

NXP — is a trademark of NXP B.V.

SafeAssure - is a trademark of NXP B.V.

**SMARTMOS** — is a trademark of NXP B.V.

# FS6500, FS4500

## Safety Power System Basis Chip with CAN FD and LIN Transceivers

## **Tables**

| Tab. 1.<br>Tab. 2.<br>Tab. 3. | Part number breakdown                                                             | Tab. 4.<br>Tab. 5.<br>Tab. 6. | Maximum ratings Package mechanical dimensions Revision history         |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------|--|--|--|

| Figur                         | res                                                                               |                               |                                                                        |  |  |  |

| Fig. 1.                       | FS6500C simplified application diagram - buck boost configuration - FS1B2         | Fig. 4.                       | FS6500/FS4500 with CAN and LIN simplified internal block diagram       |  |  |  |

| Fig. 2.                       | FS6500L simplified application diagram - buck configuration - LIN - VCCA =100 mA2 | Fig. 5.<br>Fig. 6.            | FS6500 pinout with CAN and FS1BFS6500 pinout with CAN and LIN          |  |  |  |

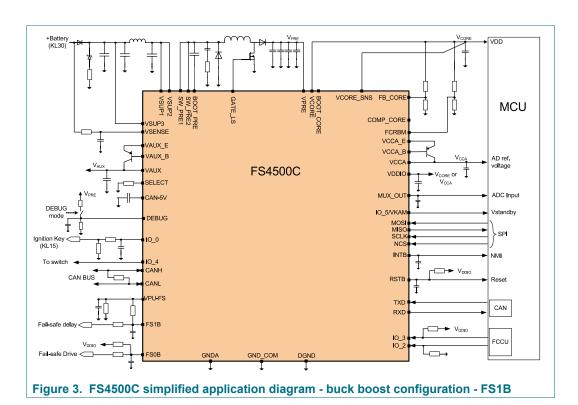

| Fig. 3.                       | FS4500C simplified application diagram - buck boost configuration - FS1B3         | Fig. 7.<br>Fig. 8.            | FS6500 pinout without CAN, without LIN FS4500 pinout with CAN and FS1B |  |  |  |

#### **Contents**

| 1   | General description            | 1  |

|-----|--------------------------------|----|

| 2   | Features                       |    |

| 3   | Applications                   | 1  |

| 4   | Simplified application diagram | 2  |

| 5   | Ordering information           | 3  |

| 5.1 | Part numbers definition        |    |

| 5.2 | Part numbers list              | 4  |

| 6   | Block diagram                  | 5  |

| 7   | Pinning information            | 6  |

| 7.1 | Pinning                        |    |

| 7.2 | Pin description                | 7  |

| 8   | Maximum ratings                | 10 |

| 9   | Packaging                      |    |

| 9.1 | Package mechanical dimensions  |    |

| 10  | References                     | 16 |

| 11  | Revision history               |    |

| 12  | Legal information              |    |

|     |                                |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.