# 50 Hz to 3.8 GHz 65 dB TruPwr<sup>™</sup> Detector

Data Sheet AD8362

### **FEATURES**

Complete, fully calibrated measurement/control system Accurate rms-to-dc conversion from 50 Hz to 3.8 GHz Input dynamic range of >65 dB: -52 dBm to +8 dBm in  $50~\Omega$  Waveform and modulation independent, such as GSM/CDMA/TDMA

Linear-in-decibels output, scaled 50 mV/dB Law conformance error of 0.5 dB All functions temperature and supply stable Operates from 4.5 V to 5.5 V at 24 mA Power-down capability to 1.3 mW

### **APPLICATIONS**

Power amplifier linearization/control loops Transmitter power controls Transmitter signal strength indication (TSSI) Radio frequency (RF) instrumentation

### **GENERAL DESCRIPTION**

The AD8362 is a true rms-responding power detector that has a 65 dB measurement range. It is intended for use in a variety of high frequency communication systems and in instrumentation requiring an accurate response to signal power. It is easy to use, requiring only a single supply of 5 V and a few capacitors. It operates from arbitrarily low frequencies to over 3.8 GHz and accepts inputs from –52 dBm to +8 dBm with crest factors that are typical of quadrature amplitude modulation (QAM) and orthogonal frequency division multiplexing (OFDM) modulation schemes.

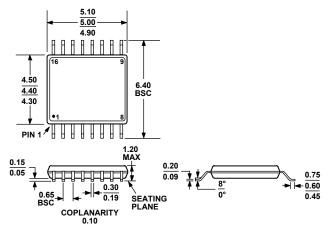

The AD8362 has a 1.3 mW power consumption when powered down by a logic high applied to the PWDN pin. It powers up within about 20  $\mu$ s to its nominal operating current of 20 mA at 25°C. The AD8362 is supplied in a 16-lead TSSOP for operation over the temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

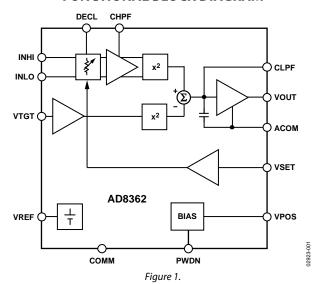

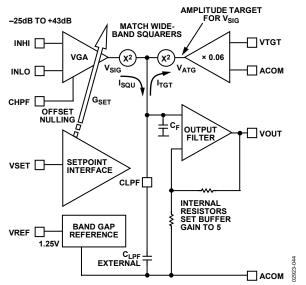

### **FUNCTIONAL BLOCK DIAGRAM**

Table 1. Next Generation Upgrades for the AD8362

| Device No. | Product Description                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------|

| ADL5902    | Improved temperature stability, single-ended input drive.                                                    |

| HMC1120    | Improved sensitivity and range, includes envelope tracking and peak-hold function, single-ended input drive. |

| ADL5906    | Improved temperature stability, single-ended input drive. Slightly lower input range.                        |

| AD8363     | Improved temperature stability, single-ended input drive. Lower input range.                                 |

| ADL5903    | Lower range, significantly lower power consumption, single-ended input drive.                                |

| ADL5501    | Lower range, significantly lower power consumption, linear in V/V output, single-ended input drive.          |

Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| Functional Block Diagram                    | 1  |

| General Description                         | 1  |

| Revision History                            | 3  |

| Specifications                              | 4  |

| Absolute Maximum Ratings                    | 7  |

| ESD Caution                                 | 7  |

| Pin Configuration and Function Descriptions | 8  |

| Equivalent Circuits                         | 9  |

| Typical Performance Characteristics         | 10 |

| Characterization Setup                      | 16 |

| Equipment                                   | 16 |

| Analysis                                    | 16 |

| Circuit Description                         | 17 |

| Square Law Detection                        | 17 |

| Voltage vs. Power Calibration               | 18 |

| Offset Elimination                          | 19 |

| Time-Domain Response of the Closed Loop     | 19 |

| Operation in RF Measurement Mode                                        |

|-------------------------------------------------------------------------|

| Basic Connections                                                       |

| Device Disable                                                          |

| Recommended Input Coupling                                              |

| Operation at Low Frequencies21                                          |

| Choosing a Value for CHPF22                                             |

| Choosing a Value for CLPF                                               |

| Adjusting VTGT to Accommodate Signals with Very High<br>Crest Factors23 |

| Altering the Slope23                                                    |

| Temperature Compensation and Reduction of Transfer Function Ripple24    |

| Temperature Compensation at Various WiMAX Frequencies up to 3.8 GHz     |

| Operation in Controller Mode27                                          |

| RMS Voltmeter with 90 dB Dynamic Range28                                |

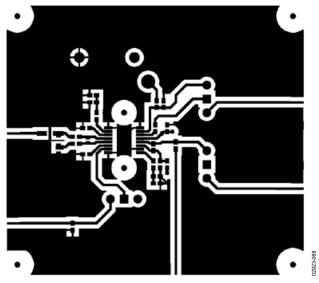

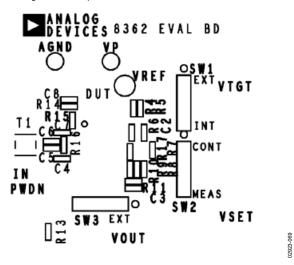

| AD8362 Evaluation Board                                                 |

| Outline Dimensions                                                      |

| Oudoring Crido                                                          |

| REVISION HISTORY                                              |

|---------------------------------------------------------------|

| 9/15—Rev. E to Rev. F                                         |

| Changes to General Description Section1                       |

| Added Table 1; Renumbered Sequentially1                       |

| Change to Equation 317                                        |

| Changes to Ordering Guide                                     |

| 12/12—Rev. D to Rev. E                                        |

| Changes to Time Domain Response of the Closed Loop Section 18 |

| Changes to Equation 13, Choosing a Value for CLPF Section     |

| and Equation 1421                                             |

| Changes to Ordering Guide31                                   |

| 6/07—Rev. C to Rev. D                                         |

| Changes to Features, General Description1                     |

| Changes to Table 1                                            |

| Changes to Table 26                                           |

| Added Figure 21 to Figure 2511                                |

| Changes to Equipment Section15                                |

| Changes to Circuit Description Section16                      |

| Changes to Single-Ended Input Drive Section19                 |

| Changes to Choosing a Value for CHPF section21                |

| Changes to Choosing a Value for CLPF section21                |

| Changes to Figure 5723                                        |

| Changes to Figure 5824                                        |

| Added Temperature Compensation at Various WiMAX               |

| Frequencies up to 3.8 GHz Section24                           |

| Changes to Ordering Guide31                                   |

| 9/05—Rev. B to Rev. C                                   |       |

|---------------------------------------------------------|-------|

| Changes to Specifications                               | 3     |

| Changes to Table 3                                      |       |

| Deleted Figure 16 to Figure 18; Renumbered Sequentially | 10    |

| Changes to Figure 32 and Figure 33                      | 13    |

| Replaced Circuit Description Section                    |       |

| Changes to Operation in RF Measurement Mode Section     | 18    |

| Deleted Using the AD8362 Section                        | 20    |

| Deleted Main Modes of Operation Section                 | 22    |

| Changes to Operation in Controller Mode Section         | 23    |

| Changes to AD8362 Evaluation Board Section              |       |

| Deleted General Applications Section                    | 29    |

| 3/04—Rev. A to Rev. B                                   |       |

| Updated Format                                          | ersal |

| Changes to Specifications                               | 3     |

| Changes to the Offset Elimination Section               | 16    |

| Changes to the Operation at Low Frequencies Section     | 17    |

| Changes to the Time-Domain Response of the Closed Loop  | ,     |

| Section                                                 | 17    |

| Changes to Equation 13                                  | 24    |

| Changes to Table 5                                      | 31    |

|                                                         |       |

| 6/03—Rev. 0 to Rev. A                                   |       |

| Updated Ordering Guide                                  | 5     |

| Change to Analysis Section                              | 12    |

| Updated AD8362 Evaluation Board Section                 | 26    |

2/03—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_S = 5 \text{ V}, T = 25^{\circ}\text{C}, Z_O = 50 \Omega$ , differential input drive via balun<sup>1</sup>, VTGT connected to VREF, VOUT tied to VSET, unless otherwise noted.

Table 2.

| Parameter                          | Test Conditions/Comments                                                                 | Min   | Тур             | Max   | Unit         |

|------------------------------------|------------------------------------------------------------------------------------------|-------|-----------------|-------|--------------|

| OVERALL FUNCTION                   |                                                                                          |       |                 |       |              |

| Maximum Input Frequency            |                                                                                          |       | 3.8             |       | GHz          |

| Input Power Range (Differential)   | dB referred to 50 Ω impedance level, $f \le 2.7$ GHz, into 1:4 balun <sup>1</sup>        |       |                 |       |              |

| Nominal Low End of Range           |                                                                                          |       | -52             |       | dBm          |

| Nominal High End of Range          |                                                                                          |       | 8               |       | dBm          |

| Input Voltage Range (Differential) | RMS voltage at input terminals, $f \le 2.7$ GHz, into input of the device                |       |                 |       |              |

| Nominal Low End of Range           |                                                                                          |       | 1.12            |       | mV rms       |

| Nominal High End of Range          |                                                                                          |       | 1.12            |       | V rms        |

| Input Power Range (S-Sided)        | Single-ended drive, CW input, $f \le 2.7$ GHz, into input resistive network <sup>2</sup> |       |                 |       |              |

| Nominal Low End of Range           |                                                                                          |       | -40             |       | dBm          |

| Nominal High End of Range          |                                                                                          |       | 0               |       | dBm          |

| Input Voltage Range (S-Sided)      | RMS voltage at input terminals, f ≤ 2.7 GHz                                              |       |                 |       |              |

| Nominal Low End of Range           | ,                                                                                        |       | 2.23            |       | mV rms       |

| Nominal High End of Range          |                                                                                          |       | 2.23            |       | V rms        |

| Input Power Range (S-Sided)        | Single-ended drive, CW input, $f \ge 2.7$ GHz, into matched input network <sup>3</sup>   |       |                 |       |              |

| Nominal Low End of Range           |                                                                                          |       | -35             |       | dBm          |

| Nominal High End of Range          |                                                                                          |       | 12 <sup>4</sup> |       | dBm          |

| Output Voltage Range               | $R_L \ge 200 \Omega$ to ground                                                           |       |                 |       |              |

| Nominal Low End of Range           | 10 = 200 12 to ground                                                                    |       | 100             |       | mV           |

| Nominal High End of Range          | In general, $V_s = 0.1 \text{ V}$                                                        |       | 4.9             |       | V            |

| Output Scaling (Log Slope)         | in general, vs. o.i v                                                                    |       | 50              |       | mV/dB        |

| Law Conformance Error              | Over central 60 dB range, f ≤ 2.7 GHz                                                    |       | ±0.5            |       | dB           |

| RF INPUT INTERFACE                 | Pin INHI, Pin INLO, ac-coupled, at low frequencies                                       |       |                 |       | GD.          |

| Input Resistance                   | Single-ended drive, with respect to DECL                                                 |       | 100             |       | Ω            |

| input nesistance                   | Differential drive                                                                       |       | 200             |       | Ω            |

| OUTPUT INTERFACE                   | Pin VOUT                                                                                 |       | 200             |       | 12           |

| Available Output Range             | $R_L \ge 200 \Omega$ to ground                                                           | 0.1   |                 | 4.9   | V            |

| Absolute Voltage Range             | N <sub>L</sub> ≥ 200 12 to ground                                                        | 0.1   |                 | 4.5   | \ \          |

| Nominal Low End of Range           | Measurement mode, $f = 900 \text{ MHz}$ , $P_{IN} = -52 \text{ dBm}$                     | 0.32  |                 | 0.48  | v            |

| Nominal High End of Range          | Measurement mode, $f = 900 \text{ MHz}$ , $P_{IN} = -32 \text{ dBH}$                     | 3.44  |                 | 3.52  | V            |

| Source/Sink Current                |                                                                                          | 3.44  | 40              | 3.32  |              |

|                                    | VOUT held at V <sub>s</sub> /2, to 1% change                                             |       | 48              |       | mA<br>V/vs   |

| Slew Rate Rising                   | C <sub>L</sub> = open                                                                    |       | 60              |       | V/µs         |

| Slew Rate Falling                  | C <sub>L</sub> = open                                                                    |       | 5               |       | V/µs         |

| Rise Time, 10% to 90%              | 0.2 V to 1.8 V, CLPF = Open                                                              |       | 45              |       | ns           |

| Fall Time, 90% to 10%              | 1.8 V to 0.2 V, CLPF = Open                                                              |       | 0.4             |       | μs           |

| Wideband Noise                     | CLPF = 1000 pF, f <sub>SPOT</sub> ≤ 100 kHz                                              |       | 70              |       | nV/√Hz       |

| VSET INTERFACE                     | Pin VSET                                                                                 |       |                 |       | .,           |

| Nominal Input Voltage Range        | To ±1 dB error                                                                           | 0.5   |                 | 3.75  | V            |

| Input Resistance                   | 6.000 MH                                                                                 | 4.5   | 68              | -,    | kΩ           |

| Scaling (Log Slope)                | f = 900 MHz                                                                              | 46    | 50              | 54    | mV/dB        |

| Scaling (Log Intercept)            | f = 900 MHz, into 1:4 balun                                                              | -64   | -60             | -56   | dBm          |

| VOLTAGE DEFENSE                    | D: VIDE                                                                                  | -77   | -73             | -69   | dBV          |

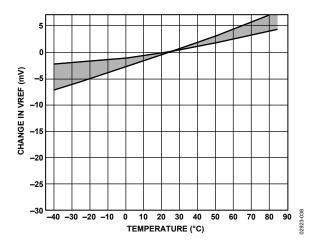

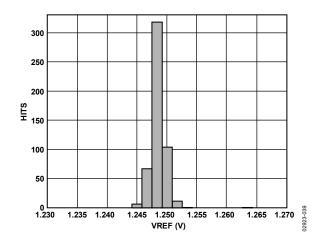

| VOLTAGE REFERENCE                  | Pin VREF                                                                                 | 4.555 | 4.0-            | 4     | <b> </b> , , |

| Output Voltage                     | 25°C                                                                                     | 1.225 | 1.25            | 1.275 | V            |

| Temperature Sensitivity            | $-40^{\circ}\text{C} \le \text{T}_{A} \le +85^{\circ}\text{C}$                           |       | 0.08            |       | mV/°C        |

| Output Resistance                  |                                                                                          |       | 8               |       | Ω            |

| Parameter                    | Test Conditions/Comments                                                                   | Min   | Тур        | Max | Unit     |

|------------------------------|--------------------------------------------------------------------------------------------|-------|------------|-----|----------|

| RMS TARGET INTERFACE         | Pin VTGT                                                                                   |       |            |     |          |

| Nominal Input Voltage Range  | Measurement range = $60 \text{ dB}$ , to $\pm 1 \text{ dB}$ error                          | 0.625 |            | 2.5 | V        |

| Input Bias Current           | VTGT = 1.25 V                                                                              |       | -28        |     | μΑ       |

|                              | VTGT = 0 V                                                                                 |       | -52        |     | μΑ       |

| Incremental Input Resistance |                                                                                            |       | 52         |     | kΩ       |

| POWER-DOWN INTERFACE         | Pin PWDN                                                                                   |       |            |     |          |

| Logic Level to Enable        | Logic low enables                                                                          |       |            | 1   | V        |

| Logic Level to Disable       | Logic high disables                                                                        | 3     |            |     | V        |

| Input Current                | Logic high                                                                                 |       | 230        |     | μΑ       |

|                              | Logic low                                                                                  |       | 5          |     | μΑ       |

| Enable Time                  | From PWDN low to VOUT within 10% of final value, CLPF = 1000 pF                            |       | 14.5       |     | ns       |

| Disable Time                 | From PWDN high to VOUT within 10% of final value, CLPF = 1000 pF                           |       | 2.5        |     | μs       |

| POWER SUPPLY INTERFACE       | Pin VPOS                                                                                   |       |            |     |          |

| Supply Voltage               |                                                                                            | 4.5   | 5          | 5.5 | V        |

| Quiescent Current            |                                                                                            |       | 20         | 22  | mA       |

| Supply Current               | When disabled                                                                              |       | 0.2        |     | mA       |

| 900 MHz                      |                                                                                            |       |            |     |          |

| Dynamic Range                | Error referred to best-fit line (linear regression)                                        |       |            |     |          |

|                              | ±1.0 dB linearity, CW input                                                                |       | 65         |     | dB       |

|                              | ±0.5 dB linearity, CW input                                                                |       | 62         |     | dB       |

| Deviation vs. Temperature    | Deviation from output at 25°C                                                              |       |            |     |          |

|                              | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}, P_{IN} = -45 \text{ dBm}$       |       | -1.7       |     | dB       |

|                              | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}, P_{IN} = -20 \text{ dBm}$       |       | -1.4       |     | dB       |

|                              | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}, P_{IN} = +5 \text{ dBm}$        |       | -1.0       |     | dB       |

| Logarithmic Slope            |                                                                                            | 46    | 50         | 54  | mV/dB    |

| Logarithmic Intercept        |                                                                                            | -64   | -60        | -56 | dBm      |

| Deviation from CW Response   | 5.5 dB peak-to-rms ratio (IS95 reverse link)                                               |       | 0.2        |     | dB       |

| ·                            | 12.0 dB peak-to-rms ratio (W-CDMA 4 channels)                                              |       | 0.2        |     | dB       |

|                              | 18.0 dB peak-to-rms ratio (W-CDMA 15 channels)                                             |       | 0.5        |     | dB       |

| 1.9 GHz                      |                                                                                            |       |            |     |          |

| Dynamic Range                | Error referred to best-fit line (linear regression)                                        |       |            |     |          |

|                              | ±1 dB linearity, CW input                                                                  |       | 65         |     | dB       |

|                              | ±0.5 dB linearity, CW input                                                                |       | 62         |     | dB       |

| Deviation vs. Temperature    | Deviation from output at 25°C                                                              |       |            |     |          |

| ·                            | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}, P_{IN} = -45 \text{ dBm}$       |       | -0.6       |     | dB       |

|                              | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}, P_{IN} = -20 \text{ dBm}$       |       | -0.5       |     | dB       |

|                              | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}, P_{\text{IN}} = +5 \text{ dBm}$ |       | -0.3       |     | dB       |

| Logarithmic Slope            |                                                                                            |       | 51         |     | mV/dB    |

| Logarithmic Intercept        |                                                                                            |       | -59        |     | dBm      |

| Deviation from CW Response   | 5.5 dB peak-to-rms ratio (IS95 reverse link)                                               |       | 0.2        |     | dB       |

| ·                            | 12.0 dB peak-to-rms ratio (W-CDMA 4 channels)                                              |       | 0.2        |     | dB       |

|                              | 18.0 dB peak-to-rms ratio (W-CDMA 15 channels)                                             |       | 0.5        |     | dB       |

| 2.2 GHz                      |                                                                                            |       |            |     |          |

| Dynamic Range                | Error referred to best-fit line (linear regression)                                        |       |            |     |          |

| ,                            | ±1.0 dB linearity, CW input                                                                |       | 65         |     | dB       |

|                              | ±0.5 dB linearity, CW input                                                                |       | 65         |     | dB       |

| Deviation vs. Temperature    | Deviation from output at 25°C                                                              |       |            |     |          |

| ·                            | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}, P_{IN} = -45 \text{ dBm}$       |       | -1.8       |     | dB       |

|                              | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}, P_{IN} = -20 \text{ dBm}$       |       | -1.6       |     | dB       |

|                              | $-40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}, P_{IN} = +5 \text{ dBm}$                 |       | -1.3       |     | dB       |

| Logarithmic Slope            |                                                                                            |       | 50.5       |     | mV/dB    |

| Logarithmic Intercept        |                                                                                            |       | -61        |     | dBm      |

|                              |                                                                                            |       |            |     |          |

|                              | 5.5 dB peak-to-rms ratio (IS95 reverse link)                                               |       | 02         |     | l dR     |

| Deviation from CW Response   | 5.5 dB peak-to-rms ratio (IS95 reverse link) 12.0 dB peak-to-rms ratio (W-CDMA 4 channels) |       | 0.2<br>0.2 |     | dB<br>dB |

| Parameter Test Conditions/Comments |                                                                                         | Min | Тур  | Max | Unit  |

|------------------------------------|-----------------------------------------------------------------------------------------|-----|------|-----|-------|

| 2.7 GHz                            |                                                                                         |     |      |     |       |

| Dynamic Range                      | Error referred to best-fit line (linear regression)                                     |     |      |     |       |

|                                    | ±1.0 dB linearity, CW input                                                             |     | 63   |     | dB    |

|                                    | ±0.5 dB linearity, CW input                                                             |     | 62   |     | dB    |

| Deviation vs. Temperature          | Deviation from output at 25°C                                                           |     |      |     |       |

|                                    | $-40^{\circ}$ C < T <sub>A</sub> < $+85^{\circ}$ C, P <sub>IN</sub> = $-40 \text{ dBm}$ |     | -5.3 |     | dB    |

|                                    | $-40^{\circ}$ C < T <sub>A</sub> < $+85^{\circ}$ C, P <sub>IN</sub> = $-15$ dBm         |     | -5.5 |     | dB    |

|                                    | $-40^{\circ}$ C < T <sub>A</sub> < $+85^{\circ}$ C, P <sub>IN</sub> = $+5$ dBm          |     | -4.8 |     | dB    |

| Logarithmic Slope                  |                                                                                         |     | 50.5 |     | mV/dB |

| Logarithmic Intercept              |                                                                                         |     | -58  |     | dBm   |

| Deviation from CW Response         | 5.5 dB peak-to-rms ratio (IS95 reverse link)                                            |     | 0.2  |     | dB    |

|                                    | 12.0 dB peak-to-rms ratio (W-CDMA 4 channels)                                           |     | 0.2  |     | dB    |

|                                    | 18.0 dB peak-to-rms ratio (W-CDMA 15 channels)                                          |     | 0.4  |     | dB    |

| 3.65 GHz                           | Single-ended drive <sup>3</sup>                                                         |     |      |     |       |

| Dynamic Range                      | Error referred to best-fit line (linear regression)                                     |     |      |     |       |

|                                    | ±1.0 dB linearity, CW input                                                             |     | 51   |     | dB    |

|                                    | ±0.5 dB linearity, CW input                                                             |     | 50   |     | dB    |

| Deviation vs. Temperature          | Deviation from output at 25°C                                                           |     |      |     |       |

|                                    | $-40^{\circ}$ C < T <sub>A</sub> < $+85^{\circ}$ C, P <sub>IN</sub> = $-35$ dBm         |     | -3   |     | dB    |

|                                    | $-40^{\circ}$ C < T <sub>A</sub> < $+85^{\circ}$ C, P <sub>IN</sub> = $-15$ dBm         |     | -3.5 |     | dB    |

|                                    | $-40^{\circ}$ C < T <sub>A</sub> < $+85^{\circ}$ C, P <sub>IN</sub> = $+10 \text{ dBm}$ |     | -3.5 |     | dB    |

| Logarithmic Slope                  |                                                                                         |     | 51.7 |     | mV/dB |

| Logarithmic Intercept              |                                                                                         |     | -45  |     | dBm   |

<sup>1:4</sup> balun transformer, M/A-COM ETC 1.6-4-2-3.

2 See Figure 48.

3 See Figure 50.

4 The limitation of the high end of the power range is due to the test equipment not the device under test.

## **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                            | Rating          |

|--------------------------------------|-----------------|

| Supply Voltage VPOS                  | 5.5 V           |

| Input Power (Into Input of Device)   | 15 dBm          |

| Equivalent Voltage                   | 2 V rms         |

| Internal Power Dissipation           | 500 mW          |

| $	heta_{JA}$                         | 125°C/W         |

| Maximum Junction Temperature         | 125°C           |

| Operating Temperature Range          | -40°C to +85°C  |

| Storage Temperature Range            | −65°C to +150°C |

| Lead Temperature (Soldering, 60 sec) | 300°C           |

|                                      |                 |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

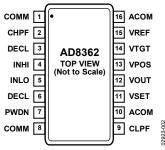

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin<br>No. | Mnemonic   | Description                                                                                                                                                                              | Equivalent<br>Circuit |

|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 1, 8       | COMM       | Common Connection. Connect via low impedance to system common.                                                                                                                           |                       |

| 2          | CHPF       | Input HPF. Connect to common via a capacitor to determine 3 dB point of input signal high-pass filter.                                                                                   |                       |

| 3, 6       | DECL       | Decoupling Terminals for INHI and INLO. Connect to common via a large capacitance to complete input circuit.                                                                             |                       |

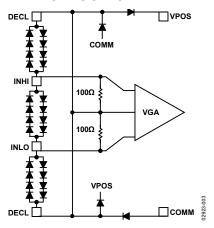

| 4, 5       | INHI, INLO | Differential Signal Input Terminals. Input Impedance = $200 \Omega$ . Can also be driven single-ended, in which case, the input impedance reduces to $100 \Omega$ .                      | Circuit A             |

| 7          | PWDN       | Disable/Enable Control Input. Apply logic high voltage to shut down the AD8362.                                                                                                          |                       |

| 9          | CLPF       | Connection for Ground Referenced Loop Filter Integration (Averaging) Capacitor.                                                                                                          |                       |

| 10, 16     | ACOM       | Analog Common Connection for Output Amplifier.                                                                                                                                           |                       |

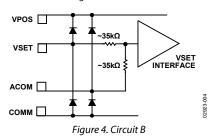

| 11         | VSET       | Setpoint Input. Connect directly to VOUT for measurement mode. Apply setpoint input to this pin for controller mode.                                                                     | Circuit B             |

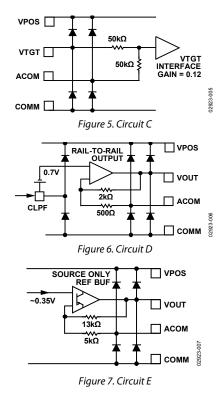

| 12         | VOUT       | RMS Output. In measurement mode, VOUT is normally connected directly to VSET.                                                                                                            | Circuit C             |

| 13         | VPOS       | Connect to 5 V Power Supply.                                                                                                                                                             |                       |

| 14         | VTGT       | The logarithmic intercept voltage is proportional to the voltage applied to this pin. The use of a lower target voltage increases the crest factor capacity. Normally connected to VREF. | Circuit D             |

| 15         | VREF       | General-Purpose Reference Voltage Output of 1.25 V. Usually connected only to VTGT.                                                                                                      | Circuit E             |

# **EQUIVALENT CIRCUITS**

Figure 3. Circuit A

## TYPICAL PERFORMANCE CHARACTERISTICS

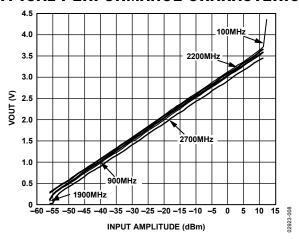

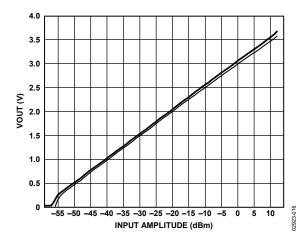

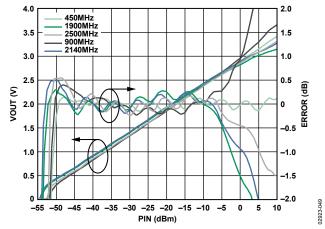

Figure 8. Output Voltage (VOUT) vs. Input Amplitude (dBm), Frequencies: 100 MHz, 900 MHz, 1900 MHz, 2200 MHz, and 2700 MHz; Sine Wave, Differential Drive

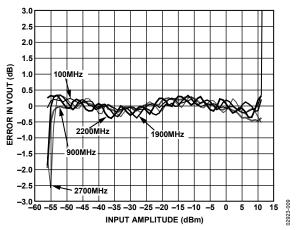

Figure 9. Logarithmic Law Conformance vs. Input Amplitude, Frequencies: 100 MHz, 900 MHz, 1900 MHz, 2200 MHz, and 2700 MHz; Sine Wave, Differential Drive

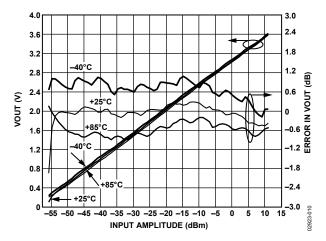

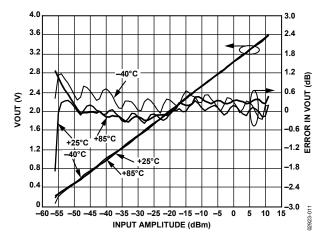

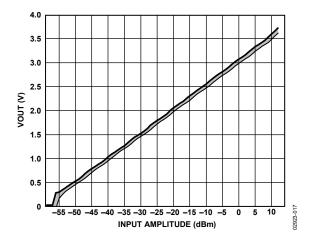

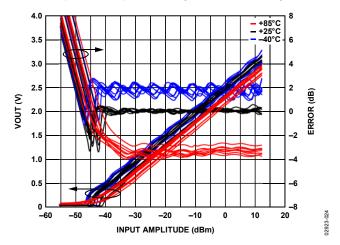

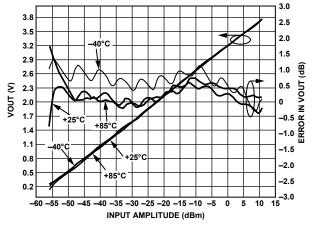

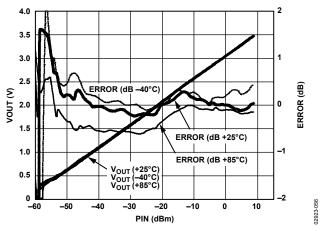

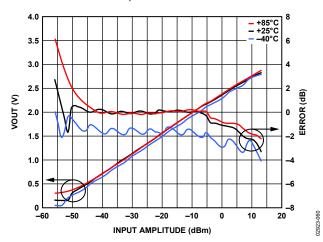

Figure 10. VOUT and Law Conformance vs. Input Amplitude, Frequency 900 MHz, Sine Wave, Temperatures:  $-40^{\circ}$ C,  $+25^{\circ}$ C, and  $+85^{\circ}$ C

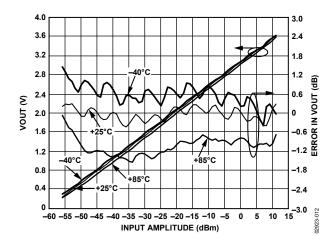

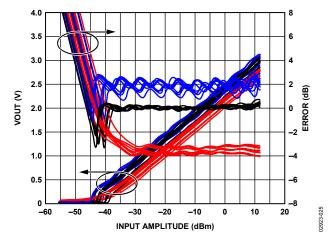

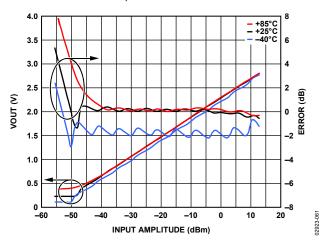

Figure 11. VOUT and Law Conformance vs. Input Amplitude, Frequency 1900 MHz, Sine Wave, Temperatures: –40°C, +25°C, and +85°C

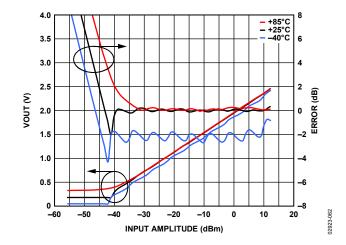

Figure 12. VOUT and Law Conformance vs. Input Amplitude, Frequency 2200 MHz, Sine Wave, Temperatures: -40°C, +25°C, and +85°C

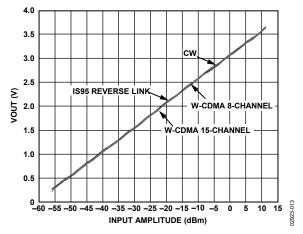

Figure 13. VOUT vs. Input Amplitude with Different Waveforms, CW, IS95 Reverse Link, W-CDMA 8-Channel, W-CDMA 15-Channel, Frequency 900 MHz

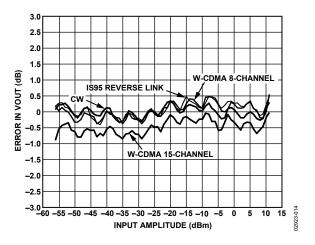

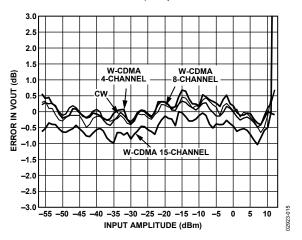

Figure 14. Output Error from CW Linear Reference vs. Input Amplitude with Different Waveforms, CW, IS95 Reverse Link, W-CDMA 8-Channel, W-CDMA 15-Channel, Frequency 900 MHz,  $V_{TGT} = 1.25 \text{ V}$

Figure 15. Output Error from CW Linear Reference vs. Input Amplitude with Different W-CDMA Channel Loading, 4-Channel, 8-Channel, 15-Channel, Frequency 2200 MHz, V<sub>TGT</sub> = 1.25 V

Figure 16. VOUT vs. Input Amplitude, 3 Sigma to Either Side of Mean, Sine Wave, Frequency 900 MHz, Part-to-Part Variation

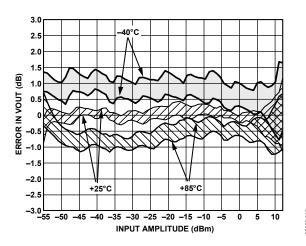

Figure 17. VOUT vs. Input Amplitude, 3 Sigma to Either Side of Mean, Sine Wave, Frequency 1900 MHz, Part-to-Part Variation

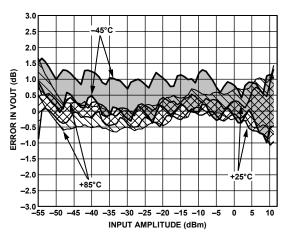

Figure 18. Logarithmic Law Conformance vs. Input Amplitude, 3 Sigma to Either Side of Mean, Sine Wave, Frequency 900 MHz, Temperatures:  $-40^{\circ}$ C,  $+25^{\circ}$ C, and  $+85^{\circ}$ C

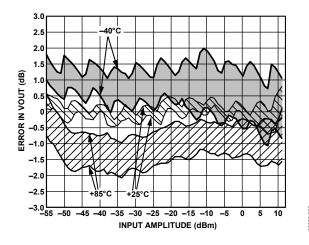

Figure 19. Logarithmic Law Conformance vs. Input Amplitude, 3 Sigma to Either Side of Mean, Sine Wave, Frequency 1900 MHz, Temperatures: –40°C, +25°C, and +85°C

2923-019

Figure 20. Logarithmic Law Conformance vs. Input Amplitude, 3 Sigma to Either Side of Mean, Sine Wave, Frequency 2200 MHz, Temperatures:  $-40^{\circ}\text{C}$ ,  $+25^{\circ}\text{C}$ , and  $+85^{\circ}\text{C}$

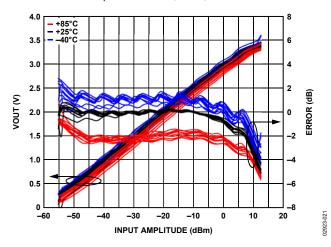

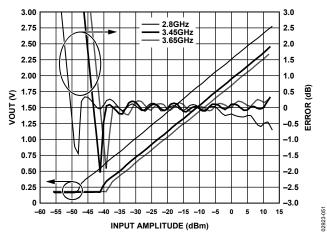

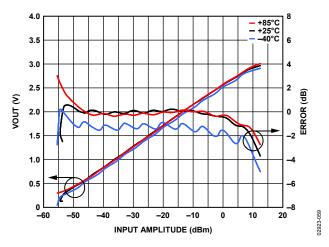

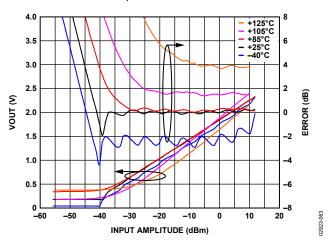

Figure 21. VOUT and Law Conformance vs. Input Amplitude for 15 Devices, Frequency 2350 MHz, Sine Wave, Temperatures: -40°C, +25°C, and +85°C, No Temperature Compensation, Single-Ended Drive, See Figure 50

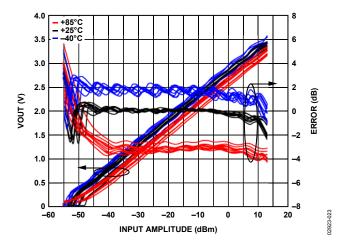

Figure 22. VOUT and Law Conformance vs. Input Amplitude for 15 Devices, Frequency 2600 MHz, Sine Wave, Temperatures: -40°C, +25°C, and +85°C, No Temperature Compensation, Single-Ended Drive, See Figure 50

Figure 23. VOUT and Law Conformance vs. Input Amplitude for 15 Devices, Frequency 2800 MHz, Sine Wave, Temperatures: –40°C, +25°C, and +85°C, No Temperature Compensation, Single-Ended Drive, See Figure 50

Figure 24. VOUT and Law Conformance vs. Input Amplitude for 15 Devices, Frequency 3450 MHz, Sine Wave, Temperatures: –40°C, +25°C, and +85°C, No Temperature Compensation, Single-Ended Drive, See Figure 50

Figure 25. VOUT and Law Conformance vs. Input Amplitude for 15 Devices, Frequency 3650 MHz, Sine Wave, Temperatures: –40°C, +25°C, and +85°C, No Temperature Compensation, Single-Ended Drive, See Figure 50

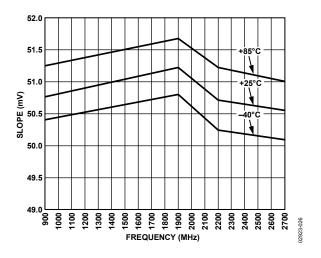

Figure 26. Logarithmic Slope vs. Frequency, Temperatures:  $-40^{\circ}\text{C}$ ,  $+25^{\circ}\text{C}$ , and  $+85^{\circ}\text{C}$

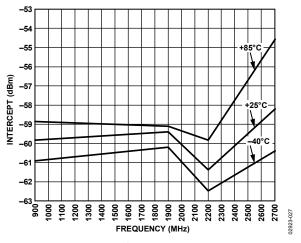

Figure 27. Logarithmic Intercept vs. Frequency, Temperatures:  $-40^{\circ}\text{C}$ ,  $+25^{\circ}\text{C}$ , and  $+85^{\circ}\text{C}$

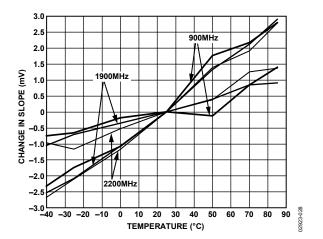

Figure 28. Change in Logarithmic Slope vs. Temperature, 3 Sigma to Either Side of Mean, Frequencies: 900 MHz, 1900 MHz, and 2200 MHz

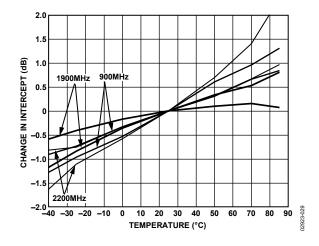

Figure 29. Change in Logarithmic Intercept vs. Temperature, 3 Sigma to Either Side of Mean, Frequencies: 900 MHz, 1900 MHz, and 2200 MHz

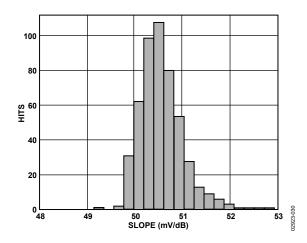

Figure 30. Slope Distribution, Frequency 900 MHz

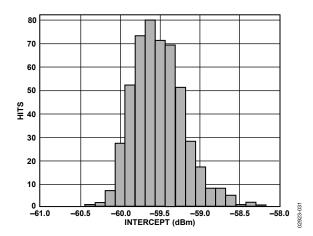

Figure 31. Logarithmic Intercept Distribution, Frequency 900 MHz

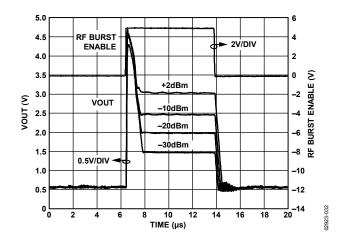

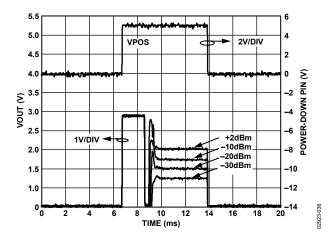

Figure 32. Output Response to RF Burst Input for Various RF Input Levels, Carrier Frequency 900 MHz, CLPF = Open

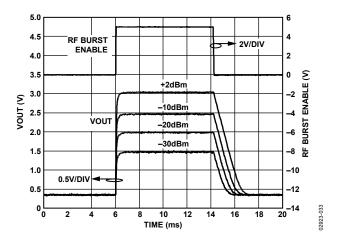

Figure 33. Output Response to RF Burst Input for Various RF Input Levels, Carrier Frequency 900 MHz, CLPF = 0.1 µF

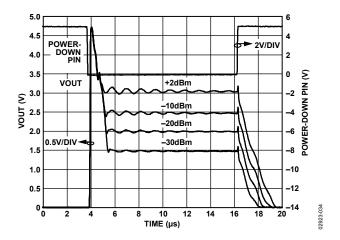

Figure 34. Output Response Using Power-Down Mode for Various RF Input Levels, Carrier Frequency 900 MHz, CLPF = 0

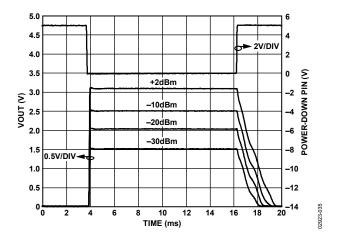

Figure 35. Output Response Using Power-Down Mode for Various RF Input Levels, Carrier Frequency 900 MHz, CLPF = 0.1 μF

Figure 36. Output Response to Gating on Power Supply for Various RF Input Levels, Carrier Frequency 900 MHz, CLPF = 0

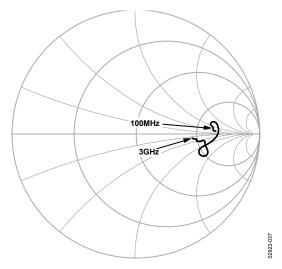

Figure 37. INHI, INLO Differential Input Impedance, 100 MHz to 3 GHz

Figure 38. Change in VREF vs. Temperature, 3 Sigma to Either Side of Mean

Figure 39. VREF Distribution

### CHARACTERIZATION SETUP

### **EQUIPMENT**

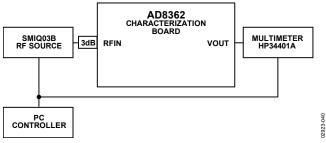

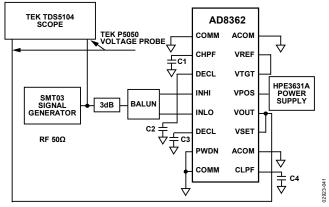

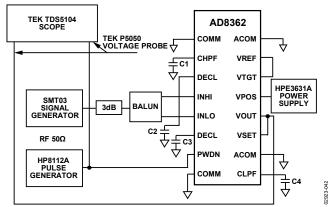

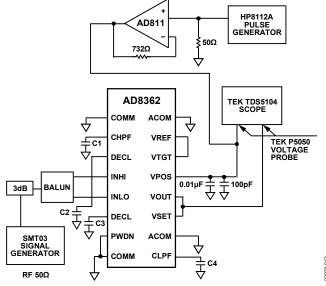

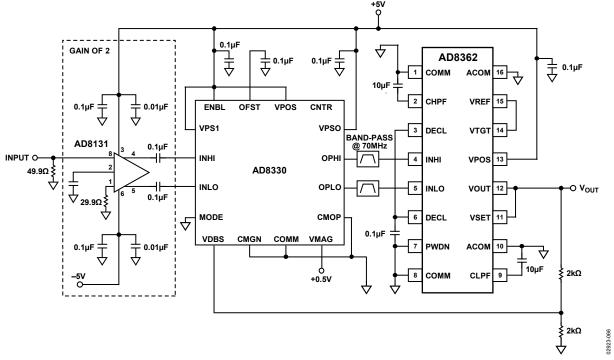

The general hardware configuration used for most of the AD8362 characterization is shown in Figure 40. The signal source is a Rohde & Schwarz SMIQ03B. A 1:4 balun transformer is used to transform the single-ended RF signal to differential form. For frequencies above 3.0 GHz, an Agilent 8521A signal source was used. For the response measurements in Figure 32 and Figure 33, the configuration shown in Figure 41 is used. For Figure 34 and Figure 35, the configuration shown in Figure 42 is used. For Figure 36, the configuration shown in Figure 43 is used.

Figure 40. Primary Characterization Setup

### **ANALYSIS**

The slope and intercept are derived using the coefficients of a linear regression performed on data collected in its central operating range. Error is stated in two forms: error from the linear response to the CW waveform and output delta from 25°C performance.

The error from linear response to the CW waveform is the decibel difference in output from the ideal output defined by the conversion gain and output reference. This is a measure of the linearity of the device response to both CW and modulated waveforms. The error in dB is calculated by

$$Error (dB) = \frac{VOUT - Slope \times (P_{IN} - P_Z)}{Slope}$$

(1)

where  $P_Z$  is the x intercept, expressed in dBm.

Error from the linear response to the CW waveform is not a measure of absolute accuracy because it is calculated using the slope and intercept of each device. However, it verifies the linearity and the effect of modulation on the device response. Error from the 25°C performance uses the performance of a given device and waveform type as the reference; it is predominantly a measurement of output variation with temperature.

Figure 41. Response Measurement Setup for Modulated Pulse

Figure 42. Response Measurement Setup for Power-Down Step

Figure 43. Response Measurement Setup for Gated Supply

### CIRCUIT DESCRIPTION

The AD8362 is a fully calibrated, high accuracy, rms-to-dc converter providing a measurement range of over 65 dB. It is capable of operating from signals as low in frequency as a few hertz to at least 3.8 GHz. Unlike earlier rms-to-dc converters, the response bandwidth is completely independent of the signal magnitude. The -3 dB point occurs at about 3.5 GHz. The capacity of this device to accurately measure waveforms having a high peak-to-rms ratio (crest factor) is independent of either the signal frequency or its absolute magnitude, over a wide range of conditions.

This unique combination allows the AD8362 to be used as a calibrated RF wattmeter covering a power ratio of >1,000,000:1, a power controller in closed-loop systems, a general-purpose rms-responding voltmeter, and in many other low frequency applications.

The device comprises the core elements of a high performance AGC loop (see Figure 44), laser-trimmed during manufacturing to close tolerances while fully operational at a test frequency of 100 MHz. Its linear, wideband VGA provides a general voltage gain,  $G_{\text{SET}}$ ; this can be controlled in a precisely exponential (linear-in-dB) manner over the full 68 dB range from -25 dB to +43 dB by a voltage,  $V_{\text{SET}}$ . However, to provide adequate guardbanding, only the central 60 dB of this range, from -21 dB to +39 dB, is normally used. The Adjusting VTGT to Accommodate Signals with Very High Crest Factors section shows how this basic range can be shifted up or down.

Figure 44. Basic Structure of the AD8362

The VGA gain has the form

$$G_{SET} = G_0 \exp(-V_{SET}/V_{GNS}) \tag{2}$$

where:

*G*<sup>0</sup> is a basic fixed gain.

$V_{GNS}$  is a scaling voltage that defines the gain slope (the dB change per volt). Note that the gain decreases with  $V_{SET}$ .

The VGA output is

$$V_{SIG} = G_{SET}V_{IN} = G_OV_{IN} \exp(-V_{SET}/V_{GNS})$$

(3)

where  $V_{IN}$  is the ac voltage applied to the input terminals of the AD8362.

As explained in the Recommended Input Coupling section, the input drive can either be single-sided or differential, although dynamic range is maximized with a differential input drive. The effect of high frequency imbalances when using a single-sided drive is less apparent at low frequencies (from 50 Hz to 500 MHz), but the peak input voltage capacity is always halved relative to differential operation.

### **SQUARE LAW DETECTION**

The output of the variable gain amplifier ( $V_{SIG}$ ) is applied to a wideband square law detector, which provides a true rms response to this alternating signal that is essentially independent of waveform. Its output is a fluctuating current ( $I_{SQU}$ ) that has a positive mean value. This current is integrated by an on-chip capacitance ( $C_F$ ), which is usually augmented by an external capacitance (CLPF) to extend the averaging time. The resulting voltage is buffered by a gain of 5, dc-coupled amplifier whose rail-to-rail output (VOUT) can be used for either measurement or control purposes.

In most applications, the AGC loop is closed via the setpoint interface pin, VSET, to which the VGA gain control voltage on VOUT is applied. In measurement modes, the closure is direct and local by a simple connection from the output of the VOUT pin to the VSET pin. In controller modes, the feedback path is around some larger system, but the operation is the same.

The fluctuating current ( $I_{SQU}$ ) is balanced against a fixed setpoint target current ( $I_{TGT}$ ) using current mode subtraction. With the exact integration provided by the capacitor(s), the AGC loop equilibrates when

$$MEAN(I_{SOU}) = I_{TGT}$$

(4)

The current,  $I_{TGT}$ , is provided by a second-reference squaring cell whose input is the amplitude-target voltage  $V_{ATG}$ . This is a fraction of the voltage VTGT applied to a special interface, which accepts this input at the VTGT pin. Because the two squaring cells are electrically identical and are carefully implemented in the IC, process and temperature-dependent variations in the detailed behavior of the two square-law functions cancel.

Accordingly, VTGT (and its fractional part  $V_{ATG}$ ) determines the output that must be provided by the VGA for the AGC loop to settle. Because the scaling parameters of the two squarers are accurately matched, it follows that Equation 4 is satisfied only when

$$MEAN(V_{SIG}^2) = V_{ATG}^2$$

(5)

In a formal solution, extract the square root of both sides to provide an explicit value for the root-mean-square (rms) value. However, it is apparent that by forcing this identity through varying the VGA gain and extracting the mean value by the filter provided by the capacitor(s), the system inherently establishes the relationship

$$rms(V_{SIG}) = V_{ATG} \tag{6}$$

Substituting the value of V<sub>SIG</sub> from Equation 3,

$$rms[G_OV_{IN} \exp(-VSET/V_{GNS})] = V_{ATG}$$

(7)

As a measurement device,  $V_{\rm IN}$  is the unknown quantity and all other parameters can be fixed by design. To solve Equation 7,

$$rms[G_OV_{IN}/V_{ATG}] = exp(VSET/V_{GNS})$$

(8)

therefore,

$$VSET = V_{GNS} \log[\text{rms}(V_{IN})/V_Z]$$

(9)

The quantity  $V_Z = V_{ATG}/G_O$  is defined as the intercept voltage because VSET must be 0 when rms  $(V_{IN}) = V_Z$ .

When connected as a measurement device, the output of the buffer is tied directly to VSET, which closes the AGC loop. Making the substitution VOUT = VSET and changing the log base to 10, as needed in a decibel conversion,

$$VOUT = V_{SLP} \log_{10}[rms(V_{IN})/V_Z]$$

(10)

where  $V_{SLP}$  is the slope voltage, that is, the change in output voltage for each decade of change in the input amplitude. Note that  $V_{SLP} = V_{GNS} \log (10) = 2.303 \ V_{GNS}$ .

In the AD8362,  $V_{\text{SLP}}$  is laser-trimmed to 1 V using a 100 MHz test signal. Because a decade corresponds to 20 dB, this slope can also be stated as 50 mV/dB. The Altering the Slope section explains how the effective value of  $V_{\text{SLP}}$  can be altered by the user. The intercept,  $V_Z$ , is also laser-trimmed to 224  $\mu V$  (–60 dBm relative to 50  $\Omega$ ). In an ideal system, VOUT would cross zero for an rms input of that value. In a single-supply realization of the function, VOUT cannot run fully down to ground; here,  $V_Z$  is the extrapolated value.

### **VOLTAGE vs. POWER CALIBRATION**

The AD8362 can be used as an accurate rms voltmeter from arbitrarily low frequencies to microwave frequencies. For low frequency operation, the input is usually specified either in volts rms or in dBV (decibels relative to 1 V rms).

At high frequencies, signal levels are commonly specified in power terms. In these circumstances, the source and termination impedances are an essential part of the overall scaling. For this condition, the output voltage can be expressed as

$$VOUT = SLOPE \times (P_{IN} - P_Z) \tag{11}$$

where  $P_{IN}$  and the intercept  $P_Z$  are expressed in dBm.

In practice, the response deviates slightly from the ideal straight line suggested by Equation 11. This deviation is called the law conformance error. In defining the performance of high accuracy measurement devices, it is customary to provide plots of this error. In general terms, it is computed by extracting the best straight line to the measured data using linear regression over a substantial region of the dynamic range and under clearly specified conditions.

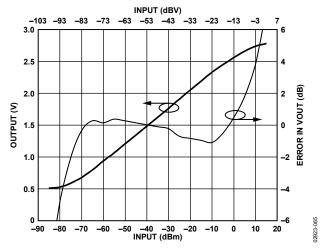

Figure 45. Output Voltage and Law Conformance Error at  $T_A = -40^{\circ}\text{C}$ ,  $+25^{\circ}\text{C}$ , and  $+85^{\circ}\text{C}$

Figure 45 shows the output of the circuit of Figure 47 over the full input range. The agreement with the ideal function (law conformance) is also shown. This was determined by linear regression on the data points over the central portion of the transfer function for the +25°C data.

The error at -40°C, +25°C, and +85°C was then calculated by subtracting the ideal output voltage at each input signal level from the actual output and dividing this quantity by the mean slope of the regression equation to provide a measurement of the error in decibels (scaled on the right-hand axis of Figure 45).

The error curves generated in this way reveal not only the deviations from the ideal transfer function at a nominal temperature, but also the additional errors caused by temperature changes. Notice that there is a small temperature dependence in the intercept (the vertical position of the error plots).

Figure 45 further reveals a periodic ripple in the conformance curves. This is due to the interpolation technique used to select the signals from the attenuator, not only at discrete tap points, but also anywhere in between, thus providing continuous attenuation values. The selected signal is then applied to the 3.5 GHz, 40 dB fixed gain amplifier in the remaining stages of the VGA of the AD8362.

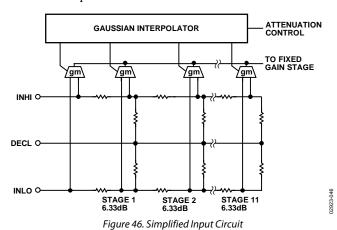

An approximate schematic of the signal input section of the AD8362 is shown in Figure 46. The ladder attenuator is composed of 11 sections (12 taps), each of which progressively attenuates the input signal by 6.33 dB. Each tap is connected to a variable transconductance cell whose bias current determines the signal weighting given to that tap. The interpolator determines which stages are active by generating a discrete set of bias currents, each having a Gaussian profile. These are arranged to move from left to right, thereby determining the attenuation applied to the input signal as the gain is progressively lowered over the 69.3 dB range under control of the VSET input. The detailed manner in which the transconductance of adjacent stages varies as the virtual tap point slides along the attenuator accounts for the ripple observed in the conformance curves. Its magnitude is slightly temperature dependent and varies with frequency (see Figure 10, Figure 11, and Figure 12). Notice that the system responses to signal inputs at INHI and INLO are not completely independent; these pins do not constitute a fully floating differential input.

### **OFFSET ELIMINATION**

To address the small dc offsets that arise in the VGA, an offsetnulling loop is used. The high-pass corner frequency of this loop is internally preset to 1 MHz, which is sufficiently low for most high frequency applications. When using the AD8362 in low frequency applications, the corner frequency can be reduced as needed by the addition of a capacitor from the CHPF pin to ground having a nominal value of  $200~\mu\text{F/Hz}$ .

For example, to lower the high-pass corner frequency to 150 Hz, a capacitance of 1.33  $\mu F$  is required. The offset voltage varies depending on the actual gain at which the VGA is operating, and thus on the input signal amplitude.

Baseline variations of this sort are a common aspect of all VGAs, but they are more evident in the AD8362 because of the method of its implementation, which causes the offsets to ripple along the gain axis with a period of 6.33 dB. When an excessively large value of CHPF is used, the offset correction process can lag the more rapid changes in the gain of the VGA, which in turn can increase the time required for the loop to fully settle for a given steady input amplitude.

### TIME-DOMAIN RESPONSE OF THE CLOSED LOOP

The external low-pass averaging capacitance (CLPF) added at the output of the squaring cell is chosen to provide adequate filtering of the fluctuating detected signal. The optimum value depends on the application; as a guideline, a value of roughly 900  $\mu F/Hz$  should be used. For example, a capacitance of 5  $\mu F$  provides adequate filtering down to 180 Hz. Note that the fluctuation in the quasi-dc output of a squaring cell operating on a sine wave input is a raised cosine at twice the signal frequency, easing this filtering function.

In the standard connections for the measurement mode, the VSET pin is tied to VOUT. For small changes in input amplitude (a few decibels), the time-domain response of this loop is essentially linear, with a 3 dB low-pass corner frequency of nominally  $f_{LP} = 1/(2\pi \times \text{CLPF} \times 1100)$ . Internal time delays around this local loop set the minimum recommended value of this capacitor to about 300 pF, resulting in an  $f_{LP}$  of approximately 500 kHz.

When large and abrupt changes of input amplitude occur, the loop response becomes nonlinear and exhibits slew rate limitations.

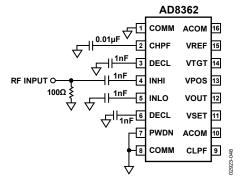

# **OPERATION IN RF MEASUREMENT MODE**BASIC CONNECTIONS

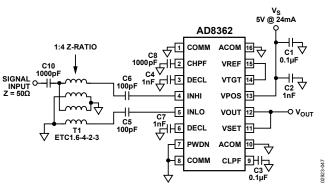

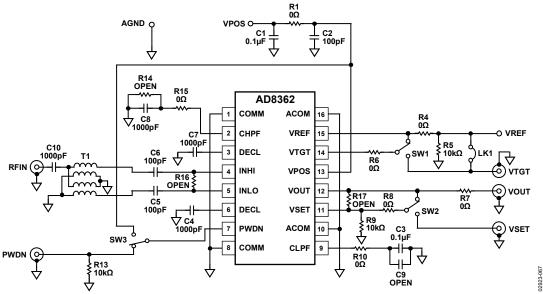

Basic connections for operating the AD8362 in measurement mode are shown in Figure 47. While the AD8362 requires a single supply of nominally 5 V, its performance is essentially unaffected by variations of up to  $\pm 10\%$ .

The supply is connected to the VPOS pin using the decoupling network also displayed in Figure 47. The capacitors used in this network must provide a low impedance over the full frequency range of the input and should be placed as close as possible to the VPOS pin. Two different capacitors are used in parallel to reduce the overall impedance because these have different resonant frequencies. The measurement accuracy is not critically dependent on supply decoupling because the high frequency signal path is confined to the relevant input pins. Lead lengths from both DECL pins to ground and from INHI/INLO to the input coupling capacitors should be as short as possible. All COMM pins should also connect directly to the ground plane.

To place the device in measurement mode, connect VOUT to VSET and connect VTGT directly to VREF.

### **DEVICE DISABLE**

The AD8362 is disabled by a logic high on the PWDN pin, which can be directly grounded for continuous operation. When enabled, the supply current is nominally 20 mA and essentially independent of supply voltage and input signal strength. When powered down by a logic low on PWDN, the supply current is reduced to 230  $\mu$ A.

### RECOMMENDED INPUT COUPLING

The full dynamic range of the AD8362, particularly at very high frequencies (above 500 MHz), is realized only when the input is presented to it in differential (balanced) form. In Figure 47, a transmission line balun is used at the input. Having a 1:4 impedance ratio (1:2 turns ratio), the 200  $\Omega$  differential input resistance of the AD8362 becomes 50  $\Omega$  at the input to the balun.

Figure 47. Basic Connections for RF Power Measurement

The balun outputs must be ac-coupled to the input of the AD8362. The balun used in this example (M/A-COM ETC 1.6-4-2-3) is specified for operation from 0.5 GHz to 2.5 GHz.

If a center-tapped, flux-coupled transformer is used, connect the center tap to the DECL pins, which are biased to the same potential as the inputs (approximately 3.6 V).

At lower frequencies where impedance matching is not necessary, the AD8362 can be driven from a low impedance differential source, remembering the inputs must be ac-coupled.

### **Choosing Input Coupling Capacitors**

As noted, the inputs must be ac-coupled. The input coupling capacitors combine with the 200  $\Omega$  input impedance to create an input high pass corner frequency equal to

$$f_{HP} = 1/(200 \times \pi \times C_C) \tag{12}$$

Typically,  $f_{\text{HP}}$  should be set to at least one tenth the lowest input frequency of interest.

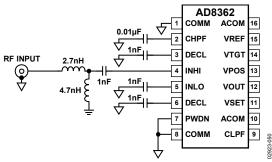

### Single-Ended Input Drive

As previously noted, the input stages of the AD8362 are optimally driven from a fully balanced source, which should be provided wherever possible. In many cases, unbalanced sources can be applied directly to one or the other of the two input pins. The chief disadvantage of this driving method is a 10 dB to 15 dB reduction in dynamic range at frequencies above 500 MHz.

Figure 48 illustrates one of many ways of coupling the signal source to the AD8362. Because the input pins are biased to about 3.6 V (for  $V_S = 5$  V), dc-blocking capacitors are required when driving from a grounded source. For signal frequencies >5 MHz, a value of 1 nF is adequate. While either INHI or INLO can be used, INHI is chosen here.

Figure 48. Input Coupling from a Single-Ended 50  $\Omega$  Source

An external 100  $\Omega$  shunt resistor combines with the internal 100  $\Omega$  single-ended input impedance to provide a broadband 50  $\Omega$  match. The unused input (in this case, INLO) is ac-coupled to ground. Figure 49 shows the transfer function of the AD8362 at various frequencies when the RF input is driven single-ended. The results show that transfer function linearity at the top end of the range is degraded by the single-ended drive.

Figure 49. Transfer Function at Various Frequencies when the RF Input is Driven Single-Ended

Figure 50. Input Matching for Operation at Frequencies ≥2.7 GHz

For operation at frequencies  $\geq$ 2.7 GHz, some additional components are required to match the AD8362 input to 50  $\Omega$  (see Figure 50). As the operating frequency increases, there is also corresponding shifting in the operating power range (see Figure 51).

Figure 51. Transfer Function at Various Frequencies ≥2.7 GHz when the RF Input is Driven Single-Ended

### **OPERATION AT LOW FREQUENCIES**

In conventional rms-to-dc converters based on junction techniques, the effective signal bandwidth is proportional to the signal amplitude. In contrast, the 3.5 GHz VGA bandwidth in the AD8362 is independent of its gain. Because this amplifier is internally dc-coupled, the system is also used as a high accuracy rms voltmeter at low frequencies, retaining its temperature-stable, decibel-scaled output (for example, in seismic, audio, and sonar instrumentation).

While the AD8362 can be operated at arbitrarily low frequencies, an ac-coupled input interface must be maintained. In such cases, the input coupling capacitors should be large enough so that the lowest frequency components of the signal to be included in the measurement are minimally attenuated. For example, for a 3 dB reduction at 1.5 kHz, capacitances of 1  $\mu F$  are needed because the input resistance is 100  $\Omega$  at each input pin (200  $\Omega$  differentially), and the calculation is  $1/(2\pi \times 1.5 \ k\Omega \times 100) = 1 \ \mu F$ . In addition, to lower the high-pass corner frequency of the VGA, a large capacitor must be connected between the CHPF pin and ground (see the Choosing a Value for CHPF section).

More information on the operation of the AD8362 and other RF power detectors at low frequency is available in AN-691 Application Note, *Operation of RF Detector Products at Low Frequency*.

### **CHOOSING A VALUE FOR CHPF**

The 3.5 GHz VGA of the AD8362 includes an offset cancellation loop, which introduces a high-pass filter effect in its transfer function. To measure the amplitude of the input signal properly, the corner frequency ( $f_{HP}$ ) of this filter must be well below that of the lowest input signal in the desired measurement bandwidth frequency. The required value of the external capacitor is given by

$$CHPF = 1/(2\pi \times 800 \times f_{HP}) \tag{13}$$

For operation at frequencies as low as 100 kHz, set  $f_{\text{HP}}$  to approximately 25 kHz (CHPF = 8 nF). For frequencies above approximately 2 MHz, no external capacitance is required because there is adequate internal capacitance on this node.

### **CHOOSING A VALUE FOR CLPF**

In the standard connections for the measurement mode, the VSET pin is tied to VOUT. For small changes in input amplitude such as a few decibels, the time-domain response of this loop is essentially linear with a 3 dB low-pass corner frequency of nominally  $f_{LP} = 1/(2\pi \times \text{CLPF} \times 1100)$ . Internal time delays around this local loop set the minimum recommended value of this capacitor to about 300 pF, making  $f_{LP} = 500 \text{ kHz}$ .

For operation at lower signal frequencies, or whenever the averaging time needs to be longer, use

$$CLPF = 1/(2\pi \times f_{LP} \times 1100) \tag{14}$$

When the input signal exhibits large crest factors, such as a CDMA or W-CDMA signal, CLPF must be much larger than might seem necessary.

This is due to the presence of significant low frequency components in the complex, pseudorandom modulation, which generates fluctuations in the output of the AD8362. Increasing CLPF also increases the step response of the AD8362 to a change at its input.

Table 5 shows recommended values of CLPF for popular modulation schemes. In each case, CLPF is increased until residual output noise falls below 50 mV. A 10% to 90% step response to an input step is also listed. Where the increased response time is unacceptably high, CLPF must be reduced. If the output of the AD8362 is sampled by an ADC, averaging in the digital domain can further reduce the residual noise.

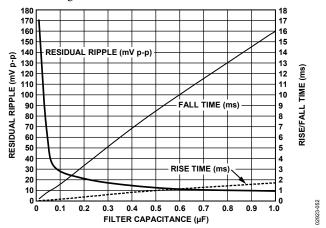

Figure 52 shows how residual ripple and rise/fall time vary with filter capacitance when the AD8362 is driven by a single carrier W-CDMA signal (Test Model 1-64) at 2140 MHz.

Figure 52. Residual Ripple, Rise and Fall Time vs. Filter Capacitance, Single Carrier W-CDMA Input Signal, Test Model 1-64

Table 5. Recommended CLPF Values for Various Modulation Schemes

|                                                         |              |        |                 | Response Time (Rise/Fall) |

|---------------------------------------------------------|--------------|--------|-----------------|---------------------------|

| Modulation Scheme/Standard                              | Crest Factor | CLPF   | Residual Ripple | 10% to 90%                |

| W-CDMA , Single-Carrier, Test Model 1-64                | 12.0 dB      | 0.1 μF | 28 mV p-p       | 171 μs/1.57 ms            |

| W-CDMA, 4-Carrier, Test Model 1-64                      | 11.0 dB      | 0.1 μF | 20 mV p-p       | 162 μs/1.55 ms            |

| CDMA2000, Single-Carrier, 9CH Test Model                | 9.1 dB       | 0.1 μF | 38 mV p-p       | 179 μs /1.55 ms           |

| CDMA2000, 3-Carrier, 9CH Test Model                     | 11.0 dB      | 0.1 μF | 29 mV p-p       | 171 μs/1.55 ms            |

| WiMAX 802.16 (64QAM, 256 Subcarriers, 10 MHz Bandwidth) | 14.0 dB      | 0.1 μF | 30 mV p-p       | 157 μs/1.47 ms            |

# ADJUSTING VTGT TO ACCOMMODATE SIGNALS WITH VERY HIGH CREST FACTORS

An external direct connection between VREF (1.25 V) and VTGT sets up the internal target voltage, which is the rms voltage that must be provided by the VGA to balance the AGC feedback loop.

In the default scheme, the VREF of 1.25 V positions this target to  $0.06 \times 1.25$  V = 75 mV. In principle, however, VTGT can be driven by voltages that are larger or smaller than 75 mV. This technique can be used to move the intercept, which increases or decreases the input sensitivity of the device, or to improve the accuracy when measuring signals with large crest factors.

For example, if this pin is supplied from VREF via a simple resistive attenuator of 1 k $\Omega$ :1 k $\Omega$ , the output required from the VGA is halved to 37.5 mV rms. Under these conditions, the effective headroom in the signal path that drives the squaring cell is doubled. In principle, this doubles the peak crest factor that can be handled by the system.

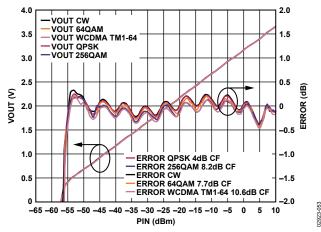

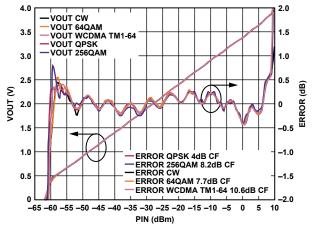

Figure 53 and Figure 54 show the effect of varying VTGT on measurement accuracy when the AD8362 is swept with a series of signals with different crest factors, varying from CW with a crest factor of 3 dB, to a W-CDMA carrier (Test Model 1-64) with a crest factor of 10.6 dB. The crest factors of each signal are listed in the plots. In Figure 53, VTGT is set to its nominal value of 1.25 V, while in Figure 54, it is reduced to 0.625 V.

Figure 53. Transfer Function and Law Conformance for Signals with Varying Crest Factors, VTGT = 1.25 V

Figure 54. Transfer Function and Law Conformance for Signals with Varying Crest Factors, VTGT = 0.625 V, CLPF =  $0.1 \mu$ F

Reducing VTGT also reduces the intercept. More significant in this case, however, is the behavior of the error curves. Note that in Figure 54 all of the error curves sit on one another, while in Figure 53, there is some vertical spreading. This suggests that VTGT should be reduced in those applications where a wide range of input crest factors is expected. As noted, VTGT can also be increased above its nominal level of 1.25 V. While this can be used to increase the intercept, it would have the undesirable effect of degrading measurement accuracy in situations where the crest factor of the signal being measured varies significantly.

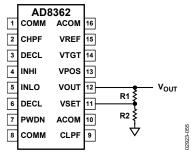

### **ALTERING THE SLOPE**

None of the changes in operating conditions discussed so far affects the logarithmic slope ( $V_{SLP}$ ) in Equation 10. This can readily be altered by controlling the fraction of VOUT that is fed back to the setpoint interface at the VSET pin. When the full signal from VOUT is applied to VSET, the slope assumes its nominal value of 50 mV/dB. It can be increased by including a voltage divider between these pins, as shown in Figure 55.

Figure 55. External Network to Raise Slope

Moderately low resistance values should be used to minimize scaling errors due to the 70 k $\Omega$  input resistance at the VSET pin. This resistor string also loads the output, and it eventually reduces the load-driving capabilities if very low values are used. To calculate the resistor values, use

$$R1 = R2' (S_D/50 - 1) (15)$$

where:

$S_D$  is the desired slope, expressed in mV/dB. R2' is the value of R2 in parallel with 70 k $\Omega$ .

For example, using  $RI = 1.65 \text{ k}\Omega$  and  $R2 = 1.69 \text{ k}\Omega$  ( $R2' = 1.649 \text{ k}\Omega$ ), the nominal slope is increased to 100 mV/dB. Note, however, that doubling the slope in this manner reduces the maximum input signal to approximately -10 dBm because of the limited swing of VOUT (4.9 V with a 5 V power supply).

# TEMPERATURE COMPENSATION AND REDUCTION OF TRANSFER FUNCTION RIPPLE

The transfer function ripple and intercept drift of the AD8362 can be reduced using two techniques detailed in Figure 57. CLPF is reduced from its nominal value. For broadband-modulated input signals, this results in increased noise at the output that is fed back to the VSET pin.

The noise contained in this signal causes the gain of the VGA to fluctuate around a central point, moving the wiper of the Gaussian Interpolator back and forth on the R-2R ladder.

Because the gain-control voltage is constantly moving across at least one of taps of the Gaussian Interpolator, the relationship between the rms signal strength of the VGA output and the VGA control voltage becomes independent of the VGA gain control ripple (see Figure 56). The signal being applied to the squaring cell is now lightly AM modulated. However, this does not change the peak-to-average ratio of the signal.

Figure 56. Transfer Function and Linearity with Combined Ripple Reduction and Temperature Compensation Circuits, Frequency = 2.14 GHz,

Single-Carrier W-CDMA, Test Model 1-64

Because of the reduced filter capacitor, the rms voltage appearing at the output of the error amplifier now contains significant peak-to-peak noise. While it is critical to feed this signal back to the VGA gain control input with the noise intact, the rms voltage going to the external measurement node can be filtered using a simple filter to yield a largely noise-free rms voltage.

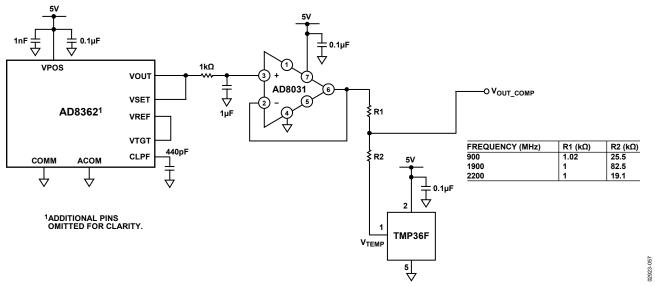

The circuit shown in Figure 57 also incorporates a temperature sensor that compensates temperature drift of the intercept. Because the temperature drift varies with frequency, the amount of compensation required must also be varied using R1 and R2.

These compensation techniques are discussed in more detail in AN-653 Application Note, *Improving Temperature, Stability, and Linearity of High Dynamic Range RMS RF Power Detectors.*

Figure 57. Temperature Compensation and Reduction of Transfer Function Ripple

## TEMPERATURE COMPENSATION AT VARIOUS WIMAX FREQUENCIES UP TO 3.8 GHz

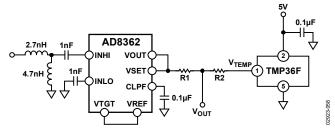

The AD8362 is ideally suited for measuring WiMAX type signals because crest factor changes in the modulation scheme have very little effect on the accuracy of the measurement. However, at higher frequencies, the AD8362 drifts more over temperature often making temperature compensation necessary. Temperature compensation is possible because the part-to-part variation over temperature is small, and temperature change only causes a shift in the AD8362 intercept. Typically, users choose to compensate for temperature changes digitally. However, temperature compensation is possible using an analog temperature sensor. Because the drift of the output voltage is due mainly to intercept shift, the whole transfer function tends to drop with increasing temperature, while the slope remains quite stable. This makes the temperature drift independent of input level. Compensating the drift based on a particular input level (for example, -15 dBm), holds up well over the dynamic range.

Figure 59 through Figure 63 show these results. The compensation is simple and relies on the TMP36 precision temperature sensor driving one side of the resistor divider as the AD8362 drives the other side. The output is at the junction of the two resistors (see Figure 58). At 25°C, TMP36 has an output voltage of 750 mV and a temperature coefficient of 10 mV/°C. As the temperature increases, the voltage from the AD8362 drops and the voltage from the TMP36 rises. R1 and R2 are chosen so the voltage at the center of the resistor divider remains steady over temperature. In practice, R2 is much larger than R1 so that the output voltage from the circuit is close to the voltage of the  $V_{\text{OUT}}$ pin. The resistor ratio R2/R1 is determined by the temperature drift of the AD8362 at the frequency of interest. To calculate the values of R1 and R2, first calculate the drift at a particular input level, -15 dBm in this case. To do this, calculate the average drift over the temperature range from 25°C to 85°C. Using the following equation, the average drift in dB/°C is obtained.

$$dB/^{\circ}C = \frac{dBError}{\Delta Temperature}$$

(16)

In this example, the drift of the AD8362 from 25°C to 85°C is -2.07 dB and the temperature delta is 60°C, which results in -0.0345 dB/°C drift. This temperature drift in dB/°C is converted to mV/°C through multiplication by the logarithmic slope (51 mV/dB at 2350 MHz). The result is -1.76 mV/°C. The following equation calculates the values of R1 and R2:

$$\frac{R2}{R1} = \frac{10 \text{ mV/°C}}{AD8362 \text{ Drift(mV/°C)}}$$

(17)

Table 6 shows the resultant values for R2 and R1 for frequencies ranging from 2350 MHz to 3650 MHz. Figure 59 through Figure 63 show the performance over temperature for the AD8362 with temperature compensation at frequencies across the WiMAX band. The compensation factor chosen optimizes temperature drift in the 25°C to 85°C range. This can be altered depending on the temperature requirements for the application.

Table 6. Recommended Resistor Values for Temperature Compensation at Various Frequencies

| Freq.<br>(MHz) | Average<br>Drift at<br>–15 dBm<br>(dB/°C) | Slope<br>(mV/dB) | Average<br>Drift at<br>–15 dBm<br>(mV/°C) | R1<br>(kΩ) | R2<br>(kΩ) |

|----------------|-------------------------------------------|------------------|-------------------------------------------|------------|------------|

| 2350           | -0.0345                                   | 51               | -1.7600                                   | 4.99       | 28         |

| 2600           | -0.0440                                   | 51.45            | -2.2639                                   | 4.99       | 22.1       |

| 2800           | -0.0486                                   | 51.68            | -2.5102                                   | 4.99       | 20         |

| 3450           | -0.0531                                   | 51.61            | -2.7402                                   | 4.99       | 18.2       |

| 3650           | -0.0571                                   | 51.73            | -2.9544                                   | 4.99       | 16.9       |

Figure 58. AD8362 with Temperature Compensation Circuit

Figure 59. AD8362 VOUT and Error with Linear Temperature Compensation at 2350 MHz

Figure 60. AD8362 VOUT and Error with Linear Temperature Compensation at 2600 MHz

Figure 61. AD8362 VOUT and Error with Linear Temperature Compensation at 2800 MHz

Figure 62. AD8362 VOUT and Error with Linear Temperature Compensation at 3450 MHz

Figure 63. AD8362 VOUT and Error with Linear Temperature Compensation at 3650 MHz, Temperature Compensation is Optimized for 85  $^{\circ}$ C

### **OPERATION IN CONTROLLER MODE**

The AD8362 provides a controller mode feature at the VOUT pin. Using VSET for the setpoint voltage, it is possible for the AD8362 to control subsystems such as power amplifiers (PAs), VGAs, or variable voltage attenuators (VVAs), which have output power that decreases monotonically with respect to their (increasing) gain control signal.

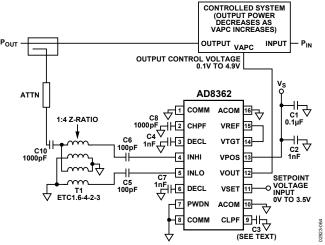

Figure 64. Basic Connections for Controller Mode Operation

To operate in controller mode, the link between VSET and VOUT is broken. A setpoint voltage is applied to the VSET input, while VOUT is connected to the gain control terminal of the VGA, and the AD8362 RF input is connected to the output of the VGA (generally using a directional coupler or power splitter and some additional attenuation). Based on the defined relationship between VOUT and the RF input signal when the device is in measurement mode, the AD8362 adjusts the voltage on VOUT (VOUT is now an error amplifier output) until the level at the RF input corresponds to the applied VSET. For example, in a closed loop system, if VSET is set to 3 V, VOUT increases or decreases until the input signal is equal to 0 dBm. This relationship follows directly from the measurement mode transfer function (see Figure 10, Figure 11, and Figure 12). Therefore, when the AD8362 operates in controller mode, there is no defined relationship between VSET and VOUT. VOUT settles to a value that results in balance between the input signal levels appearing at INHI/INLO and VSET.

For this output power control loop to be stable, a ground-referenced capacitor must be connected to the CLPF pin. This capacitor integrates the internal error current that is present when the loop is not balanced.