## **Data Sheet**

### FEATURES

Full 16-bit performance 3 V and 5 V single-supply operation Low 0.625 mW power dissipation 1 μs settling time Unbuffered voltage output capable of driving 60 kΩ loads directly SPI-/QSPI-/MICROWIRE-compatible interface standards Power-on reset clears DAC output to 0 V (unipolar mode) 5 kV HBM ESD classification Low glitch: 1.1 nV-sec

#### **APPLICATIONS**

Digital gain and offset adjustment Automatic test equipment Data acquisition systems Industrial process control

#### **GENERAL DESCRIPTION**

The AD5541/AD5542 are single, 16-bit, serial input, voltage output digital-to-analog converters (DACs) that operate from a single 2.7 V to 5.5 V supply. The DAC output range extends from 0 V to  $V_{REF}$ .

The DAC output range extends from 0 V to V<sub>REF</sub> and is guaranteed monotonic, providing 1 LSB INL accuracy at 16 bits without adjustment over the full specified temperature range of –40°C to +85°C. Offering unbuffered outputs, the AD5541/AD5542 achieve a 1  $\mu s$  settling time with low power consumption and low offset errors. Providing a low noise performance of 11.8 nV/ $\sqrt{Hz}$  and low glitch, the AD5541/AD5542 is suitable for deployment across multiple end systems.

The AD5542 can be operated in bipolar mode, which generates a  $\pm V_{\text{REF}}$  output swing. The AD5542 also includes Kelvin sense connections for the reference and analog ground pins to reduce layout sensitivity.

The AD5541/AD5542 utilize a versatile 3-wire interface that is compatible with SPI, QSPI<sup>™</sup>, MICROWIRE<sup>™</sup> and DSP interface standards. The AD5541/AD5542 are available in 8-lead and 14-lead SOIC packages.

#### Rev. F

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# 2.7 V to 5.5 V, Serial-Input, Voltage-Output, 16-Bit DACs

# AD5541/AD5542

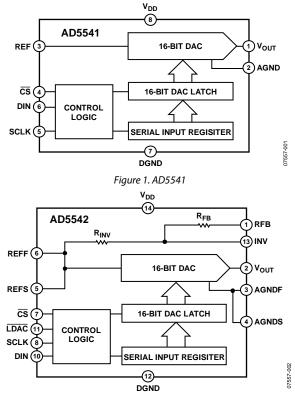

#### FUNCTIONAL BLOCK DIAGRAMS

Figure 2. AD5542

| Table 1.             |                                                                  |

|----------------------|------------------------------------------------------------------|

| Part No.             | Description                                                      |

| AD5541A/AD5542A      | Single, 16-bit unbuffered <i>nano</i> DAC™,<br>±1 LSB INL, LFCSP |

| AD5024/AD5044/AD5064 | Quad 12-/14-/16-bit <i>nano</i> DAC,<br>±1 LSB INL, TSSOP        |

| AD5062               | Single, 16-bit <i>nano</i> DAC, ±1 LSB INL,<br>SOT-23            |

| AD5063               | Single, 16-bit <i>nano</i> DAC, ±1 LSB INL,<br>SOT-23            |

#### **PRODUCT HIGHLIGHTS**

- Single-Supply Operation. The AD5541 and AD5542 are fully specified and guaranteed for a single 2.7 V to 5.5 V supply.

- 2. Low Power Consumption. These parts consume typically 0.625 mW with a 5 V supply and 0.375 mV at 3 V.

- 3. 3-Wire Serial Interface.

- 4. Unbuffered Output Capable of Driving 60 k $\Omega$  Loads. This reduces power consumption because there is no internal buffer to drive.

- 5. Power-On Reset Circuitry.

# TABLE OF CONTENTS

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| General Description                          |

| Functional Block Diagrams1                   |

| Product Highlights 1                         |

| Revision History                             |

| Specifications                               |

| Timing Characteristics 4                     |

| Absolute Maximum Ratings                     |

| ESD Caution                                  |

| Pin Configurations and Function Descriptions |

| Typical Performance Characteristics          |

|                                              |

| Terminology 10                               |

| Terminology 10   Theory of Operation 11      |

|                                              |

| Theory of Operation                          |

### **REVISION HISTORY**

### 3/12—Rev. E to Rev. F

| Change to Figure 199        |  |

|-----------------------------|--|

| Changes to Ordering Guide17 |  |

#### 3/11-Rev. D to Rev. E

#### 2/11-Rev. C to Rev. D

| Changes to Features Section, General Description Section, |   |

|-----------------------------------------------------------|---|

| Product Highlights Section                                | 1 |

| Added Table 1; Renumbered Sequentially                    | 1 |

| Added Output Noise Spectral Density Parameter and Output  |   |

| Noise Parameter, Table 2                                  | 3 |

| Changes to Ordering Guide1                                | 7 |

### 4/10-Rev. B to Rev. C

| Changes to General Description Section1 |

|-----------------------------------------|

| Changes to Features List 1              |

| Bipolar Output Operation                | 12 |

|-----------------------------------------|----|

| Output Amplifier Selection              | 12 |

| Force Sense Amplifier Selection         | 12 |

| Reference and Ground                    | 12 |

| Power-On Reset                          | 13 |

| Power Supply and Reference Bypassing    | 13 |

| Microprocessor Interfacing              | 14 |

| AD5541/AD5542 to ADSP-21xx Interface    | 14 |

| AD5541/AD5542 to 68HC11/68L11 Interface | 14 |

| AD5541/AD5542 to MICROWIRE Interface    | 14 |

| AD5541/AD5542 to 80C51/80L51 Interface  | 14 |

| Applications Information                | 15 |

| Optocoupler Interface                   | 15 |

| Decoding Multiple AD5541/AD5542s        | 15 |

| Outline Dimensions                      | 16 |

| Ordering Guide                          |    |

| Changes to Product Highlights                  | 1  |

|------------------------------------------------|----|

| Changes to Table 1                             | 3  |

| Changes to Table 3                             |    |

| Changes to Figure 16, Figure 17, and Figure 19 |    |

| Changes to Theory of Operations Section        | 11 |

| Changes to Microprocessor Interfacing Section  | 14 |

| Changes to Outline Dimensions                  | 16 |

| Changes to Ordering Guide                      | 17 |

### 8/08—Rev. A to Rev. B

| Updated Format                            | Universal |

|-------------------------------------------|-----------|

| Changes to Timing Characteristics Section | 4         |

| Changes to Table 3                        |           |

| Updated Outline Dimensions                |           |

| Changes to Ordering Guide                 |           |

10/99—Rev. 0 to Rev. A

# **SPECIFICATIONS**

$V_{\text{DD}} = 2.7 \text{ V to } 5.5 \text{ V}, 2.5 \text{ V} \le V_{\text{REF}} \le V_{\text{DD}}, \text{AGND} = \text{DGND} = 0 \text{ V}. \text{ All specifications } T_{\text{A}} = T_{\text{MIN}} \text{ to } T_{\text{MAX}}, \text{ unless otherwise noted}.$

#### Table 2.

| Parameter <sup>1</sup>                     | Min        | Тур     | Max                      | Unit      | Test Conditions                                                      |

|--------------------------------------------|------------|---------|--------------------------|-----------|----------------------------------------------------------------------|

| STATIC PERFORMANCE                         |            |         |                          |           |                                                                      |

| Resolution                                 | 16         |         |                          | Bits      |                                                                      |

| Relative Accuracy (INL)                    |            | ±0.5    | ±1.0                     | LSB       | L, C grades                                                          |

|                                            |            | ±0.5    | ±2.0                     | LSB       | B, J grades                                                          |

|                                            |            | ±0.5    | ±4.0                     | LSB       | A grade                                                              |

| Differential Nonlinearity (DNL)            |            | ±0.5    | ±1.0                     | LSB       | Guaranteed monotonic                                                 |

|                                            |            |         | ±1.5                     | LSB       | J grade                                                              |

| Gain Error                                 |            | +0.5    | ±2                       | LSB       | $T_A = 25^{\circ}C$                                                  |

|                                            |            |         | ±3                       | LSB       |                                                                      |

| Gain Error Temperature Coefficient         |            | ±0.1    |                          | ppm/°C    |                                                                      |

| Unipolar Zero Code Error                   |            | ±0.3    | ±0.7                     | LSB       | $T_A = 25^{\circ}C$                                                  |

|                                            |            |         | ±1.5                     | LSB       |                                                                      |

| Unipolar Zero Code Temperature Coefficient |            | ±0.05   |                          | ppm/°C    |                                                                      |

| AD5542                                     |            |         |                          |           |                                                                      |

| Bipolar Resistor Matching                  |            | 1.000   |                          | Ω/Ω       | $R_{FB}/R_{INV}$ , typically $R_{FB} = R_{INV} = 28 \text{ k}\Omega$ |

| -                                          |            | ±0.0015 | ±0.0076                  | %         | Ratio error                                                          |

| Bipolar Zero Offset Error                  |            | ±1      | ±5                       | LSB       | $T_A = 25^{\circ}C$                                                  |

|                                            |            |         | ±б                       | LSB       |                                                                      |

| Bipolar Zero Temperature Coefficient       |            | ±0.2    |                          | ppm/°C    |                                                                      |

| Bipolar Zero Code Offset Error             |            | ±1      | ±5                       | LSB       | $T_A = 25^{\circ}C$                                                  |

|                                            |            |         | ±б                       | LSB       |                                                                      |

| Bipolar Gain Error                         |            | +1      | ±5                       | LSB       | $T_A = 25^{\circ}C$                                                  |

|                                            |            |         | ±6                       | LSB       |                                                                      |

| Bipolar Gain Temperature Coefficient       |            | ±0.1    | _0                       | ppm/°C    |                                                                      |

| OUTPUT CHARACTERISTICS                     |            |         |                          | - -···/ - |                                                                      |

| Output Voltage Range                       | 0          |         | V <sub>REF</sub> – 1 LSB | v         | Unipolar operation                                                   |

|                                            | $-V_{REF}$ |         | V <sub>REF</sub> – 1 LSB | v         | AD5542 bipolar operation                                             |

| Output Voltage Settling Time               | NLI        | 1       | NLI                      | μs        | To $1/2$ LSB of FS, C <sub>L</sub> = 10 pF                           |

| Slew Rate                                  |            | 17      |                          | V/µs      | $C_L = 10 \text{ pF}$ , measured from 0% to 63%                      |

| Digital-to-Analog Glitch Impulse           |            | 1.1     |                          | nV-sec    | 1 LSB change around the major carry                                  |

| Digital Feedthrough                        |            | 0.2     |                          | nV-sec    | All 1s loaded to DAC, $V_{REF} = 2.5 V$                              |

| DAC Output Impedance                       |            | 6.25    |                          | kΩ        | Tolerance typically 20%                                              |

| Output Noise Spectral Density              |            | 11.8    |                          | nV/√Hz    | DAC code = $0x8400$ , frequency = 1 kHz                              |

| Output Noise                               |            | 0.134   |                          | μV p-p    | 0.1 Hz to 10 Hz                                                      |

| Power Supply Rejection Ratio               |            | 0.151   | ±1.0                     | LSB       | $\Delta V_{\text{DD}} \pm 10\%$                                      |

| DAC REFERENCE INPUT                        |            |         | 1.0                      | LJD       |                                                                      |

| Reference Input Range                      | 2.0        |         | V <sub>DD</sub>          | v         |                                                                      |

| Reference Input Resistance <sup>2</sup>    | 9          |         | ♥ DD                     | kΩ        | Unipolar operation                                                   |

| hererence input hesistance                 | 7.5        |         |                          | kΩ        | AD5542, bipolar operation                                            |

| LOGIC INPUTS                               | ,.5        |         |                          | 1122      |                                                                      |

| Input Current                              |            |         | ±1                       | μA        |                                                                      |

| Input Low Voltage, V <sub>INL</sub>        |            |         | 0.8                      | V         |                                                                      |

| Input High Voltage, V <sub>INH</sub>       | 2.4        |         | 0.0                      | v         |                                                                      |

| Input Capacitance <sup>3</sup>             | 2.7        |         | 10                       | pF        |                                                                      |

| Hysteresis Voltage <sup>3</sup>            |            | 0.15    |                          | V         |                                                                      |

| REFERENCE <sup>3</sup>                     |            | 0.15    |                          | v         |                                                                      |

|                                            |            | 2.2     |                          |           |                                                                      |

| Reference –3 dB Bandwidth                  |            | 2.2     |                          | MHz       | All 1s loaded                                                        |

| Reference Feedthrough                      |            | 1       |                          | mV p-p    | All 0s loaded, $V_{REF} = 1 V p-p at 100 kHz$                        |

| Signal-to-Noise Ratio                      |            | 92      |                          | dB        |                                                                      |

| Reference Input Capacitance                |            | 26      |                          | pF        | Code 0x0000                                                          |

|                                            | 1          | 26      |                          | pF        | Code 0xFFFF                                                          |

| Parameter <sup>1</sup> | Min | Тур   | Max   | Unit | Test Conditions         |

|------------------------|-----|-------|-------|------|-------------------------|

| POWER REQUIREMENTS     |     |       |       |      | Digital inputs at rails |

| V <sub>DD</sub>        | 2.7 |       | 5.5   | V    |                         |

| I <sub>DD</sub>        |     | 125   | 150   | μΑ   |                         |

| Power Dissipation      |     | 0.625 | 0.825 | mW   |                         |

<sup>1</sup> Temperature ranges are as follows: A, B, C versions: -40°C to +85°C; J, L versions: 0°C to 70°C. <sup>2</sup> Reference input resistance is code-dependent, minimum at 0x8555.

<sup>3</sup> Guaranteed by design, not subject to production test.

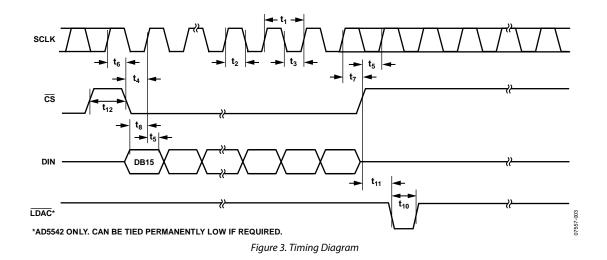

### TIMING CHARACTERISTICS

+85°C, unless otherwise noted.

#### Table 3.

| Parameter <sup>1, 2</sup> | Limit | Unit    | Description                                                                    |  |  |  |  |

|---------------------------|-------|---------|--------------------------------------------------------------------------------|--|--|--|--|

| f <sub>sclk</sub>         | 25    | MHz max | SCLK cycle frequency                                                           |  |  |  |  |

| t <sub>1</sub>            | 40    | ns min  | SCLK cycle time                                                                |  |  |  |  |

| t <sub>2</sub>            | 20    | ns min  | SCLK high time                                                                 |  |  |  |  |

| t <sub>3</sub>            | 20    | ns min  | SCLK low time                                                                  |  |  |  |  |

| t <sub>4</sub>            | 10    | ns min  | CS low to SCLK high setup                                                      |  |  |  |  |

| t <sub>5</sub>            | 15    | ns min  | CS high to SCLK high setup                                                     |  |  |  |  |

| t <sub>6</sub>            | 30    | ns min  | SCLK high to $\overline{CS}$ low hold time                                     |  |  |  |  |

| t <sub>7</sub>            | 20    | ns min  | SCLK high to $\overline{\text{CS}}$ high hold time                             |  |  |  |  |

| t <sub>8</sub>            | 15    | ns min  | Data setup time                                                                |  |  |  |  |

| t <sub>9</sub>            | 4     | ns min  | Data hold time ( $V_{INH} = 90\%$ of $V_{DD}$ , $V_{INL} = 10\%$ of $V_{DD}$ ) |  |  |  |  |

| t <sub>9</sub>            | 7.5   | ns min  | Data hold time $(V_{INH} = 3V, V_{INL} = 0V)$                                  |  |  |  |  |

| t <sub>10</sub>           | 30    | ns min  | LDAC pulse width                                                               |  |  |  |  |

| t <sub>11</sub>           | 30    | ns min  | CS high to LDAC low setup                                                      |  |  |  |  |

| t <sub>12</sub>           | 30    | ns min  | CS high time between active periods                                            |  |  |  |  |

<sup>1</sup> Guaranteed by design and characterization. Not production tested

<sup>2</sup> All input signals are specified with  $t_R = t_F = 1 \text{ ns/V}$  and timed from a voltage level of  $(V_{INL} + V_{INH})/2$ .

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 4.

| Parameter                                         | Rating                            |  |  |

|---------------------------------------------------|-----------------------------------|--|--|

| V <sub>DD</sub> to AGND                           | –0.3 V to +6 V                    |  |  |

| Digital Input Voltage to DGND                     | -0.3 V to V <sub>DD</sub> + 0.3 V |  |  |

| V <sub>OUT</sub> to AGND                          | -0.3 V to V <sub>DD</sub> + 0.3 V |  |  |

| AGND, AGNDF, AGNDS to DGND                        | –0.3 V to +0.3 V                  |  |  |

| Input Current to Any Pin Except Supplies          | ±10 mA                            |  |  |

| Operating Temperature Range                       |                                   |  |  |

| Industrial (A, B, C Versions)                     | -40°C to +85°C                    |  |  |

| Commercial (J, L Versions)                        | 0°C to 70°C                       |  |  |

| Storage Temperature Range                         | –65°C to +150°C                   |  |  |

| Maximum Junction Temperature (T <sub>J</sub> max) | 150°C                             |  |  |

| Package Power Dissipation                         | $(T_J max - T_A)/\theta_{JA}$     |  |  |

| Thermal Impedance, $\theta_{JA}$                  |                                   |  |  |

| SOIC (R-8)                                        | 149.5°C/W                         |  |  |

| SOIC (R-14)                                       | 104.5°C/W                         |  |  |

| Lead Temperature, Soldering                       |                                   |  |  |

| Peak Temperature <sup>1</sup>                     | 260°C                             |  |  |

| ESD <sup>2</sup>                                  | 5 kV                              |  |  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>1</sup> As per JEDEC Standard 20.

<sup>2</sup>HBM Classification

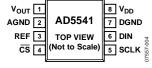

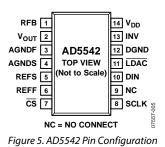

# **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

Figure 4. AD5541 Pin Configuration

#### Table 5. AD5541 Pin Function Descriptions

| Pin No. | Mnemonic         | Description                                                                                                              |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>OUT</sub> | Analog Output Voltage from the DAC.                                                                                      |

| 2       | AGND             | Ground Reference Point for Analog Circuitry.                                                                             |

| 3       | REF              | Voltage Reference Input for the DAC. Connect to an external 2.5 V reference. Reference can range from 2 V to $V_{DD}$ .  |

| 4       | CS               | Logic Input Signal. The chip select signal is used to frame the serial data input.                                       |

| 5       | SCLK             | Clock Input. Data is clocked into the input register on the rising edge of SCLK. Duty cycle must be between 40% and 60%. |

| 6       | DIN              | Serial Data Input. This device accepts 16-bit words. Data is clocked into the input register on the rising edge of SCLK. |

| 7       | DGND             | Digital Ground. Ground reference for digital circuitry.                                                                  |

| 8       | V <sub>DD</sub>  | Analog Supply Voltage, 5 V $\pm$ 10%.                                                                                    |

#### Table 6. AD5542 Pin Function Descriptions

| Pin No. | Mnemonic         | Description                                                                                                                     |

|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1       | RFB              | Feedback Resistor Pin. In bipolar mode, connect this pin to the external op amp output.                                         |

| 2       | V <sub>OUT</sub> | Analog Output Voltage from the DAC.                                                                                             |

| 3       | AGNDF            | Ground Reference Point for Analog Circuitry (Force).                                                                            |

| 4       | AGNDS            | Ground Reference Point for Analog Circuitry (Sense).                                                                            |

| 5       | REFS             | Voltage Reference Input (Sense) for the DAC. Connect to an external 2.5 V reference. Reference can range from 2 V to $V_{DD}$ . |

| 6       | REFF             | Voltage Reference Input (Force) for the DAC. Connect to an external 2.5 V reference. Reference can range from 2 V to $V_{DD}$ . |

| 7       | CS               | Logic Input Signal. The chip select signal is used to frame the serial data input.                                              |

| 8       | SCLK             | Clock Input. Data is clocked into the input register on the rising edge of SCLK. Duty cycle must be between 40% and 60%.        |

| 9       | NC               | No Connect.                                                                                                                     |

| 10      | DIN              | Serial Data Input. This device accepts 16-bit words. Data is clocked into the input register on the rising edge of SCLK.        |

| 11      | LDAC             | LDAC Input. When this input is taken low, the DAC register is simultaneously updated with the contents of the                   |

|         |                  | input register.                                                                                                                 |

| 12      | DGND             | Digital Ground. Ground reference for digital circuitry.                                                                         |

| 13      | INV              | Connected to the Internal Scaling Resistors of the DAC. Connect the INV pin to external op amps inverting input in              |

|         |                  | bipolar mode.                                                                                                                   |

| 14      | V <sub>DD</sub>  | Analog Supply Voltage, 5 V $\pm$ 10%.                                                                                           |

# **TYPICAL PERFORMANCE CHARACTERISTICS**

# **Data Sheet**

# AD5541/AD5542

# TERMINOLOGY

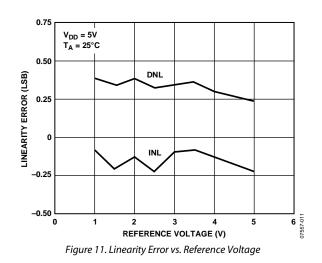

#### Relative Accuracy or Integral Nonlinearity (INL)

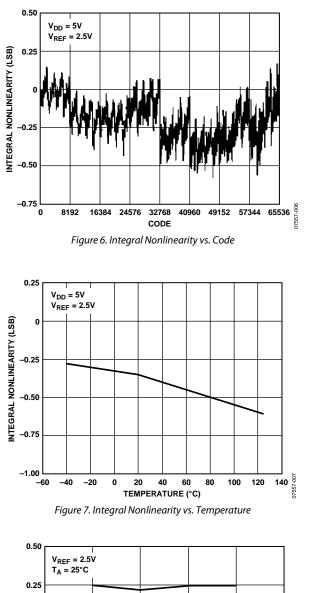

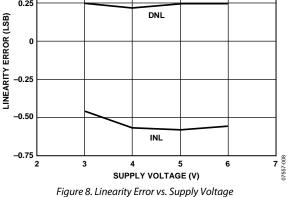

For the DAC, relative accuracy or INL is a measure of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function. A typical INL vs. code plot can be seen in Figure 6.

#### Differential Nonlinearity (DNL)

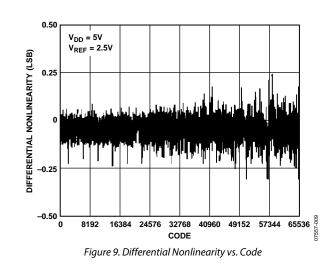

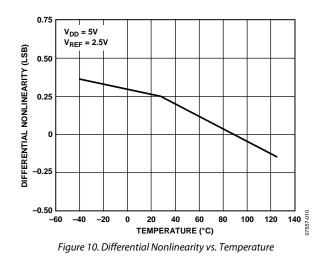

DNL is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB maximum ensures monotonicity. Figure 9 illustrates a typical DNL vs. code plot.

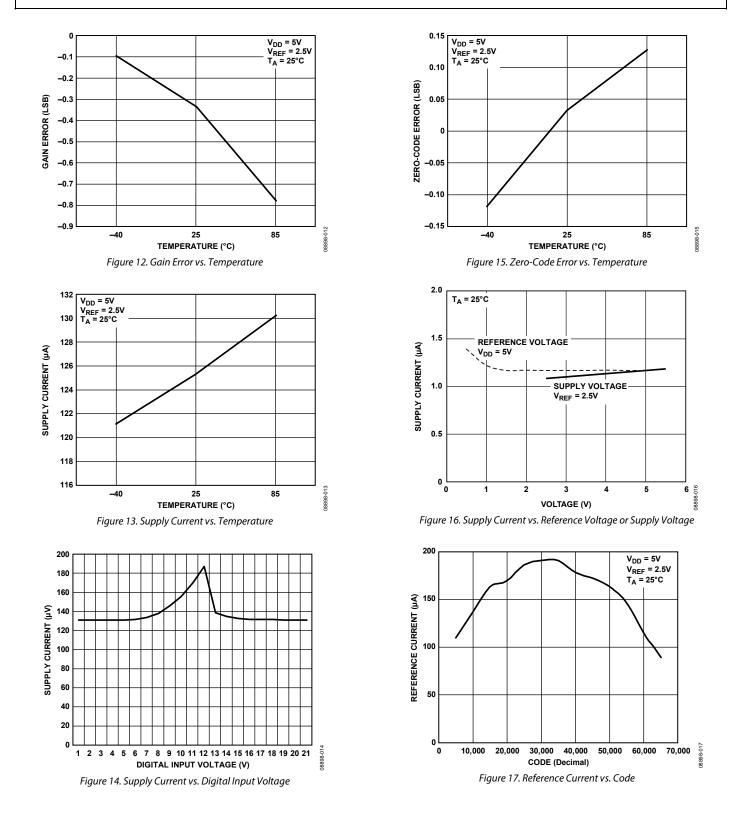

#### **Gain Error**

Gain error is the difference between the actual and ideal analog output range, expressed as a percent of the full-scale range. It is the deviation in slope of the DAC transfer characteristic from ideal.

#### **Gain Error Temperature Coefficient**

Gain error temperature coefficient is a measure of the change in gain error with changes in temperature. It is expressed in ppm/°C.

#### Zero Code Error

Zero code error is a measure of the output error when zero code is loaded to the DAC register.

#### Zero Code Temperature Coefficient

This is a measure of the change in zero code error with a change in temperature. It is expressed in  $mV/^{\circ}C$ .

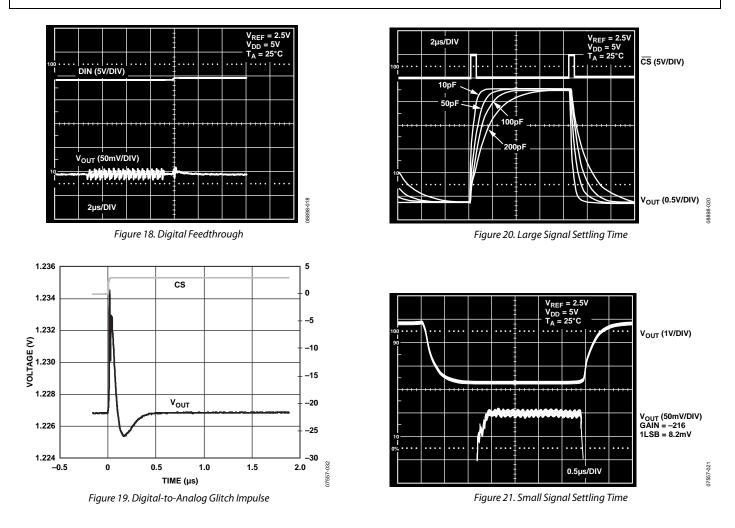

#### Digital-to-Analog Glitch Impulse

Digital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state. It is normally specified as the area of the glitch in nV-sec and is measured when the digital input code is changed by 1 LSB at the major carry transition. A plot of the digital-to-analog glitch impulse is shown in Figure 19.

#### **Digital Feedthrough**

Digital feedthrough is a measure of the impulse injected into the analog output of the DAC from the digital inputs of the DAC, but it is measured when the DAC output is not updated.  $\overline{\text{CS}}$  is held high while the CLK and DIN signals are toggled. It is specified in nV-sec and is measured with a full-scale code change on the data bus, that is, from all 0s to all 1s and vice versa. A typical plot of digital feedthrough is shown in Figure 18.

#### Power Supply Rejection Ratio (PSRR)

PSRR indicates how the output of the DAC is affected by changes in the power supply voltage. Power-supply rejection ratio is quoted in terms of percent change in output per percent change in  $V_{DD}$  for full-scale output of the DAC.  $V_{DD}$  is varied by ±10%.

#### **Reference Feedthrough**

Reference feedthrough is a measure of the feedthrough from the  $V_{REF}$  input to the DAC output when the DAC is loaded with all 0s. A 100 kHz, 1 V p-p is applied to  $V_{REF}$ . Reference feedthrough is expressed in mV p-p.

# THEORY OF OPERATION

The AD5541/AD5542 are single, 16-bit, serial input, voltage output DACs. They operate from a single supply ranging from 2.7 V to 5.5 V and consume typically 125  $\mu$ A with a supply of 5 V. Data is written to these devices in a 16-bit word format, via a 3- or 4-wire serial interface. To ensure a known power-up state, these parts are designed with a power-on reset function. In unipolar mode, the output is reset to 0 V; in bipolar mode, the AD5542 output is set to  $-V_{REF}$ . Kelvin sense connections for the reference and analog ground are included on the AD5542.

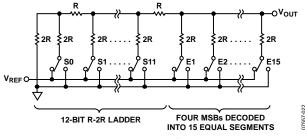

### **DIGITAL-TO-ANALOG SECTION**

The DAC architecture consists of two matched DAC sections. A simplified circuit diagram is shown in Figure 22. The DAC architecture of the AD5541/AD5542 is segmented. The four MSBs of the 16-bit data-word are decoded to drive 15 switches, E1 to E15. Each switch connects one of 15 matched resistors to either AGND or  $V_{REF}$ . The remaining 12 bits of the data-word drive switches S0 to S11 of a 12-bit voltage mode R-2R ladder network.

Figure 22. DAC Architecture

With this type of DAC configuration, the output impedance is independent of code, while the input impedance seen by the reference is heavily code dependent. The output voltage is dependent on the reference voltage, as shown in the following equation:

$$V_{OUT} = \frac{V_{REF} \times D}{2^N}$$

where:

*D* is the decimal data-word loaded to the DAC register. *N* is the resolution of the DAC.

For a reference of 2.5 V, the equation simplifies to the following:

$$V_{OUT} = \frac{2.5 \times D}{65,536}$$

This gives a  $\rm V_{\rm OUT}$  of 1.25 V with midscale loaded and 2.5 V with full-scale loaded to the DAC.

The LSB size is  $V_{\text{REF}}/65,536$ .

### SERIAL INTERFACE

The AD5541/AD5542 are controlled by a versatile 3- or 4-wire serial interface that operates at clock rates up to 25 MHz and is compatible with SPI, QSPI, MICROWIRE, and DSP interface standards. The timing diagram is shown in Figure 3. Input data is framed by the chip select input,  $\overline{CS}$ . After a high-to-low transition on  $\overline{CS}$ , data is shifted synchronously and latched into the input register on the rising edge of the serial clock, SCLK. Data is loaded MSB first in 16-bit words. After 16 data bits have been loaded into the serial input register, a low-to-high transition on  $\overline{CS}$  transfers the contents of the shift register to the DAC. Data can be loaded to the part only while  $\overline{CS}$  is low.

The AD5542 has an  $\overline{\text{LDAC}}$  function that allows the DAC latch to be updated asynchronously by bringing  $\overline{\text{LDAC}}$  low after  $\overline{\text{CS}}$ goes high.  $\overline{\text{LDAC}}$  should be maintained high while data is written to the shift register. Alternatively,  $\overline{\text{LDAC}}$  can be tied permanently low to update the DAC synchronously. With  $\overline{\text{LDAC}}$  tied permanently low, the rising edge of  $\overline{\text{CS}}$  loads the data to the DAC.

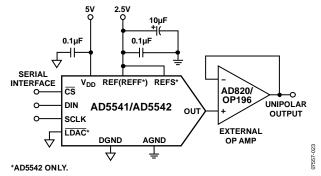

## UNIPOLAR OUTPUT OPERATION

These DACs are capable of driving unbuffered loads of 60 k $\Omega$ . Unbuffered operation results in low supply current, typically 300  $\mu$ A, and a low offset error. The AD5541 provides a unipolar output swing ranging from 0 V to V<sub>REF</sub>. The AD5542 can be configured to output both unipolar and bipolar voltages. Figure 23 shows a typical unipolar output voltage circuit. The code table for this mode of operation is shown in Table 7.

Figure 23. Unipolar Output

| Table 7. | Unipo | lar Code | Table |

|----------|-------|----------|-------|

|----------|-------|----------|-------|

| DAC Latch Contents  |                                                        |

|---------------------|--------------------------------------------------------|

| MSB LSB             | Analog Output                                          |

| 1111 1111 1111 1111 | V <sub>REF</sub> × (65,535/65,536)                     |

| 1000 0000 0000 0000 | $V_{REF} \times (32,768/65,536) = \frac{1}{2} V_{REF}$ |

| 0000 0000 0000 0001 | V <sub>REF</sub> × (1/65,536)                          |

| 0000 0000 0000 0000 | 0 V                                                    |

Assuming a perfect reference, the unipolar worst-case output voltage can be calculated from the following equation:

$$\mathbf{V}_{\text{OUT-UNI}} = \frac{D}{2^{16}} \times \left( V_{REF} + V_{GE} \right) + V_{ZSE} + INL$$

where:

$V_{OUT-UNI}$  is unipolar mode worst-case output. D is code loaded to DAC.

$V_{REF}$  is reference voltage applied to the part.

$V_{GE}$  is gain error in volts.

$V_{ZSE}$  is zero scale error in volts.

INL is integral nonlinearity in volts.

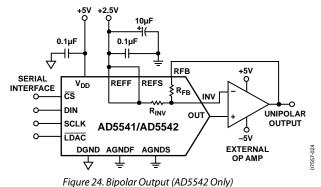

## **BIPOLAR OUTPUT OPERATION**

With the aid of an external op amp, the AD5542 can be configured to provide a bipolar voltage output. A typical circuit of such operation is shown in Figure 24. The matched bipolar offset resistors,  $R_{FB}$  and  $R_{INV}$ , are connected to an external op amp to achieve this bipolar output swing, typically  $R_{FB} = R_{INV} = 28 \text{ k}\Omega$ . Table 8 shows the transfer function for this output operating mode. Also provided on the AD5542 are a set of Kelvin connections to the analog ground inputs.

Table 8. Bipolar Code Table

| DAC Latch Contents  |                                              |

|---------------------|----------------------------------------------|

| MSB LSB             | Analog Output                                |

| 1111 1111 1111 1111 | +V <sub>REF</sub> × (32,767/32,768)          |

| 1000 0000 0000 0001 | +V <sub>REF</sub> × (1/32,768)               |

| 1000 0000 0000 0000 | 0 V                                          |

| 0111 1111 1111 1111 | $-V_{REF} \times (1/32,768)$                 |

| 0000 0000 0000 0000 | $-V_{REF} \times (32,768/32,768) = -V_{REF}$ |

Assuming a perfect reference, the worst-case bipolar output voltage can be calculated from the following equation:

$$V_{OUT-BIP} = \frac{\left[ \left( V_{OUT-UNI} + V_{OS} \right) (2 + RD) - V_{REF} (1 + RD) \right]}{1 + (2 + RD) / A}$$

where:

$V_{OUT\text{-}BIP}$  is the bipolar mode worst-case output.  $V_{OUT\text{-}UNI}$  is the unipolar mode worst-case output.  $V_{OS}$  is the external op amp input offset voltage. RD is the R\_{\rm FB} and R\_{\rm INV} resistor matching error. A is the op amp open-loop gain.

## **OUTPUT AMPLIFIER SELECTION**

For bipolar mode, a precision amplifier should be used and supplied from a dual power supply. This provides the  $\pm V_{REF}$  output. In a single-supply application, selection of a suitable op amp may be more difficult as the output swing of the amplifier does not usually include the negative rail, in this case, AGND. This can result in some degradation of the specified performance unless the application does not use codes near zero.

The selected op amp needs to have a very low-offset voltage (the DAC LSB is 38  $\mu$ V with a 2.5 V reference) to eliminate the need for output offset trims. Input bias current should also be very low because the bias current, multiplied by the DAC output impedance (approximately 6 k $\Omega$ ), adds to the zero code error. Rail-to-rail input and output performance is required. For fast settling, the slew rate of the op amp should not impede the settling time of the DAC. Output impedance of the DAC is constant and code-independent, but to minimize gain errors, the input impedance of the output amplifier should be as high as possible. The amplifier should also have a 3 dB bandwidth of 1 MHz or greater. The amplifier adds another time constant to the system, hence increasing the settling time of the output. A higher 3 dB amplifier bandwidth results in a shorter effective settling time of the combined DAC and amplifier.

### FORCE SENSE AMPLIFIER SELECTION

Use single-supply, low-noise amplifiers. A low-output impedance at high frequencies is preferred because the amplifiers need to be able to handle dynamic currents of up to  $\pm 20$  mA.

### **REFERENCE AND GROUND**

Because the input impedance is code-dependent, the reference pin should be driven from a low impedance source. The AD5541/AD5542 operate with a voltage reference ranging from 2 V to  $V_{\rm DD}$ . References below 2 V result in reduced accuracy. The full-scale output voltage of the DAC is determined by the reference. Table 7 and Table 8 outline the analog output voltage or particular digital codes. For optimum performance, Kelvin sense connections are provided on the AD5542.

If the application does not require separate force and sense lines, tie the lines close to the package to minimize voltage drops between the package leads and the internal die.

### **POWER-ON RESET**

The AD5541/AD5542 have a power-on reset function to ensure that the output is at a known state on power-up. On power-up, the DAC register contains all 0s until the data is loaded from the serial register. However, the serial register is not cleared on power-up, so its contents are undefined. When loading data initially to the DAC, 16 bits or more should be loaded to prevent erroneous data appearing on the output. If more than 16 bits are loaded, the last 16 are kept, and if less than 16 bits are loaded, bits remain from the previous word. If the AD5541/AD5542 need to be interfaced with data shorter than 16 bits, the data should be padded with 0s at the LSBs.

### POWER SUPPLY AND REFERENCE BYPASSING

For accurate high-resolution performance, it is recommended that the reference and supply pins be bypassed with a  $10 \,\mu\text{F}$  tantalum capacitor in parallel with a  $0.1 \,\mu\text{F}$  ceramic capacitor.

# MICROPROCESSOR INTERFACING

Microprocessor interfacing to the AD5541/AD5542 is via a serial bus that uses standard protocol that is compatible with DSP processors and microcontrollers. The communications channel requires a 3- or 4-wire interface consisting of a clock signal, a data signal and a synchronization signal. The AD5541/AD5542 require a 16-bit data-word with data valid on the rising edge of SCLK. The DAC update can be done automatically when all the data is clocked in or it can be done under control of the LDAC (AD5542 only).

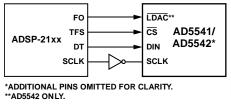

## AD5541/AD5542 TO ADSP-21XX INTERFACE

Figure 25 shows a serial interface between the AD5541/AD5542 and the ADSP-21xx. The ADSP-21xx should be set to operate in the SPORT transmit alternate framing mode. The ADSP-21xx are programmed through the SPORT control register and should be configured as follows: internal clock operation, active low framing, 16-bit word length. Transmission is initiated by writing a word to the Tx register after the SPORT has been enabled. As the data is clocked out on each rising edge of the serial clock, an inverter is required between the DSP and the DAC, because the AD5541/AD5542 clock data in on the falling edge of the SCLK.

Figure 25. AD5541/AD5542 to ADSP-21xx Interface

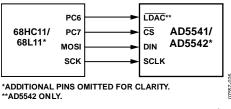

### AD5541/AD5542 TO 68HC11/68L11 INTERFACE

Figure 26 shows a serial interface between the AD5541/AD5542 and the 68HC11/68L11 microcontroller. SCK of the 68HC11/ 68L11 drives the SCLK of the DAC, and the MOSI output drives the serial data line serial DIN. The  $\overline{\text{CS}}$  signal is driven from one of the port lines. The 68HC11/68L11 is configured for master mode: MSTR = 1, CPOL = 0, and CPHA = 0. Data appearing on the MOSI output is valid on the rising edge of SCK.

Figure 26. AD5541/AD5542 to 68HC11/68L11 Interface

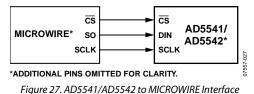

### AD5541/AD5542 TO MICROWIRE INTERFACE

Figure 27 shows an interface between the AD5541/AD5542 and any MICROWIRE-compatible device. Serial data is shifted out on the falling edge of the serial clock and into the AD5541/ AD5542 on the rising edge of the serial clock. No glue logic is required because the DAC clocks data into the input shift register on the rising edge.

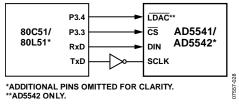

### AD5541/AD5542 TO 80C51/80L51 INTERFACE

A serial interface between the AD5541/AD5542 and the 80C51/80L51 microcontroller is shown in Figure 28. TxD of the microcontroller drives the SCLK of the AD5541/AD5542, and RxD drives the serial data line of the DAC. P3.3 is a bit programmable pin on the serial port that is used to drive  $\overline{CS}$ .

The 80C51/80L51 provide the LSB first, whereas the AD5541/ AD5542 expects the MSB of the 16-bit word first. Care should be taken to ensure the transmit routine takes this into account.

When data is to be transmitted to the DAC, P3.3 is taken low. Data on RxD is valid on the falling edge of TxD, so the clock must be inverted as the DAC clocks data into the input shift register on the rising edge of the serial clock. The 80C51/80L51 transmit data in 8-bit bytes with only eight falling clock edges occurring in the transmit cycle. As the DAC requires a 16-bit word, P3.3 must be left low after the first eight bits are transferred, and brought high after the second byte is transferred. <u>LDAC</u> on the AD5542 can also be controlled by the 80C51/ 80L51 serial port output by using another bit programmable pin, P3.4.

Figure 28. AD5541/AD5542 to 80C51/80L51 Interface

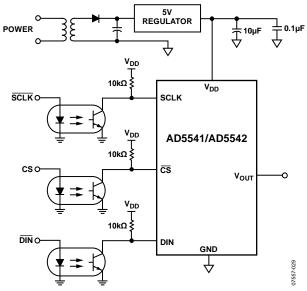

## APPLICATIONS INFORMATION OPTOCOUPLER INTERFACE

The digital inputs of the AD5541/AD5542 are Schmitt-triggered so that they can accept slow transitions on the digital input lines. This makes these parts ideal for industrial applications where it may be necessary to isolate the DAC from the controller via optocouplers. Figure 29 illustrates such an interface.

Figure 29. AD5541/AD5542 in an Optocoupler Interface

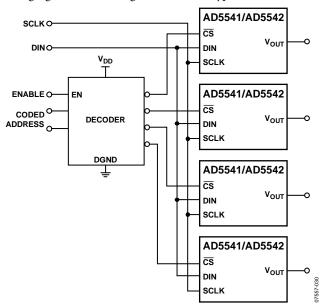

## DECODING MULTIPLE AD5541/AD5542s

The  $\overline{\text{CS}}$  pin of the AD5541/AD5542 can be used to select one of a number of DACs. All devices receive the same serial clock and serial data, but only one device receives the  $\overline{\text{CS}}$  signal at any one time. The DAC addressed is determined by the decoder. There is some digital feedthrough from the digital input lines. Using a burst clock minimizes the effects of digital feedthrough on the analog signal channels. Figure 30 shows a typical circuit.

Figure 30. Addressing Multiple AD5541/AD5542s

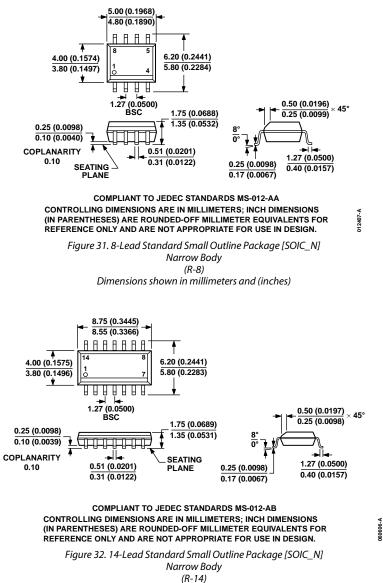

# **OUTLINE DIMENSIONS**

Dimensions shown in millimeters and (inches)

### **ORDERING GUIDE**

| Model <sup>1</sup> | INL    | DNL      | Temperature Range | Package Description | Package Option |

|--------------------|--------|----------|-------------------|---------------------|----------------|

| AD5541CR           | ±1 LSB | ±1 LSB   | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD5541CRZ          | ±1 LSB | ±1 LSB   | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD5541CRZ-REEL7    | ±1 LSB | ±1 LSB   | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD5541LR           | ±1 LSB | ±1 LSB   | 0°C to 70°C       | 8-Lead SOIC_N       | R-8            |

| AD5541LR-REEL7     | ±1 LSB | ±1 LSB   | 0°C to 70°C       | 8-Lead SOIC_N       | R-8            |

| AD5541LRZ          | ±1 LSB | ±1 LSB   | 0°C to 70°C       | 8-Lead SOIC_N       | R-8            |

| AD5541LRZ-REEL7    | ±1 LSB | ±1 LSB   | 0°C to 70°C       | 8-Lead SOIC_N       | R-8            |

| AD5541BR           | ±2 LSB | ±1 LSB   | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD5541BRZ          | ±2 LSB | ±1 LSB   | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD5541BRZ-REEL     | ±2 LSB | ±1 LSB   | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD5541JR           | ±2 LSB | ±1.5 LSB | 0°C to 70°C       | 8-Lead SOIC_N       | R-8            |

| AD5541JR-REEL7     | ±2 LSB | ±1.5 LSB | 0°C to 70°C       | 8-Lead SOIC_N       | R-8            |

| AD5541JRZ          | ±2 LSB | ±1.5 LSB | 0°C to 70°C       | 8-Lead SOIC_N       | R-8            |

| AD5541JRZ-REEL7    | ±2 LSB | ±1.5 LSB | 0°C to 70°C       | 8-Lead SOIC_N       | R-8            |

| AD5541AR           | ±4 LSB | ±1 LSB   | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD5541AR-REEL7     | ±4 LSB | ±1 LSB   | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD5541ARZ          | ±4 LSB | ±1 LSB   | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD5541ARZ-REEL7    | ±4 LSB | ±1 LSB   | –40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD5542CR           | ±1 LSB | ±1 LSB   | -40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| AD5542CR-REEL7     | ±1 LSB | ±1 LSB   | -40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| AD5542CRZ          | ±1 LSB | ±1 LSB   | –40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| AD5542CRZ-REEL7    | ±1 LSB | ±1 LSB   | -40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| AD5542LR           | ±1 LSB | ±1 LSB   | 0°C to 70°C       | 14-Lead SOIC_N      | R-14           |

| AD5542LRZ          | ±1 LSB | ±1 LSB   | 0°C to 70°C       | 14-Lead SOIC_N      | R-14           |

| AD5542BR           | ±2 LSB | ±1 LSB   | –40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| AD5542BRZ          | ±2 LSB | ±1 LSB   | –40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| AD5542BRZ-REEL7    | ±2 LSB | ±1 LSB   | –40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| AD5542JR           | ±2 LSB | ±1.5 LSB | 0°C to 70°C       | 14-Lead SOIC_N      | R-14           |

| AD5542JR-REEL7     | ±2 LSB | ±1.5 LSB | 0°C to 70°C       | 14-Lead SOIC_N      | R-14           |

| AD5542JRZ          | ±2 LSB | ±1.5 LSB | 0°C to 70°C       | 14-Lead SOIC_N      | R-14           |

| AD5542JRZ-REEL7    | ±2 LSB | ±1.5 LSB | 0°C to 70°C       | 14-Lead SOIC_N      | R-14           |

| AD5542AR           | ±4 LSB | ±1 LSB   | -40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| AD5542AR-REEL7     | ±4 LSB | ±1 LSB   | -40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| AD5542ARZ          | ±4 LSB | ±1 LSB   | -40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| AD5542ARZ-REEL7    | ±4 LSB | ±1 LSB   | -40°C to +85°C    | 14-Lead SOIC_N      | R-14           |

| EVAL-AD5541/42EBZ  |        |          |                   | Evaluation Board    |                |

<sup>1</sup> Z = RoHS Compliant Part.

# NOTES

# NOTES

# **Data Sheet**

# NOTES

(F) ANALOG Rev. F | Page 20 of 20

www.analog.com

©1999–2012 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D07557-0-3/12(F)