## 21V, 5A, 500KHz Synchronous PWM-Buck DC/DC Converter

### Description

FR9809 is a high-efficiency synchronous step-down DC/DC converter that employs a special process technique to obtain very low  $R_{DS}(ON)$  for the internal metal–oxide–semiconductor field-effect transistor (MOSFET). The input operation voltage is in a wide range from 4.75V to 21V, and continuous load current capability is 5A. Control circuit is designed by a particular current mode which provides fast transient response and eases loop stabilization.

This product has a very low standby current less than 1 $\mu$ A in shutdown mode. When the SHDN/S pin voltage is less than 0.4V, FR9809 will turn off. Fault protection includes over current protection (OCP), under voltage lockout protection (UVLO) and over temperature protection (OTP) function.

This high-efficiency current mode step-down "Green Power Converter" offers the standard SOP-8 package with an exposed pad.

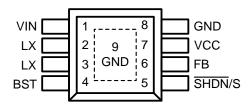

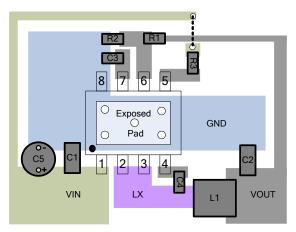

### **Pin Assignments**

SP Package (SOP-8 Exposed Pad)

Figure 1. Pin Assignment of FR9809

### Features

- High Efficiency up to 90%

- Internal MOSFET R<sub>DS</sub>(ON): 110mΩ/20mΩ

- Internal Compensation

- Input Operation Voltage Range: 4.75V to 21V

- 5A Continuous Output Current

- Output Voltage down to 0.805V

- 500KHz Oscillation Frequency

- Sync to External Clock from 300KHz to 800KHz

- Cycle-by-Cycle Current Limit

- Under Voltage Lockout

- Over-Temperature Protection with Auto Recovery

- <1µA Shutdown Current

- Thermal Enhanced SOP-8 (Exposed Pad) Package

- RoHS Compliant

### Applications

- Networking Equipment

- OLPC, Netbook

- Distributed Power System

- LCD Monitor, TV, STB

- External HDD

- Security System

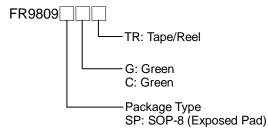

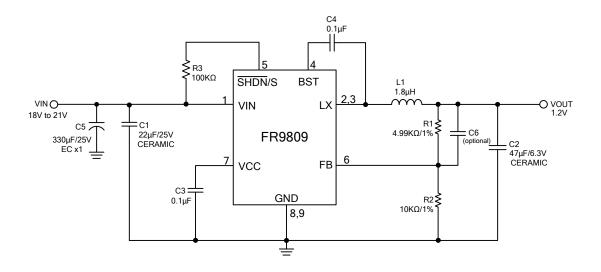

### **Ordering Information**

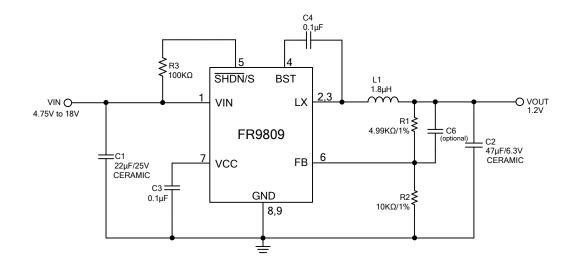

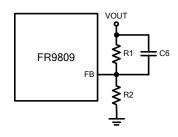

# **Typical Application Circuit**

Figure 2. Output 1.2V Application Circuit

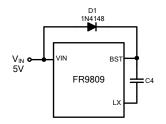

Figure 3. High Input Voltage Application Circuit

## **Functional Pin Description**

| I/O | Pin Name    | Pin No. | Pin Function                                                                                                                                                                                                                                                                                      |

|-----|-------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I   | FB          | 6       | Voltage Feedback Input Pin. FB and VOUT are connected by a resistive voltage divider. This IC senses feedback voltage via FB and regulates it at 805mV.                                                                                                                                           |

| I   | VIN         | 1       | Power Supply Input Pin. Drive $4.75V \sim 21V$ voltage to this pin to power on this chip. A $22\mu$ F ceramic bypass capacitor is connected between VIN and GND to eliminate noise.                                                                                                               |

| ο   | vcc         | 7       | Bias Supply Output Pin. A capacitor rating between $0.001\mu$ F~1µF must be connected from this pin to GND.                                                                                                                                                                                       |

| I   | SHDN/S      | 5       | This pin provides a digital control to turn the converter on or off. For automatic start-up, connect the $\overline{SHDN}/S$ pin to VIN pin with a 100K $\Omega$ resistor. An external clock from 300KHz to 800KHz can be applied to the $\overline{SHDN}/S$ pin to change oscillation frequency. |

| ο   | LX          | 2,3     | Power Switching Output Pin. This is the output pin that internal high-side NMOS switches to supply power.                                                                                                                                                                                         |

| ο   | BST         | 4       | High-Side Gate-Drive BST Input. A capacitor rating between $0.01\mu$ F $\sim$ 0.1 $\mu$ F must be connected from this pin to LX. It can boost the gate drive to fully turn on the internal high-side NMOS.                                                                                        |

| I   | GND         | 8       | Ground Pin. This pin is connected to the exposed pad with copper.                                                                                                                                                                                                                                 |

| I   | Exposed Pad | 9       | Ground Pin. The exposed pad must be soldered to a large PCB area and connected to GND for maximum power dissipation.                                                                                                                                                                              |

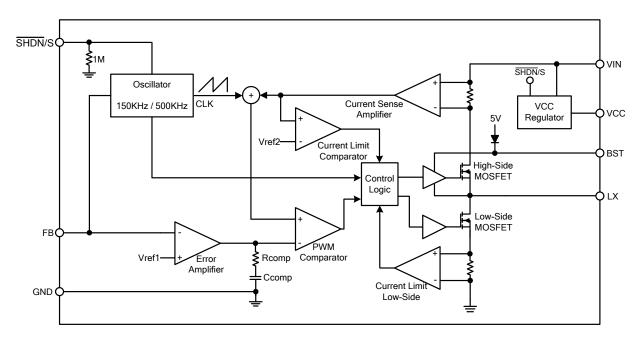

## **Block Diagram**

Figure 4. Block Diagram of FR9809

## Absolute Maximum Ratings (Note1)

| Input Supply Voltage V <sub>IN</sub>                                                         | -0.3V to +23V                                |

|----------------------------------------------------------------------------------------------|----------------------------------------------|

| • Enable Voltage V <sub>SHDN/S</sub>                                                         | -0.3V to +23V                                |

| • LX Voltage V <sub>LX</sub>                                                                 | -0.3V to V <sub>IN</sub> +1V                 |

| • BST Voltage V <sub>BST</sub>                                                               | $V_{\text{LX}}$ -0.3V to $V_{\text{LX}}$ +6V |

| All Other Pins Voltage                                                                       | -0.3V to +6V                                 |

| • Maximum Junction Temperature (T <sub>J</sub> )                                             | +150°C                                       |

| • Storage Temperature (T <sub>s</sub> )                                                      | -65°C to +150°C                              |

| Lead Temperature (Soldering, 10sec.)                                                         | +260°C                                       |

| <ul> <li>Package Thermal Resistance (θ<sub>JA</sub>) (Note2)</li> </ul>                      |                                              |

| SOP-8 (Exposed Pad)                                                                          | 60°C/W                                       |

| • Package Thermal Resistance ( $\theta_{JC}$ )                                               |                                              |

| SOP-8 (Exposed Pad)                                                                          | 15°C/W                                       |

| Note 1 : Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent d | amage to the device.                         |

Note 2 : PCB heat sink copper area =  $10 \text{mm}^2$ .

### **Recommended Operating Conditions**

| <ul> <li>Input Supply Voltage V<sub>IN</sub></li> </ul> | +4.75V to +21V |

|---------------------------------------------------------|----------------|

| Operation Temperature Range                             |                |

## **Electrical Characteristics**

(V<sub>IN</sub>=12V,  $T_A$ =25°C, unless otherwise specified.)

| Parameter                                     | Symbol                  | Conditions                                 | Min  | Тур | Мах | Unit |

|-----------------------------------------------|-------------------------|--------------------------------------------|------|-----|-----|------|

| Input Supply Voltage                          | V <sub>IN</sub>         |                                            | 4.75 |     | 21  | V    |

| VIN Shutdown Supply Current                   | I <sub>SD</sub>         | V <sub>SHDN</sub> =0V                      |      |     | 1   | μA   |

| VIN Quiescent Supply Current                  | I <sub>DDQ</sub>        | V <sub>SHDN</sub> =2V, V <sub>FB</sub> =1V |      | 1.5 |     | mA   |

| Feedback Voltage                              | V <sub>FB</sub>         | $4.75V{\leq}V_{IN}{\leq}21V$               | 780  | 805 | 830 | mV   |

| High-Side MOSFET R <sub>DS</sub> (ON) (Note2) | HSR <sub>DS</sub> (ON)  |                                            |      | 110 |     | mΩ   |

| Low-Side MOSFET R <sub>DS</sub> (ON) (Note2)  | LSR <sub>DS</sub> (ON)  |                                            |      | 20  |     | mΩ   |

| MOSFET Leakage Current                        | I <sub>∟x</sub> (Leak)  | V <sub>SHDN</sub> =0V, V <sub>LX</sub> =0V |      | 0   | 10  | μA   |

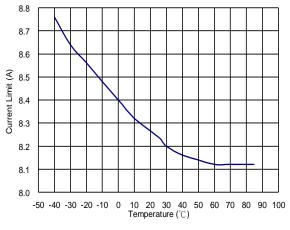

| High-Side MOSFET Current Limit (Note2)        | I <sub>LIMIT</sub>      |                                            |      | 8   |     | А    |

| Maximum Duty Cycle                            | D <sub>MAX</sub>        | V <sub>FB</sub> =0.7V                      |      | 90  |     | %    |

| Oscillation frequency                         | F <sub>LX</sub>         |                                            | 350  | 500 | 650 | KHz  |

| Short-Circuit Oscillation Frequency           | F <sub>LX</sub> (Short) | V <sub>FB</sub> =0.3V                      |      | 150 |     | KHz  |

| Sync Frequency Range                          | F <sub>SYNC</sub>       |                                            | 300  |     | 800 | KHz  |

| Input UVLO Threshold                          | VUVLO(Vth)              | V <sub>IN</sub> Rising                     |      | 4   |     | V    |

| Under Voltage Lockout Threshold<br>Hysteresis | VUVLO(Hys)              |                                            |      | 200 |     | mV   |

| SHDN/S Input Low Voltage                      | V <sub>SHDN</sub> (L)   |                                            |      |     | 0.4 | V    |

| SHDN/S Input High Voltage                     | V <sub>SHDN</sub> (H)   |                                            | 2.0  |     |     | V    |

| SHDN/S Input Current                          | I <sub>SHDN</sub>       | V <sub>SHDN</sub> =2V                      |      | 2   |     | μA   |

| VCC Regulator                                 | V <sub>cc</sub>         |                                            |      | 4.5 |     | V    |

| Soft-Start Time                               | T <sub>SS</sub>         |                                            |      | 600 |     | μs   |

| Thermal Shutdown Threshold (Note 2)           | T <sub>SD</sub>         |                                            |      | 170 |     | °C   |

Note 2 : Guarantee by design.

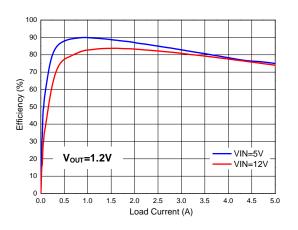

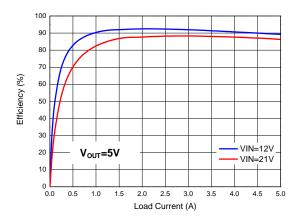

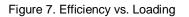

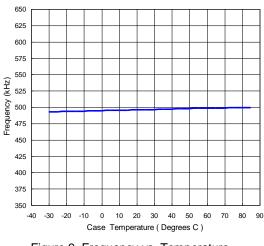

### **Typical Performance Curves**

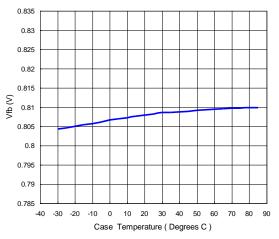

V<sub>IN</sub>=12V, V<sub>OUT</sub>=3.3V, C1=22µF, C2=47µF, L1=1.8µH, TA=+25°C, unless otherwise noted.

Figure 9. Frequency vs. Temperature

Figure 6. Efficiency vs. Loading

Figure 8. Feedback Voltage vs. Temperature

## **Typical Performance Curves (Continued)**

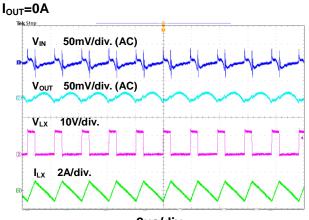

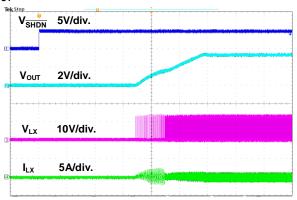

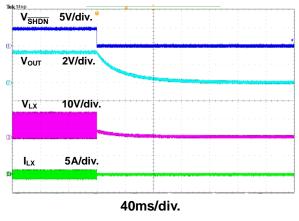

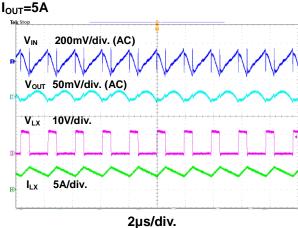

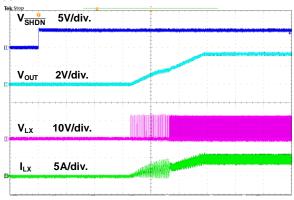

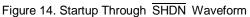

$V_{IN}$ =12V,  $V_{OUT}$ =3.3V, C1=22 $\mu$ F, C2=47 $\mu$ F, L1=1.8 $\mu$ H, TA=+25°C, unless otherwise noted.

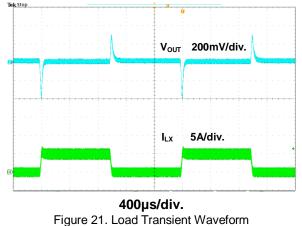

2µs/div.

Figure 11. DC Ripple Waveform

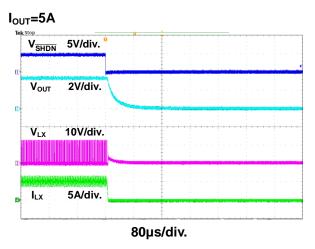

**200µs/div.** Figure 13. Startup Through SHDN Waveform

Figure 15. Shutdown Through SHDN Waveform

2µ5/uiv.

Figure 12. DC Ripple Waveform

I<sub>OUT</sub>=5A

Figure 16. Shutdown Through SHDN Waveform

## **Typical Performance Curves (Continued)**

V<sub>IN</sub>=12V, V<sub>OUT</sub>=3.3V, C1=22µF, C2=47µF, L1=1.8µH, TA=+25°C, unless otherwise noted.

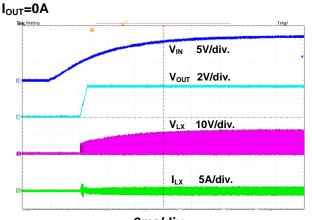

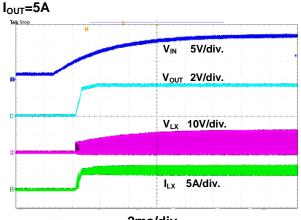

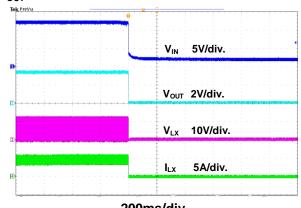

2ms/div. Figure 17. Startup Through VIN Waveform

2ms/div. Figure 18. Startup Through VIN Waveform

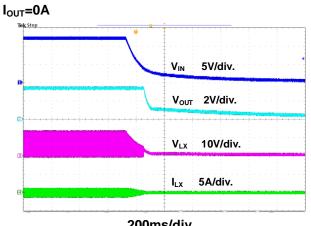

200ms/div.

Figure 19. Shutdown Through VIN Waveform

I<sub>OUT</sub>=5A

200ms/div.

Figure 20. Shutdown Through VIN Waveform

### **Function Description**

#### Introduction

FR9809 is a constant-frequency current-mode step-down synchronous DC/DC converter. It regulates input voltage from 4.75V to 21V and provides 5A of continuous load current.

To achieve bias power supply, FR9809 contains an internal voltage regulator to support the internal circuits. For applications in which VIN is less than 4.5V, output decreases and a  $0.1\mu$ F ceramic capacitor are required for decoupling. If VIN is greater than 4.5V, the output of the regulator will be in full regulation.

The error amplifier compares the FB voltage with the internal 0.805V reference. And the voltage of error amplifier output is compared to the switch current to control the RS flip-flop. At the beginning of each clock cycle, the high-side NMOS turns on when the oscillator sets the RS flip-flop, and turns off when current comparator resets the RS flip-flop. Then the low-side NMOS will turn on until the clock period ends.

#### **Internal Soft-Start**

The internal soft-start function is used to eliminate the output voltage overshooting during start-up. When the chip initiates, the internal reference voltage will rise slowly to 0.805V and the internal COMP signal will rise slowly to achieve output voltage. The soft-start time is approximate 600µs.

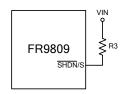

#### SHDN/S

The FR9809  $\overline{\text{SHDN}/\text{S}}$  pin provides digital control to turn on/turn off the regulator. For automatic start-up, tie  $\overline{\text{SHDN}/\text{S}}$  and  $\overline{\text{VIN}}$  with a resister, as shown in the figure. The recommended value of R3 is 100K $\Omega$ . The FR9809 can be synchronized with an external clock from 300KHz to 800KHz by using the  $\overline{\text{SHDN}/\text{S}}$  pin.

#### **Device Protection:**

#### 1. Input Under Voltage Lockout

When the power of FR9809 is on, the internal circuits will be held inactive until VIN exceeds the input UVLO threshold voltage. The regulator will be disabled when VIN falls below the input UVLO threshold voltage. The hysteretic of the UVLO comparator is 200mV.

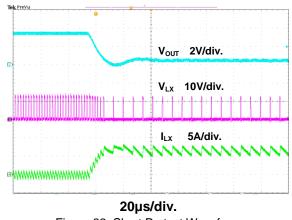

#### 2. Short Circuit Protection

The FR9809 provides short circuit protection function to prevent the device damaged from short condition. When the short condition occurs and the feedback voltage drops lower than 40% of the reference, the oscillator frequency will be reduced to 150KHz to prevent the inductor current increasing beyond the current limit. In the meantime, the current limit will also be reduced to lower the short current. Once the short condition is removed, the frequency and current limit will return to normal.

#### 3. Over Current Protection

The FR9809 over current protection function is implemented using cycle-by-cycle current limit architecture. The inductor current is monitored by measuring the high-side MOSFET series sense resistor voltage. When the load current increases, the inductor current will also increase. When the peak inductor current reaches the current limit threshold, the output voltage will start to drop. When the over current condition is removed, the output voltage will return to the regulated value.

#### 4. Over Temperature Protection

The FR9809 incorporates an over temperature protection circuit to protect itself from overheating. When the junction temperature exceeds the thermal shutdown threshold temperature, the regulator will shutdown. When the junction temperature is less than the recovery threshold temperature, the chip will re-enable.

### **Application Information**

#### **Output Voltage Setting**

The output voltage  $V_{OUT}$  is set by using a resistive divider from the output to FB. The FB pin regulated voltage is 0.805V. Thus the output voltage is:

$$V_{OUT}=0.805 \times \left(1+\frac{R1}{R2}\right) V$$

Table 1 lists recommended values of R1 and R2 for most used output voltage.

| V <sub>OUT</sub> | R1 (1%) | R2 (1%) |  |  |

|------------------|---------|---------|--|--|

| 5V               | 30.9kΩ  | 5.76kΩ  |  |  |

| 3.3V             | 30.9kΩ  | 9.76kΩ  |  |  |

| 2.5V             | 4.99kΩ  | 2.32kΩ  |  |  |

| 1.8V             | 4.99kΩ  | 3.92kΩ  |  |  |

| 1.2V             | 4.99kΩ  | 10kΩ    |  |  |

Resistors R1 and R2 should be placed close to the FB pin to prevent stray pickup.

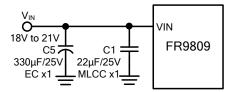

#### **Input Capacitor Selection**

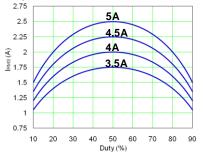

The use of the input capacitor is filtering the input voltage ripple and the MOSFETS switching spike voltage. Because the input current to the step-down converter is discontinuous, the input capacitor is required to supply the current to the converter to keep the DC input voltage. The capacitor voltage rating should be 1.25 to 1.5 times greater than the maximum input voltage. The input capacitor ripple current RMS value is calculated as:

$$I_{IN(RMS)} = I_{OUT} \times \sqrt{D \times (1-D)}$$

$$D = \frac{V_{OUT}}{V_{IN}}$$

Where D is the duty cycle of the power MOSFET.

This function reaches the maximum value at D=0.5 and the equivalent RMS current is equal to  $I_{OUT}/2$ . The following diagram is the graphical representation of above equation.

A low ESR capacitor is required to keep the noise minimum. Ceramic capacitors are better, but tantalum or low ESR electrolytic capacitors may also suffice. When using tantalum or electrolytic capacitors, a  $0.1\mu$ F ceramic capacitor should be placed as close to the IC as possible.

It is recommended that the input EC capacitor should be added for applications if the FR9809 suffers high spike input voltage (ex. hot plug test). It can eliminate the spike voltage and induce the IC damage from high input voltage stress.

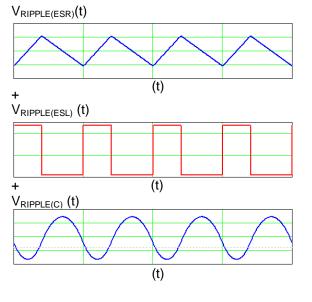

#### **Output Capacitor Selection**

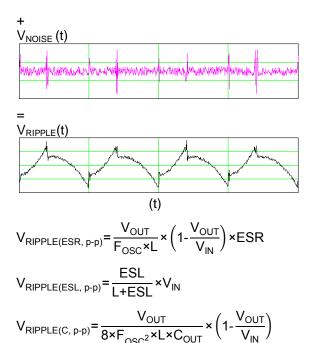

The output capacitor is used to keep the DC output voltage and supply the load transient current. When operating in constant current mode, the output ripple is determined by four components:

$$\begin{split} V_{\text{RIPPLE}}(t) = V_{\text{RIPPLE}(C)}(t) + V_{\text{RIPPLE}(\text{ESR})}(t) \\ + V_{\text{RIPPLE}(\text{ESL})}(t) + V_{\text{NOISE}}(t) \end{split}$$

The following figures show the form of the ripple contributions.

FR9809-Preliminary 0.4-OCT-2012

FR9809

### **Application Information (Continued)**

Where  $F_{OSC}$  is the switching frequency, L is the inductance value,  $V_{IN}$  is the input voltage, ESR is the equivalent series resistance value of the output capacitor, ESL is the equivalent series inductance value of the output capacitor and the  $C_{OUT}$  is the output capacitor.

Low ESR capacitors are preferred to use. Ceramic, tantalum or low ESR electrolytic capacitors can be used depending on the output ripple requirements. When using the ceramic capacitors, the ESL component is usually negligible.

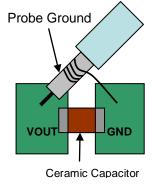

It is important to use the proper method to eliminate high frequency noise when measuring the output ripple. The figure shows how to locate the probe across the capacitor when measuring output ripple. Remove the scope probe plastic jacket in order to expose the ground at the tip of the probe. It gives a very short connection from the probe ground to the capacitor and eliminates noise.

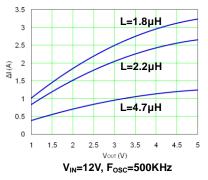

#### **Inductor Selection**

The output inductor is used for storing energy and filtering output ripple current. But the trade-off condition often happens between maximum energy storage and the physical size of the inductor. The first consideration for selecting the output inductor is to make sure that the inductance is large enough to keep the converter in the continuous current mode. That will lower ripple current and result in lower output ripple voltage. The  $\Delta I_L$  is inductor peak-to-peak ripple current:

$$\Delta I_{L} = \frac{V_{OUT}}{F_{OSC} \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

The following diagram is an example to graphical represent  $\Delta I_L$  equation.

A good compromise value between size and efficiency is to set the peak-to-peak inductor ripple current  $\Delta I_{L}$  equal to 30% of the maximum load current. But setting the peak-to-peak inductor ripple current  $\Delta I_{L}$  between 20%~50% of the maximum load current is also acceptable. Then the inductance can be calculated with the following equation:

$\Delta I_L = 0.3 \times I_{OUT(MAX)}$

$$L = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN} \times F_{OSC} \times \Delta I_{I}}$$

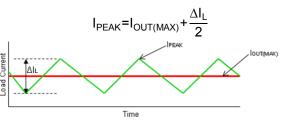

To guarantee sufficient output current, peak inductor current must be lower than the FR9809 high-side MOSFET current limit. The peak inductor current is shown as below:

### **Application Information (Continued)**

#### Feedforward Capacitor Selection

Internal compensation function allows users saving time in design and saving cost by reducing the number of external components. The use of a feedforward capacitor C6 in the feedback network is recommended to improve the transient response or higher phase margin.

For optimizing the feedforward capacitor, knowing the cross frequency is the first thing. The cross frequency (or the converter bandwidth) can be determined by using a network analyzer. When getting the cross frequency with no feedforward capacitor identified, the value of feedforward capacitor C6 can be calculated with the following equation:

$$C6 = \frac{1}{2\pi \times F_{CROSS}} \times \sqrt{\frac{1}{R1} \times \left(\frac{1}{R1} + \frac{1}{R2}\right)}$$

Where  $F_{CROSS}$  is the cross frequency.

To reduce transient ripple, the feedforward capacitor value can be increased to push the cross frequency to higher region. Although this can improve transient response, it also decreases phase margin and causes more ringing. In the other hand, if more phase margin is desired, the feedforward capacitor value can be decreased to push the cross frequency to lower region. In general, the feedforward capacitor range is between 10pF to 1nF.

#### **External Diode Selection**

For 5V input applications, it is recommended to add an external bootstrap diode. This helps improving efficiency. The bootstrap diode can be a low cost one such as 1N4148.

#### **PCB Layout Recommendation**

The device's performance and stability are dramatically affected by PCB layout. It is recommended to follow these general guidelines shown as below:

- 1. Place the input capacitors and output capacitors as close to the device as possible. The traces which connect to these capacitors should be as short and wide as possible to minimize parasitic inductance and resistance.

- 2. Place feedback resistors close to the FB pin.

- 3. Keep the sensitive signal (FB) away from the switching signal (LX).

- 4. The exposed pad of the package should be soldered to an equivalent area of metal on the PCB. This area should connect to the GND plane and have multiple via connections to the back of the PCB as well as connections to intermediate PCB layers. The GND plane area connecting to the exposed pad should be maximized to improve thermal performance.

- 5. Multi-layer PCB design is recommended.

Figure 23. Recommended PCB Layout Diagram

MAX

1.70

0.15

1.55 0.51 5.00 3.50

4.00

2.41 1.34

6.20 1.27

. .

DIMENSION IN MILLIMETER

MIN

1.25

0.00

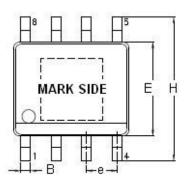

### **Outline Information**

SOP-8 (Exposed Pad) Package (Unit: mm)

| A2              | 1.25          |    |

|-----------------|---------------|----|

| В               | 0.31          |    |

| D               | 4.80          |    |

| D1              | 3.04          |    |

| E               | 3.80          |    |

| E1              | 2.15          |    |

| е               | 1.20          |    |

| н               | 5.80          |    |

| L               | 0.40          |    |

| Note : Followed | From JEDEC MO | -0 |

SYMBOLS UNIT

А

A1

| E      | )1<br> |   | 8  |

|--------|--------|---|----|

| 0      | <br>   |   | E1 |

| L<br>H |        | H |    |

Note : Followed From JEDEC MO-012-E.

# Carrier Dimensions

| Feed Direction |              |        |          |            |              |                |  |  |  |

|----------------|--------------|--------|----------|------------|--------------|----------------|--|--|--|

| Tape Size      | Pocket Pitch | Reel S | Size (A) | Reel Width | Empty Cavity | Units per Reel |  |  |  |

| (W1) mm        | (P) mm       | in     | mm       | (W2) mm    | Length mm    |                |  |  |  |

| 12             | 8            | 13     | 330      | 12.4       | 400~1000     | 2,500          |  |  |  |

#### Life Support Policy

Fitipower's products are not authorized for use as critical components in life support devices or other medical systems.