# <u>Linear Regulator</u> - Low Dropout, Very Low I<sub>q</sub>, Reset, Reset Delay

# 350 mA

The NCV8675 is a precision 5.0 V and 3.3 V fixed output, low dropout integrated voltage regulator with an output current capability of 350 mA. Careful management of light load current consumption, combined with a low leakage process, achieve a typical quiescent ground current of  $34~\mu A$ .

NCV8675 is pin for pin compatible with NCV4275 and it could replace this part when very low quiescent current is required.

The output voltage is accurate within ±2.0% for D<sup>2</sup>PAK-5 package and ±2.5% for DPAK-5 package, and maximum dropout voltage is 600 mV at full rated load current.

It is internally protected against input transients, input supply reversal, output overcurrent faults, and excess die temperature. No external components are required to enable these features.

#### **Features**

- 5 V and 3.3 V Fixed Output (2.5 V Version Available Upon Request)

- ±2.0% or ±2.5% Output Accuracy, Over Full Temperature Range

- 34  $\mu A$  Typical Quiescent Current at  $I_{out}$  = 100  $\mu A$ , 50  $\mu A$  Maximum up to 85°C

- 600 mV Maximum Dropout Voltage at 350 mA Load Current

- Wide Input Voltage Operating Range of 4.5 V to 45 V

- Internal Fault Protection

- → -42 V Reverse Voltage

- ◆ Short Circuit/Overcurrent

- ◆ Thermal Overload

- AEC-O100 Oualified

- EMC Compliant

- NCV Prefix for Automotive and Other Applications Requiring Site and Control Changes

- These are Pb-Free Devices

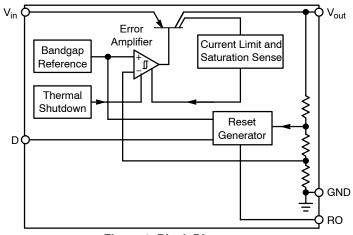

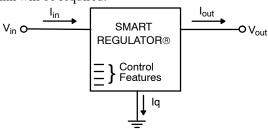

Figure 1. Block Diagram

## ON Semiconductor®

http://onsemi.com

#### MARKING DIAGRAMS

DPAK-5 DT SUFFIX CASE 175AA

D<sup>2</sup>PAK-5 DS SUFFIX CASE 936A

Pin 1. V<sub>in</sub> 2. RO

2. RO Tab. 3. GND\*

4. D

5. V<sub>out</sub>

\* Tab is connected to Pin 3 on all packages

xx = 50 (5.0 V Version) 33 (3.3 V Version)

A = Assembly Location

WL, L = Wafer Lot

Y = Year

WW = Work Week

= Pb-Free Package

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 14 of this data sheet.

#### **PIN DESCRIPTIONS**

| Symbol           | Function                                                                                                 |

|------------------|----------------------------------------------------------------------------------------------------------|

| V <sub>in</sub>  | Unregulated Input Voltage; 4.5 V to 45 V; Battery Input Voltage. Bypass to GND with a Ceramic Capacitor. |

| RO               | Reset Output; Open Collector Active Reset (Accurate when V <sub>in</sub> > 1.0 V)                        |

| GND              | Ground; Pin 3 Internally Connected to Tab                                                                |

| D                | Reset Delay; Timing Capacitor to GND for Reset Delay Function                                            |

| V <sub>out</sub> | Output; 350 mA. 22 $\mu$ F, ESR < 9 $\Omega$                                                             |

#### **MAXIMUM RATINGS**

| Pin Symbol, Parameter                           | Symbol           | Min      | Max  | Unit    |

|-------------------------------------------------|------------------|----------|------|---------|

| Input Voltage                                   | V <sub>in</sub>  | -42      | 45   | V       |

| Output Voltage                                  | V <sub>out</sub> | -0.3     | 16   | V       |

| Reset Output Voltage                            | V <sub>RO</sub>  | -0.3     | 25   | V       |

| Reset Output Current                            | I <sub>RO</sub>  | -5.0     | 5.0  | mA      |

| Reset Delay Voltage                             | V <sub>D</sub>   | -0.3     | 7.0  | V       |

| Reset Delay Current                             | I <sub>D</sub>   | -2.0     | 2.0  | mA      |

| Storage Temperature                             | T <sub>Stg</sub> | -55      | +150 | °C      |

| ESD Capability -Human Body Model -Machine Model |                  | 4<br>200 |      | kV<br>V |

| Storage Temperature                             | T <sub>Stg</sub> | -55      | +150 | °C      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

## **OPERATING RANGE**

| Pin Symbol, Parameter         | Symbol          | Min | Max | Unit |

|-------------------------------|-----------------|-----|-----|------|

| Input Voltage Operating Range | V <sub>in</sub> | 4.5 | 45  | V    |

| Junction Temperature          | $T_J$           | -40 | 150 | °C   |

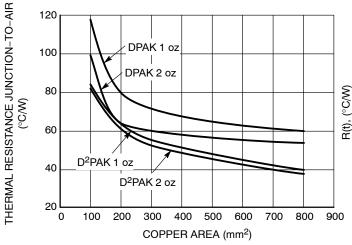

#### THERMAL RESISTANCE

| Parameter        |                    |                   | Min | Max   | Unit  |

|------------------|--------------------|-------------------|-----|-------|-------|

| Junction Ambient | D <sup>2</sup> PAK | R <sub>thja</sub> |     | 82.1  | °C AM |

| Junction Case    | D <sup>2</sup> PAK | R <sub>thjc</sub> |     | 4.3   | °C/W  |

| Junction Ambient | DPAK               | R <sub>thja</sub> |     | 112.2 | °C/W  |

| Junction Case    | DPAK               | R <sub>thjc</sub> |     | 4.3   | C/VV  |

<sup>1. 1</sup> oz., 100 mm<sup>2</sup> copper area.

#### Pb SOLDERING TEMPERATURE AND MSL

| Parameter                                                                | Symbol           | Min | Max    | Unit |

|--------------------------------------------------------------------------|------------------|-----|--------|------|

| Lead Temperature Soldering<br>Reflow (SMD styles only), Pb-Free (Note 2) | T <sub>sld</sub> |     | 265 pk | °C   |

| Moisture Sensitivity Level                                               | MSL              | 1   |        | _    |

<sup>2.</sup> Pb-Free, 60 sec - 150 sec above 217°C, 40 sec maximum at peak.

# **ELECTRICAL CHARACTERISTICS** $V_{in}$ = 13.5 V, $T_J$ = -40°C to +150°C, unless otherwise specified

| Parameter                                                                                                                                                              | Symbol                                             | Test Conditions                                                                                                                                                    | Min            | Тур            | Max            | Unit               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|--------------------|

| OUTPUT                                                                                                                                                                 | · ·                                                |                                                                                                                                                                    |                |                |                |                    |

| Output Voltage D <sup>2</sup> PAK 5.0 V Version DPAK                                                                                                                   | V <sub>out</sub>                                   | 0.1 mA $\leq$ I <sub>out</sub> $\leq$ 350 mA (Note 3)<br>6.0 V $\leq$ V <sub>in</sub> $\leq$ 16 V                                                                  | 4.900<br>4.875 | 5.000<br>5.000 | 5.100<br>5.125 | V                  |

| Output Voltage $D^2PAK$ $V_{out}$ $0.1 \text{ mA} \le I_{out} \le 350 \text{ mA} \text{ (Note 3)}$<br>3.3 V Version $DPAK$ $4.5 \text{ V} \le V_{in} \le 16 \text{ V}$ |                                                    | 3.234<br>3.217                                                                                                                                                     | 3.300<br>3.300 | 3.366<br>3.383 | V              |                    |

| Output Voltage D <sup>2</sup> PAK<br>5.0 V Version DPAK                                                                                                                | 1 3 out 1 out 1                                    |                                                                                                                                                                    | 4.900<br>4.875 | 5.000<br>5.000 | 5.100<br>5.125 | V                  |

| Output Voltage D <sup>2</sup> PAK 3.3 V Version DPAK                                                                                                                   | $V_{out}$                                          | 0.1 mA $\leq$ I <sub>out</sub> $\leq$ 200 mA (Note 3)<br>4.5 V $\leq$ V <sub>in</sub> $\leq$ 40 V                                                                  | 3.234<br>3.217 | 3.300<br>3.300 | 3.366<br>3.383 | V                  |

| Line Regulation                                                                                                                                                        | $\Delta V_{out}$<br>Versus $V_{in}$                | $I_{out} = 5 \text{ mA}$<br>6.0 V $\leq V_{in} \leq 28 \text{ V}$                                                                                                  | -25            | 5              | +25            | mV                 |

| Load Regulation                                                                                                                                                        | $\Delta V_{ m out}$<br>Versus. I $_{ m out}$       | 1.0 mA ≤ I <sub>out</sub> ≤ 350 mA (Note 3)                                                                                                                        | -40            | 5              | +40            | mV                 |

| Dropout Voltage<br>5.0 V Version                                                                                                                                       | V <sub>in</sub> – V <sub>out</sub>                 | I <sub>out</sub> = 200 mA (Notes 3 and 4)<br>I <sub>out</sub> = 350 mA (Notes 3 and 4)                                                                             | -<br>-         | 215<br>310     | 500<br>600     | mV                 |

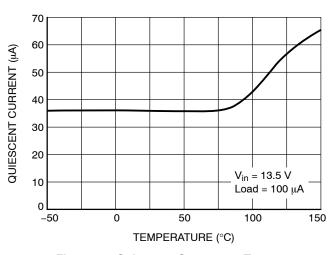

| Quiescent Current                                                                                                                                                      | Iq                                                 | $\begin{split} I_{out} &\leq 100~\mu\text{A} \\ T_J &= 25^\circ\text{C} \\ T_J &= -40^\circ\text{C to } +85^\circ\text{C} \\ T_J &= 125^\circ\text{C} \end{split}$ |                | 34<br>34<br>54 | 45<br>50<br>60 | μΑ                 |

| Active Ground Current                                                                                                                                                  | I <sub>G (ON)</sub>                                | I <sub>out</sub> = 50 mA (Note 3)<br>I <sub>out</sub> = 350 mA (Note 3)                                                                                            |                | 1.8<br>20      | 3.5<br>40      | mA                 |

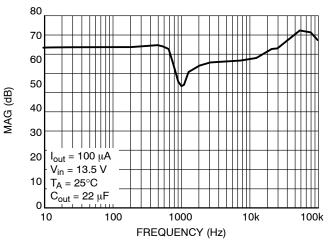

| Power Supply Rejection                                                                                                                                                 | P <sub>SRR</sub>                                   | V <sub>RIPPLE</sub> = 0.5 V <sub>PP</sub> , F = 100 Hz                                                                                                             |                | 70             |                | %/V                |

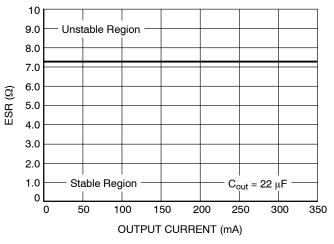

| Output Capacitor for Stability<br>5.0 V Version<br>3.3 V Version                                                                                                       | C <sub>out</sub><br>ESR<br>C <sub>out</sub><br>ESR | I <sub>out</sub> = 0.1 mA to 350 mA                                                                                                                                | 22<br>22       |                | 9              | μF<br>Ω<br>μF<br>Ω |

| RESET TIMING D AND OUTPUT R                                                                                                                                            | )                                                  |                                                                                                                                                                    | •              | •              | •              | 1                  |

| Reset Switching Threshold                                                                                                                                              | V <sub>out</sub> , r <sub>t</sub>                  | 5.0 V Version<br>3.3 V Version                                                                                                                                     | 4.50<br>2.97   | 4.65<br>3.069  | 4.80<br>3.168  | V                  |

| Reset Output Low Voltage                                                                                                                                               | $V_{ROL}$                                          | $R_{Ext} > 5.0k, V_{out} > 1.0V$                                                                                                                                   | -              | 0.20           | 0.40           | V                  |

| Reset Output Leakage Current                                                                                                                                           | I <sub>ROH</sub>                                   | $V_{ROH} = 5.0 \text{ V}$ $V_{ROH} = 3.3 \text{ V}$                                                                                                                | -<br>-         | 0<br>0         | 10<br>10       | μΑ                 |

| Reset Charging Current                                                                                                                                                 | $I_{D,C}$                                          | V <sub>D</sub> = 1.0 V                                                                                                                                             | 2.0            | 4.0            | 6.5            | μΑ                 |

| Upper Timing Threshold                                                                                                                                                 | $V_{DU}$                                           | -                                                                                                                                                                  | 1.2            | 1.3            | 1.4            | V                  |

| Lower Timing Threshold                                                                                                                                                 | $V_{LU}$                                           |                                                                                                                                                                    |                | 1.24           |                | V                  |

| Reset Delay Time 5.0 V Version 3.3 V Version                                                                                                                           |                                                    | C <sub>D</sub> = 47 nF 10                                                                                                                                          |                | 16<br>16       | 22<br>24       | ms                 |

| Reset Reaction Time                                                                                                                                                    | t <sub>rr</sub>                                    | C <sub>D</sub> = 47 nF                                                                                                                                             |                | 1.5            | 4.0            | μs                 |

| PROTECTION                                                                                                                                                             |                                                    |                                                                                                                                                                    |                |                |                |                    |

| Current Limit                                                                                                                                                          | I <sub>out(LIM)</sub>                              | V <sub>out</sub> = 4.5 V (5.0 V Version)<br>V <sub>out</sub> = 3.0 V (3.3 V Version)                                                                               | 350<br>350     |                |                | mA                 |

| Short Circuit Current Limit                                                                                                                                            | I <sub>out(SC)</sub>                               | V <sub>out</sub> = 0 V (Note 3)                                                                                                                                    | 100            | 600            |                | mA                 |

| Thermal Shutdown Threshold                                                                                                                                             | T <sub>TSD</sub>                                   | (Note 5)                                                                                                                                                           | 150            |                | 200            | °C                 |

Use pulse loading to limit power dissipation.

Dropout voltage = (V<sub>in</sub> - V<sub>out</sub>), measured when the output voltage has dropped 100 mV relative to the nominal value obtained with V<sub>in</sub> = 13.5 V.

Not tested in production. Limits are guaranteed by design.

0.07 QUIESCENT CURRENT (mA) 0.06 0.05 0.04 0.03 0.02  $V_{in} = 13.5 \text{ V}$ 0.01 Load = 100  $\mu$ A 0 100 150 -50 0 50 TEMPERATURE (°C)

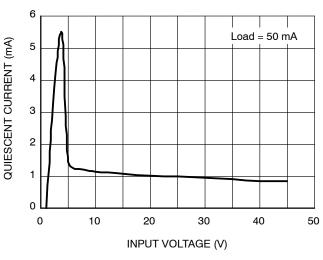

Figure 8. NCV8675 Quiescent Current vs. Input Voltage (5 V Version)

Figure 9. NCV8675 Quiescent Current vs. Temperature (5 V Version)

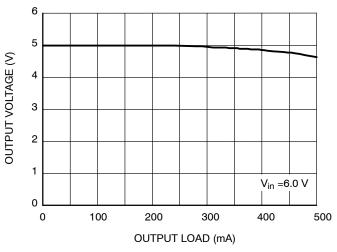

Figure 10. NCV8675 Output Voltage vs. Output Load (5 V Version)

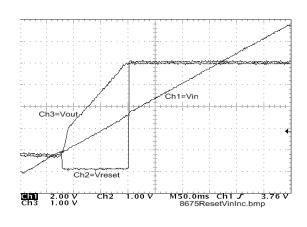

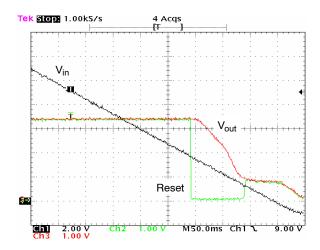

Figure 11. Reset vs. Output Voltage (V<sub>in</sub> Rising) (5 V Version)

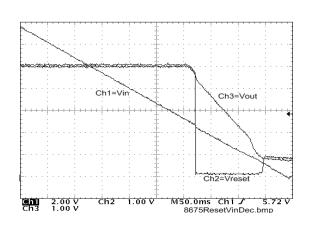

Figure 12. Reset vs. Output Voltage (V<sub>in</sub> Falling) (5 V Version)

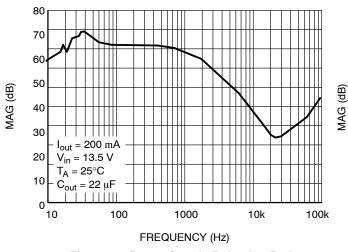

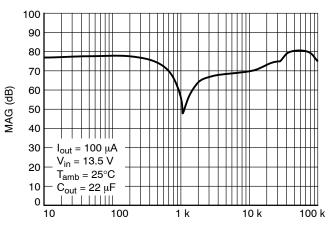

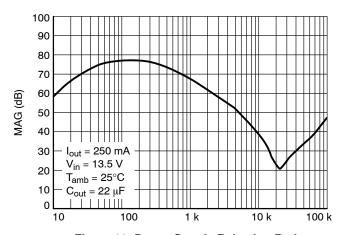

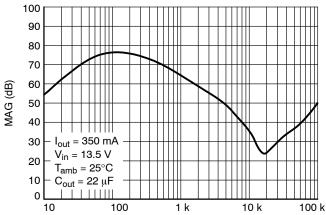

Figure 13. Power Supply Rejection Ratio (5 V Version)

Figure 14. Power Supply Rejection Ratio (5 V Version)

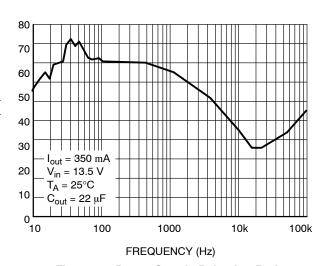

Figure 15. Power Supply Rejection Ratio (5 V Version)

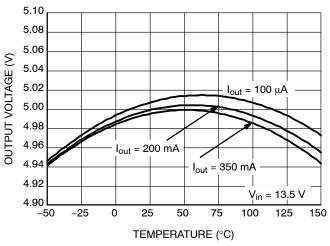

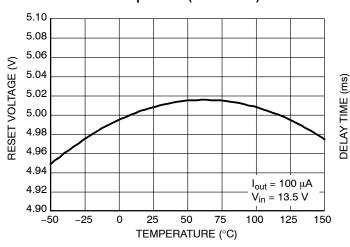

Figure 16. NCV8675 Output Voltage vs. Temperature (5 V Version)

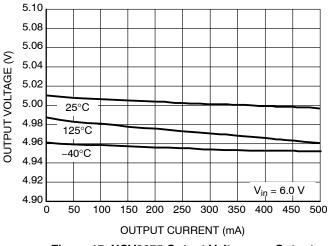

Figure 17. NCV8675 Output Voltage vs. Output Load (5 V Version)

Figure 18. NCV8675 Reset Voltage vs. Temperature (5 V Version)

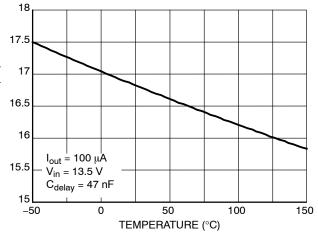

Figure 19. NCV8675 Reset Delay Time vs. Temperature (5 V Version)

$V_{in} = 13.5 \text{ V}$ -50 -25 TEMPERATURE (°C)

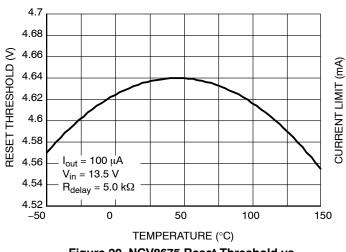

Figure 20. NCV8675 Reset Threshold vs. Temperature (5 V Version)

Figure 21. NCV8675 Current Limit Threshold vs. Temperature (5 V Version)

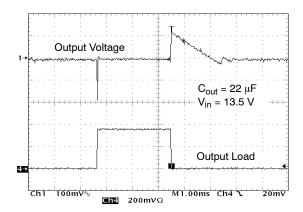

Figure 22. NCV8675 100 μA – 350 mA Load Transient (5 V Version)

Figure 23. ESR Stability vs. Output Current (3.3 V Version)

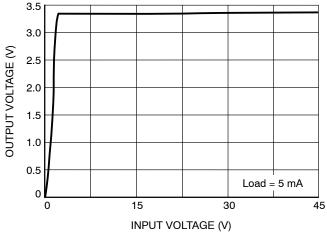

Figure 24. Input Voltage vs. Output Voltage (3.3 V Version)

Figure 25. Quiescent Current vs. Temperature (3.3 V Version)

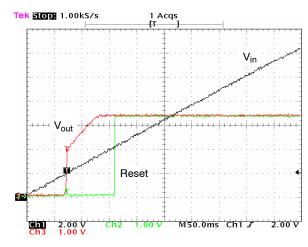

Figure 26. Reset vs. Output Voltage (V<sub>in</sub> Rising) (3.3 V Version)

Figure 27. Reset vs. Output Voltage (V<sub>in</sub> Falling) (3.3 V Version)

Figure 28. Power Supply Rejection Ratio (3.3 V Version)

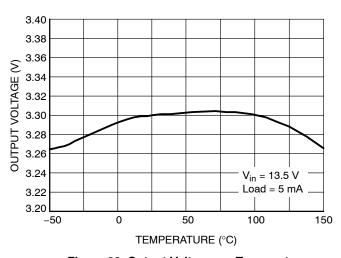

Figure 29. Power Supply Rejection Ratio (3.3 V Version)

Figure 30. Power Supply Rejection Ratio (3.3 V Version)

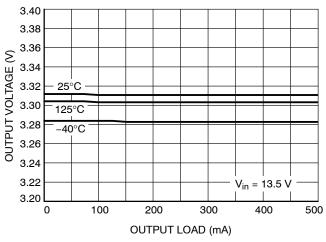

Figure 31. Output Voltage vs. Output Load (3.3 V Version)

Figure 32. Output Voltage vs. Temperature (3.3 V Version)

Figure 33. Reset Delay Time vs. Temperature (3.3 V Version)

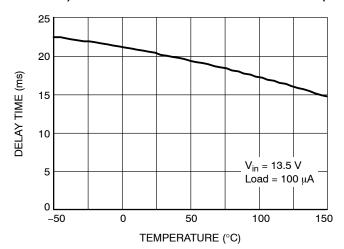

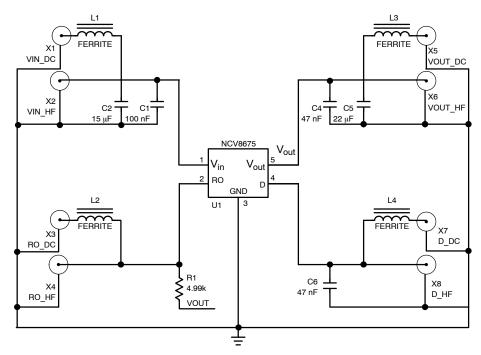

Figure 34. Application Circuits

#### **Circuit Description**

The NCV8675 is an integrated low dropout regulator that provides 5.0 V 350 mA, or 3.3 V 350 mA protected output and a signal for power on reset. The regulation is provided by a PNP pass transistor controlled by an error amplifier with a bandgap reference, which gives it the lowest possible drop out voltage and best possible temperature stability. The output current capability is 350 mA, and the base drive quiescent current is controlled to prevent over saturation when the input voltage is low or when the output is overloaded. The regulator is protected by both current limit and thermal shutdown. Thermal shutdown occurs above 150°C to protect the IC during overloads and extreme ambient temperatures. The delay time for the reset output is adjustable by selection of the timing capacitor. See Figure 34, Test Circuit, for circuit element nomenclature illustration.

## Regulator

The error amplifier compares the reference voltage to a sample of the output voltage  $(V_{out})$  and drives the base of a PNP series pass transistor by a buffer. The reference is a bandgap design to give it a temperature–stable output. Saturation control of the PNP is a function of the load current and input voltage. Oversaturation of the output power device is prevented, and quiescent current in the ground pin is minimized.

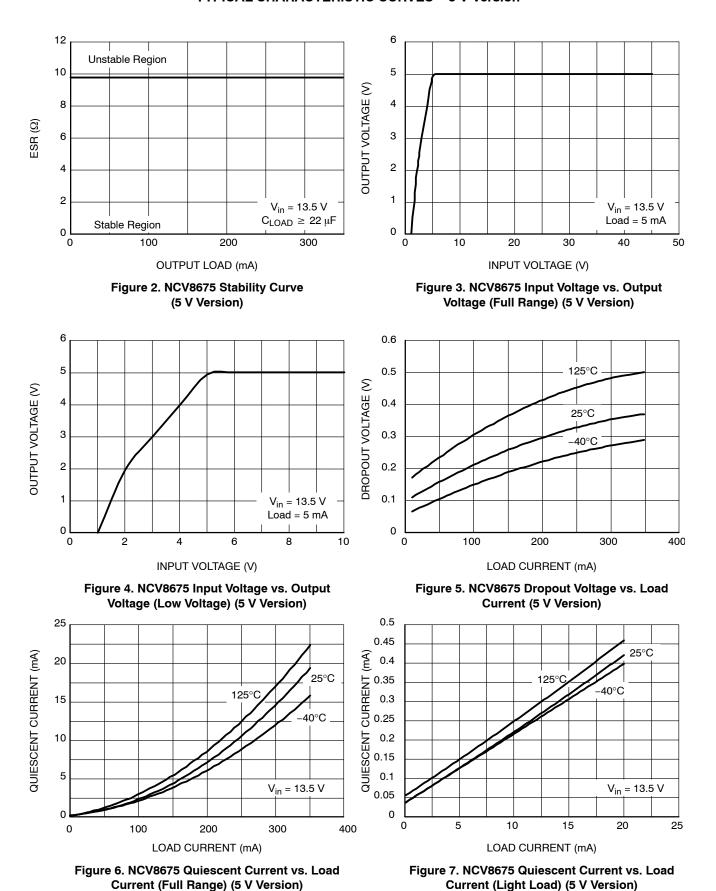

#### **Regulator Stability Considerations**

The input capacitor ( $C_{in}$ ) is necessary to stabilize the input impedance to avoid voltage line influences. The output capacitor helps determine three main characteristics of a linear regulator: startup delay, load transient response and loop stability. The capacitor value and type should be based on cost, availability, size and temperature constraints. Ceramic, tantalum, or electrolytic capacitors of 22  $\mu$ F, or greater, are stable with very low ESR values. Refer to

Figure 2 for specific ESR ratings. The aluminum electrolytic capacitor is the least expensive solution, but, if the circuit operates at low temperatures ( $-25^{\circ}$ C to  $-40^{\circ}$ C), both the capacitance and ESR of the capacitor will vary considerably. The capacitor manufacturer's data sheet usually provides this information. The value for the output capacitor  $C_{out}$  shown in Figure 13, Test Circuit, should work for most applications; however, it is not necessarily the optimized solution.

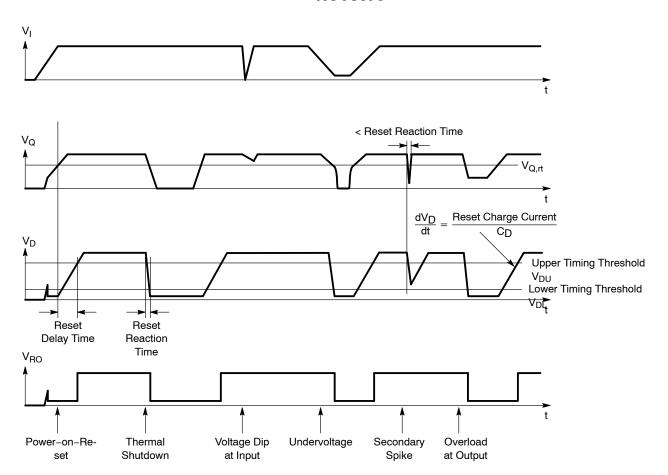

#### **Reset Output**

The reset output is used as the power on indicator to the microcontroller. This signal indicates when the output voltage is suitable for reliable operation of the controller. It pulls low when the output is not considered to be ready. RO is pulled up to  $V_{out}$  by an external resistor, typically 5.0 k $\Omega$ in value. The input and output conditions that control the Reset Output and the relative timing are illustrated in Figure 35, Reset Timing. Output voltage regulation must be maintained for the delay time before the reset output signals a valid condition. The delay for the reset output is defined as the amount of time it takes the timing capacitor on the delay pin to charge from a residual voltage of 0 V to the upper timing threshold voltage V<sub>DU</sub> of 1.3 V. The charging current for this is I<sub>D</sub> of 4 µA and D pin voltage in steady state is typically 2.4 V. By using typical IC parameters with a 47 nF capacitor on the D Pin, the following time delay is derived:

$$\begin{split} t_{RD} &= \, C_D^{\,\,*} \, V_{DU}^{} / I_D^{} \\ t_{RD} &= \, 47 \; nF \,^* \, (1.3 \; V) / 4 \; \mu A \, = \, 15.3 \; ms \end{split}$$

Other time delays can be obtained by changing the  $C_D$  capacitor value. The Delay Time can be reduced by decreasing the capacitance of  $C_D$ . Using the formula above, Delay can be reduced as desired. Leaving the Delay Pin open is not desirable as it can result in unwanted signals being coupled onto the pin.

Figure 35. Reset Timing

# Calculating Power Dissipation in a Single Output Linear Regulator

The maximum power dissipation for a single output regulator (Figure 36) is:

$$PD(max) = [Vin(max) - Vout(min)] Iout(max) + VI(max)Iq$$

(1)

where

$\begin{array}{lll} V_{in(max)} & \text{is the maximum input voltage,} \\ V_{out(min)} & \text{is the minimum output voltage,} \\ I_{out(max)} & \text{is the maximum output current for the} \\ & & \text{application,} \\ I_{q} & \text{is the quiescent current the regulator} \\ & & \text{consumes at } I_{O(max)}. \end{array}$

Once the value of  $P_{D(max)}$  is known, the maximum permissible value of  $R_{\theta JA}$  can be calculated:

$$R_{\theta JA} = \frac{150^{\circ}C - T_{A}}{P_{D}}$$

(2)

The value of  $R_{\theta JA}$  can then be compared with those in the package section of the data sheet. Those packages with  $R_{\theta JA}$ 's less than the calculated value in Equation 2 will keep the die temperature below 150°C.

In some cases, none of the packages will be sufficient to dissipate the heat generated by the IC, and an external heatsink will be required.

Figure 36. Single Output Regulator with Key Performance Parameters Labeled

#### **Heatsinks**

A heatsink effectively increases the surface area of the package to improve the flow of heat away from the IC and into the surrounding air.

Each material in the heat flow path between the IC and the outside environment will have a thermal resistance. Like series electrical resistances, these resistances are summed to determine the value of  $R_{\theta JA}$ :

$$R_{\theta}JA = R_{\theta}JC + R_{\theta}CS + R_{\theta}SA \tag{3}$$

where

$\begin{array}{ll} R_{\theta JC} & \text{is the junction-to-case thermal resistance,} \\ R_{\theta CS} & \text{is the case-to-heatsink thermal resistance,} \\ R_{\theta SA} & \text{is the heatsink-to-ambient thermal resistance.} \end{array}$

$R_{\theta JC}$  appears in the package section of the data sheet. Like  $R_{\theta JA}$ , it too is a function of package type.  $R_{\theta CS}$  and  $R_{\theta SA}$  are functions of the package type, heatsink and the interface between them. These values appear in heatsink data sheets of heatsink manufacturers.

Thermal, mounting, and heatsinking considerations are discussed in the ON Semiconductor application note AN1040/D.

Figure 37. JA vs. Copper Spreader Area

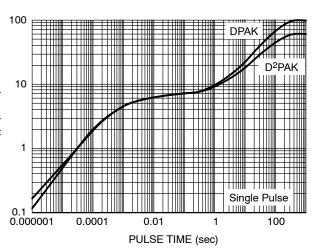

Figure 38. NCV8675 @ PCB Cu Area 100 mm<sup>2</sup> PCB Cu thk 1 oz

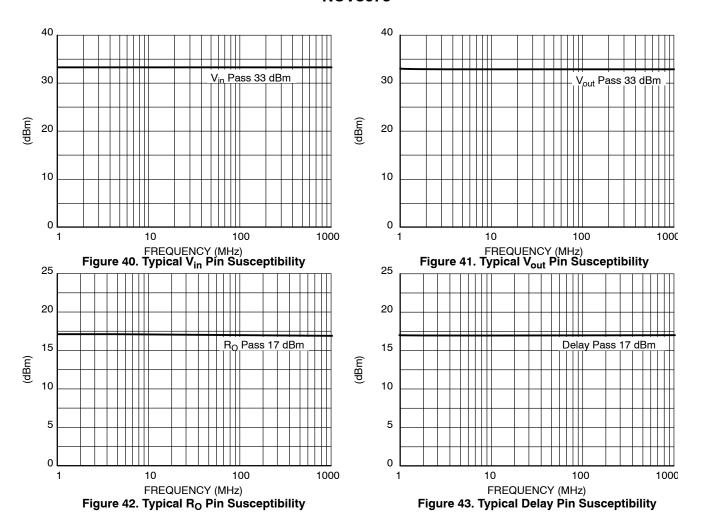

#### **EMC-Characteristics: Conducted Susceptibility**

All EMC-Characteristics are based on limited samples and no part of production test according to 47A/658/CD IEC62132-4 (direct Power Injection).

#### **Test Conditions**

Supply Voltage  $V_{in} = 12 \text{ V}$

Temperature  $T_A = 23^{\circ}C + -5^{\circ}C$

Load  $R_L = 100 \Omega$

#### **Direct power Injection**

33d Bm (Note 1) forward power CW for global pin (Note 2) 17 dBm (Note 1) forward power CW for local pin (Note 3)

# Acceptance Criteria

Amplitude Dev. max 4% of Output Voltage Reset outputs remain in correct state + -1 V

- 1. dBm means dB milli-Watts,  $P_{(dBm)} = 10 \log (P_{(mW)})$

- 2. A global pin carries a signal or power which enters or leaves the application board

- A local pin carries a signal or power which does not leave the application board. It remains on the application board as a signal between two components

Figure 39. Test Circuit

#### **ORDERING INFORMATION**

| Device         | Output Voltage | Package            | Shipping <sup>†</sup> |

|----------------|----------------|--------------------|-----------------------|

| NCV8675DS50G   |                | D <sup>2</sup> PAK | 50 Units / Rail       |

| NCV8675DS50R4G | 5.0 V          | (Pb-Free)          | 800 / Tape & Reel     |

| NCV8675DT50RKG | 3.0 V          | DPAK<br>(Pb-Free)  | 2500 / Tape & Reel    |

| NCV8675DS33G   |                | D <sup>2</sup> PAK | 50 Units / Rail       |

| NCV8675DS33R4G | 3.3 V          | (Pb-Free)          | 800 / Tape & Reel     |

| NCV8675DT33RKG |                | DPAK<br>(Pb-Free)  | 2500 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

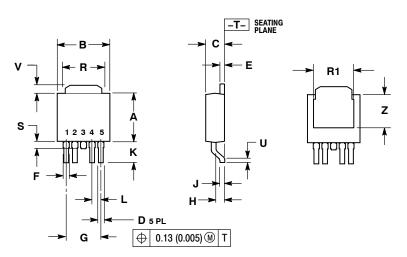

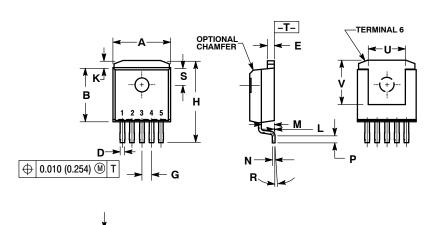

#### **PACKAGE DIMENSIONS**

# DPAK-5, CENTER LEAD CROP

CASE 175AA-01 **ISSUE A**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: INCH.

|     | INCHES |       | MILLIN | IETERS |

|-----|--------|-------|--------|--------|

| DIM | MIN    | MAX   | MIN    | MAX    |

| Α   | 0.235  | 0.245 | 5.97   | 6.22   |

| В   | 0.250  | 0.265 | 6.35   | 6.73   |

| C   | 0.086  | 0.094 | 2.19   | 2.38   |

| D   | 0.020  | 0.028 | 0.51   | 0.71   |

| Е   | 0.018  | 0.023 | 0.46   | 0.58   |

| F   | 0.024  | 0.032 | 0.61   | 0.81   |

| G   | 0.180  | BSC   | 4.56   | BSC    |

| H   | 0.034  | 0.040 | 0.87   | 1.01   |

| J   | 0.018  | 0.023 | 0.46   | 0.58   |

| K   | 0.102  | 0.114 | 2.60   | 2.89   |

| L   | 0.045  | BSC   | 1.14   | BSC    |

| R   | 0.170  | 0.190 | 4.32   | 4.83   |

| R1  | 0.185  | 0.210 | 4.70   | 5.33   |

| S   | 0.025  | 0.040 | 0.63   | 1.01   |

| כ   | 0.020  |       | 0.51   |        |

| ٧   | 0.035  | 0.050 | 0.89   | 1.27   |

| Z   | 0.155  | 0.170 | 3.93   | 4.32   |

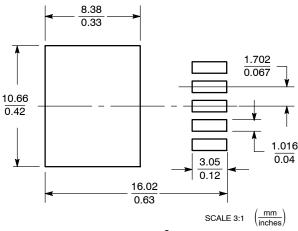

#### **SOLDERING FOOTPRINT\***

SCALE 4:1  $\left(\frac{\text{mm}}{\text{inches}}\right)$

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

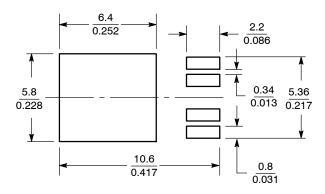

#### PACKAGE DIMENSIONS

#### D<sup>2</sup>PAK-5 CASE 936A-02 ISSUE C

# SOLDERING FOOTPRINT\*

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982. 2. CONTROLLING DIMENSION: INCH.

- 3. TAB CONTOUR OPTIONAL WITHIN DIMENSIONS A AND K.

- 4. DIMENSIONS U AND V ESTABLISH A MINIMUM MOUNTING SURFACE FOR TERMINAL 6.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH OR GATE PROTRUSIONS. MOLD FLASH AND GATE PROTRUSIONS NOT TO EXCEED 0.025 (0.635) MAXIMUM.

|     | INCHES    |       | MILLIN    | IETERS |  |

|-----|-----------|-------|-----------|--------|--|

| DIM | MIN       | MAX   | MIN       | MAX    |  |

| Α   | 0.386     | 0.403 | 9.804     | 10.236 |  |

| В   | 0.356     | 0.368 | 9.042     | 9.347  |  |

| С   | 0.170     | 0.180 | 4.318     | 4.572  |  |

| D   | 0.026     | 0.036 | 0.660     | 0.914  |  |

| E   | 0.045     | 0.055 | 1.143     | 1.397  |  |

| G   | 0.067     | BSC   | 1.702     | BSC    |  |

| Н   | 0.539     | 0.579 | 13.691    | 14.707 |  |

| K   | 0.050     | REF   | 1.270 RE  |        |  |

| L   | 0.000     | 0.010 | 0.000     | 0.254  |  |

| М   | 0.088     | 0.102 | 2.235     | 2.591  |  |

| N   | 0.018     | 0.026 | 0.457     | 0.660  |  |

| Р   | 0.058     | 0.078 | 1.473     | 1.981  |  |

| R   | 5° REF    |       | 5° REF    |        |  |

| S   | 0.116 REF |       | 2.946 REF |        |  |

| U   | 0.200 MIN |       | 5.080 MIN |        |  |

| V   | 0.250 MIN |       | 6.350 MIN |        |  |

#### 5-LEAD D2PAK

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual. SOLDERRM/D.

ON Semiconductor and was are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303-675-2175 or 800-344-3860 Toll Free USA/Canada

Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative