#### DESCRIPTION

The PT5606 is a high speed high voltage (600V) driver to control power devices like MOS-transistors or IGBTs in half bridge systems with dependent high and low side referenced output channels. The logic input is compatible with standard CMOS or LSTTL output, down to 3.3V logic. The device includes an under-voltage detection unit with hysteresis characteristic and prevents power devices against large amount of conduction loss, when voltage margin of gate is not high enough. The output drivers feature a high pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to drive an N-channel power MOSFET or IGBT, in the high side configuration which operates up to 600 volts.

### **APPLICATIONS**

- Appliance motor drives—air conditioners, washing machines, refrigerator, dish washer, Fans

- General purpose inverters

- Electric bike, Electric tools

- Lighting, switching power supply

### **FEATURES**

- Drives two IGBT/MOSFET power devices

- high side channel fully operate up to +600V

- Gate drive supplies from 10V to 20 V per channel

- Under-voltage lockout

- Advanced input filter

- Built-in dead-time protection: 0.5us

- IO+/-: 290/620mA, large sourcing current to bypass miller effect

- Shoot-through (cross-conduction) protection

- 3.3 V/5V/15V input logic compatible

- Matched propagation delays for all channels

- Matched dead time

- High side output in phase with HIN input

- Low side output out of phase with IIN input

- Tolerant to negative transient voltage, immunity of dv/dt up to 50V/ns

- Low di/dt gate drive for better noised immunity

- -40°C to 125°C operating range

- SOP8L Package available

- Lead-free

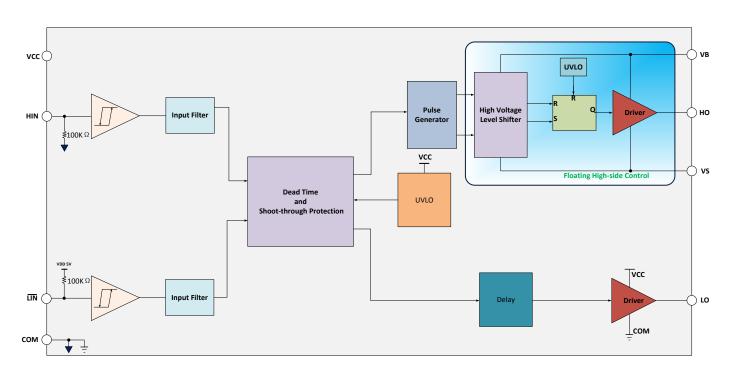

### **BLOCK DIAGRAM**

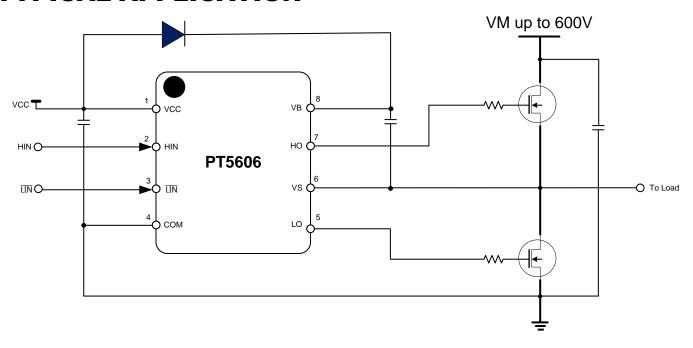

## **TYPICAL APPLICATION**

V1.0 2 December 2016

## **ORDER INFORMATION**

| Valid Part Number | Package Type        | Top Code |

|-------------------|---------------------|----------|

| PT5606            | 8-Pin, SOP, 150 MIL | PT5606-S |

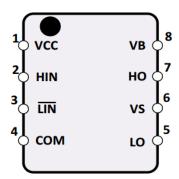

## **PIN CONFIGURATION**

PT5606-S

Pin Configuration of PT5606

## **PIN DESCRIPTION**

| Pin Name | Description                                                   | Pin No. |

|----------|---------------------------------------------------------------|---------|

| VCC      | Low-side supply voltage                                       | 1       |

| HIN      | Logic input for high-side gate driver output(HO), in phase    | 2       |

| LIN      | Logic input for low-side gate driver output(LO), out of phase | 3       |

| COM      | Low-side gate drive return                                    | 4       |

| LO       | Low-side driver output                                        | 5       |

| VS       | High voltage floating supply return                           | 6       |

| НО       | High-side driver output                                       | 7       |

| VB       | High-side gate drive floating supply                          | 8       |

V1.0 3 December 2016

### **FUNCTION DESCRIPTION**

#### LOW SIDE POWER SUPPLY

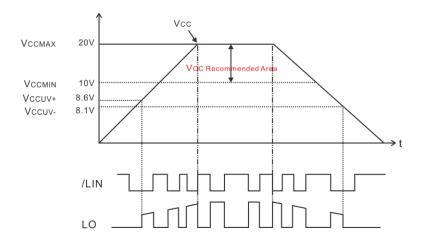

VCC is the low side supply and it provides power both to input logic and to low side output power stage. The built-in under-voltage lockout circuit enables the device to operate at sufficient power on when a typical VCC supply voltage higher than  $V_{\text{CCUV}_{-}}$  =8.6 is present, shown as Figure 1. The IC shuts down the gate drivers outputs, when the VCC supply voltage is below  $V_{\text{CCUV}_{-}}$  =8.1 V, shown as Figure 1. This prevents the external power devices from extremely low gate voltage levels during on-state and therefore from excessive power dissipation.

Figure.1: VCC supply UVLO operating area

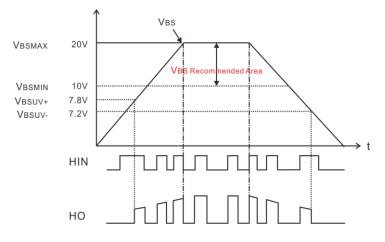

#### HIGH SIDE POWER SUPPLY

VB to VS is the high side supply voltage. The totally high side circuitry can float with respect to COM following the external high side power device emitter/source voltage. Due to the internally low power consumption, the whole high side circuitry can be supplied by bootstrap topology connected to VCC, and it can be powered with small bootstrap capacitor tied between PIN VB and PIN VS.

The device operating area as a function of the supply voltage is given in Figure 2.

Figure.2: VBS supply UVLO operating area

V1.0 4 December 2016

#### LOW SIDE AND HIGH CONTROL INPUT LOGIC

The Schmitt trigger threshold of each input is designed enough low such to guarantee LSTTL and CMOS compatibility down to 3.3 V controller outputs. Input Schmitt trigger and advanced noise filter provide beneficial noise rejection to short input pulses.

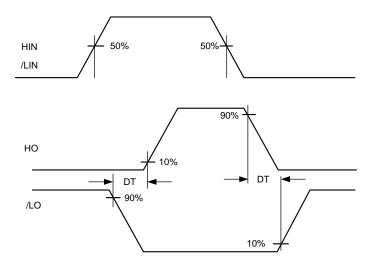

#### **DEAD TIME**

Figure.3: Dead Time

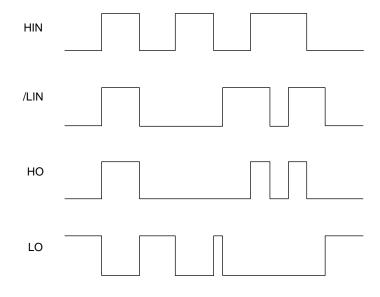

### INPUT/OUTPUT TIMING DIAGRAM

Figure.4: Timing diagram

V1.0 5 December 2016

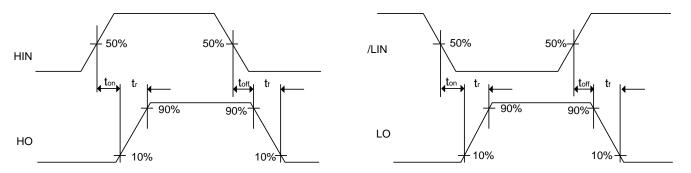

## **SWITCHING TIME WAVEFORM**

Figure.5: switching time waveform

V1.0 6 December 2016

### **ABSOLUTE MAXIMUM RATINGS**

Stresses exceeding the absolute maximum ratings may damage the device or make the function abnormal. All the voltage parameters are absolute voltages referenced to COM unless otherwise stated in the table.

| Parameter                                          | Symbol                               | Min.                | Max.                | Units |

|----------------------------------------------------|--------------------------------------|---------------------|---------------------|-------|

| High-side floating supply voltage                  | V <sub>B</sub>                       | -0.3                | 625                 |       |

| High-side offset voltage                           | Vs                                   | V <sub>B</sub> -25  | V <sub>B</sub> +0.3 |       |

| High-side gate driver output voltage               | V <sub>HO</sub>                      | V <sub>S</sub> -0.3 | Vs +0.3             |       |

| Low-side gate driver output voltage                | $V_{LO}$                             | COM-0.3             | Vcc+0.3             | V     |

| Logic input voltage(HIN, $\overline{\text{LIN}}$ ) | V <sub>HIN</sub><br>V <del>LIN</del> | -0.3                | 25                  |       |

| Low-side supply voltage                            | Vcc                                  | -0.3                | 25                  |       |

| Allowable offset voltage slew rate                 | DV/DT                                | -                   | 50                  | V/ns  |

| Package power dissipation @ T <sub>A</sub> ≤+25°C  | PD                                   | -                   | 0.625               | W     |

| Thermal resistance, junction to ambient            | Rth <sub>JA</sub>                    |                     | 200                 | °C/W  |

| Junction temperature                               | TJ                                   | -50                 | +150                |       |

| Storage temperature                                | Ts                                   | -50                 | +150                | °C    |

| Lead temperature (soldering, 10 seconds)           | TL                                   | -                   | 300                 |       |

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                       | Symbol                               | Min.  | Тур. | Max.           | Units |

|-------------------------------------------------|--------------------------------------|-------|------|----------------|-------|

| Low-side supply voltage                         | Vcc                                  | 10    | -    | 20             |       |

| High-side Floating Supply Offset Voltage(Note1) | Vs                                   | -6    | -    | 600            |       |

| High-side Floating Supply Voltage               | V <sub>B</sub>                       | Vs+10 | -    | Vs+20          |       |

| High-side gate driver output voltage            | Vно                                  | Vs    | -    | V <sub>B</sub> | V     |

| Low-side gate driver output voltage             | $V_{LO}$                             | COM   | -    | Vcc            |       |

| Logic input voltage                             | V <sub>HIN</sub><br>V <del>LIN</del> | 0     | -    | 5              |       |

| IC operating junction temperature               | TJ                                   | -40   | -    | +125           | °C    |

#### Note:

V1.0 7 December 2016

<sup>1)</sup> For normal logic operation, it is recommended to keep the VS above -6V referenced to COM.

### STATIC ELECTRICAL CHARACTERISTICS

$(V_{CC}\text{-COM})=(V_B\text{-}V_S)=15V$ . TAMB=25°C unless otherwise specified, The  $V_{IN}$ ,  $V_{TH}$  and  $I_{IN}$  parameters are referenced to COM. The  $V_O$  and  $I_O$  parameters are referenced to COM and are applicable to the respective output leads: HO or LO.

| Parameter                                                                                          | Symbol               | Test Conditions                                                                         | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------|------|------|------|------|

| Low Side Power Supply Characteristics                                                              |                      |                                                                                         |      |      |      |      |

| VCC quiescent current                                                                              | lavcc                | V <sub>HIN</sub> =0,V <u>IIN</u> =5V                                                    | -    | 180  | 250  | μΑ   |

| VCC supply under-voltage positive going threshold                                                  | Vccuv+               |                                                                                         | 7.7  | 8.6  | 9.5  |      |

| VCC supply under-voltage negative going threshold                                                  | V <sub>CCUV</sub> -  |                                                                                         | 7.2  | 8.1  | 9    | V    |

| V <sub>CC</sub> supply under-voltage lockout hysteresis                                            | Vcchys               |                                                                                         | -    | 0.5  | -    |      |

| High Side Floating Power Supply Characteristics                                                    |                      |                                                                                         |      |      |      |      |

| High side VBS supply under-voltage positive going threshold                                        | V <sub>BSUV+</sub>   |                                                                                         | 6.6  | 7.8  | 9    |      |

| High side VBS supply under-voltage negative going threshold                                        | V <sub>BSUV</sub> -  |                                                                                         | 6    | 7.2  | 8.4  | V    |

| High side VBS supply under-voltage lockout hysteresis                                              | V <sub>BSUVHYS</sub> |                                                                                         | -    | 0.6  | -    |      |

| High side VBS quiescent current                                                                    | IQBS                 | V <sub>BS</sub> =15V                                                                    | -    | 50   | 85   |      |

| Offset supply leakage current                                                                      | I <sub>LK</sub>      | V <sub>B</sub> =V <sub>S</sub> =600V<br>V <sub>CC</sub> =0V                             | -    | -    | 10   | μA   |

| Gate Driver Output Section                                                                         |                      |                                                                                         |      |      |      |      |

| Output High Short-Circuit Pulse Current                                                            | I <sub>O+</sub>      | V <sub>HO</sub> =V <sub>S</sub> =0,<br>V <sub>HO</sub> =V <sub>B</sub> =15V,<br>PW<10us | -    | 290  | -    |      |

| Output Low Short-Circuit Pulse Current                                                             | lo-                  | V <sub>LO</sub> =COM=0,<br>V <sub>LO</sub> =V <sub>CC</sub> =15V,<br>PW<10us            | -    | 620  | -    | mA   |

| High level output voltage drop, V <sub>CC</sub> -V <sub>LO</sub> ,V <sub>BS</sub> -V <sub>HO</sub> | $\Delta V_{OH}$      | Io+= 20 mA                                                                              | -    | 0.4  | 1    | V    |

| Low level output voltage drop                                                                      | $\Delta V_{OL}$      | Io-= 20 mA                                                                              | -    | 0.15 | 0.3  | V    |

| Allowable Negative Vs Pin Voltage for COM                                                          | Vsn                  | Fixed V <sub>BS</sub> =15V                                                              | -6   | -    | -    | V    |

| Logic Input Section                                                                                |                      |                                                                                         |      |      |      |      |

| Logic"1" Input voltage HIN and LIN                                                                 | VIH                  |                                                                                         | 2.5  | _    | _    |      |

| Logic"0" Input voltage HIN and LIN                                                                 | V <sub>IL</sub>      |                                                                                         | -    | -    | 0.8  | 1    |

| Input positive going threshold                                                                     | V <sub>IN,TH+</sub>  |                                                                                         | -    | 1.9  | -    | V    |

| Input negative going threshold                                                                     | VIN,TH-              |                                                                                         | -    | 1.4  | -    |      |

| Logic "1" Input bias current                                                                       | I <sub>HIN+</sub>    | V <sub>IN</sub> =5V                                                                     | -    | 50   | 90   |      |

| Logic "0" Input bias current                                                                       | I <sub>HIN-</sub>    | V <sub>IN</sub> =0V                                                                     | -    | 0    | 1    |      |

| Logic "1" Input bias current                                                                       | I <sub>LIN+</sub>    | V <sub>IN</sub> =5V                                                                     | -    | 0    | 1    | μΑ   |

| Logic "0" Input bias current                                                                       | I <sub>LIN</sub> -   | V <sub>IN</sub> =0V                                                                     | -    | 50   | 90   |      |

V1.0 8 December 2016

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

$(V_{CC}\text{-COM}) = (V_B\text{-}V_S)=15V$ ,  $V_S=COM$ , and  $C_{HO}=C_{LO}=1nF$  unless otherwise specified, TAMB=25°C.

| Parameter                        | Symbol           | Test Conditions                                                | Min. | Тур. | Max. | Unit |

|----------------------------------|------------------|----------------------------------------------------------------|------|------|------|------|

| VCC operating Vcc supply current | Ivccop           | f LIN=20K,<br>f HIN =20K,                                      | -    | 1    | 1.5  | mA   |

| Turn-On propagation delay        | ton              |                                                                | 300  | 500  | 700  |      |

| Turn-Off propagation delay       | toff             |                                                                | 300  | 500  | 700  |      |

| Turn-On rise time                | t <sub>R</sub>   |                                                                | -    | 70   | -    |      |

| Turn-Off fall time               | t <sub>F</sub>   |                                                                | 1    | 32   | -    |      |

| Input filter                     | t <sub>flt</sub> | V <sub>IN</sub> =0 or 5V,                                      | 100  | 250  | 400  | ns   |

| Dead Time                        | DT               | HIN and LIN inputs without external dead time                  | 250  | 500  | 750  | 115  |

| Delay Matching(ton, toff)        | MT               | HIN and LIN inputs with external dead time >2µs                | -    | -    | 50   |      |

| Output Pulse-Width Matching      | PM               | PW <sub>IN</sub> =10µs, PM=PW <sub>OUT</sub> -PW <sub>IN</sub> | -    | -    | 50   |      |

V1.0 9 December 2016

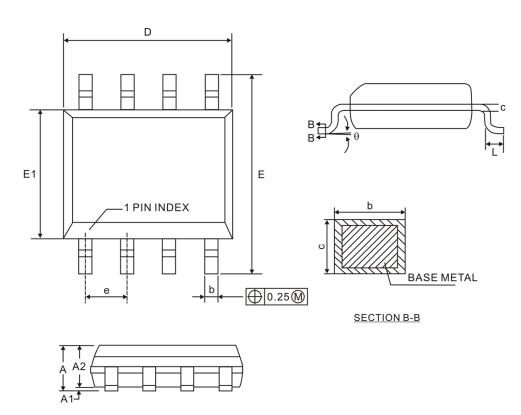

## **PACKAGE INFORMATION**

# 8 PINS, SOP, 150MIL

| Cumbal | Dimension |      |      |  |  |  |

|--------|-----------|------|------|--|--|--|

| Symbol | Min.      | Nom. | Max. |  |  |  |

| Α      | 1.35      | 1.60 | 1.77 |  |  |  |

| A1     | 0.08      | 0.15 | 0.28 |  |  |  |

| A2     | 1.20      | 1.40 | 1.65 |  |  |  |

| b      | 0.33      | •    | 0.51 |  |  |  |

| С      | 0.17      | -    | 0.26 |  |  |  |

| е      | 1.27 BSC  |      |      |  |  |  |

| D      | 4.70      | 4.90 | 5.10 |  |  |  |

| E      | 5.80      | 6.00 | 6.20 |  |  |  |

| E1     | 3.70      | 3.90 | 4.10 |  |  |  |

| L      | 0.38      | 0.60 | 1.27 |  |  |  |

| θ      | 0°        | -    | 8°   |  |  |  |

#### Notes:

- 1. Refer to JEDEC MS-012 AA

- 2. Unit: mm