# CWQ1000<sup>®</sup> Datasheet

Qi Compliant 15W Wireless Power Transmitter IC

## **General Description**

CWQ1000 can deliver up to 15W as a highly-integrated single-chip wireless medium power transmitter IC. It can be configured to receive its input power from USB or AC adapter. Our chip integrates a power amp driver, a wide range DCDC converter, and communication controllers which use Amplitude Shift Keying (ASK) and Frequency Shift Keying (FSK). Our chip includes a 32-bit ARM Cortex M0 processor in order to offer high level of programmability according to its applications. Communication and control units (CCU) can accommodate WPC protocol including fault condition handling associated with power transfer. The CCU supports the foreign object detection (FOD) extension. Also, the chip includes over-temperature and voltage protection.

# **Features Overview**

- WPC-1.2.4 compliant for MP-A2 medium power specification

- High-efficiency power transfer system supporting baseline power profile (<5W) and extended power profile (<15W)</li>

- Overall system efficiency up to 90%

- Input operating voltage of 4.5V to 20V, supporting USB and AC adapter

- Integrated pre-amplify drivers for external power amp

- Integrated high-efficiency DCDC converter

- Integrated 32-bit ARM Cortex M0 processor

- SRAM for program memory and data memory

- Bi-directional channel communication

- FSK modulation for PTx to PRx

- ASK demodulation for PRx to PTx

- 12-bit ADC for voltage/current measurement

- I2C programmable interface

- Foreign object detection

- Current sensing

- Over voltage protection

- Over current limit

- Over-temperature protection

- Optional external power amp configuration

- 128-bit One-Time-Programmable Device

- Low standby power

### Applications

- Wireless charging pads

- Wireless power solutions for Mobile Applications

Information furnished by CELFRAS is believed to be accurate and reliable. However, no responsibility is assumed by CELFRAS for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of CELFRAS.

## 1. Description for Implementation

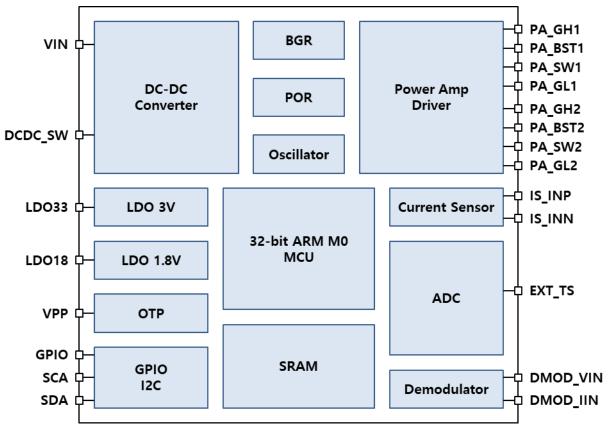

Figure 1. CWQ1000 Block Diagram

#### 1.1 Overview

A wireless power charging system is composed of transmitter and receiver. In general, wireless power transmitter will transfer AC power using a power amplifier through a TX inductor coil. Then wireless power receiver will receive AC power through an RX inductor coil which is strongly coupled with the TX coil. In transmitter part, power amplifier (PA) will change the DC power to AC power and transfer the AC power to the TX coil.

Figure1 shows the block diagram of CWQ1000 wireless charging transmitter IC. CWQ1000 transmitter will support power transfer up to 15W and it is compliant with WPC 1.2.4 standard. It consists of power amp driver, step down DC-DC converter, internal LDOs, ADC, 32-bit ARM M0 MCU, SRAM and etc.

#### 1.2 DC-DC Converter

CWQ1000 employs an internal step down DC-DC converter in order to reduce its power consumption. The DC-DC converter supplies the power used by internal building blocks. However, the DC-DC converter is not the main power transfer path in CWQ1000.

The DC-DC converter in CWQ1000 will support bypass mode according to the transmitter input voltage VIN. When the VIN voltage is high DC-DC converter will operate to save power consumption, oppositely when the VIN voltage is low it will be bypassed because the power consumption due to the DC-DC operation can be greater. The DC-DC converter in CWQ1000 also will support PWM (Pulse Width Modulation) and PFM (Pulse Frequency Modulation) function according to its load current.

#### 1.3 Power Amp Driver

The power amplifier of CWQ1000 consists of four external power NLDMOSs and internal driver circuits. The power amp driver also includes boosting circuits for driving external high side NLDMOS. Each gate control signal can be adjusted by internal control and MCU.

The power amplifier of CWQ1000 converts input DC power to AC power and transfers it directly to the TX coil. Since power amplifier directly influences the overall transmitter efficiency, the gate control of power MOSFET switches is very important. The power amp driver of CWQ1000 changes its switching frequency and duty cycle according to the load current and feedback from the receiver.

#### 1.4 FSK Modulator

The Qi extended power profile (EPP) uses two-way communication for power transfer. In the Qi standard, TX to RX communication is accomplished by frequency shift keying (FSK) modulation over the power signal frequency.

CWQ1000 power transmitter uses FSK modulation for transmitting protocol data to the power receiver. CWQ1000 changes the period of the power transfer signal by counting the internal 60MHz oscillator. The frequency deviation between the base operating frequency  $f_{OP}$  and the modulation frequency  $f_{MOD}$  is designed according to the Qi EPP standard.

#### 1.5 ASK Demodulator

In the Qi standard, RX to TX communication is accomplished by amplitude shift keying (ASK) modulation with a bit rate of 2Kbps. CWQ1000 power transmitter uses an external peak detection circuit and an internal comparator circuit for ASK demodulation. The external peak detection circuit include diode and filtering capacitors and resistors. The ASK demodulator in CWQ1000 demodulates the WPC standard 2kHz bi-phase signal from the power receiver.

#### 1.6 ADC

CWQ1000 power transmitter employs 12-bit SAR ADC because it has low power, small area characteristics and moderate speed performance. ADC monitors important internal voltages and currents and gives the system information to the digital controller.

#### 1.7 Protection

CWQ1000 power transmitter employs various protection schemes in order to prevent system damage. When the external power amplifier current is too large, the OCL (Over Current Limit) function will limit the output current. When the temperature inside or outside the chip is too high, the OTP (Over Temperature Protection) function will shut down the transmitter system to prevent damage resulting from excessive thermal stress under fault conditions.

#### 1.8 Digital Controller

Digital controller of CWQ1000 is composed of a 32-bit ARM Cortex M0 processor, OTP, SRAM for program and data memory, etc. Digital controller controls all the analog blocks and entire system to perform power transfer operation according to the wireless power transfer Qi standard. CWQ1000 supports the eight GPIO pins and two of them can be dedicated to I2C interface for communication with external host.

## 2. Pin-out and description

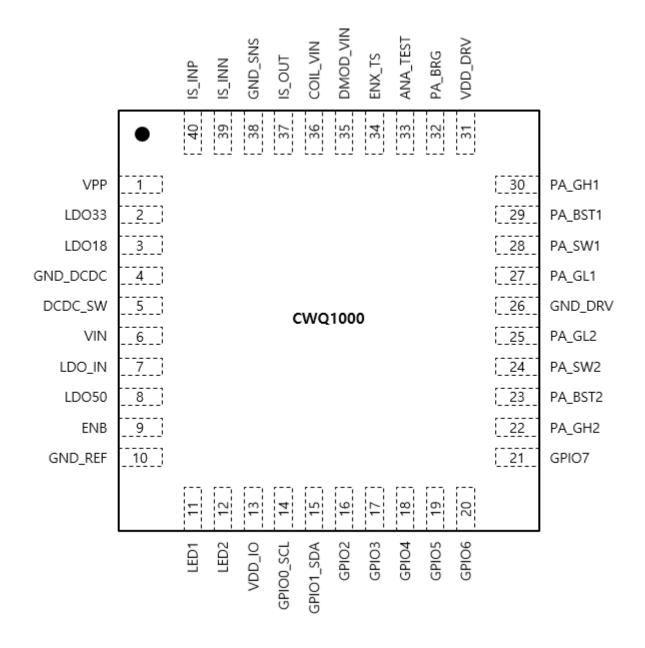

Figure 2. CWQ1000 Pin Configuration (QFN 40-pin 5mm x 5mm, 0.4mm pitch)

### 2.1 Pin Description

| Pin Number | Name                                                                                                  | Туре | Description                                                                                        |

|------------|-------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------|

| 1          | 1 VPP I 8V high voltage power for OTP programming. During the normal op<br>connect this pin to LDO33. |      | 8V high voltage power for OTP programming. During the normal operation, connect this pin to LDO33. |

| 2          | LDO33                                                                                                 | 0    | Internal 3.3V LDO output pin for capacitor connection.                                             |

# CWQ1000

Qi Compliant 15W Wireless Power Transmitter IC

| 3                    | LDO18      | 0   | Internal 1.8V LDO output pin for capacitor connection.                                                                         |  |

|----------------------|------------|-----|--------------------------------------------------------------------------------------------------------------------------------|--|

| 4                    | GND_DCDC   |     | Ground for DCDC block.                                                                                                         |  |

| 5                    | DCDC_SW    | 0   | Switching node of DCDC converter. Connect this pin to the external inductor for DCDC converter.                                |  |

| 6                    | VIN        | I   | DC power input for power transmission.                                                                                         |  |

| 7                    | LDO_IN     | I   | DCDC converter output and input power supply for internal LDOs.                                                                |  |

| 8                    | LDO50      | 0   | Internal 5V LDO output pin for capacitor connection.                                                                           |  |

| 9                    | ENB        | I   | Active-low enable pin for the entire chip.                                                                                     |  |

| 10                   | GND_REF    |     | Ground for internal reference block.                                                                                           |  |

| 11                   | LED1       | 0   | Open drain output for LED connection                                                                                           |  |

| 12                   | LED2       | 0   | Open drain output for LED connection                                                                                           |  |

| 13                   | VDD_IO     | I   | Input power supply for GPIO0-7. The operating range of this pin is 1.8-5.0V.                                                   |  |

| 14                   | GPIO0_SCL  | 1/0 | General purpose input/output 0. This pin can be dedicated for I <sup>2</sup> C clock input for internal register access.       |  |

| 15                   | GPIO1_SDA  | 1/0 | General purpose input/output 1. This pin can be dedicated for I <sup>2</sup> C data input/output for internal register access. |  |

| 16,17,18<br>19,20,21 | GPIO [2:7] | 1/0 | General purpose input/output [2:7].                                                                                            |  |

| 22                   | PA_GH2     | 0   | PA gate driver output for the high side FET of half bridge 2.                                                                  |  |

| 23                   | PA_BST2    | I   | PA bootstrap capacitor connection pin for driving the high-side FET of half bridge 2.                                          |  |

| 24                   | PA_SW2     | I   | PA switching node for half bridge 2.                                                                                           |  |

| 25                   | PA_GL2     | 0   | PA gate driver output for the low side FET of half bridge 2.                                                                   |  |

| 26                   | GND_DRV    |     | Ground for PA driver.                                                                                                          |  |

| 27                   | PA_GL1     | 0   | PA gate driver output for the low side FET of half bridge 1.                                                                   |  |

| 28                   | PA_SW1     | I   | PA switching node for half bridge 1.                                                                                           |  |

| 29                   | PA_BST1    | I   | PA bootstrap capacitor connection pin for driving the high-side FET of half bridge 1.                                          |  |

| 30                   | PA_GH1     | 0   | PA gate driver output for the high side FET of half bridge 1.                                                                  |  |

| 31                   | VDD_DRV    | I   | Input power supply for the PA drivers.                                                                                         |  |

| 32                   | PA_BRG     | I   | PA bridge voltage sensing pin.                                                                                                 |  |

| 33                   | ANA_TEST   | 0   | Analog test output pin.                                                                                                        |  |

| 34                   | EXT_TS     | I   | External temperature sensor input. Connect this pin to external NTC thermistor. If not used, connect this pin to LDO33.        |  |

| 35                   | DMOD_VIN   | I   | Voltage sensing input pin for ASK demodulation.                                                                                |  |

| 36                   | COIL_VIN   | I   | Q factor Measurement                                                                                                           |  |

| 37                   | IS_OUT     | 0   | Input current sensor output.                                                                                                   |  |

| 38                   | GND_SNS    |     | Ground for internal sensors.                                                                                                   |  |

# CWQ1000

Qi Compliant 15W Wireless Power Transmitter IC

| 39 | IS_INN | I | Input current sensor negative input. |

|----|--------|---|--------------------------------------|

| 40 | IS_INP | I | Input current sensor positive input. |

## 3. Application Guide

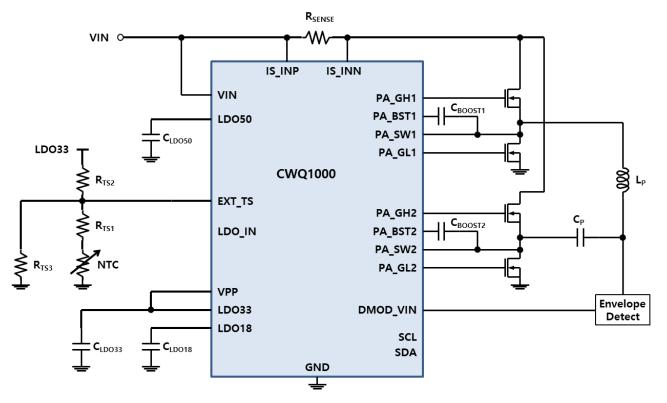

Figure 3. CWQ1000 Typical Application Diagram

### 3.1 Transmitter Coil and Resonant Capacitors

The transmitter coil design is related to the overall system application. The coil inductance, shape and material can be chosen according to its applications. However, it must comply with the WPC recommendations which include the self-inductance value, DC resistance, Q factor, etc. The resonant circuits of the power transmitter consist of an inductance  $L_P$ , a capacitance  $C_P$ , and a resistance  $R_P$ , where the  $R_P$  is the parasitic resistance. With respect to TX coil and capacitor, the resonant frequency  $f_P$  and the quality factor  $Q_P$  can be calculated by the following equations.

$$f_{\rm P} = \frac{1}{2\pi\sqrt{L_{\rm P}C_{\rm P}}}$$

$$Q_{\rm P} = \frac{2\pi f_{\rm P}L_{\rm P}}{R_{\rm P}}$$

The resonant frequency  $f_P$  and the quality factor  $Q_P$  must be in the range of WPC recommendation.

#### 3.2 Power MOSFETs and Boost Capacitors

As shown in Figure 3, CWQ1000 power transmitter uses four external power MOSFETs for the power amplifier configuration. Since the input voltage range of CWQ1000 is 0 to 21V, the external power MOSFETs

should be high voltage devices. CWQ1000 power transmitter uses two high side N-channel MOSFETs to

improve efficiency and uses boosting circuits to drive them. The recommended power MOSFETs are 30V N-channel LDMOS.

As explained, two external bootstrap capacitors  $C_{BOOST1}$  and  $C_{BOOST2}$  are needed to drive the high-side FETs of external power amplifier. Bootstrap capacitors should have voltage rating of more than 25V and their recommended capacitances are 0.1uF.

#### 3.3 Output Regulating Capacitors

As shown in Figure 3, DCDC converter output LDO\_IN and internal LDOs' output LDO50, LDO33, LDO18 should be connected to external capacitor for voltage regulation. Typical recommended capacitance values are  $C_{LDO_IN}$ =10uF,  $C_{LDO50}$ =1uF,  $C_{LDO18}$ =1uF, respectively.

#### 3.4 Inductor for DCDC Converter

The CWQ1000 power transmitter uses DCDC converter to reduce power consumption and it needs an external power inductor. The DCDC output voltage is used as the power supply of the internal circuits and LDOs, so the voltage ripple must be small. It is recommended to use a power inductor greater than 4.7uH to reduce voltage ripple.

#### 3.5 Input Current Sensing Resistor

The CWQ1000 power transmitter uses an external resistor for the PA input current path to sense the input current. The sensing resistor tolerance should be less than 1% to meet the WPC FOD specification. Also, the current capacity of the resistor must be large because its maximum current reaches up to 2A.

#### 3.6 External Temperature Sensor

When the temperature inside or outside the chip is too high, the OTP (Over Temperature Protection) function will send the EPT packet to transmitter or shutdown the receiver system. In order to sense the temperature outside chip, connect EXT\_TS pin to external NTC (Negative temperature Coefficient) thermistor as shown in Figure 3. The NTC thermistor should be placed close to the heat emission device. The EXT\_TS voltage  $V_{EXT}$  can be calculated as follows,

$$V_{EXT_{TS}} = V_{LDO33} \times \frac{\frac{(R_{NTC} + R_{TS1}) \times R_{TS3}}{(R_{NTC} + R_{TS1}) + R_{TS3}}}{\frac{(R_{NTC} + R_{TS1}) \times R_{TS3}}{(R_{NTC} + R_{TS1}) + R_{TS3}} + R_{TS2}}$$

In this equation,  $V_{LDO33}$  is 3.3V from the internal LDO.

CWQ1000 compares  $V_{EXT_TS}$  with internal reference voltages  $V_{TS_HOT}$  and  $V_{TS_COLD}$ . If  $V_{EXT_TS} < V_{TS_HOT}$ , it means external temperature is too high and CWQ1000 sends the EPT packet to transmitter. On the other hand, if  $V_{EXT_TS} > V_{TS_COLD}$ , it means external temperature is too low and CWQ1000 also sends the EPT packet to transmitter. Remind that  $V_{EXT_TS}$  is negative slope curve vs temperature.

The reference voltages  $V_{TS\_HOT}$  and  $V_{TS\_COLD}$  are programmable values by firmware. For example,  $V_{TS\_HOT}$  and  $V_{TS\_COLD}$  are programmed as follows,

| Internal TS Reference | Threshold Voltage [V] | Hysteresis [mV] |

|-----------------------|-----------------------|-----------------|

| V <sub>TS_HOT</sub>   | 0.315                 | 20              |

| V <sub>TS_COLD</sub>  | 0.980                 | 80              |

| Temp<br>[℃] | V <sub>LDO33</sub><br>[V] | R <sub>NTC</sub><br>[kΩ] | R <sub>TS1</sub><br>[kΩ] | R <sub>TS2</sub><br>[kΩ] | R <sub>TS3</sub><br>[kΩ] | V <sub>EXT_TS</sub><br>[V] | Status                                                           |

|-------------|---------------------------|--------------------------|--------------------------|--------------------------|--------------------------|----------------------------|------------------------------------------------------------------|

| -40         | 3.3                       | 188.5                    | 3.9                      | 47                       | 68                       | 1.550                      |                                                                  |

| -30         | 3.3                       | 111.3                    | 3.9                      | 47                       | 68                       | 1.429                      | V <sub>EXT_TS</sub> > V <sub>TS_COLD</sub>                       |

| -20         | 3.3                       | 67.8                     | 3.9                      | 47                       | 68                       | 1.278                      | Send EPT packet                                                  |

| -10         | 3.3                       | 42.5                     | 3.9                      | 47                       | 68                       | 1.109                      |                                                                  |

| 0           | 3.3                       | 27.3                     | 3.9                      | 47                       | 68                       | 0.938                      |                                                                  |

| 10          | 3.3                       | 18.0                     | 3.9                      | 47                       | 68                       | 0.782                      |                                                                  |

| 20          | 3.3                       | 12.1                     | 3.9                      | 47                       | 68                       | 0.648                      |                                                                  |

| 30          | 3.3                       | 8.31                     | 3.9                      | 47                       | 68                       | 0.541                      | V <sub>TS_HOT</sub> < V <sub>EXT_TS</sub> < V <sub>TS_COLD</sub> |

| 40          | 3.3                       | 5.83                     | 3.9                      | 47                       | 68                       | 0.460                      | Normal charging operation                                        |

| 50          | 3.3                       | 4.16                     | 3.9                      | 47                       | 68                       | 0.399                      |                                                                  |

| 60          | 3.3                       | 3.02                     | 3.9                      | 47                       | 68                       | 0.354                      |                                                                  |

| 70          | 3.3                       | 2.23                     | 3.9                      | 47                       | 68                       | 0.321                      |                                                                  |

| 80          | 3.3                       | 1.67                     | 3.9                      | 47                       | 68                       | 0.296                      |                                                                  |

| 90          | 3.3                       | 1.27                     | 3.9                      | 47                       | 68                       | 0.278                      |                                                                  |

| 100         | 3.3                       | 0.98                     | 3.9                      | 47                       | 68                       | 0.265                      | V <sub>EXT_TS</sub> < V <sub>TS_HOT</sub><br>Send EPT packet     |

| 110         | 3.3                       | 0.76                     | 3.9                      | 47                       | 68                       | 0.255                      |                                                                  |

| 120         | 3.3                       | 0.60                     | 3.9                      | 47                       | 68                       | 0.247                      |                                                                  |

Recommended NTC resistance range is from hundreds of  $\Omega$  to hundreds of  $k\Omega$  vs temperature. After choosing the appropriate NTC thermistor, you can design R<sub>TS1</sub>, R<sub>TS2</sub> and R<sub>TS3</sub> according to your thermal protection specification. Table 1 shows an EXT\_TS thermal protection design example.

#### Table 1. EXT\_TS Thermal Protection Design Example

In this example, the hot temperature threshold  $T_{TS\_HOT}$  and the cold temperature threshold  $T_{TS\_COLD}$  are designed to be 80°C and -10°C respectively. You can change the hot and cold temperature threshold according to your application by changing the related resistors.

#### 3.7 PCB Layout Guide

- Keep the trace resistance as low as possible on large current nets associated with the external power MOSFETs.

- Resonant capacitor C<sub>P</sub> needs to be as close to the device as possible.

- Boost capacitors (C<sub>BOOST1</sub>, C<sub>BOOST2</sub>) need to be as close to the device as possible.

- Output regulating capacitors C<sub>LDO\_IN</sub>, C<sub>LDO50</sub>, C<sub>LDO33</sub> and C<sub>LDO18</sub> need to be as close to the device as possible.

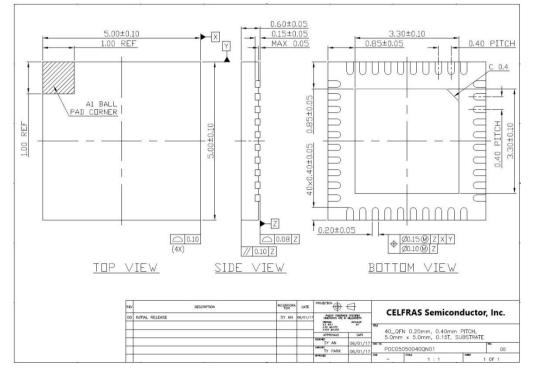

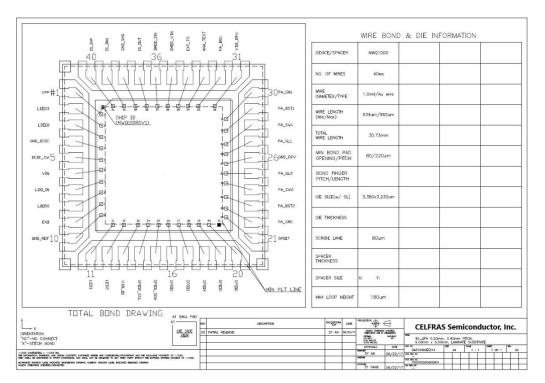

# 4. Package Outline

Figure 4. QFN 40-pin Package Outline, 5.0mm x 5.0mm, 0.4mm pitch

Figure 5. QFN 40-pin Bonding Diagram

# 5. Electrical Characteristics

### 5.1 Absolute Maximum Rating

| PIN                                                                                                                                                                                     | Parameter | Rating      | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|------|

| DCDC_SW, VIN, ENB, PA_GH2, PA_BST2<br>PS_SW2, PA_SW1, PA_BST1, PA_GH1, PA_BRG<br>IS_INP, IS_INN                                                                                         | Voltage   | -0.3 to 26  | v    |

| VPP                                                                                                                                                                                     | Voltage   | -0.3 to 8   | V    |

| LDO33, LDO_IN, LDO50, LED1, LED2<br>VDD_IO, GPIO0_SCL, GPIO1_SDA, GPIO2, GPIO3<br>GPIO4, GPIO5, GPIO6, GPIO7, PA_GL2<br>PA_GL1, VDD_DRV, ANA_TEST, EXT_TS, DMOD_VIN<br>DMOD_IIN, IS_OUT | Voltage   | -0.3 to 6   | v    |

| LDO18                                                                                                                                                                                   | Voltage   | -0.3 to 2   | V    |

| GND_DCDC, GND_REF, GND_SNS, GND_DRV                                                                                                                                                     | Voltage   | -0.3 to 0.3 | V    |

### 5.2 Recommended Operating Condition

| Symbol          | Description                            |     | Тур. | Max. | Unit |

|-----------------|----------------------------------------|-----|------|------|------|

| V <sub>IN</sub> | DC power input for power transmission. | 4.5 |      | 20   | V    |

| TJ              | Junction temperature                   | -30 |      | 125  | °C   |

| T <sub>A</sub>  | Ambient temperature                    | -30 |      | 85   | °C   |

### 5.3 Device Characteristics

| Symbol                | Description                                    | Conditions               | Min. | Тур. | Max. | Unit |  |  |

|-----------------------|------------------------------------------------|--------------------------|------|------|------|------|--|--|

| Input Supply a        | Input Supply and Current Consumption           |                          |      |      |      |      |  |  |

| V <sub>IN</sub>       | Input supply voltage range                     |                          | 4.5  | 12   | 20   | V    |  |  |

| V <sub>UVLO</sub>     | Under voltage lockout                          | $V_{IN}$ : 0V to 5V      |      | 4.0  | 4.2  | V    |  |  |

| $V_{UVLO_HYS}$        | Under voltage lockout hysteresis               | $V_{IN}$ : 5V to 0V      |      | 500  |      | mV   |  |  |

| I <sub>IN</sub>       | Input current at power transfer mode           | V <sub>IN</sub> =12V     |      | 10   |      | mA   |  |  |

| I <sub>STD_BY</sub>   | Input current at stand-by mode (periodic ping) | V <sub>IN</sub> =12V     |      | 1    |      | mA   |  |  |

| I <sub>PDN</sub>      | Input current at power down mode               | ENB=V <sub>IN</sub> =12V |      | 25   |      | uA   |  |  |

| Step-down DCI         | DC Converter                                   |                          |      |      |      |      |  |  |

| V <sub>OUT_DCDC</sub> | DCDC converter output voltage                  | V <sub>IN</sub> =12V     | 4.5  | 5.5  | 5.5  | V    |  |  |

| IOUT_DCDC             | DCDC converter output current                  |                          |      | 10   |      | mA   |  |  |

| E <sub>ff_DCDC</sub>  | DCDC power conversion efficiency               |                          |      | 90   |      | %    |  |  |

| Power Amplifi         | Power Amplifier and Driver                     |                          |      |      |      |      |  |  |

# CWQ1000

Qi Compliant 15W Wireless Power Transmitter IC

| f <sub>PA</sub>            | Power amplifier switching frequency                              |                                       | 85 |       | 205 | kHz  |

|----------------------------|------------------------------------------------------------------|---------------------------------------|----|-------|-----|------|

| T <sub>LS_SW</sub>         | Low side gate driver rising and falling times                    |                                       | 00 | 50    | 200 | ns   |

| T <sub>HS_SW</sub>         | High side gate driver rising and falling times                   |                                       |    | 150   |     | ns   |

| P <sub>OUT_PA_MAX</sub>    | Power amplifier maximum output power                             |                                       |    | 15    |     | W    |

| Internal LDOs              |                                                                  |                                       |    | 10    |     |      |

| V <sub>OUT_LD050</sub>     | Internal LDO50 output voltage range                              | V <sub>IN</sub> >5V                   |    | 5     |     | V    |

| IOUT_LDO50_MAX             | LDO50 maximum output current                                     |                                       |    |       | 20  | mA   |

| V <sub>OUT_LDO33</sub>     | Internal LDO33 output voltage range                              | V <sub>IN</sub> >5V                   |    | 3.3   |     | V    |

| I <sub>OUT_LDO33_MAX</sub> | LDO33 maximum output current                                     |                                       |    |       | 20  | mA   |

| V <sub>OUT_LDO18</sub>     | Internal LDO18 output voltage range                              | V <sub>IN</sub> >5V                   |    | 1.8   |     | V    |

| I <sub>OUT_LDO18_MAX</sub> | LDO18 maximum output current                                     |                                       |    |       | 10  | mA   |

| BGR                        |                                                                  |                                       |    |       |     |      |

| V <sub>BGR</sub>           | Internal BGR output voltage<br>Register programmable             | V <sub>IN</sub> >3.3V                 |    | 1.22  |     | v    |

| Oscillator                 |                                                                  |                                       |    |       |     |      |

| f <sub>OSC50K</sub>        | Internal low speed oscillator frequency<br>Register programmable | V <sub>IN</sub> >3.3V                 |    | 50    |     | kH:  |

| f <sub>OSC60M</sub>        | Internal main oscillator frequency<br>Register programmable      | V <sub>IN</sub> >3.3V                 |    | 60    |     | MH   |

| ADC                        |                                                                  | · · · · ·                             |    |       |     |      |

| N <sub>ADC</sub>           | ADC resolution                                                   | V <sub>IN</sub> >3.3V                 |    | 12    |     | bit  |

| <b>f</b> <sub>SAMPLE</sub> | ADC sampling rate                                                | f <sub>OSC60M</sub> =60MHz            |    | 217   |     | kSa, |

| $N_{CH\_ADC}$              | ADC channel                                                      |                                       |    | 6     |     |      |

| Protection                 |                                                                  |                                       |    |       |     |      |

| I <sub>OCL</sub>           | $I_{\ensuremath{IN}}$ over current limit protection              | R <sub>SENSE</sub> =20mΩ              |    | 2     |     | А    |

| T <sub>OTP</sub>           | Over temperature protection<br>Thermal shutdown temperature      | Temperature:<br>30℃ to 160℃           |    | 150   |     | °C   |

| T <sub>OTP_HYS</sub>       | OTP hysteresis                                                   | Temperature:<br>160℃ to 30℃           |    | 20    |     | °C   |

| V <sub>TS_HOT</sub>        | EXT_TS hot temperature protection threshold voltage              | V <sub>EXT_TS</sub> : 0V to 0.5V      |    | 0.315 |     | v    |

| V <sub>TS_HOT_HYS</sub>    | V <sub>TS_HOT</sub> hysteresis                                   | $V_{EXT_TS}$ : 0.5V to 0V             |    | 20    |     | m∖   |

| V <sub>TS_COLD</sub>       | EXT_TS cold temperature protection threshold voltage             | V <sub>EXT_TS</sub> : 0.5V to<br>1.5V |    | 0.980 |     | v    |

| VTS_COLD_HYS               | V <sub>TS_COLD</sub> hysteresis                                  | V <sub>EXT_TS</sub> : 1.5V to<br>0.5V |    | 80    |     | m\   |

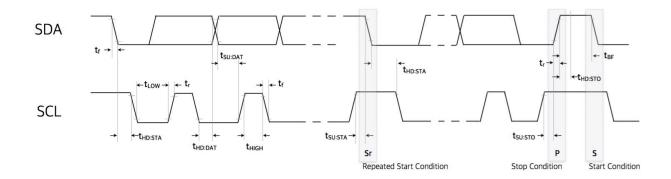

# 6. I<sup>2</sup>C Signal Timing

Figure 6. Timing Diagram for I<sup>2</sup>C interface

| Symbol              | Description                                    | Conditions                       | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------------------|----------------------------------|------|------|------|------|

| V <sub>IL_SDA</sub> | Input low threshold level SDA                  | V <sub>PULLUP</sub> =VDD_IO=3.3V |      |      | 0.7  | V    |

| $V_{IH\_SDA}$       | Input high threshold level SDA                 | V <sub>PULLUP</sub> =VDD_IO=3.3V | 2.6  |      |      | V    |

| V <sub>IL_SCL</sub> | Input low threshold level SCL                  | V <sub>PULLUP</sub> =VDD_IO=3.3V |      |      | 0.7  | V    |

| V <sub>IH_SCL</sub> | Input high threshold level SCL                 | V <sub>PULLUP</sub> =VDD_IO=3.3V | 2.6  |      |      | V    |

| f <sub>SCL</sub>    | SCL clock frequency                            |                                  |      |      | 400  | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                             |                                  | 1.3  |      |      | us   |

| t <sub>HIGH</sub>   | SCL clock high time                            |                                  | 0.6  |      |      | us   |

| t <sub>r</sub>      | Rise time of both SDA and SCL                  |                                  |      |      | 0.3  | us   |

| t <sub>f</sub>      | Fall time of both SDA and SCL                  |                                  |      |      | 0.3  | us   |

| t <sub>su,sta</sub> | Setup time for START condition                 |                                  | 0.6  |      |      | us   |

| t <sub>hd,sta</sub> | Hold time for START condition                  |                                  | 0.6  |      |      | us   |

| t <sub>su,dat</sub> | Data setup time                                |                                  | 0.1  |      |      | us   |

| t <sub>hd,dat</sub> | Data hold time                                 |                                  |      |      | 0.9  | us   |

| t <sub>su,sto</sub> | Setup time for STOP condition                  |                                  | 0.6  |      |      | us   |

| t <sub>BF</sub>     | Bus free time between STOP and START condition |                                  | 1.3  |      |      | us   |

Table 2. I<sup>2</sup>C Characteristics

# **Revision History**

| Date       | Version No. | Description                                 |

|------------|-------------|---------------------------------------------|

| 2017/07/27 | 1.0         | Preliminary Release                         |

| 2017/08/03 | 1.1         | Updated and Modify again                    |

| 2018/01/29 | 1.2         | Chinese edition release and typo correction |

| 2018/05/04 | 1.3         | Modify Sales Contact point                  |

| 2018/07/26 | 1.4         | Modify pin definition                       |

|            |             |                                             |

### **Contact US**

### > Headquarters

#### CELFRAS Semiconductor Inc. 江西联智集成电路有限公司

59 Chuangxin No.1 Road, Nanchang Hi-tech Development Zone, Nanchang, Jiangxi, P.R.CHINA, Zip:330000

### > International

#### **CELFRAS Design Center Inc.**

7F, 225-14, Pangyoyeok-ro, Bundang-gu, Seongnam-si, Gyeonggi-do, 13494, Korea Tel. +82-70-4055-6466 Fax +82-31-707-8825

### Contact

#### Website

Technical Support <u>cts@celfras.com</u>, <u>june\_yoo@celfras.com</u> Sales Contact marketing@celfras.com

Copyright © 2017 CELFRAS., Inc. All rights reserved. CELFRAS., Inc.