**DAC088S085**

SNAS424D -AUGUST 2007-REVISED APRIL 2016

# DAC088S085 8-Bit Micro Power OCTAL Digital-to-Analog Converter With Rail-to-Rail **Outputs**

### **Features**

- **Ensured Monotonicity**

- Low Power Operation

- Rail-to-Rail Voltage Output

- Daisy Chain Capability

- Power-On Reset to 0 V

- Simultaneous Output Updating

- Individual Channel Power Down Capability

- Wide Power Supply Range (2.7 V to 5.5 V)

- Dual Reference Voltages With Range of 0.5 V to

- Operating Temperature Range of -40°C to 125°C

- Industry's Smallest Package

- **Key Specifications**

- Resolution: 8 Bits

- INL: ±0.5 LSB (Maximum)

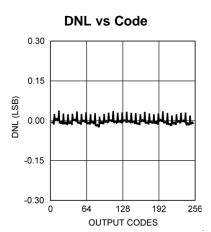

- DNL: 0.15 / -0.1 LSB (Maximum)

- Settling Time: 4.5 µs (Maximum)

- Zero Code Error: 15 mV (Maximum)

- Full-Scale Error: -0.75 %FSR (Maximum)

- Supply Power:

- Normal: 1.95 mW (3 V) / 4.85 mW (5 V)

- Power Down: 0.3 μW (3 V) / 1 μW (5 V) **Typical**

# 2 Applications

- **Battery-Powered Instruments**

- Digital Gain and Offset Adjustment

- Programmable Voltage and Current Sources

- **Programmable Attenuators**

- Voltage Reference for ADCs

- Sensor Supply Voltage

- Range Detectors

## 3 Description

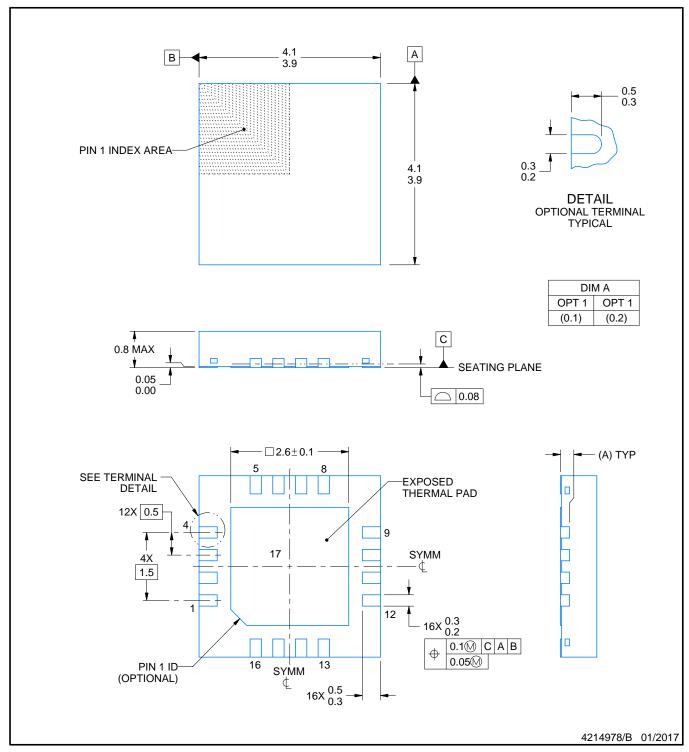

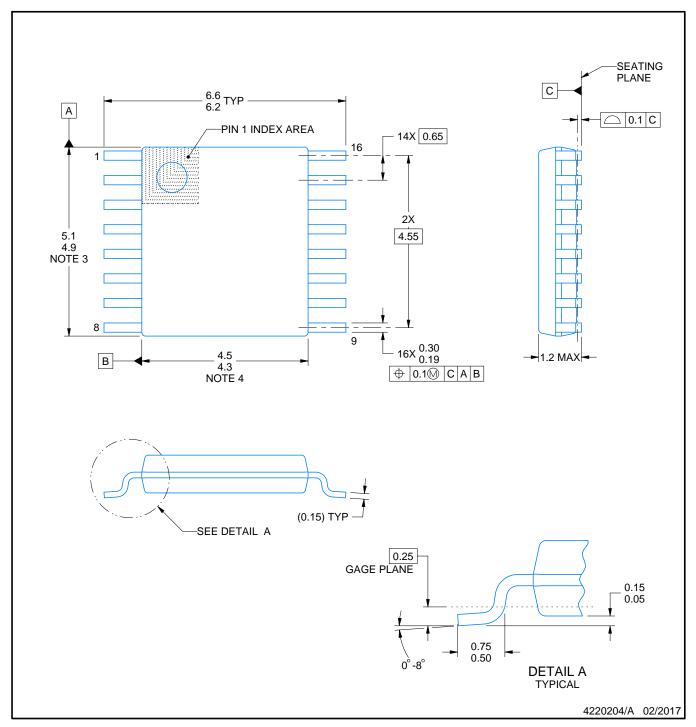

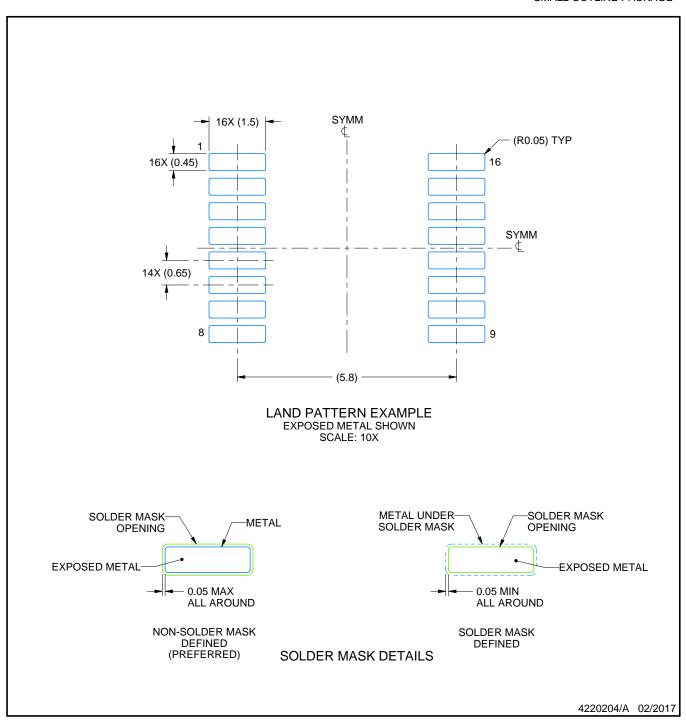

The DAC088S085 is a full-featured, general-purpose, OCTAL. 8-bit. voltage-output, digital-to-analog converter (DAC) that can operate from a single 2.7 V to 5.5 V supply and consumes 1.95 mW at 3 V and 4.85 mW at 5 V. The DAC088S085 is packaged in a 16-pin WQFN package and a 16-pin TSSOP The WQFN package makes DAC088S085 the smallest OCTAL DAC in its class. The on-chip output amplifiers allow rail-to-rail output swing and the three-wire serial interface operates at clock rates up to 40 MHz over the entire supply voltage range. Competitive devices are limited to 25-MHz clock rates at supply voltages in the range of 2.7 V to 3.6 V. The serial interface is compatible with standard SPI™, QSPI, MICROWIRE, and DSP interfaces. The DAC088S085 also offers daisy chain operation where an unlimited number of devices can be updated simultaneously using a single serial interface.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| DACORRORE   | TSSOP (16) | 5.00 mm × 4.40 mm |

| DAC088S085  | WQFN (16)  | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## **Table of Contents**

| 1 | Features 1                           |    | 8.4 Device Functional Modes                      | 16              |

|---|--------------------------------------|----|--------------------------------------------------|-----------------|

| 2 | Applications 1                       |    | 8.5 Programming                                  | 17              |

| 3 | Description 1                        | 9  | Application and Implementation                   | 20              |

| 4 | Revision History2                    |    | 9.1 Application Information                      | 20              |

| 5 | Description (continued)3             |    | 9.2 Typical Applications                         | 25              |

| 6 | Pin Configuration and Functions3     |    | 9.3 Do's and Don'ts                              | 27              |

| 7 | Specifications5                      | 10 | Power Supply Recommendations                     | 27              |

| ′ | 7.1 Absolute Maximum Ratings         |    | 10.1 Using References as Power Supplies          | <mark>27</mark> |

|   | 7.1 Absolute Maximum Ratings         | 11 | Layout                                           | 29              |

|   | 7.3 Recommended Operating Conditions |    | 11.1 Layout Guidelines                           | 29              |

|   | 7.4 Thermal Information              |    | 11.2 Layout Example                              | 30              |

|   | 7.5 Electrical Characteristics 6     | 12 | Device and Documentation Support                 | 31              |

|   | 7.6 AC and Timing Requirements8      |    | 12.1 Device Support                              |                 |

|   | 7.7 Typical Characteristics          |    | 12.2 Community Resources                         |                 |

| 8 | Detailed Description14               |    | 12.3 Trademarks                                  |                 |

| O | 8.1 Overview                         |    | 12.4 Electrostatic Discharge Caution             | 32              |

|   | 8.2 Functional Block Diagram         |    | 12.5 Glossary                                    |                 |

|   | 8.3 Feature Description              | 13 | Mechanical, Packaging, and Orderable Information | 32              |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

## Changes from Revision C (March 2013) to Revision D

**Page**

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and

## Changes from Revision B (March 2013) to Revision C

**Page**

## 5 Description (continued)

There are two references for the DAC088S085. One reference input serves channels A through D, while the other reference serves channels E through H. Each reference can be set independently between 0.5 V and V<sub>A</sub>, providing the widest possible output dynamic range. The DAC088S085 has a 16-bit input shift register that controls the mode of operation, the power-down condition, and the DAC channels' register and output value. All eight DAC outputs can be updated simultaneously or individually.

A power-on reset circuit ensures that the DAC outputs power up to 0 V and remain there until there is a valid write to the device. The power-down feature of the DAC088S085 allows each DAC to be independently powered with three different termination options. With all the DAC channels powered down, power consumption reduces to less than 0.3 µW at 3 V and less than 1 µW at 5 V. The low power consumption and small packages of the DAC088S085 make it an excellent choice for use in battery-operated equipment.

The DAC088S085 is one of a family of pin-compatible DACs, including the 10-bit DAC108S085 and the 12-bit DAC128S085. All three parts are offered with the same pinout, allowing system designers to select a resolution appropriate for their application without redesigning their printed-circuit board. The DAC088S085 operates over the extended industrial temperature range of -40°C to 125°C.

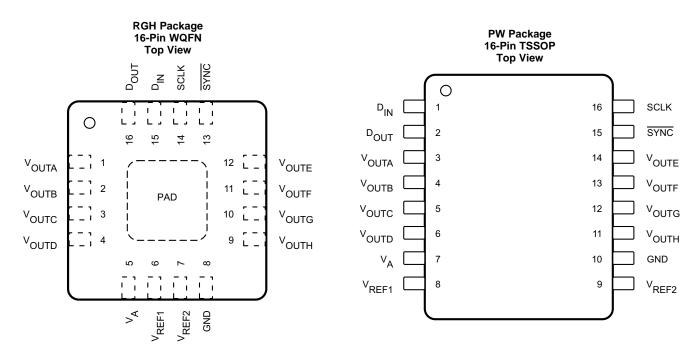

## **Pin Configuration and Functions**

Copyright © 2007-2016, Texas Instruments Incorporated

## **Pin Functions**

| PIN                |          |       |                |                                                                                                                                                                                                                                                                                                                                                                                          |  |

|--------------------|----------|-------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NIA BAT            | NAME NO. |       | TYPE           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                              |  |

| NAIVIE             | WQFN     | TSSOP |                |                                                                                                                                                                                                                                                                                                                                                                                          |  |

| D <sub>IN</sub>    | 15       | 1     | Digital Input  | Serial Data Input. Data is clocked into the 16-bit shift register on the falling edges of SCLK after the fall of SYNC.                                                                                                                                                                                                                                                                   |  |

| D <sub>OUT</sub>   | 16       | 2     | Digital Output | Serial Data Output. D <sub>OUT</sub> is used in daisy chain operation and is connected directly to a D <sub>IN</sub> pin on another DAC088S085. Data is not available at D <sub>OUT</sub> unless SYNC remains low for more than 16 SCLK cycles.                                                                                                                                          |  |

| GND                | 8        | 10    | Ground         | Ground reference for all on-chip circuitry.                                                                                                                                                                                                                                                                                                                                              |  |

| SCLK               | 14       | 16    | Digital Input  | Serial Clock Input. Data is clocked into the input shift register on the falling edges of this pin.                                                                                                                                                                                                                                                                                      |  |

| SYNC               | 13       | 15    | Digital Input  | Frame Synchronization Input. When this pin goes low, data is written into the DAC's input shift register on the falling edges of SCLK. After the 16th falling edge of SCLK, a rising edge of SYNC causes the DAC to be updated. If SYNC is brought high before the 15th falling edge of SCLK, the rising edge of SYNC acts as an interrupt and the write sequence is ignored by the DAC. |  |

| $V_A$              | 5        | 7     | Supply         | Power supply input. Must be decoupled to GND.                                                                                                                                                                                                                                                                                                                                            |  |

| $V_{OUTA}$         | 1        | 3     | Analog Output  | Channel A Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                                         |  |

| $V_{\text{OUTB}}$  | 2        | 4     | Analog Output  | Channel B Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                                         |  |

| $V_{\text{OUTC}}$  | 3        | 5     | Analog Output  | Channel C Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                                         |  |

| $V_{OUTD}$         | 4        | 6     | Analog Output  | Channel D Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                                         |  |

| $V_{\text{OUTE}}$  | 12       | 14    | Analog Output  | Channel E Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                                         |  |

| $V_{\text{OUTF}}$  | 11       | 13    | Analog Output  | Channel F Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                                         |  |

| $V_{\text{OUTG}}$  | 10       | 12    | Analog Output  | Channel G Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                                         |  |

| $V_{\text{OUTH}}$  | 9        | 11    | Analog Output  | Channel H Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                                         |  |

| V <sub>REF1</sub>  | 6        | 8     | Analog Input   | Unbuffered reference voltage shared by Channels A, B, C, and D. Must be decoupled to GND.                                                                                                                                                                                                                                                                                                |  |

| V <sub>REF2</sub>  | 7        | 9     | Analog Input   | Unbuffered reference voltage shared by Channels E, F, G, and H. Must be decoupled to GND.                                                                                                                                                                                                                                                                                                |  |

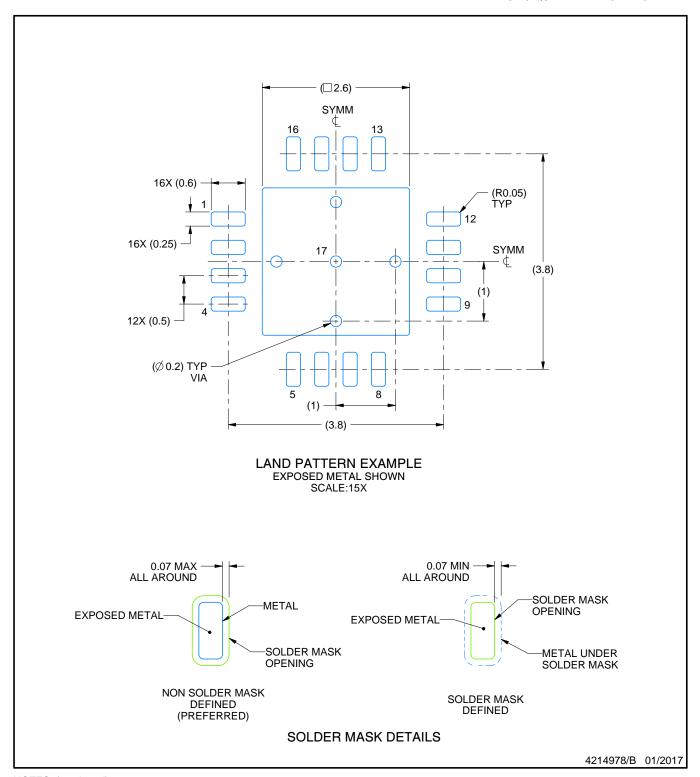

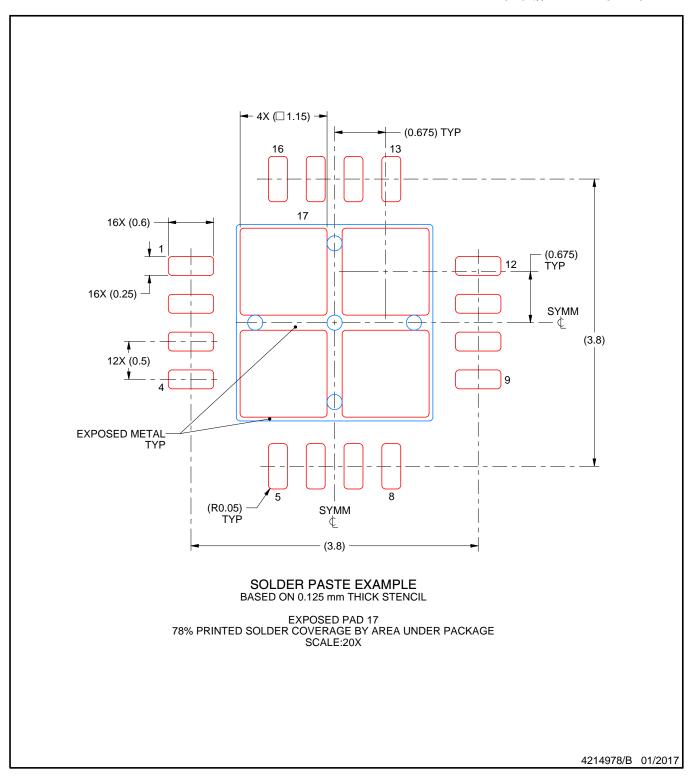

| PAD <sup>(1)</sup> | _        | _     | Ground         | Exposed die attach pad can be connected to ground or left floating. Soldering the pad to the PCB offers optimal thermal performance and enhances package self-alignment during reflow.                                                                                                                                                                                                   |  |

(1) WQFN only

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2) (3)

|                                            | MIN  | MAX | UNIT |

|--------------------------------------------|------|-----|------|

| Supply voltage, V <sub>A</sub>             |      | 6.5 | V    |

| Voltage on any input pin                   | -0.3 | 6.5 | V    |

| Input current at any pin <sup>(4)</sup>    |      | 10  | mA   |

| Package input current <sup>(4)</sup>       |      | 30  | mA   |

| Power Consumption at T <sub>A</sub> = 25°C | See  | (5) |      |

| Junction temperature, T <sub>J</sub>       |      | 150 | °C   |

| Storage temperature, T <sub>stg</sub>      | -65  | 150 | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2) All voltages are measured with respect to GND = 0 V, unless otherwise specified.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (4) When the input voltage at any pin exceeds 5.5 V or is less than GND, the current at that pin must be limited to 10 mA. The 30-mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 10 mA to three.

- (5) The absolute maximum junction temperature (T<sub>J</sub>max) for this device is 150°C. The maximum allowable power dissipation is dictated by T<sub>J</sub>max, the junction-to-ambient thermal resistance (R<sub>θJA</sub>), and the ambient temperature (T<sub>A</sub>), and can be calculated using the formula P<sub>D</sub>MAX = (T<sub>J</sub>max T<sub>A</sub>) / R<sub>θJA</sub>. The values for maximum power dissipation is reached only when the device is operated in a severe fault condition (for example, when input or output pins are driven beyond the operating ratings, or the power supply polarity is reversed). Such conditions must always be avoided.

## 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

|                    |                         | Machine model (MM)                                                  | ±250  |      |

- (1) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

| 1 0 1 0 1                              |     |         |      |

|----------------------------------------|-----|---------|------|

|                                        | MIN | MAX     | UNIT |

| Operating temperature, T <sub>A</sub>  | -40 | 125     | °C   |

| Supply voltage, V <sub>A</sub>         | 2.7 | 5.5     | V    |

| Reference voltage, V <sub>REF1,2</sub> | 0.5 | $V_{A}$ | V    |

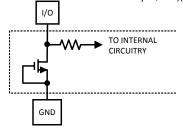

| Digital input voltage (2)              | 0   | 5.5     | V    |

| Output load                            | 0   | 1500    | pF   |

| SCLK frequency                         |     | 40      | MHz  |

Product Folder Links: DAC088S085

(1) All voltages are measured with respect to GND = 0 V, unless otherwise specified.

2) The inputs are protected as shown below. Input voltage magnitudes up to 5.5 V, regardless of V<sub>A</sub>, does not cause errors in the conve<u>rsion</u> result. For example, if V<sub>A</sub> is 3 V, the digital input pins can be driven with a 5 V logic device.

### 7.4 Thermal Information

|                      |                                              | DAC088S085 |            |      |  |  |

|----------------------|----------------------------------------------|------------|------------|------|--|--|

|                      | THERMAL METRIC <sup>(1)(2)</sup>             | PW (TSSOP) | RGH (WQFN) | UNIT |  |  |

|                      |                                              | 16 PINS    | 16 PINS    |      |  |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 130        | 38         | °C/W |  |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 32         | 21         | °C/W |  |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 44.2       | 9.8        | °C/W |  |  |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 2          | 0.2        | °C/W |  |  |

| $\psi_{JB}$          | Junction-to-board characterization parameter | 43.5       | 9.8        | °C/W |  |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance |            | 2.4        | °C/W |  |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 7.5 Electrical Characteristics

The following specifications apply for  $V_A$  = 2.7 V to 5.5 V,  $V_{REF1}$  =  $V_{REF2}$  =  $V_A$ ,  $C_L$  = 200 pF to GND,  $f_{SCLK}$  = 30 MHz, input code range 3 to 252. Typical values apply for  $T_A$  = 25°C; minimum and maximum limits apply for  $T_A$  = -40°C to 125°C, unless otherwise specified.

|                 | PARAMETER                                            | TEST CONDITIONS                                                | MIN T    | YP MAX              | UNIT   |  |

|-----------------|------------------------------------------------------|----------------------------------------------------------------|----------|---------------------|--------|--|

| STATIC          | PERFORMANCE                                          |                                                                | -        |                     | ı      |  |

|                 | Resolution                                           |                                                                | 8        |                     | Bits   |  |

|                 | Monotonicity                                         |                                                                | 8        |                     | Bits   |  |

| INL             | Integral non-linearity                               |                                                                | ±0.      | 12 ±0.5             | LSB    |  |

| DNII            | Differential near linearity                          |                                                                | 0.       | 03 0.15             | LCD    |  |

| DNL             | Differential non-linearity                           |                                                                | -0.1 -0. | 02                  | LSB    |  |

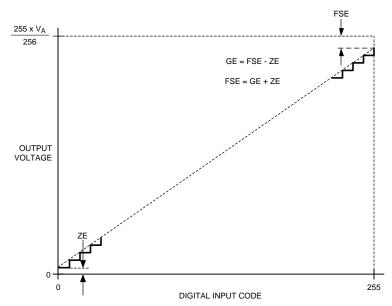

| ZE              | Zero code error                                      | I <sub>OUT</sub> = 0                                           |          | 5 15                | mV     |  |

| FSE             | Full-scale error                                     | I <sub>OUT</sub> = 0                                           | -(       | 0.1 –0.75           | %FSR   |  |

| GE              | Gain error                                           |                                                                | -(       | 0.2 –1              | %FSR   |  |

| ZCED            | Zero code error drift                                |                                                                | _        | -20                 | μV/°C  |  |

| TC GE           | Gain error tempco                                    |                                                                |          | <b>–</b> 1          | ppm/°C |  |

| OUTPUT          | CHARACTERISTICS                                      |                                                                |          |                     |        |  |

|                 | Output voltage range                                 |                                                                | 0        | V <sub>REF1,2</sub> | V      |  |

| l <sub>OZ</sub> | High-impedance output leakage current <sup>(1)</sup> |                                                                |          | ±1                  | μA     |  |

|                 |                                                      | V <sub>A</sub> = 3 V, I <sub>OUT</sub> = 200 μA                |          | 10                  |        |  |

| 700             | 7                                                    | V <sub>A</sub> = 3 V, I <sub>OUT</sub> = 1 mA                  |          | 45                  | >/     |  |

| ZCO             | Zero code output                                     | V <sub>A</sub> = 5 V, I <sub>OUT</sub> = 200 μA                |          | 8                   | mV     |  |

|                 |                                                      | V <sub>A</sub> = 5 V, I <sub>OUT</sub> = 1 mA                  |          | 34                  |        |  |

|                 |                                                      | V <sub>A</sub> = 3 V, I <sub>OUT</sub> = 200 μA                | 2.9      | 84                  |        |  |

| F00             | Full scale systems                                   | V <sub>A</sub> = 3 V, I <sub>OUT</sub> = 1 mA                  | 2.9      | 33                  | V      |  |

| FSO             | Full scale output                                    | V <sub>A</sub> = 5 V, I <sub>OUT</sub> = 200 μA                | 4.9      | 87                  | V      |  |

|                 |                                                      | $V_A = 5 \text{ V}, I_{OUT} = 1 \text{ mA}$                    | 4.9      | 55                  |        |  |

|                 | Output short circuit current                         | V <sub>A</sub> = 3 V, V <sub>OUT</sub> = 0 V, Input Code = FFh | _        | -50                 | A      |  |

| los (source)    |                                                      | V <sub>A</sub> = 5 V, V <sub>OUT</sub> = 0 V, Input Code = FFh | _        | -60                 | mA     |  |

|                 | Output short circuit current                         | V <sub>A</sub> = 3 V, V <sub>OUT</sub> = 3 V, Input Code = 00h |          | 50                  | A      |  |

| los             | (sink)                                               | V <sub>A</sub> = 5 V, V <sub>OUT</sub> = 5 V, Input Code = 00h |          | 70                  | mA     |  |

|                 | Continuous output current                            | T <sub>A</sub> = 105°C                                         |          | 10                  | mΛ     |  |

| I <sub>O</sub>  | per channel <sup>(1)</sup>                           | T <sub>A</sub> = 125°C                                         |          | 6.5                 | mA     |  |

(1) This parameter is specified by design or characterization and is not tested in production.

<sup>(2)</sup> Soldering process must comply with Texas Instruments' Reflow Temperature Profile specifications. See http://www.ti.com/packaging. Reflow temperature profiles are different for lead-free packages.

## **Electrical Characteristics (continued)**

The following specifications apply for  $V_A$  = 2.7 V to 5.5 V,  $V_{REF1}$  =  $V_{REF2}$  =  $V_A$ ,  $C_L$  = 200 pF to GND,  $f_{SCLK}$  = 30 MHz, input code range 3 to 252. Typical values apply for  $T_A$  = 25°C; minimum and maximum limits apply for  $T_A$  = -40°C to 125°C, unless otherwise specified.

|                  | PARAMETER                                                        | TEST CONDIT                                                            | IONS                                    | MIN  | TYP  | MAX   | UNIT |  |

|------------------|------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------|------|------|-------|------|--|

| ^                | Marrian and annual to an                                         | R <sub>L</sub> = ∞                                                     |                                         |      | 1500 |       |      |  |

| C <sub>L</sub>   | Maximum load capacitance                                         | $R_L = 2 k\Omega$                                                      |                                         | 1500 |      | pF    |      |  |

| Z <sub>OUT</sub> | DC output impedance                                              |                                                                        |                                         |      | 8    |       | Ω    |  |

| REFEREN          | NCE INPUT CHARACTERISTI                                          | cs                                                                     |                                         |      |      |       |      |  |

| VDEE4.0          | input range                                                      |                                                                        |                                         | 2.7  | 0.5  | $V_A$ | V    |  |

| VREF1,2          | Input impedance                                                  |                                                                        |                                         |      | 30   |       | kΩ   |  |

| LOGIC IN         | PUT CHARACTERISTICS                                              |                                                                        |                                         |      |      |       |      |  |

| I <sub>IN</sub>  | Input Current <sup>(1)</sup>                                     |                                                                        |                                         |      |      | ±1    | μΑ   |  |

| \ /              | lanut laurusliana                                                | V <sub>A</sub> = 2.7 V to 3.6 V                                        |                                         |      | 1    | 0.6   | V    |  |

| $V_{IL}$         | Input low voltage                                                | V <sub>A</sub> = 4.5 V to 5.5 V                                        |                                         |      | 1.1  | 0.8   | V    |  |

|                  | Lancet Is Sub-continue                                           | V <sub>A</sub> = 2.7 V to 3.6 V                                        |                                         | 2.1  | 1.4  |       |      |  |

| V <sub>IH</sub>  | Input high voltage                                               | V <sub>A</sub> = 4.5 V to 5.5 V                                        |                                         | 2.4  | 2    |       | V    |  |

| C <sub>IN</sub>  | Input Capacitance <sup>(1)</sup>                                 |                                                                        |                                         |      |      | 3     | pF   |  |

| POWER F          | REQUIREMENTS                                                     |                                                                        |                                         |      |      |       |      |  |

| V <sub>A</sub>   | Supply voltage                                                   |                                                                        |                                         | 2.7  |      | 5.5   | V    |  |

|                  | Normal supply current for supply pin V <sub>A</sub>              | f <sub>SCLK</sub> = 30 MHz, output unloaded                            | V <sub>A</sub> = 2.7 V to 3.6 V         |      | 460  | 575   |      |  |

|                  |                                                                  |                                                                        | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |      | 650  | 840   |      |  |

| I <sub>N</sub>   | Normal supply current for V <sub>REF1</sub> or V <sub>REF2</sub> | f 20 MHz, output uploaded                                              | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |      | 95   | 135   | μA   |  |

|                  |                                                                  | f <sub>SCLK</sub> = 30 MHz, output unloaded                            | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |      | 160  | 225   |      |  |

|                  | Static supply current for                                        | f <sub>SCLK</sub> = 0, output unloaded                                 | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |      | 370  |       |      |  |

| I                | supply pin V <sub>A</sub>                                        | ISCLK = 0, output unloaded                                             | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |      | 440  |       | μA   |  |

| I <sub>ST</sub>  | Static supply current for                                        | $f_{SCLK} = 0$ , output unloaded                                       | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |      | 95   |       | μΑ   |  |

|                  | V <sub>REF1</sub> or V <sub>REF2</sub>                           | ISCLK = 0, output unloaded                                             | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |      | 160  |       |      |  |

|                  |                                                                  | $f_{SCLK} = 30 \text{ MHz}, SYNC = V_A, and$                           | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |      | 0.2  | 1.5   |      |  |

| I                | Total power down supply                                          | D <sub>IN</sub> = 0 V after PD mode loaded                             | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |      | 0.5  | 3     | μΑ   |  |

| I <sub>PD</sub>  | current for all PD Modes <sup>(1)</sup>                          | f <sub>SCLK</sub> = 0, SYNC = V <sub>A</sub> , and                     | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |      | 0.1  | 1     | μΛ   |  |

|                  |                                                                  | $D_{IN} = 0 \text{ V}$ after PD mode loaded $V_A = 4.5 \text{ V}$ to 5 |                                         |      | 0.2  | 2     |      |  |

|                  |                                                                  | f <sub>SCLK</sub> = 30 MHz, output unloaded                            | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |      | 1.95 | 3     |      |  |

| $P_N$            | Total power consumption                                          | ISCLK = 30 Williz, Output unloaded                                     | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |      | 4.85 | 7.1   | mW   |  |

| ' N              | (output unloaded)                                                | f <sub>SCLK</sub> = 0, output unloaded                                 | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |      | 1.68 |       | mvv  |  |

|                  |                                                                  | SCLK - 0, output unloaded                                              | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |      | 3.8  |       |      |  |

|                  |                                                                  | f <sub>SCLK</sub> = 30 MHz, SYNC = V <sub>A</sub> , and                | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |      | 0.6  | 5.4   |      |  |

| Poo              | Total power consumption in                                       | D <sub>IN</sub> = 0 V after PD mode loaded                             | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |      | 2.5  | 16.5  | μW   |  |

| $P_{PD}$         | all PD Modes <sup>(1)</sup>                                      | $f_{SCLK} = 0$ , SYNC = $V_A$ , and                                    | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |      | 0.3  | 3.6   | μνν  |  |

|                  |                                                                  | D <sub>IN</sub> = 0 V after PD mode loaded                             | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |      | 1    | 11    | ļ    |  |

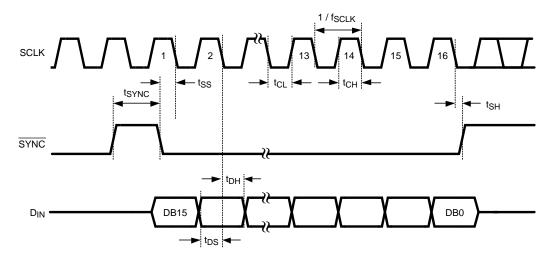

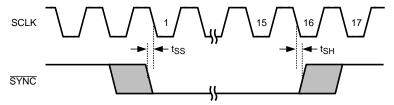

## 7.6 AC and Timing Requirements

Test limits are specified to AOQL (Average Outgoing Quality Level). Typical values apply for  $T_A = 25^{\circ}C$ ; minimum and maximum limits apply for  $T_A = -40^{\circ}C$  to 125°C, unless otherwise noted.

|                     |                                              |                                                               | MIN | NOM | MAX                     | UNIT     |

|---------------------|----------------------------------------------|---------------------------------------------------------------|-----|-----|-------------------------|----------|

| f <sub>SCLK</sub>   | SCLK frequency                               |                                                               |     | 40  | 30                      | MHz      |

| t <sub>s</sub>      | Output voltage settling time <sup>(1)</sup>  | 40h to C0h code change,<br>$R_L = 2 k\Omega$ , $C_L = 200 pF$ |     | 3   | 4.5                     | μs       |

| SR                  | Output Slew Rate                             |                                                               |     | 1   |                         | V/µs     |

| GI                  | Glitch Impulse                               | Code change from 80h to 7Fh                                   |     | 40  |                         | nV-sec   |

| DF                  | Digital Feedthrough                          |                                                               |     | 0.5 |                         | nV-sec   |

| DC                  | Digital Crosstalk                            |                                                               |     | 0.5 |                         | nV-sec   |

| CROSS               | DAC-to-DAC crosstalk                         |                                                               |     | 1   |                         | nV-sec   |

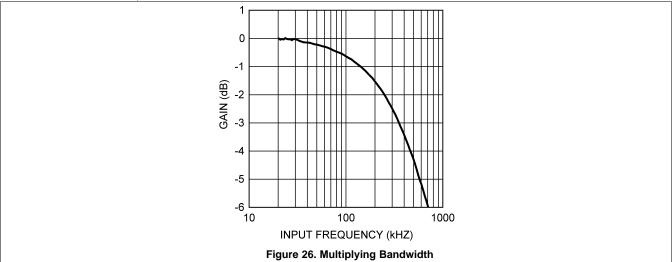

| MBW                 | Multiplying bandwidth                        | $V_{REF1,2} = 2.5 V \pm 2 V_{PP}$                             |     | 360 |                         | kHz      |

| ONSD                | Output noise spectral density                | DAC Code = 80h, 10 kHz                                        |     | 40  |                         | nV/√(Hz) |

| ON                  | Output noise                                 | BW = 30 kHz                                                   |     | 14  |                         | μV       |

|                     | Walance Care                                 | V <sub>A</sub> = 3 V                                          |     | 3   |                         |          |

| t <sub>WU</sub>     | Wake-up time                                 | V <sub>A</sub> = 5 V                                          |     | 20  |                         | μs       |

| 1/f <sub>SCLK</sub> | SCLK cycle time                              |                                                               | 33  | 25  |                         | ns       |

| t <sub>CH</sub>     | SCLK high time                               |                                                               | 10  | 7   |                         | ns       |

| $t_{CL}$            | SCLK low time                                |                                                               | 10  | 7   |                         | ns       |

|                     | CVAIC and up time hafare CCI I/ falling adap | T <sub>A</sub> = 25°C                                         |     | 3   | 1/f <sub>SCLK</sub> - 3 |          |

| t <sub>SS</sub>     | SYNC set-up time before SCLK falling edge    | $T_A = -40$ °C to 125°C                                       | 10  |     |                         | ns       |

| t <sub>DS</sub>     | Data set-up time before SCLK falling edge    |                                                               | 2.5 | 1   |                         | ns       |

| t <sub>DH</sub>     | Data hold time after SCLK falling edge       |                                                               | 2.5 | 1   |                         | ns       |

|                     | SYNC hold time after the 16th                | T <sub>A</sub> = 25°C                                         |     | 0   | 1/f <sub>SCLK</sub> - 3 |          |

| t <sub>SH</sub>     | falling edge of SCLK                         | $T_A = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$   | 3   |     |                         | ns       |

| t <sub>SYNC</sub>   | SYNC high time                               |                                                               | 15  | 5   |                         | ns       |

(1) This parameter is specified by design or characterization and is not tested in production.

Figure 1. Serial Timing Diagram

## 7.7 Typical Characteristics

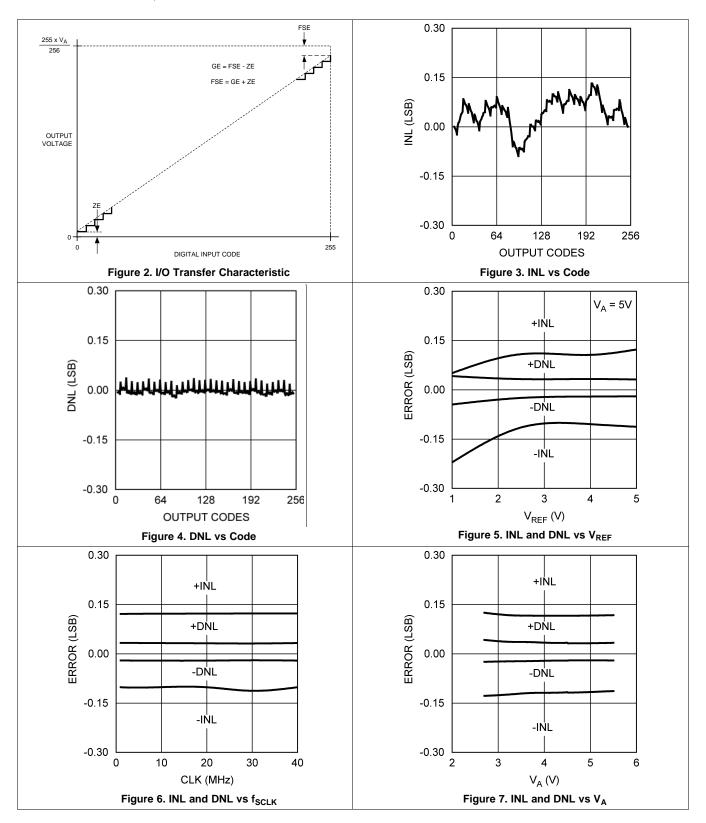

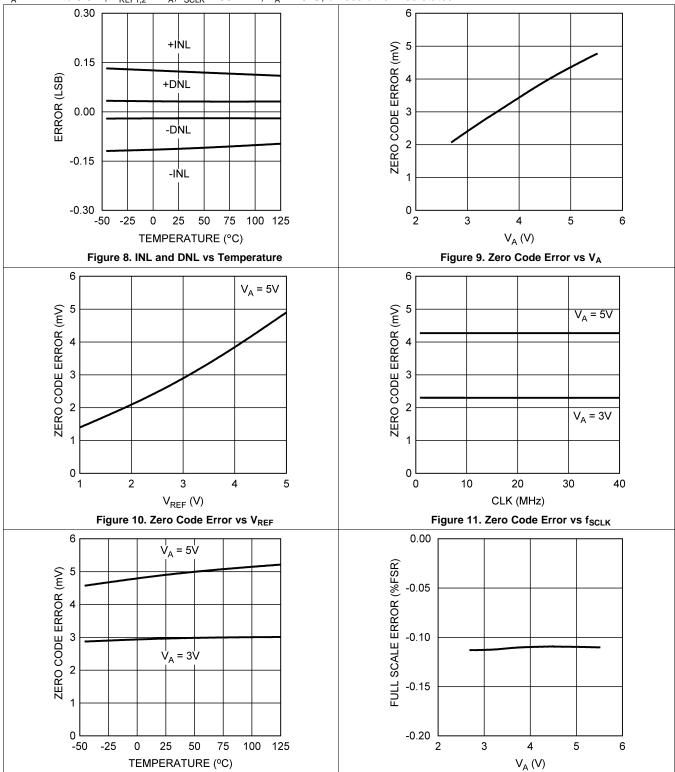

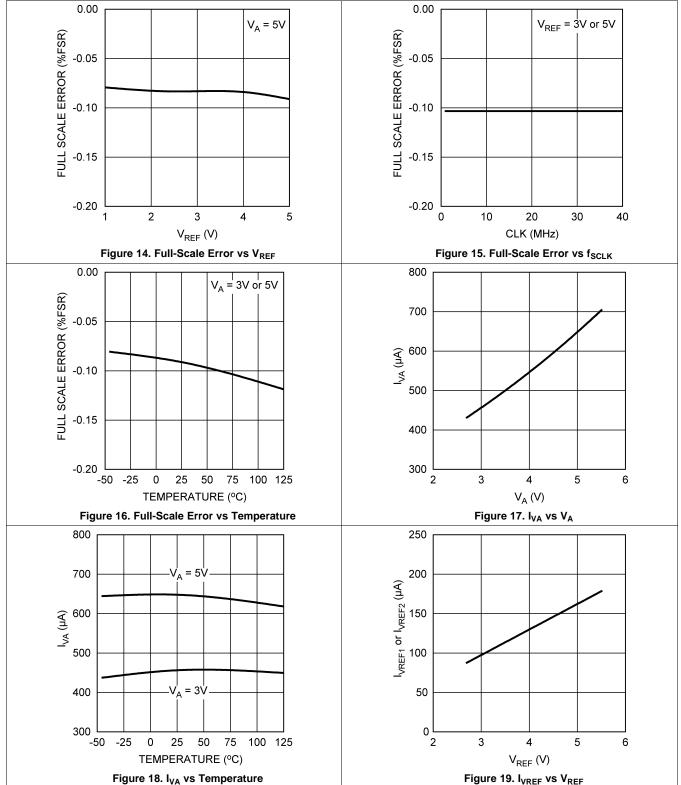

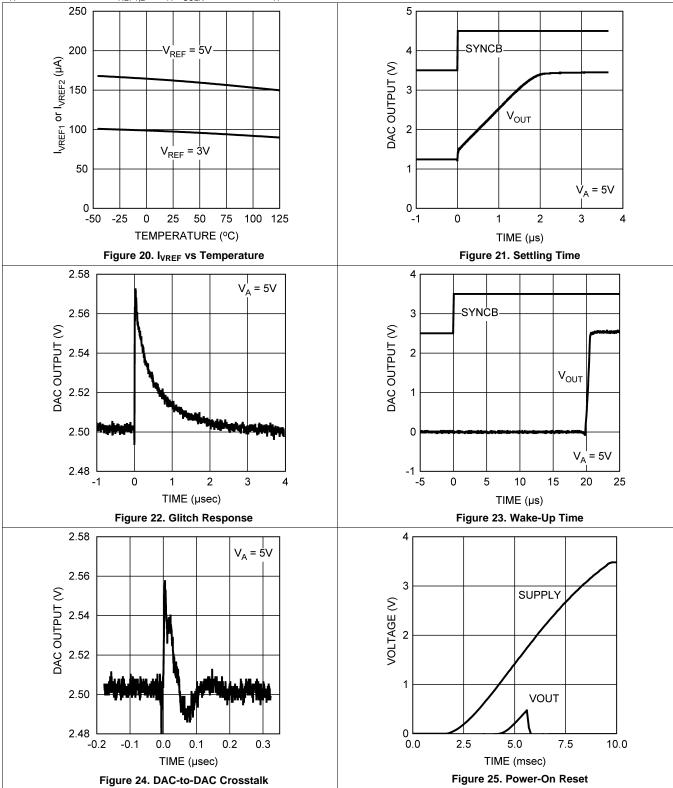

$V_A$  = 2.7 V to 5.5 V,  $V_{REF1,2}$  =  $V_A$ ,  $f_{SCLK}$  = 30 MHz,  $T_A$  = 25°C, unless otherwise stated

$V_A = 2.7 \text{ V}$  to 5.5 V,  $V_{REF1,2} = V_A$ ,  $f_{SCLK} = 30 \text{ MHz}$ ,  $T_A = 25^{\circ}\text{C}$ , unless otherwise stated

Figure 12. Zero Code Error vs Temperature

Figure 13. Full-Scale Error vs V<sub>A</sub>

$V_A = 2.7 \text{ V}$  to 5.5 V,  $V_{REF1,2} = V_A$ ,  $f_{SCLK} = 30 \text{ MHz}$ ,  $T_A = 25^{\circ}\text{C}$ , unless otherwise stated

$V_A = 2.7 \text{ V}$  to 5.5 V,  $V_{REF1,2} = V_A$ ,  $f_{SCLK} = 30 \text{ MHz}$ ,  $T_A = 25^{\circ}\text{C}$ , unless otherwise stated

$V_A$  = 2.7 V to 5.5 V,  $V_{REF1,2}$  =  $V_A$ ,  $f_{SCLK}$  = 30 MHz,  $T_A$  = 25°C, unless otherwise stated

## 8 Detailed Description

## 8.1 Overview

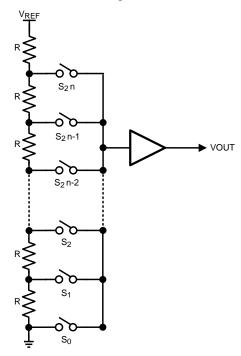

The DAC085S085 is fabricated on a CMOS process with an architecture that consists of switches and resistor strings that are followed by an output buffer.

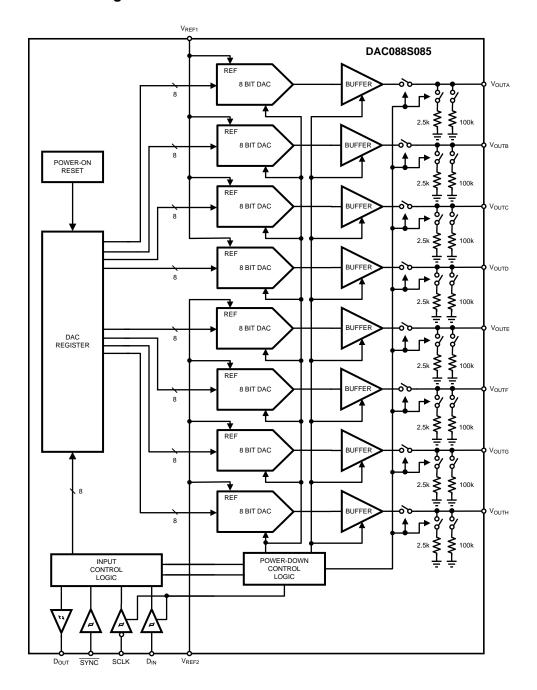

## 8.2 Functional Block Diagram

(2)

### 8.3 Feature Description

### 8.3.1 DAC Architecture

The DAC088S085 is fabricated on a CMOS process with an architecture that consists of switches and resistor strings that are followed by an output buffer. The reference voltages are externally applied at  $V_{REF1}$  for DAC channels A through D and  $V_{REF2}$  for DAC channels E through H.

For simplicity, a single resistor string is shown in Figure 27. This string consists of 256 equal valued resistors with a switch at each junction of two resistors, plus a switch-to-ground. The code loaded into the DAC register determines which switch is closed, connecting the proper node to the amplifier. The input coding is straight binary with an ideal output voltage of:

$$V_{OUTA,B,C,D} = V_{REF1} \times (D / 256)$$

(1)

$V_{OUTE,F,G,H} = V_{REF2} \times (D / 256)$

where

D is the decimal equivalent of the binary code that is loaded into the DAC register.

D can take on any value between 0 and 255. This configuration ensures that the DAC is monotonic.

Figure 27. DAC Resistor String

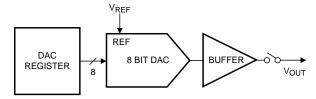

Because all eight DAC channels of the DAC088S085 can be controlled independently, each channel consists of a DAC register and a 8-bit DAC. Figure 28 is a simple block diagram of an individual channel in the DAC088S085. Depending on the mode of operation, data written into a DAC register causes the 8-bit DAC output to be updated or an additional command is required to update the DAC output. Further description of the modes of operation can be found in *Serial Interface*.

Figure 28. Single-Channel Block Diagram

## **Feature Description (continued)**

### 8.3.2 Output Amplifiers

The output amplifiers are rail-to-rail, providing an output voltage range of 0 V to  $V_A$  when the reference is  $V_A$ . All amplifiers, even rail-to-rail types, exhibit a loss of linearity as the output approaches the supply rails (0 V and  $V_A$ , in this case). For this reason, linearity is specified over less than the full output range of the DAC. However, if the reference is less than  $V_A$ , there is only a loss in linearity in the lowest codes.

The output amplifiers are capable of driving a load of 2 k $\Omega$  in parallel with 1500 pF to ground or to  $V_A$ . The zero-code and full-scale outputs for given load currents are available in *Electrical Characteristics*.

### 8.3.3 Reference Voltage

The DAC088S085 uses dual external references,  $V_{REF1}$  and  $V_{REF2}$ , that are shared by channels A, B, C, D and channels E, F, G, H respectively. The reference pins are not buffered and have an input impedance of 30 k $\Omega$ . TI recommends that  $V_{REF1}$  and  $V_{REF2}$  be driven by voltage sources with low output impedance. The reference voltage range is 0.5 V to  $V_A$ , providing the widest possible output dynamic range.

### 8.4 Device Functional Modes

### 8.4.1 Power-On Reset

The power-on reset circuit controls the output voltages of the eight DACs during power up. Upon application of power, the DAC registers are filled with zeros and the output voltages are set to 0 V. The outputs remain at 0 V until a valid write sequence is made.

### 8.4.2 Power-Down Modes

The DAC088S085 has three power-down modes where different output terminations can be selected (see Table 1). With all channels powered down, the supply current drops to 0.1  $\mu$ A at 3 V and 0.2  $\mu$ A at 5 V. By selecting the channels to be powered down in DB[7:0] with a 1, individual channels can be powered down separately or multiple channels can be powered down simultaneously. The three different output terminations include high output impedance, 100 k $\Omega$  to GND, and 2.5 k $\Omega$  to GND.

The output amplifiers, resistor strings, and other linear circuitry are all shut down in any of the power-down modes. The bias generator, however, is only shut down if all the channels are placed in power down mode. The contents of the DAC registers are unaffected when in power down. Therefore, each DAC register maintains its value before the DAC088S085 being powered down unless it is changed during the write sequence which instructed it to recover from power down. Minimum power consumption is achieved in the power-down mode with SYNC idled high,  $D_{IN}$  idled low, and SCLK disabled. The time to exit power-down (Wake-Up Time) is typically 3  $\mu$ s at 3 V and 20  $\mu$ s at 5 V.

**Table 1. Power-Down Modes**

| DB[15:12] | DB[11:8] | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | OUTPUT IMPEDANCE |

|-----------|----------|---|---|---|---|---|---|---|---|------------------|

| 1101      | XXXX     | Н | G | F | Е | D | С | В | Α | High-Z outputs   |

| 1110      | XXXX     | Н | G | F | Е | D | С | В | Α | 100-kΩ outputs   |

| 1111      | XXXX     | Н | G | F | Е | D | С | В | Α | 2.5-kΩ outputs   |

Product Folder Links: DAC088S085

## 8.5 Programming

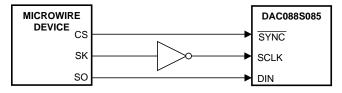

#### 8.5.1 Serial Interface

The three-wire interface is compatible with SPI, QSPI, and MICROWIRE, as well as most DSPs and operates at clock rates up to 40 MHz. A valid serial frame contains 16 falling edges of SCLK. See Figure 1 for information on a write sequence.

A write sequence begins by bringing the SYNC line low. Once SYNC is low, the data on the D<sub>IN</sub> line is clocked into the 16-bit serial input register on the falling edges of SCLK. To avoid mis-clocking data into the shift register, it is critical that SYNC not be brought low on a falling edge of SCLK (see minimum and maximum setup times for SYNC in Figure 1 and Figure 29). On the 16th falling edge of SCLK, the last data bit is clocked into the register. The write sequence is concluded by bringing the SYNC line high. Once SYNC is high, the programmed function (a change in the DAC channel address, mode of operation or register contents) is executed. To avoid misclocking data into the shift register, it is critical that SYNC be brought high between the 16th and 17th falling edges of SCLK (see minimum and maximum hold times for SYNC in Figure 1 and Figure 29).

Figure 29. CS Setup and Hold Times

If  $\overline{\text{SYNC}}$  is brought high before the 15th falling edge of  $\overline{\text{SCLK}}$ , the write sequence is aborted and the data that has been shifted into the input register is discarded. If  $\overline{\text{SYNC}}$  is held low beyond the 17th falling edge of SCLK, the serial data presented at  $D_{\text{IN}}$  begins to be output on  $D_{\text{OUT}}$ . More information on this mode of operation can be found in  $D_{\text{aisy}}$   $C_{\text{hain}}$   $D_{\text{peration}}$ . In either case,  $\overline{\text{SYNC}}$  must  $\overline{\text{be}}$  brought high for the minimum specified time before the next write sequence is initiated with a falling edge of  $\overline{\text{SYNC}}$ .

Because the  $D_{IN}$  buffer draws more current when it is high, it must be idled low between write sequences to minimize power consumption. On the other hand, SYNC must be idled high to avoid the activation of daisy chain operation where  $D_{OUT}$  is active.

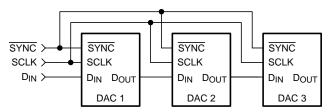

### 8.5.2 Daisy Chain Operation

Daisy chain operation allows communication with any number of DAC088S085s using a single serial interface. As long as the correct number of data bits are input in a write sequence (multiple of sixteen bits), a rising edge of SYNC properly updates all DACs in the system.

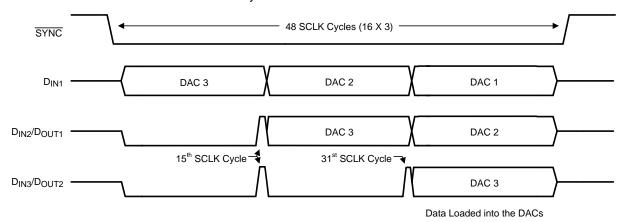

To support multiple devices in a daisy chain configuration, SCLK and  $\overline{\text{SYNC}}$  are shared across all DAC088S085s and D<sub>OUT</sub> of the first DAC in the chain is connected to D<sub>IN</sub> of the second. Figure 30 shows three DAC088S085s connected in daisy chain fashion. Similar to a single-channel write sequence, the conversion for a daisy chain operation begins on a falling edge of  $\overline{\text{SYNC}}$  and ends on a rising edge of  $\overline{\text{SYNC}}$ . A valid write sequence for n devices in a chain requires n times 16 falling edges to shift the entire input data stream through the chain. Daisy chain operation is specified for a maximum SCLK speed of 30 MHz.

Figure 30. Daisy Chain Configuration

## **Programming (continued)**

The serial data output pin,  $D_{OUT}$ , is available on the DAC088S085 to allow daisy-chaining of multiple DAC088S085 devices in a system. In a write sequence,  $D_{OUT}$  remains low for the first fourteen falling edges of SCLK before going high on the fifteenth falling edge. Subsequently, the next sixteen falling edges of SCLK outputs the first sixteen data bits entered into  $D_{IN}$ . Figure 31 shows the timing of three DAC088S085s in Figure 30. In this instance, It takes forty-eight falling edges of SCLK followed by a rising edge of SYNC to load all three DAC088S085s with the appropriate register data. On the rising edge of SYNC, the programmed function is executed in each DAC088S085 simultaneously.

Figure 31. Daisy Chain Timing Diagram

### 8.5.3 Serial Input Register

The DAC088S085 has two modes of operation plus a few special command operations. The two modes of operation are Write Register Mode (WRM) and Write Through Mode (WTM). For the rest of this document, these modes is referred to as WRM and WTM. The special command operations are separate from WRM and WTM because they can be called upon regardless of the current mode of operation. The mode of operation is controlled by the first four bits of the control register, DB15 through DB12. See Table 2 for a detailed summary.

Table 2. Write Register and Write Through Modes

| DB[15:12] | DB[11:0]    | DESCRIPTION OF MODE                                                                               |  |  |  |

|-----------|-------------|---------------------------------------------------------------------------------------------------|--|--|--|

| 1000      | xxxxxxxxxx  | WRM: The registers of each DAC Channel can be written to without causing their outputs to change. |  |  |  |

| 1 0 0 1   | XXXXXXXXXXX | WTM: Writing data to a channel's register causes the DAC output to change.                        |  |  |  |

When the DAC088S085 first powers up, the DAC is in WRM. In WRM, the registers of each individual DAC channel can be written to without causing the DAC outputs to be updated. This is accomplished by setting DB15 to 0, specifying the DAC register to be written to in DB[14:12], and entering the new DAC register setting in DB[11:0] (see Table 3). The DAC088S085 remains in WRM until the mode of operation is changed to WTM. The mode of operation is changed from WRM to WTM by setting DB[15:12] to 1001. Once in WTM, writing data to a DAC channel's register causes the DAC's output to be updated as well. Changing a DAC channel's register in WTM is accomplished in the same manner as it is done in WRM. However, in WTM the DAC's register and output are updated at the completion of the command (see Table 3). Similarly, the DAC088S085 remains in WTM until the mode of operation is changed to WRM by setting DB[15:12] to 1000.

Table 3. Commands Impacted by WRM and WTM

| DB15 | DB[14:12] | DB[11:0]           | DESCRIPTION OF MODE                                                                              |

|------|-----------|--------------------|--------------------------------------------------------------------------------------------------|

| 0    | 0 0 0     | D11 D10 D4 X X X X | WRM: D[11:0] written to ChA's data register only WTM: ChA's output is updated by data in D[11:0] |

| 0    | 0 0 1     | D11 D10 D4 X X X X | WRM: D[11:0] written to ChB's data register only WTM: ChB's output is updated by data in D[11:0] |

| 0    | 0 1 0     | D11 D10 D4 X X X X | WRM: D[11:0] written to ChC's data register only WTM: ChC's output is updated by data in D[11:0] |

| 0    | 0 1 1     | D11 D10 D4 X X X X | WRM: D[11:0] written to ChD's data register only WTM: ChD's output is updated by data in D[11:0] |

| 0    | 100       | D11 D10 D4 X X X X | WRM: D[11:0] written to ChE's data register only WTM: ChE's output is updated by data in D[11:0] |

| 0    | 1 0 1     | D11 D10 D4 X X X X | WRM: D[11:0] written to ChF's data register only WTM: ChF's output is updated by data in D[11:0] |

| 0    | 110       | D11 D10 D4 X X X X | WRM: D[11:0] written to ChG's data register only WTM: ChG's output is updated by data in D[11:0] |

| 0    | 111       | D11 D10 D4 X X X X | WRM: D[11:0] written to ChH's data register only WTM: ChH's output is updated by data in D[11:0] |

As mentioned previously, the special command operations can be exercised at any time regardless of the mode of operation. There are three special command operations. The first command is exercised by setting data bits DB[15:12] to 1010. This allows a user to update multiple DAC outputs simultaneously to the values currently loaded in their respective control registers. This command is valuable if the user wants each DAC output to be at a different output voltage but still have all the DAC outputs change to their appropriate values simultaneously (see Table 4).

The second special command allows the user to alter the DAC output of channel A with a single write frame. This command is exercised by setting data bits DB[15:12] to 1011 and data bits DB[11:0] to the desired control register value. It also has the added benefit of causing the DAC outputs of the other channels to update to their current control register values as well. A user may choose to exercise this command to save a write sequence. For example, the user may wish to update several DAC outputs simultaneously, including channel A. To accomplish this task in the minimum number of write frames, the user would alter the control register values of all the DAC channels except channel A while operating in WRM. The last write frame would be used to exercise the special command *Channel A Write Mode*. In addition to updating channel A's control register and output to a new value, all of the other channels would be updated as well. At the end of this sequence of write frames, the DAC088S085 would still be operating in WRM (see Table 4).

The third special command allows the user to set all the DAC control registers and outputs to the same level. This command is commonly referred to as *broadcast* mode because the same data bits are being broadcast to all of the channels simultaneously. This command is exercised by setting data bits DB[15:12] to 1100 and data bits DB[7:0] to the value that the user wishes to broadcast to all the DAC control registers. Once the command is exercised, each DAC output is updated by the new control register value. This command is frequently used to set all the DAC outputs to some known voltage such as 0 V, V<sub>REF</sub> / 2, or Full Scale. A summary of the commands can be found in Table 4.

**Table 4. Special Command Operations**

| DB[15:12] | DB[11:0]           | DESCRIPTION OF MODE                                                                                                                                                                                                    |

|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1010      | XXXXHGFEDCBA       | Update Select: The DAC outputs of the channels selected with a 1 in DB[7:0] are updated simultaneously to the values in their respective control registers.                                                            |

| 1011      | D11 D10 D4 X X X   | Channel A Write: the control register of Channel A and DAC output are updated to the data in DB[11:0]. The outputs of the other seven channels are also updated according to their respective control register values. |

| 1100      | D11 D10 D4 X X X X | Broadcast: The data in DB[11:0] is written to all channels' control register and DAC output simultaneously.                                                                                                            |

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

## 9.1.1 Examples Programming the DAC088S085

This section presents the step-by-step instructions for programming the serial input register.

### 9.1.1.1 Updating DAC Outputs Simultaneously

When the DAC088S085 is first powered on, the DAC is operating in Write Register Mode (WRM). Operating in WRM allows the user to program the registers of multiple DAC channels without causing the DAC outputs to be updated. As an example, here are the steps for setting Channel A to a full scale output, Channel B to three-quarters full scale, Channel C to half-scale, Channel D to one-quarter full scale and having all the DAC outputs update simultaneously.

As stated previously, the DAC088S085 powers up in WRM. If the device was previously operating in Write Through Mode (WTM), an extra step to set the DAC into WRM would be required. First, the DAC registers need to be programmed to the desired values. To set Channel A to an output of full scale, write 0FF0 to the control register. This updates the data register for Channel A without updating the output of Channel A. Second, set Channel B to an output of three-quarters full scale by writing 1C00 to the control register. This updates the data register for Channel B. Once again, the output of Channel B and Channel A is not updated because the DAC is operating in WRM. Third, set Channel C to half scale by writing 2800 to the control register. Fourth, set Channel D to one-quarter full scale by writing 3400 to the control register. Finally, update all four DAC channels simultaneously by writing A00F to the control register. This procedure allows the user to update four channels simultaneously with five steps.

Because Channel A was one of the DACs to be updated, one command step could have been saved by writing to Channel A last. This is accomplished by writing to Channel B, C, and D first and using the special command Channel A Write to update the DAC register and output of Channel A. This special command has the added benefit of updating all DAC outputs while updating Channel A. With this sequence of commands, the user was able to update four channels simultaneously with four steps. A summary of this command can be found in Table 4.

### 9.1.1.2 Updating DAC Outputs Independently

If the DAC088S085 is currently operating in WRM, change the mode of operation to WTM by writing 9XXX to the control register. Once the DAC is operating in WTM, any DAC channel can be updated in one step. For example, if a design required Channel G to be set to half scale, the user can write 6800 to the control register and the data register of Channel G and DAC output is updated. Similarly, if the output of Channel F needed to be set to full scale, 5FF0 would need to be written to the control register. Channel A is the only channel that has a special command that allows its DAC output to be updated in one command regardless of the mode of operation. Setting the DAC output of Channel A to full scale could be accomplished in one step by writing BFFF to the control register.

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

## **Application Information (continued)**

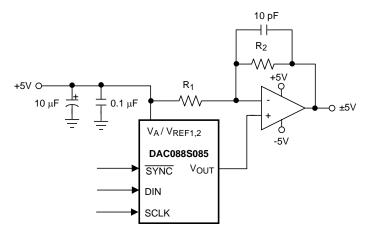

## 9.1.2 Bipolar Operation

The DAC088S085 is designed for single-supply operation and thus has a unipolar output. However, a bipolar output may be achieved with the circuit in Figure 32. This circuit provides an output voltage range of ±5 V. A railto-rail amplifier must be used if the amplifier supplies are limited to ±5 V.

Figure 32. Bipolar Operation

The output voltage of this circuit for any code is found to be

$$V_O = V_A \times (D / 256) \times ((R1 + R2) / R1) - V_A \times R2 / R1$$

where

• D is the input code in decimal form.

With

$$V_A = 5 V$$

and  $R1 = R2$ ,

$$V_0 = (10 \times D / 256) - 5 V$$

(4)

A list of rail-to-rail amplifiers suitable for this application are indicated in Table 5.

Table 5. Some Rail-to-Rail Amplifiers

| AMP     | PKGS   | TYP V <sub>os</sub> | TYP I <sub>SUPPLY</sub> |

|---------|--------|---------------------|-------------------------|

| LMP7701 | SOT-23 | ±37 μV              | 0.79 mA                 |

| LMV841  | SOT-23 | –17 μV              | 1.11 mA                 |

| LMC7111 | SOT-23 | 900 μV              | 25 μΑ                   |

| LM7301  | SOT-23 | 30 μV               | 620 µA                  |

| LM8261  | SOT-23 | 700 μV              | 1 mA                    |

Copyright © 2007-2016, Texas Instruments Incorporated

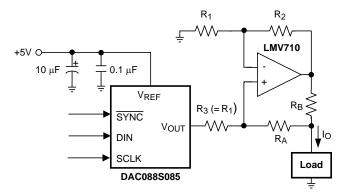

## 9.1.3 Variable Current Source Output

The DAC088S085 is a voltage output DAC but can be easily converted to a current output with the addition of an operational amplifier. In Figure 33, one of the channels of the DAC088S085 is converted to a variable current source capable of sourcing up to 40 mA.

Figure 33. Variable Current Source

The output current of this circuit (I<sub>O</sub>) for any DAC code is found to be

$$I_{O} = (V_{REF} \times (D / 256) \times (R_{2})) / (R_{1} \times R_{B})$$

where

· D is the input code in decimal form

$$\bullet \quad R_2 = R_A + R_B \tag{5}$$

### 9.1.4 DSP and Microprocessor Interfacing

Interfacing the DAC088S085 to microprocessors and DSPs is quite simple. The following guidelines are offered to hasten the design process.

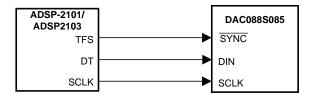

### 9.1.4.1 ADSP-2101 and ADSP2103 Interfacing

Figure 34 shows a serial interface between the DAC088S085 and the ADSP-2101 or ADSP2103. The DSP must be set to operate in the SPORT Transmit Alternate Framing Mode. It is programmed through the SPORT control register and must be configured for Internal Clock Operation, Active Low Framing and 16-bit Word Length. Transmission is started by writing a word to the Tx register after the SPORT mode has been enabled.

Figure 34. ADSP-2101 and ADSP-2103 Interface

22

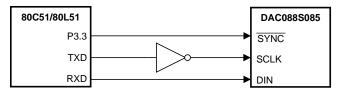

#### 9.1.4.2 80C51 and 80L51 Interface

A serial interface between the DAC088S085 and the 80C51 or 80L51 microcontroller is shown in Figure 35. The SYNC signal comes from a bit-programmable pin on the microcontroller. The example shown here uses port line P3.3. This line is taken low when data is transmitted to the DAC088S085. Because the 80x51 transmits 8-bit bytes, only eight falling clock edges occur in the transmit cycle. To load data into the DAC, the P3.3 line must be left low after the first eight bits are transmitted. A second write cycle is initiated to transmit the second byte of data, after which port line P3.3 is brought high. The 80x51 transmit routine must recognize that the 80x51 transmits data with the LSB first while the DAC088S085 requires data with the MSB first.

Figure 35. 80C51 and 80L51 Interface

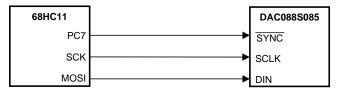

#### 9.1.4.3 68HC11 Interface

A serial interface between the DAC088S085 and the 68HC11 microcontroller is shown in Figure 36. The SYNC line of the DAC088S085 is driven from a port line (PC7 in the figure), similar to the 80C51 and 80L51.

The 68HC11 must be configured with its CPOL bit as a zero and its CPHA bit as a one. This configuration causes data on the MOSI output to be valid on the falling edge of SCLK. PC7 is taken low to transmit data to the DAC. The 68HC11 transmits data in 8-bit bytes with eight falling clock edges. Data is transmitted with the MSB first. PC7 must remain low after the first eight bits are transferred. A second write cycle is initiated to transmit the second byte of data to the DAC, after which PC7 must be raised to end the write sequence.

Figure 36. 68HC11 Interface

### 9.1.4.4 Microwire Interface

Figure 37 shows an interface between a Microwire compatible device and the DAC088S085. Data is clocked out on the rising edges of the SK signal. As a result, the SK of the Microwire device must be inverted before driving the SCLK of the DAC088S085.

Figure 37. Microwire Interface

Copyright © 2007–2016, Texas Instruments Incorporated

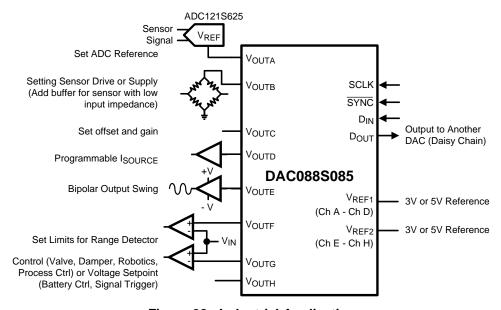

### 9.1.5 Industrial Application

Figure 38 shows the DAC088S085 controlling several different circuits in an industrial setting. Channel A is shown providing the reference voltage to the ADC081S625, one of Texas Instruments' general-purpose Analog-to-Digital Converters (ADCs). The reference for the ADC121S625 may be set to any voltage from 0.2 V to 5.5 V, providing the widest dynamic range possible. Typically, the ADC121S625 is monitoring a sensor and would benefit from the reference voltage of ADC being adjustable. Channel B is providing the drive or supply voltage for a sensor. By having the sensor supply voltage adjustable, the output of the sensor can be optimized to the input level of the ADC monitoring it. Channel C is defined to adjust the offset or gain of an amplifier stage in the system. Channel D is configured with an operational amplifier to provide an adjustable current source. Being able to convert one of the eight channels of the DAC088S085 to a current output eliminates the need for a separate current output DAC to be added to the circuit. Channel E, in conjunction with an operational amplifier, provides a bipolar output swing for devices requiring control voltages that are centered around ground. Channel F and G are used to set the upper and lower limits for a range detector. Channel H is reserved for providing voltage control or acting as a voltage setpoint.

Figure 38. Industrial Application

24

Submit Documentation Feedback

Product Folder Links: DAC088S085

### 9.2 Typical Applications

The following figures are examples of the DAC088S085 in typical application circuits. These circuits are basic and generally requires modification for specific circumstances.

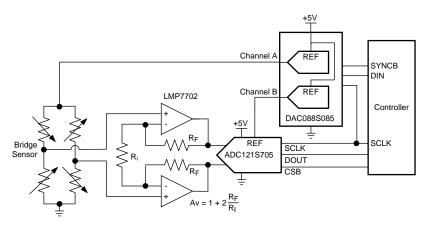

#### 9.2.1 ADC Reference

Figure 39 shows Channel A of the DAC088S085 providing the drive or supply voltage for a bridge sensor. By having the sensor supply voltage adjustable, the output of the sensor can be optimized to the input level of the ADC monitoring it.

Figure 39. Driving an ADC Reference

## 9.2.1.1 Design Requirements

For this design example, use these requirements:

- Provide drive for a bridge sensor that is adjustable through SPI from an MCU.

- Provide reference voltage for an ADC that is adjustable through SPI from an MCU.

- Use a single 5 V supply.

- Use ratiometric design for the bridge and ADC reference.

#### 9.2.1.2 Detailed Design Procedure

The output of the sensor is amplified by a fixed gain amplifier stage with a differential gain of  $1 + 2 \times (R_F / R_I)$ . The advantage of this amplifier configuration is the high input impedance seen by the output of the bridge sensor. The disadvantage is the poor common-mode rejection ratio (CMRR). The common-mode voltage ( $V_{CM}$ ) of the bridge sensor is half of the DAC output of Channel A. The  $V_{CM}$  is amplified by a gain of 1 V/V by the amplifier stage and thus becomes the bias voltage for the input of the ADC121S705. Channel B of the DAC088S085 is providing the reference voltage to the ADC121S705. The reference for the ADC121S705 may be set to any voltage from 1 V to 5 V, providing the widest dynamic range possible.

The reference voltage for Channel A and B is powered by an external 5 V power supply. Because the 5 V supply is common to the sensor supply voltage and the reference voltage of the ADC, fluctuations in the value of the 5-V supply has a minimal effect on the digital output code of the ADC. This type of configuration is often referred to as a *Ratio-metric* design. For example, an increase of 5% to the 5 V supply causes the sensor supply voltage to increase by 5%. This causes the gain or sensitivity of the sensor to increase by 5%. The gain of the amplifier stage is unaffected by the change in supply voltage. The ADC121S705 on the other hand, also experiences a 5% increase to its reference voltage. This causes the size of the least significant bit (LSB) of the ADC to increase by 5%. As a result of the sensor's gain increasing by 5% and the LSB size of the ADC increasing by the same 5%, there is no net effect on the circuit's performance. It is assumed that the amplifier gain is set low enough to allow for a 5% increase in the sensor output. Otherwise, the increase in the sensor output level may cause the output of the amplifiers to clip.

## **Typical Applications (continued)**

### 9.2.1.3 Application Curve

Figure 40. I/O Transfer Characteristic

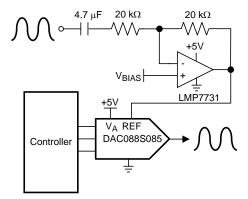

### 9.2.2 Programmable Attenuator

Figure 41 shows one of the channels of the DAC088S085 being used as a single-quadrant multiplier.

Figure 41. Programmable Attenuator Diagram

### 9.2.2.1 Design Requirements

For this design example, use these requirements:

- Use a single 5 V supply.

- Use the SPI interface to control the amount of attenuation of a signal.

- Do not add any noise to the signal.

### 9.2.2.2 Detailed Design Procedure

In this configuration, an AC or DC signal can be driven into one of the reference pins. The SPI interface of the DAC can be used to digitally attenuate the signal to any level from 0 dB (full scale) to 0 V. This is accomplished without adding any noticeable level of noise to the signal. An amplifier stage is shown in Figure 41 as a reference for applications where the input signal requires amplification. Notice how the AC signal in this application is AC-coupled to the amplifier before being amplified. A separate bias voltage is used to set the common-mode voltage for the DAC088S085's reference input to  $V_{\rm A}$  / 2, allowing the largest possible input swing. The multiplying bandwidth of  $V_{\rm REF1,2}$  is 360 kHz with a  $V_{\rm CM}$  of 2.5 V and a peak-to-peak signal swing of 2 V.

## **Typical Applications (continued)**

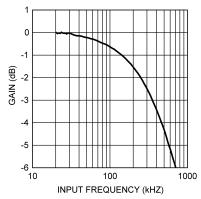

### 9.2.2.3 Application Curve

Figure 42. Multiplying Bandwidth

### 9.3 Do's and Don'ts

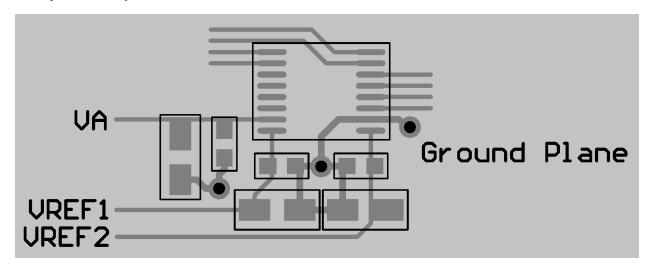

- Install bypass capacitors next to the V<sub>A</sub>, V<sub>REF1</sub>, and V<sub>REF2</sub> pins.

- The reference inputs must be kept stable and noise free. Besides installing bypass capacitors close to the pins, the traces that have the reference voltages must kept away from noisy traces.

- Keep analog and digital traces away from each other. If they need to cross, have the traces cross at a 90° angle.

## 10 Power Supply Recommendations

## 10.1 Using References as Power Supplies

While the simplicity of the DAC088S085 implies ease of use, it is important to recognize that the path from the reference input ( $V_{REF1,2}$ ) to the DAC outputs has zero Power Supply Rejection Ratio (PSRR). Therefore, it is necessary to provide a noise-free supply voltage to  $V_{REF1,2}$ . To use the full dynamic range of the DAC088S085, the supply pin ( $V_A$ ) and  $V_{REF1,2}$  can be connected together and share the same supply voltage. Because the DAC088S085 consumes very little power, a reference source may be used as the reference input or the supply voltage. The advantages of using a reference source over a voltage regulator are accuracy and stability. Some low noise regulators can also be used. Listed below are a few reference and power supply options for the DAC088S085.

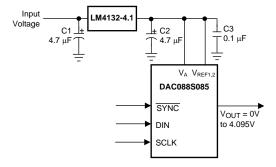

#### 10.1.1 LM4132

The LM4132, with its ±0.05% accuracy over temperature, is a good choice as a reference source for the DAC088S085. The 4.096 V version is useful if a 0 V to 4.09 V output range is desirable. Bypassing the LM4132 voltage input pin with a 4.7-μF capacitor and the voltage output pin with a 4.7-μF capacitor improves stability and reduce output noise. The LM4132 comes in a space-saving, 5-pin SOT-23 package.

Figure 43. The LM4132 as a Power Supply

(7)

## **Using References as Power Supplies (continued)**

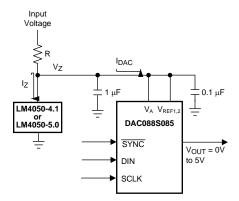

#### 10.1.2 LM4050

Available with accuracy of  $\pm 0.1\%$ , the LM4050 shunt reference is also a good choice as a reference for the DAC088S085. It is available in 4.096 V and 5 V versions and comes in a space-saving, 3-pin SOT-23 package.

Figure 44. The LM4050 as a Power Supply

The minimum resistor value in the circuit of Figure 44 must be chosen such that the maximum current through the LM4050 does not exceed its 15-mA rating. The conditions for maximum current include the input voltage at its maximum, the LM4050 voltage at its minimum, and the DAC088S085 drawing zero current. The maximum resistor value must allow the LM4050 to draw more than its minimum current for regulation plus the maximum DAC088S085 current in full operation. The conditions for minimum current include the input voltage at its minimum, the LM4050 voltage at its maximum, the resistor value at its maximum due to tolerance, and the DAC088S085 draws its maximum current. These conditions can be summarized as:

$$R(\min) = (V_{IN}(\max) - V_{Z}(\min)) / I_{Z}(\max)$$

(6)

and

$R(max) = (V_{IN}(min) - V_{Z}(max)) / (I_{DAC}(max) + I_{Z}(min))$

where

- V<sub>Z</sub>(min) and V<sub>Z</sub>(max) are the nominal LM4050 output voltages ± the LM4050 output tolerance over temperature

- I<sub>Z</sub>(max) is the maximum allowable current through the LM4050, I<sub>Z</sub>(min) is the minimum current required by the LM4050 for proper regulation

- I<sub>DAC</sub>(max) is the maximum DAC088S085 supply current.

#### 10.1.3 LP3985

The LP3985 is a low-noise, ultra-low dropout voltage regulator with a ±3% accuracy over temperature. It is a good choice for applications that do not require a precision reference for the DAC088S085. It comes in 3 V, 3.3 V, and 5 V versions, among others, and sports a low 30-µV noise specification at low frequencies. Because low frequency noise is relatively difficult to filter, this specification could be important for some applications. The LP3985 comes in a space-saving, 5-pin SOT-23 and 5-bump DSBGA packages.

Figure 45. Using the LP3985 Regulator

## Using References as Power Supplies (continued)

An input capacitance of 1 µF without any ESR requirement is required at the LP3985 input, while a 1-µF ceramic capacitor with an ESR requirement of 5 m $\Omega$  to 500 m $\Omega$  is required at the output. Careful interpretation and understanding of the capacitor specification is required to ensure correct device operation.

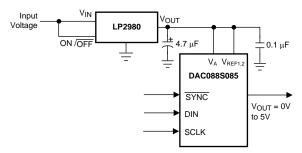

### 10.1.4 LP2980

The LP2980 is an ultra-low dropout regulator with a ±0.5% or ±1% accuracy over temperature, depending upon grade. It is available in 3 V, 3.3 V, and 5 V versions, among others.

Figure 46. Using the LP2980 Regulator