Order

Now

**CDCI6214** SNAS734D -JULY 2017-REVISED JUNE 2019

# CDCI6214 Ultra-Low Power Clock Generator With PCIe Support, Four Programmable Outputs and EEPROM

#### 1 Features

- One Configurable High Performance, Low-Power PLL With 4 Programmable Outputs

- RMS Jitter Performance

- Supports PCIe Gen1 with or without Spread Spectrum Clocking (SSC)

- Supports PCIe Gen2 / Gen3 / Gen4 without SSC

- Typical Power Consumption: 150 mW at 1.8 V<sup>(2)</sup>

- Universal Clock Input

- Differential AC-Coupled or LVCMOS: 1 MHz to 250 MHz

- Crystal: 8 MHz to 50 MHz

- Flexible Output Frequencies

- 44.1 kHz to 350 MHz

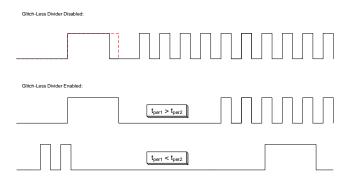

- Glitchless Output Divider Switching

- Four Individually Configurable Outputs

- LVCMOS, LVDS or HCSL

- Differential AC-Coupled With Programmable Swing (LVDS-, CML-, LVPECL-Compatible)

- Fully Integrated PLL, Configurable Loop Bandwidth: 100 kHz to 3 MHz

- Single or Mixed Supply Operation for Level Translation: 1.8 V, 2.5 V and 3.3 V

- Configurable GPIOs

- Status Signals

- Up to 4 Individual Output Enables

- Output Divider Synchronization

- **Flexible Configuration Options**

- I<sup>2</sup>C-Compatible Interface: Up to 400 kHz

- Integrated EEPROM With Two Pages and **External Select Pin**

- Only Supports 100  $\Omega$  Systems

- Industrial Temperature Range: -40°C to 85°C

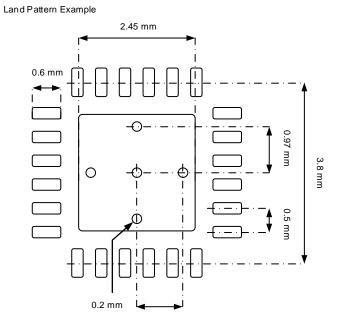

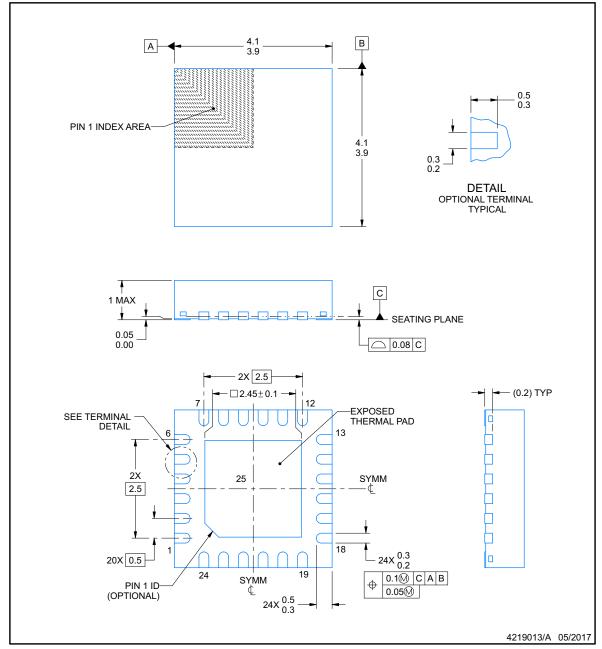

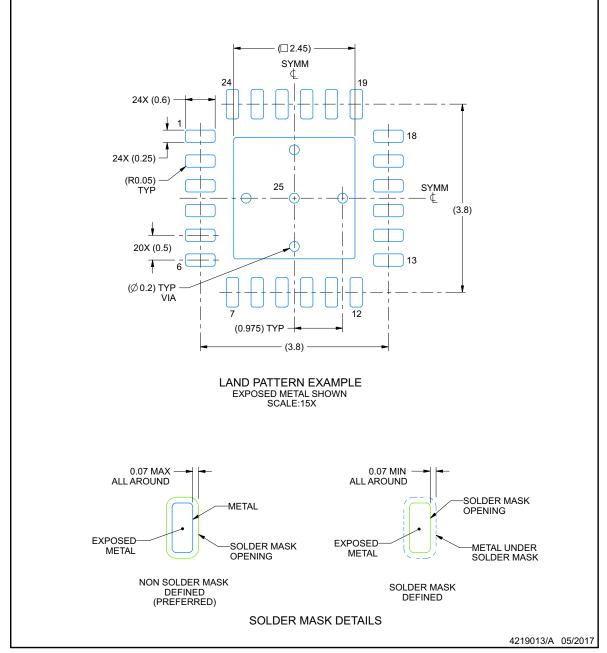

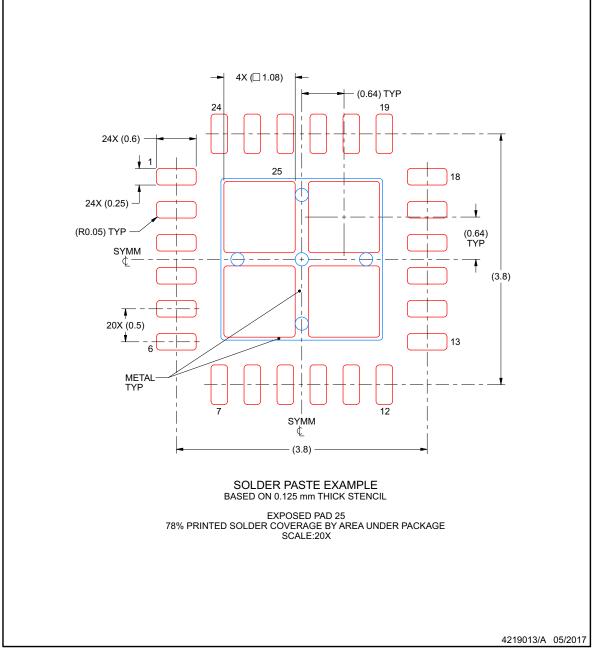

- Small Footprint: 24-Pin VQFN (4 mm x 4 mm)

#### 2 Applications

- PCIe Gen 1/2/3/4 clocking

- 1G / 10G Ethernet Switches, NIC, Accelerators

- Test & Measurement, Handheld Equipment

- **Multi-Function Printers**

- Broadcast Infrastructure

# 3 Description

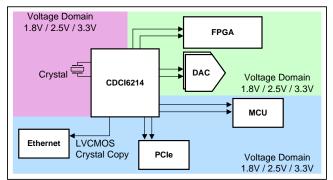

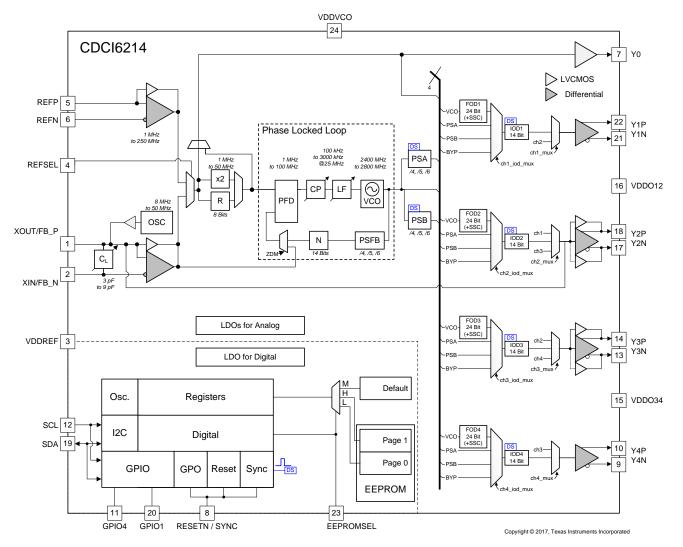

The CDCI6214 device is an ultra-low power clock generator. The device selects between two independent reference inputs to a phase-locked loop and generates up to four different frequencies on configurable differential output channels and also a copy of the reference clock on a LVCMOS output channel.

Each of the four output channels has a configurable integer / fractional output divider and a dedicated integer divider. Together with the output muxes, this allows up to five different frequencies. Clock distribution dividers are reset in a deterministic way for clean clock gating and glitch-less update capability. Flexible power-down options allow to optimize the device for lowest power consumption in active and standby operation. Typically four 156.25 MHz LVDS outputs consume 150 mW at 1.8V. Typical RMS jitter of 386 fs for 100 MHz HCSL output enhances system margin for PCIe applications.

The CDCI6214 is configured using internal registers that are accessed by an I<sup>2</sup>C-compatible serial interface and internal EEPROM.

The CDCI6214 enables high-performance clock trees from a single reference at ultra-low power with a small footprint. The factory- and user-programmable EEPROM make the CDCI6214 ideal as easy-to-use, instant-on clockina solution with low power consumption.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |

|-------------|-----------|-------------------|--|

| CDCI6214    | VQFN (24) | 4.00 mm × 4.00 mm |  |

- (1) For all available packages, see the orderable addendum at the end of the data sheet.

- (2) Four LVDS outputs, 156.25 MHz with crystal reference.

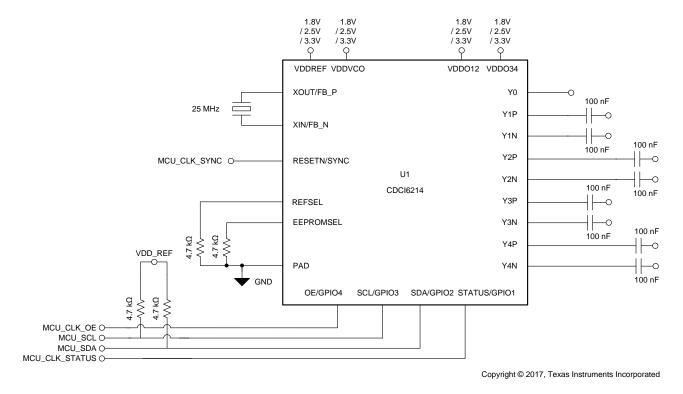

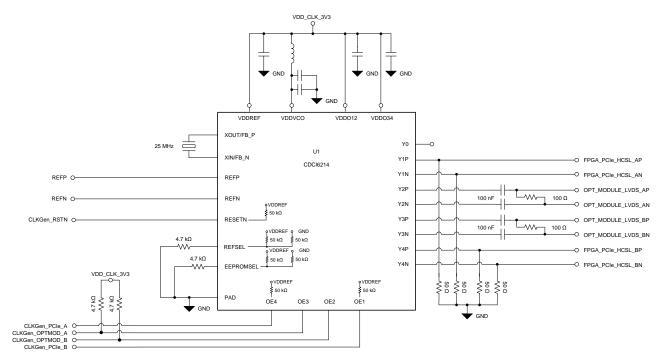

# Application Example CDCI6214

Copyright © 2017, Texas Instruments Incorporated

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# Table of Contents

| 1 | Feat | ures 1                                                                                       |

|---|------|----------------------------------------------------------------------------------------------|

| 2 | App  | lications 1                                                                                  |

| 3 | Des  | cription 1                                                                                   |

| 4 |      | sion History 2                                                                               |

| 5 | Pin  | Configuration and Functions 4                                                                |

| 6 |      | cifications5                                                                                 |

|   | 6.1  | Absolute Maximum Ratings 5                                                                   |

|   | 6.2  | ESD Ratings5                                                                                 |

|   | 6.3  | Recommended Operating Conditions 5                                                           |

|   | 6.4  | Thermal Information 5                                                                        |

|   | 6.5  | EEPROM Characteristics 6                                                                     |

|   | 6.6  | Reference Input, Single-Ended and Differential Mode Characteristics (REFP, REFN, FB_P, FB_N) |

|   | 6.7  | Reference Input, Crystal Mode Characteristics (XIN, XOUT)                                    |

|   | 6.8  | General-Purpose Input and Output Characteristics<br>(GPIO[4:1], SYNC/RESETN)                 |

|   | 6.9  | Triple Level Input Characteristics (EEPROMSEL,<br>REFSEL)                                    |

|   | 6.10 | Reference Mux Characteristics 7                                                              |

|   | 6.11 | Phase-Locked Loop Characteristics7                                                           |

|   | 6.12 | Closed-Loop Output Jitter Characteristics                                                    |

|   | 6.13 | PCIe Gen1 Spread Spectrum Generator 8                                                        |

|   | 6.14 | Output Mux Characteristics8                                                                  |

|   | 6.15 | LVCMOS Output Characteristics9                                                               |

|   | 6.16 | HCSL Output Characteristics9                                                                 |

|   | 6.17 | LVDS DC-Coupled Output Characteristics                                                       |

|   | 6.18 | Programmable Differential AC-Coupled Output<br>Characteristics                               |

|   | 6.19 | Output Skew and Delay Characteristics 10                                                     |

|   | 6.20 | Output Synchronization Characteristics 10                                                    |

|   | 6.21 | Timing Characteristics 11                                                                    |

|   | 6.22 | I <sup>2</sup> C-Compatible Serial Interface Characteristics<br>(SDA/GPIO2, SCL/GPIO3) 11    |

|    | 6.23 | Timing Requirements, I <sup>2</sup> C-Compatible Serial<br>Interface (SDA/GPIO2, SCL/GPIO3) | 11 |

|----|------|---------------------------------------------------------------------------------------------|----|

|    | 6.24 | Power Supply Characteristics                                                                |    |

|    | 6.25 |                                                                                             |    |

| 7  |      | meter Measurement Information                                                               |    |

| '  | 7.1  | Parameters                                                                                  |    |

| 8  |      | iled Description                                                                            |    |

| -  | 8.1  | Overview                                                                                    |    |

|    | 8.2  | Functional Block Diagram                                                                    |    |

|    | 8.3  | Feature Description                                                                         |    |

|    | 8.4  | Device Functional Modes                                                                     |    |

|    | 8.5  | Programming                                                                                 | 31 |

|    | 8.6  | Register Maps                                                                               |    |

| 9  | App  | lication and Implementation                                                                 | 92 |

| -  | 9.1  | Application Information                                                                     |    |

|    | 9.2  | Typical Applications                                                                        |    |

|    | 9.3  | Do's and Don'ts                                                                             |    |

|    | 9.4  | Initialization Setup                                                                        |    |

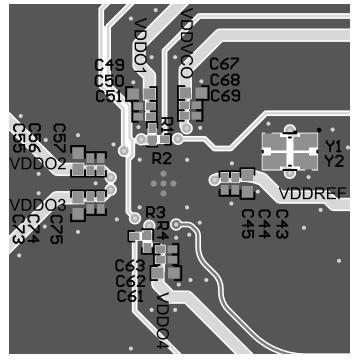

| 10 | Pow  | ver Supply Recommendations                                                                  |    |

| -  | 10.1 | Power-Up Sequence                                                                           |    |

|    | 10.2 | De-Coupling                                                                                 |    |

| 11 | Lave | out                                                                                         |    |

|    | 11.1 | Layout Guidelines                                                                           |    |

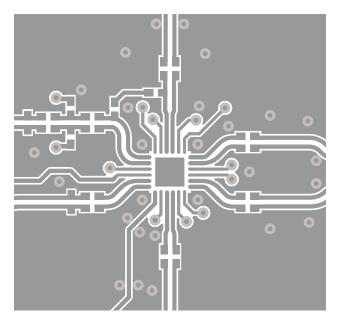

|    | 11.2 | Layout Examples                                                                             |    |

| 12 | Dev  | ice and Documentation Support                                                               |    |

|    | 12.1 | Device Support                                                                              |    |

|    | 12.2 | Receiving Notification of Documentation Updates                                             |    |

|    | 12.3 | Community Resources                                                                         |    |

|    | 12.4 | Trademarks                                                                                  |    |

|    | 12.5 | Electrostatic Discharge Caution                                                             |    |

|    | 12.6 | Glossary                                                                                    |    |

| 13 | -    | hanical, Packaging, and Orderable                                                           |    |

|    |      | mation                                                                                      | 99 |

|    |      |                                                                                             |    |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | nanges from Revision C (November 2018) to Revision D Page                                                 |    |  |

|----|-----------------------------------------------------------------------------------------------------------|----|--|

| •  | Added VDDREF and tablenote to the output supply voltage parameter in the Recommended Operating Conditions | 5  |  |

| •  | Added statement on chX_1p8vdet setting                                                                    | 21 |  |

| •  | Changed CDCI6214 - Pre-Configured EEPROM Page 0 graphic                                                   | 38 |  |

# Changes from Revision B (April 2018) to Revision C

| • | Corrected PCIe compliance statement                                                                                                                                                                                                                                            | . 1 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | Changed pin names for pins 1 and 2 from: XIN and XOUT to: XOUT/FB_P and XIN/FB_N.                                                                                                                                                                                              | . 4 |

| • | Changed descriptions for pins 1 and 2                                                                                                                                                                                                                                          | . 4 |

| • | Changed pin names for pins 1 and 2 in Absolute Maximum Ratings                                                                                                                                                                                                                 | . 5 |

| • | Changed pin names for pins 1 and 2 in <i>Reference Input, Single-Ended and Differential Mode Characteristics</i> (REFP, REFN, FB_P, FB_N)                                                                                                                                      | . 6 |

| • | Changed Input capacitance specification symbols in <i>Reference Input, Single-Ended and Differential Mode</i><br><i>Characteristics (REFP, REFN, FB_P, FB_N)</i> from: C <sub>IN_XOUT</sub> and C <sub>IN_XIN</sub> to: C <sub>IN_XOUT/FB_P</sub> and C <sub>IN_XIN/FB_P</sub> | . 6 |

STRUMENTS

EXAS

| • | Changed the test conditions for the fractional RMS Jitter specification in <i>Closed-Loop Output Jitter Characteristics</i> from: Y1 =122.88 MHz LVDS to: Y1 =133+1/3 MHz LVDS and the typical value from: 2 ps to: 3 ps | 8  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • | Changed name of the PCIe Spread Spectrum Generator table to PCIe Gen1 Spread Spectrum Generator                                                                                                                          | 8  |

| • | Changed pins 1 and 2 from: XIN and XOUT to: XOUT/FB_P and XIN/FB_N in the Functional Block Diagram                                                                                                                       | 18 |

| • | Changed pins 1 and 2 from: XIN and XOUT to: XOUT/FB_P and XIN/FB_N in the Reference Block graphic                                                                                                                        | 19 |

| • | Changed External (XIN) pin to: FB_P/N in the Phase-Locked Loop Circuit graphic                                                                                                                                           | 21 |

| • | Changed pins 1 and 2 from: XIN and XOUT to: XOUT/FB_P and XIN/FB_N in the CDCI6214 - Pre-Configured<br>EEPROM Page 0 and CDCI6214 - Pre-Configured EEPROM Page 1 graphics                                                | 38 |

| • | Changed pins XIN and XOUT to: XOUT/FB_P and XIN/FB_N in the Typical Applications schematics                                                                                                                              | 92 |

| • | Changed design parameter superscript to a subscript                                                                                                                                                                      | 93 |

# Changes from Revision A (October 2017) to Revision B

#### Page

| • | Changed pinout pins 5 and 6 from NC to REFP, REFN inputs                               | . 4 |

|---|----------------------------------------------------------------------------------------|-----|

| • | Changed supply voltage maximum from: 3.6 V to: 3.65 V                                  | . 5 |

| • | Removed Skew between HCSL maximum from the Output Skew and Delay Characteristics table | 10  |

#### Changes from Original (July 2017) to Revision A

| CI | Changes from Original (July 2017) to Revision A Pag         |    |

|----|-------------------------------------------------------------|----|

| •  | Changed device status from Advanced Info to Production Data | 1  |

| •  | Changed REFSEL pin description to reflext REFMUX control.   | 26 |

TEXAS INSTRUMENTS

www.ti.com

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN          |     | TYPE | DESCRIPTION                                                                                 |  |

|--------------|-----|------|---------------------------------------------------------------------------------------------|--|

| NAME         | NO. | TIPE | DESCRIPTION                                                                                 |  |

| XOUT/FB_P    | 1   | 10   | Crystal Driver Output / LVCMOS Input / Differential Positive Reference                      |  |

| XIN/FB_N     | 2   | Ι    | Crystal Input / Differential Negative Reference                                             |  |

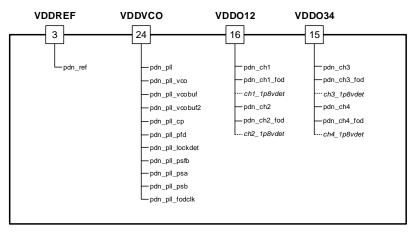

| VDDREF       | 3   | Р    | Power Supply Pin for Input Path, Digital and EEPROM                                         |  |

| REFSEL       | 4   | Ι    | Manual Reference Selection MUX for PLL, $R_{PU}$ = 50 k $\Omega$ , $R_{PD}$ = 50 k $\Omega$ |  |

| REFP         | 5   | Ι    | Differential Positive Reference                                                             |  |

| REFN         | 6   | Ι    | Differential Negative Reference                                                             |  |

| Y0           | 7   | 0    | Output 0 Pin                                                                                |  |

| RESETN/SYNC  | 8   | I    | Chip Reset. Alternatively, Output Divider Sync, $R_{PU} = 50 \text{ k}\Omega^{(1)}$         |  |

| Y4N          | 9   | 0    | Output 4 Negative Pin                                                                       |  |

| Y4P          | 10  | 0    | Output 4 Positive Pin                                                                       |  |

| OE/GPIO4     | 11  | Ю    | Global output enable (default) or programmable GPIO, $R_{PU}$ = 50 k $\Omega^{(1)}$         |  |

| SCL/GPIO3    | 12  | Ю    | Serial interface clock (default) or programmable GPIO                                       |  |

| Y3N          | 13  | 0    | Output 3 Negative Pin                                                                       |  |

| Y3P          | 14  | 0    | Output 3 Positive Pin                                                                       |  |

| VDDO34       | 15  | Р    | Power Supply for Outputs 3 and 4                                                            |  |

| VDDO12       | 16  | Р    | Power Supply for Outputs 1 and 2                                                            |  |

| Y2N          | 17  | 0    | Output 2 Negative Pin                                                                       |  |

| Y2P          | 18  | 0    | Output 2 Positive Pin                                                                       |  |

| SDA/GPIO2    | 19  | Ю    | Serial interface data (default) or programmable GPIO                                        |  |

| STATUS/GPIO1 | 20  | Ю    | Status (default) or programmable GPIO, $R_{PU} = 50 \text{ k}\Omega^{(1)}$                  |  |

| Y1N          | 21  | 0    | Output 1 Negative Pin                                                                       |  |

| Y1P          | 22  | 0    | Output 1 Positive Pin                                                                       |  |

| EEPROMSEL    | 23  | Ι    | EEPROM Page Mode Select, $R_{PU}$ = 50 k $\Omega$ , $R_{PD}$ = 50 k $\Omega^{(1)}$          |  |

| VDDVCO       | 24  | Р    | Power Supply Pin for VCO / PLL                                                              |  |

| GND          | 25  | G    | Ground, Thermal Pad                                                                         |  |

(1)  $R_{PU}$  is an internal pullup resistor.  $R_{PD}$  is an internal pulldown resistor.

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                              |                      | MIN  | MAX             | UNIT |

|------------------------------------------------------------------------------|----------------------|------|-----------------|------|

| VDDREF, VDDVCO, VDDO12, VDDO34                                               | Supply voltage       | -0.3 | 3.65            | V    |

| XIN/FB_P, XOUT/FB_N, REFP, REFN                                              | Input voltage        | -0.3 | VDDREF +<br>0.3 | V    |

| STATUS/GPIO1, SDA/GPIO2, SCL/GPIO3, OE/GPIO4, REFSEL, EEPROMSEL, RESETN/SYNC | Input voltage        | -0.3 | VDDREF +<br>0.3 | V    |

| Y0, Y1P, Y1N, Y2P, Y2N, Y3P, Y3N, Y4P, Y4N                                   | Output voltage       | -0.3 | VDDO_x +<br>0.3 | V    |

| STATUS/GPIO1, SDA/GPIO2, SCL/GPIO3, OE/GPIO4                                 | Output voltage       | -0.3 | VDDREF +<br>0.3 | V    |

| TJ                                                                           | Junction temperature |      | 125             | °C   |

| T <sub>stg</sub>                                                             | Storage temperature  |      | 150             | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | 2000  |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | 500   | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                    | MIN   | NOM MAX | UNIT |

|-------------------|------------------------------------|-------|---------|------|

| VDDREF,<br>VDDVCO | Core supply voltage <sup>(1)</sup> | 1.71  | 3.465   | V    |

| VDDO1             | Output supply voltage              | 1.71  | 3.465   | V    |

| VDDO2             | Output supply voltage              | 1.71  | 3.465   | V    |

| VDDO3             | Output supply voltage              | 1.71  | 3.465   | V    |

| VDDO4             | Output supply voltage              | 1.71  | 3.465   | V    |

| T <sub>A</sub>    | Ambient temperature                | -40°C | 85      | °C   |

(1) VDDREF and VDDVCO must be powered from the same supply voltage.

### 6.4 Thermal Information

|                       |                                              | CDCI6214   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGE (VQFN) | UNIT |

|                       |                                              | 24 PINS    |      |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 39.5       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 29.5       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 16.9       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.6        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.4        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 16.8       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

SNAS734D-JULY 2017-REVISED JUNE 2019

www.ti.com

#### 6.5 **EEPROM** Characteristics

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A = -40^{\circ}C$  to 85°C

|                    | PARAMETER                 | TEST CONDITIONS | MIN | TYP MAX | UNIT   |

|--------------------|---------------------------|-----------------|-----|---------|--------|

| n <sub>EEcyc</sub> | EEPROM programming cycles | each word       | 10  | 10,000  | cycles |

| t <sub>EEret</sub> | EEPROM data retention     |                 | 10  |         | years  |

# 6.6 Reference Input, Single-Ended and Differential Mode Characteristics (REFP, REFN, FB\_P, FB\_N)

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and T\_A = -40^{\circ}C to 85°C

|                           | PARAMETER                                      | TEST CONDITIONS                                                   | MIN             | TYP MAX         | UNIT |

|---------------------------|------------------------------------------------|-------------------------------------------------------------------|-----------------|-----------------|------|

| f <sub>IN_Ref</sub>       | Reference frequency                            |                                                                   | 1               | 250             | MHz  |

| V <sub>IH</sub>           | Input high voltage                             | LVCMOS input buffer                                               | 0.8 ×<br>VDDREF |                 | V    |

| V <sub>IL</sub>           | Input low voltage                              | LVCMOS input buffer                                               |                 | 0.2 ×<br>VDDREF | V    |

| V <sub>IN_DIFF</sub>      | Differential input voltage swing, peak-to-peak | VDDREF = 2.5 V or 3.3 V, AC-<br>coupled differential input buffer | 0.5             | 1.6             | V    |

| V <sub>IN_DIFF</sub>      | Differential input voltage swing, peak-to-peak | VDDREF = 1.8 V, AC-coupled differential input buffer              | 0.5             | 1.0             | V    |

| dV <sub>IN</sub> /dT      | Input slew rate                                | 20% - 80%                                                         | 3               |                 | V/ns |

| IDC                       | Input duty cycle                               |                                                                   | 40%             | 60%             |      |

| C <sub>IN_XOUT/FB_P</sub> | Input capacitance                              | No xtal active, on-chip load disabled, at 25°C                    |                 | 7               | pF   |

| C <sub>IN_XIN/FB_P</sub>  | Input capacitance                              | No xtal active, on-chip load disabled, at 25°C                    |                 | 5               | pF   |

| C <sub>IN_REF</sub>       | Input capacitance                              | at 25°C                                                           |                 | 5               | pF   |

# 6.7 Reference Input, Crystal Mode Characteristics (XIN, XOUT)

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A = -40^{\circ}C$  to 85°C

|                         | PARAMETER                            | TEST CONDITIONS                                                | MIN | TYP | MAX | UNIT |

|-------------------------|--------------------------------------|----------------------------------------------------------------|-----|-----|-----|------|

| f <sub>IN_Xtal</sub>    | Crystal frequency                    | Fundamental mode                                               | 8   |     | 50  | MHz  |

| Z <sub>ESR</sub>        | Crystal equivalent series resistance | A supported crystal is within                                  | 30  |     | 100 | Ω    |

| CL                      | Crystal load capacitance             | Using on-chip load capacitance. A supported crystal is within. | 5   |     | 8   | pF   |

| P <sub>XTAL</sub>       | Crystal tolerated drive power        | A supported crystal tolerates up to                            | 100 |     |     | uW   |

| C <sub>XIN_LOAD</sub>   | On-Chip load capacitance             | Programmable in typical 200-<br>fF steps at room temp          | 3   |     | 9.1 | pF   |

| DNL <sub>XIN_LOAD</sub> | Differential non-linearity           | at room temp                                                   |     | 200 |     | fF   |

# 6.8 General-Purpose Input and Output Characteristics (GPIO[4:1], SYNC/RESETN)

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V  $\pm$ 5%, 2.5 V  $\pm$ 5%, 3.3 V  $\pm$ 5% and T<sub>A</sub> = -40°C to 85°C

|                      | PARAMETER                | TEST CONDITIONS          | MIN             | TYP    | MAX             | UNIT |

|----------------------|--------------------------|--------------------------|-----------------|--------|-----------------|------|

| V <sub>IH</sub>      | Input high voltage       |                          | 0.8 ×<br>VDDREF |        |                 | V    |

| V <sub>IL</sub>      | Input low voltage        |                          |                 |        | 0.2 ×<br>VDDREF | V    |

| I <sub>IH</sub>      | Input high level current | VIH = VDDREF             |                 | -0.02  |                 | μA   |

| IIH                  | Input high level current | VIH = VDDREF, Pin 12, 19 |                 | 0.004  |                 | μA   |

| IIL                  | Input low level current  | VIL = GND                |                 | -50    |                 | μA   |

| IIL                  | Input low level current  | VIL = GND, Pin 12, 19    |                 | -0.004 |                 | μA   |

| dV <sub>IN</sub> /dT | Input slew rate          | 20% - 80%                | 0.5             |        |                 | V/ns |

| C <sub>IN_GPIO</sub> | Input Capacitance        |                          |                 |        | 10              | pF   |

# General-Purpose Input and Output Characteristics (GPIO[4:1], SYNC/RESETN) (continued)

|--|

|                       | PARAMETER           | TEST CONDITIONS      | MIN             | TYP MA       | X UNIT |

|-----------------------|---------------------|----------------------|-----------------|--------------|--------|

| V <sub>OH</sub>       | Output high voltage | only capacitive load | 0.8 ×<br>VDDREF |              | V      |

| V <sub>OL</sub>       | Output low voltage  | only capacitive load |                 | 0.2<br>VDDRE | V      |

| dV <sub>OUT</sub> /dT | Output slew rate    | 20% - 80%, at 10pF   |                 | 0.3          | V/ns   |

| R <sub>PU</sub>       | Pullup resistance   | Pin 11, 20           |                 | 77           | kΩ     |

# 6.9 Triple Level Input Characteristics (EEPROMSEL, REFSEL)

VDDVCO,VDDO12, VDDO34, VDDREF = 1.8V  $\pm$ 5%, 2.5V  $\pm$ 5%, 3.3V  $\pm$ 5% and T<sub>A</sub> = -40°C to 85°C

|                     | PARAMETER                | TEST CONDITIONS | MIN              | TYP             | MAX              | UNIT |

|---------------------|--------------------------|-----------------|------------------|-----------------|------------------|------|

| V <sub>IH</sub>     | Input high voltage       |                 | 0.8 ×<br>VDDREF  |                 |                  | V    |

| V <sub>IM</sub>     | Input mid voltage        |                 | 0.41 ×<br>VDDREF | 0.5 ×<br>VDDREF | 0.58 ×<br>VDDREF | V    |

| V <sub>IL</sub>     | Input low voltage        |                 |                  |                 | 0.2 ×<br>VDDREF  | V    |

| I <sub>IH</sub>     | Input high level current | VIH = VDDREF    |                  | 40              |                  | μA   |

| I <sub>IM</sub>     | Input mid level current  | VIH = VDDREF/2  |                  | -1              |                  | μA   |

| IIL                 | Input low level current  | VIL = GND       |                  | -40             |                  | μA   |

| t <sub>RIN</sub>    | input slew rate          | 10% - 90%       | 50               |                 |                  | ns   |

| C <sub>IN_TRI</sub> |                          |                 |                  |                 | 10               | pF   |

| R <sub>PDPU</sub>   |                          |                 |                  | 64              |                  | kΩ   |

# 6.10 Reference Mux Characteristics<sup>(1)</sup>

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V  $\pm$ 5%, 2.5 V  $\pm$ 5%, 3.3 V  $\pm$ 5% and T<sub>A</sub> = -40°C to 85°C

|                      | PARAMETER               | TEST CONDITIONS                           | MIN    | ТҮР | MAX   | UNIT |

|----------------------|-------------------------|-------------------------------------------|--------|-----|-------|------|

|                      |                         | TEST CONDITIONS                           | IVIIIN |     | INIAA | UNIT |

| L <sub>REF_MUX</sub> | Reference mux isolation | XIN = Crystal 25 MHz, REF = 27<br>MHz     |        | 89  |       | dBc  |

| L <sub>REF_MUX</sub> | Reference mux isolation | XIN = Crystal 25 MHz, REF =<br>24.576 MHz |        | 78  |       | dBc  |

(1) Mux isolation is defined as the attenuation relative to the carrier base harmonic as a positive dBc number.

# 6.11 Phase-Locked Loop Characteristics

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A = -40^{\circ}$ C to 85°C

|                      | PARAMETER                                          | TEST CONDITIONS            | MIN  | TYP | MAX  | UNIT  |

|----------------------|----------------------------------------------------|----------------------------|------|-----|------|-------|

| f <sub>PFD</sub>     | Phase detector frequency                           |                            | 1    |     | 100  | MHz   |

| f <sub>VCO</sub>     | Voltage-controlled oscillator<br>frequency         |                            | 2400 |     | 2800 | MHz   |

| f <sub>BW</sub>      | Configurable closed-loop PLL bandwidth             | REF = 25 MHz               | 100  |     | 3000 | kHz   |

| f <sub>CLKDIST</sub> | Clock distribution frequency                       |                            | 400  |     | 700  | MHz   |

| K <sub>VCO</sub>     | Voltage-controlled oscillator gain                 | f <sub>VCO</sub> = 2.4 GHz |      | 62  |      | MHz/V |

| K <sub>VCO</sub>     | Voltage-controlled oscillator gain                 | f <sub>VCO</sub> = 2.5 GHz |      | 62  |      | MHz/V |

| K <sub>VCO</sub>     | Voltage-controlled oscillator gain                 | f <sub>VCO</sub> = 2.8 GHz |      | 92  |      | MHz/V |

| $ \Delta T_{CL} $    | Allowable temperature drift for<br>continuous lock | dT/dt ≤ 20 K / min         |      |     | 125  | °C    |

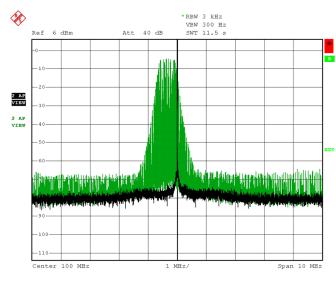

# 6.12 Closed-Loop Output Jitter Characteristics

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V  $\pm$ 5%, 2.5 V  $\pm$ 5%, 3.3 V  $\pm$ 5% and T<sub>A</sub> = -40°C to 85°C

| PARAMETER                           | TEST CONDITIONS                                                                                                                                   | MIN | TYP | MAX | UNIT |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

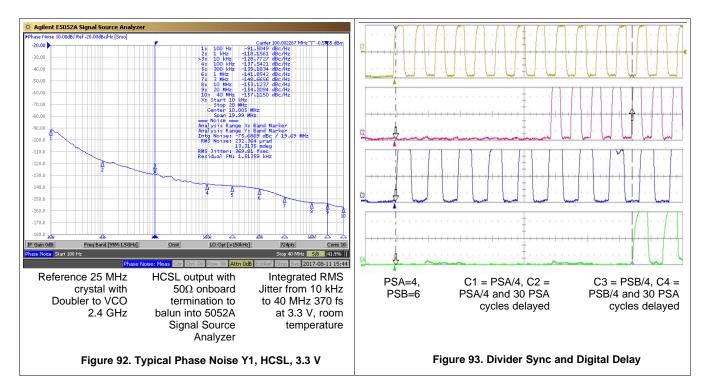

|                                     | int. Range from 10 kHz to 20 MHz ,<br>XIN = Crystal 25 MHz, Integer<br>Output Divider, Yx = 156.25 MHz<br>LVDS                                    |     | 500 | 750 | fs   |

|                                     | int. Range from 10 kHz to 20 MHz ,<br>XIN = Crystal 25 MHz, Integer<br>Output Divider, Yx = 100 MHz HCSL                                          |     | 386 | 800 | fs   |

| t <sub>RJ_CL</sub> RMS phase jitter | PCIe Gen 3/4 Common Clock<br>transfer functions applied, XIN =<br>Crystal 25 MHz, Integer Output<br>Divider, Yx = 100 MHz HCSL                    |     |     | 500 | fs   |

|                                     | int. Range from 10 kHz to 20 MHz ,<br>XIN = Crystal 25 MHz, VCO = 2500<br>MHz, Fractional Output Divider , Y1<br>=133+1/3 MHz LVDS <sup>(1)</sup> |     | 3   |     | ps   |

(1) Integrated RMS jitter at other frequencies using fractional output divider may vary. Contact TI for further assistance.

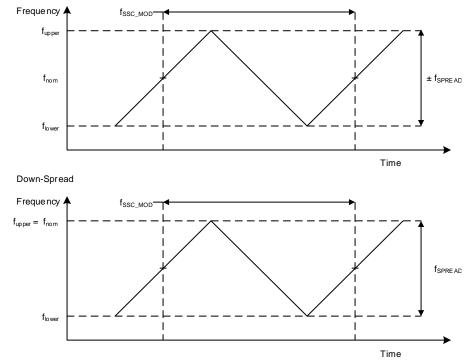

#### 6.13 PCIe Gen1 Spread Spectrum Generator

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V  $\pm$ 5%, 2.5 V  $\pm$ 5%, 3.3 V  $\pm$ 5% and T<sub>A</sub> = -40°C to 85°C, f<sub>VCO</sub> = 2.4 GHz, ch[4:1]\_iod\_mux = 2, ch[4:1]\_iod = 3, ch[4:1]\_ssc\_counter = 4, ch[4:1]\_ssc\_fmod = 1, ch[4:1]\_ssc\_type = 1, ch[4:1]\_ssc\_spread = 0

|                                     | PARAMETER     | TEST CONDITIONS | MIN | TYP   | MAX | UNIT |

|-------------------------------------|---------------|-----------------|-----|-------|-----|------|

| f <sub>SSC</sub>                    | SSC deviation |                 |     | 31.25 |     | kHz  |

| t <sub>SSC_FREQ_</sub><br>DEVIATION | SSC deviation |                 |     | -0.5% |     |      |

# 6.14 Output Mux Characteristics<sup>(1)</sup>

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V  $\pm$ 5%, 2.5 V  $\pm$ 5%, 3.3 V  $\pm$ 5% and T<sub>A</sub> = -40°C to 85°C

|                      | PARAMETER            | TEST CONDITIONS                                                                                              | MIN | TYP | MAX | UNIT |

|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| L <sub>OUT_MUX</sub> | Output mux isolation | REF = 27 MHz, XIN = 25 MHz, VCO<br>= 2500 MHz, PSFB = 4, Y_ODD =<br>312.5 MHz, Y_EVEN = 208.3 MHz,<br>LVPECL |     | 65  |     | dBc  |

| L <sub>OUT_MUX</sub> | Output mux isolation | REF = 27 MHz, XIN = 25 MHz, VCO<br>= 2500 MHz, PSFB = 4, Y_ODD =<br>312.5 MHz, Y_EVEN = 250 MHz,<br>LVPECL   |     | 63  |     | dBc  |

| L <sub>OUT_MUX</sub> | Output mux isolation | REF = 27 MHz, XIN = 25 MHz, VCO<br>= 2500 MHz, PSFB = 4, Y_ODD =<br>312.5 MHz, Y_EVEN = 89.3 MHz,<br>LVPECL  |     | 72  |     | dBc  |

| L <sub>OUT_MUX</sub> | Output mux isolation | REF = 27 MHz, XIN = 25 MHz, VCO<br>= 2500 MHz, PSFB = 4, IODs =<br>312.5 MHz, Yx=BYPASS (XIN),<br>LVPECL     |     | 64  |     | dBc  |

| L <sub>OUT_MUX</sub> | Output mux isolation | REF = 27 MHz, XIN = 25 MHz, VCO<br>= 2500 MHz, PSFB = 4, Y_ODD =<br>100 MHz, Y_EVEN = 266.6 MHz,<br>LVPECL   |     | 57  |     | dBc  |

(1) Mux isolation is defined as the attenuation relative to the carrier base harmonic as a positive dBc number.

# 6.15 LVCMOS Output Characteristics

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A$  = –40°C to 85°C

|                            | PARAMETER                           | TEST CONDITIONS                                                 | MIN             | TYP MAX         | UNIT   |

|----------------------------|-------------------------------------|-----------------------------------------------------------------|-----------------|-----------------|--------|

| f <sub>O_LVCMOS</sub>      | Output frequency                    | VDDO_x = 2.5 V or 3.3 V, normal drive                           | 0.1             | 350             | MHz    |

| fo_LVCMOS                  | Output frequency                    | $VDDO_x = 1.8 V$ , normal drive                                 | 0.1             | 250             | MHz    |

| V <sub>OH_LVCMO</sub><br>s | Output high voltage                 | Normal mode, only capacitive load                               | 0.8 ×<br>VDDREF |                 | V      |

| V <sub>OL_LVCMO</sub><br>s | Output low voltage                  | Normal mode, only capacitive load                               |                 | 0.2 ×<br>VDDREF | V      |

| V <sub>OH_LVCMO</sub><br>s | Output high voltage                 | Slow mode, only capacitive load                                 | 0.7 ×<br>VDDREF |                 | V      |

| V <sub>OL_LVCMO</sub><br>s | Output low voltage                  | Slow mode, only capacitive load                                 |                 | 0.3 ×<br>VDDREF | V      |

| R <sub>ON_LVCMO</sub><br>s | Output impedance                    | Normal mode                                                     |                 | 28              | Ω      |

| R <sub>ON_LVCMO</sub><br>s | Output impedance                    | Weak mode                                                       |                 | 80              | Ω      |

| L <sub>LVCMOS_10</sub>     | Phase noise floor, single side band | f <sub>CARRIER</sub> = 100 MHz, f <sub>OFFSET</sub> = 10<br>MHz |                 | -148            | dBc/Hz |

### 6.16 HCSL Output Characteristics

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A$  = –40°C to 85°C

|                        | PARAMETER                                 | TEST CONDITIONS                                                                           | MIN | TYP  | MAX  | UNIT   |

|------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------|-----|------|------|--------|

| f <sub>O_HCSL</sub>    | Output frequency                          |                                                                                           | 0.1 |      | 350  | MHz    |

| V <sub>CM_HCSL</sub>   | Output common mode                        |                                                                                           | 0.2 | 0.34 | 0.55 | V      |

| V <sub>OD</sub>        | Differential output voltage               | f <sub>O_HCSL</sub> = 100 MHz                                                             | 0.4 |      | 1.0  | V      |

| V <sub>SS</sub>        | Differential output voltage, peak to peak | f <sub>O_HCSL</sub> = 100 MHz                                                             | 0.8 |      | 2.0  | Vpp    |

| V <sub>CROSS</sub>     | Absolute crossing point                   | $R_p$ = 49.9 $\Omega$ ±5%, $f_{O_HCSL}$ = 100 MHz                                         | 250 |      | 550  | mV     |

| $\Delta V_{CROSS}$     | Relative crossing point variation         | w.r.t to average crossing<br>point, f <sub>O_HCSL</sub> = 100 MHz                         |     | 100  |      | mV     |

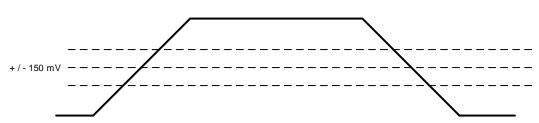

| dV/dt                  | Slew rate for rising and falling edge     | Differential, at V <sub>CROSS</sub> ±150 mV, $f_{O_{-}HCSL} = 100 \text{ MHz}^{(1)}$      | 1   |      | 4    | V/ns   |

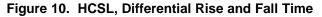

| ∆dV/dt                 | Slew rate matching                        | Single-ended, at V <sub>CROSS</sub> $\pm$ 75 mV, $f_{O_{-}HCSL}$ = 100 MHz <sup>(1)</sup> |     |      | 20%  |        |

| ODC                    | Output duty cycle                         | Not in PLL bypass mode                                                                    | 45% |      | 55%  |        |

| R <sub>P</sub>         | Parallel termination                      | $R_p = 49.9 \Omega \pm 5\%$ required                                                      | 45  |      | 55   | Ω      |

| L <sub>HCSL_100M</sub> | Phase noise floor, single side band       | f <sub>CARRIER</sub> = 100 MHz, f <sub>OFFSET</sub> = 10<br>MHz                           |     | -152 |      | dBc/Hz |

(1) PCIe test load slew rate

# 6.17 LVDS DC-Coupled Output Characteristics

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V  $\pm$ 5%, 2.5 V  $\pm$ 5%, 3.3 V  $\pm$ 5% and T<sub>A</sub> = -40°C to 85°C

|                       | PARAMETER                   | TEST CONDITIONS                                   | MIN   | TYP | MAX   | UNIT |

|-----------------------|-----------------------------|---------------------------------------------------|-------|-----|-------|------|

| f <sub>O_PRG_AC</sub> | Output frequency            |                                                   | 0.1   |     | 350   | MHz  |

| V <sub>CM</sub>       | Output common mode          | VDDO_X = 2.5 V, 3.3 V,<br>chx_lvds_cmtrim_inc = 2 | 1.125 | 1.2 | 1.375 | V    |

| V <sub>CM</sub>       | Output common mode          | VDDO_X = 1.8 V,<br>chx_lvds_cmtrim_inc = 2        | 0.8   | 0.9 | 1     | V    |

| V <sub>OD</sub>       | Differential output voltage | LVDS                                              | 0.25  | 0.3 | 0.45  | V    |

| t <sub>RF</sub>       | Output rise/fall times      | LVDS (20% to 80%)                                 |       | 675 |       | ps   |

Copyright © 2017–2019, Texas Instruments Incorporated

# LVDS DC-Coupled Output Characteristics (continued)

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V  $\pm$ 5%, 2.5 V  $\pm$ 5%, 3.3 V  $\pm$ 5% and T<sub>A</sub> = -40°C to 85°C

|                        | PARAMETER                           | TEST CONDITIONS                                               | MIN | TYP  | MAX | UNIT   |

|------------------------|-------------------------------------|---------------------------------------------------------------|-----|------|-----|--------|

| ODC                    | Output duty cycle                   | Not in PLL bypass mode                                        | 45% |      | 55% |        |

| L <sub>LVDS_DC_1</sub> | Phase noise floor, single side band | f <sub>CARRIER</sub> = 100MHz, f <sub>OFFSET</sub> =<br>10MHz |     | -152 |     | dBc/Hz |

# 6.18 Programmable Differential AC-Coupled Output Characteristics

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A = -40^{\circ}C$  to 85°C and AC-coupled outputs

|                         | PARAMETER                           | TEST CONDITIONS                                              | MIN | ТҮР  | MAX | UNIT   |

|-------------------------|-------------------------------------|--------------------------------------------------------------|-----|------|-----|--------|

| f <sub>O_PRG_AC</sub>   | Output frequency                    |                                                              | 0.1 |      | 350 | MHz    |

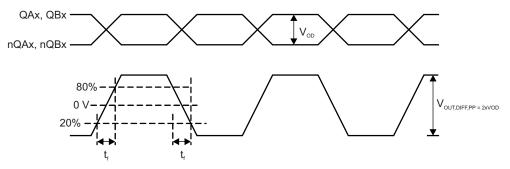

| V <sub>OD</sub>         | Differential output voltage         | LVDS-like                                                    |     | 0.45 |     | V      |

| V <sub>OD</sub>         | Differential output voltage         | CML-like                                                     |     | 0.8  |     | V      |

| V <sub>OD</sub>         | Differential output voltage         | LVPECL-like                                                  |     | 0.9  |     | V      |

| t <sub>RF</sub>         | Output rise/fall times              | LVDS-like (20% to 80%)                                       |     | 675  |     | ps     |

| t <sub>RF</sub>         | Output rise/fall times              | CML-like (20% to 80%)                                        |     | 520  |     | ps     |

| t <sub>RF</sub>         | Output rise/fall times              | LVPECL-like (20% to 80%)                                     |     | 500  |     | ps     |

| ODC                     | Output duty cycle                   | Not in PLL bypass mode                                       | 45% |      | 55% |        |

| L <sub>DIFF_AC_10</sub> | Phase noise floor, single side band | $f_{CARRIER} = 100 \text{ MHz}, f_{OFFSET} = 10 \text{ MHz}$ |     | -152 |     | dBc/Hz |

## 6.19 Output Skew and Delay Characteristics

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A = -40^{\circ}C$  to 85°C

|                                | PARAMETER                           | TEST CONDITIONS                                                                                                                                                                                                                                 | MIN  | ТҮР | MAX | UNIT |

|--------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| t <sub>SK_HCSL</sub>           | Skew between HCSL                   | Y[4:1] = HCSL, f <sub>OY[4:1]</sub> = 100 MHz                                                                                                                                                                                                   |      | 140 |     | ps   |

| t <sub>SK_DIFFAC</sub>         | Skew between progr. differential AC | $Y[4:1] = programmable output swing, f_{OY[4:1]} = 100 MHz$                                                                                                                                                                                     |      | 150 |     | ps   |

| t <sub>SK_LVCMOS</sub>         | Skew between LVCMOS                 | Y[4:1] = LVCMOS, f <sub>OY[4:1]</sub> = 100<br>MHz                                                                                                                                                                                              |      | 100 |     | ps   |

| t <sub>SK_LVCMOS</sub><br>_BYP | Skew between LVCMOS to Bypass       | Y[4:0] = LVCMOS, f <sub>OY[4:0]</sub> = 100<br>MHz                                                                                                                                                                                              |      | 3   |     | ns   |

| t <sub>PD_ZDM</sub>            | Propagation delay                   | $\begin{array}{l} REF = 67 \; MHz, \; VCO = 2680 \; MHz, \\ PSFB = 4, \; PSA_{V\_ODD} = 4, \\ PSB_{V\_EVEN} = 4, \; IOD_{V\_ODD} = 10, \\ IOD_{V\_EVEN} = 10, \; Y_{P\_ODD} = Y_{N\_ODD} \\ = IOD, \; in \; ext. \; ZDM, \; LVCMOS \end{array}$ | -600 |     | 600 | ps   |

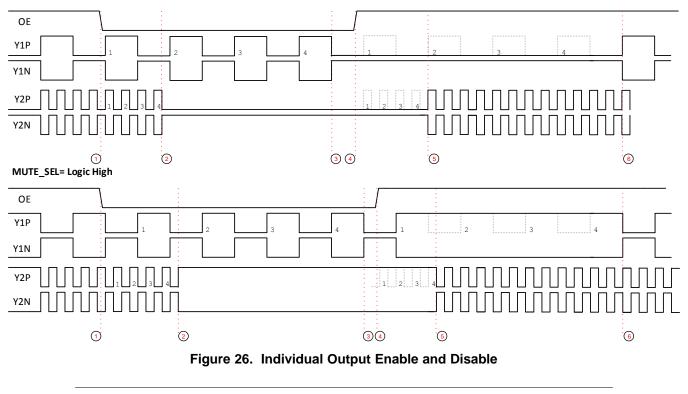

# 6.20 Output Synchronization Characteristics

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A = -40^{\circ}$ C to 85°C

|                       | PARAMETER                                    | TEST CONDITIONS                                                        | MIN | TYP | MAX | UNIT |

|-----------------------|----------------------------------------------|------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>SU_SYNC</sub>  | Setup time SYNC pulse                        | With respect to PLL reference rising edge at 100 MHz with $R = 1$      | 3   |     |     | ns   |

| t <sub>H_SYNC</sub>   | Hold time SYNC pulse                         | With respect to PLL reference rising edge at 100 MHz with $R = 1$      |     |     | 3   | ns   |

| t <sub>PWH_SYNC</sub> | High pulse width for SYNC                    | With R = 1, at least 2 PFD periods<br>+ 24 feedback pre-scaler periods | 60  |     |     | ns   |

| t <sub>PWL_SYNC</sub> | Low pulse width for SYNC                     | With R = 1, at least 1 PFD period                                      | 6   |     |     | ns   |

| t <sub>EN</sub>       | Individual output enable time <sup>(1)</sup> | Tri-state to first rising edge, f <sub>Y[4:1]</sub> < 200 MHz          |     | 4   |     | nCK  |

(1) Output clock cycles of respective output channel. Global output enable handled by digital logic, additional propagation will be added.

# **Output Synchronization Characteristics (continued)**

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V  $\pm$ 5%, 2.5 V  $\pm$ 5%, 3.3 V  $\pm$ 5% and T<sub>A</sub> = -40°C to 85°C

|                  | PARAMETER                                     | TEST CONDITIONS                                               | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------------------------|---------------------------------------------------------------|-----|-----|-----|------|

| t <sub>DIS</sub> | Individual output disable time <sup>(1)</sup> | Last falling edge to tri-state, f <sub>Y[4:1]</sub> < 200 MHz |     | 4   |     | nCK  |

# 6.21 Timing Characteristics

VDDVCO,VDDO12,VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A = -40^{\circ}C$  to 85°C

|                   | PARAMETER           | TEST CONDITIONS                                               | MIN | TYP MAX | UNIT |

|-------------------|---------------------|---------------------------------------------------------------|-----|---------|------|

| t <sub>INIT</sub> | Initialization time | Initialization time from POR to device releasing PLL outputs. |     | 5       | ms   |

| t <sub>VDD</sub>  | Power supply ramp   | Timing requirement for any VDD pin while RESETN = LOW         | 50  | 2000    | μs   |

# 6.22 I<sup>2</sup>C-Compatible Serial Interface Characteristics (SDA/GPIO2, SCL/GPIO3)

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A = -40^{\circ}$ C to 85°C

|                  | PARAMETER                        | TEST CONDITIONS                                | MIN             | TYP MAX         | UNIT |

|------------------|----------------------------------|------------------------------------------------|-----------------|-----------------|------|

| VIH              | Input voltage, logic high        |                                                | 0.7 ×<br>VDDREF |                 | V    |

| V <sub>IL</sub>  | Input voltage, logic low         |                                                |                 | 0.3 ×<br>VDDREF | V    |

| V <sub>HYS</sub> | Input Schmitt trigger hysteresis | VDDREF = 3.3 V, f <sub>SCL</sub> = 400 kHz     | 156             |                 | mV   |

| V <sub>HYS</sub> | Input Schmitt trigger hysteresis | VDDREF = 2.5 V, $f_{SCL}$ = 400 kHz            | 118             |                 | mV   |

| V <sub>HYS</sub> | Input Schmitt trigger hysteresis | VDDREF = 1.8 V, f <sub>SCL</sub> = 400 kHz     | 85              |                 | mV   |

| I <sub>IH</sub>  | Input leakage current            | VDDREF = 0.17 V3.12 V                          | -10             | 10              | μA   |

| V <sub>OL</sub>  | Low-level output voltage         | At 3-mA sink current, VDDREF = $3.3$<br>V - 5% |                 | 0.4             | V    |

| V <sub>OL</sub>  | Low-level output voltage         | At 3-mA sink current, VDDREF = $2.5$<br>V - 5% |                 | 0.4             | V    |

| V <sub>OL</sub>  | Low-level output voltage         | At 2-mA sink current, VDDREF = $1.8$<br>V - 5% |                 | 0.342           | V    |

| I <sub>OL</sub>  | Low-level output current         | V <sub>OL</sub> = 0.4 V                        | 3               |                 | mA   |

| C <sub>IN</sub>  | Input capacitance                |                                                |                 | 10              | pF   |

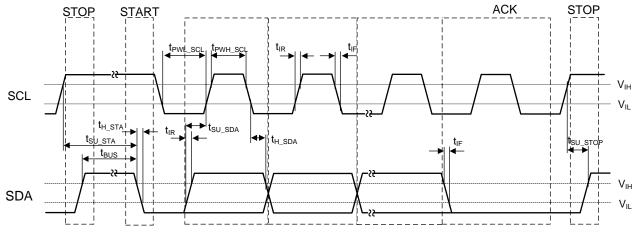

### 6.23 Timing Requirements, I<sup>2</sup>C-Compatible Serial Interface (SDA/GPIO2, SCL/GPIO3)

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A = -40^{\circ}$ C to 85°C

|                      | PARAMETER                          | TEST CONDITIONS                                                                           | MIN | TYP | MAX | UNIT |

|----------------------|------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>PW_G</sub>    | Pulse width of suppressed glitches |                                                                                           |     |     | 50  | ns   |

| f <sub>SCL</sub>     | SCL clock frequency                | Standard                                                                                  |     | 100 |     | kHz  |

| f <sub>SCL</sub>     | SCL clock frequency                | Fast-mode                                                                                 |     | 400 |     | kHz  |

| t <sub>SU_STA</sub>  | Setup time start condition         | $SCL = V_{IH}$ before $SDA = V_{IL}$                                                      |     | 0.6 |     | μs   |

| t <sub>H_STA</sub>   | Hold time start condition          | SCL = $V_{IL}$ after SCL = $V_{IL}$ . After this time, the first clock edge is generated. |     | 0.6 |     | μS   |

| t <sub>SU_SDA</sub>  | Setup time data                    | SDA valid after SCL = V <sub>IL</sub> , f <sub>SCL</sub> = 100 kHz                        | 250 |     |     | ns   |

| t <sub>SU_SDA</sub>  | Setup time data                    | SDA valid after SCL = V <sub>IL</sub> , f <sub>SCL</sub> = 400 kHz                        | 100 |     |     | ns   |

| t <sub>H_SDA</sub>   | Hold time data                     | SDA valid before SCL = $V_{IH}$                                                           | 0   |     |     | μs   |

| t <sub>PWH_SCL</sub> | Pulse width high, SCL              | f <sub>SCL</sub> = 100 kHz                                                                | 4   |     |     | μs   |

| t <sub>PWH_SCL</sub> | Pulse width high, SCL              | f <sub>SCL</sub> = 400 kHz                                                                | 0.6 |     |     | μs   |

| t <sub>PWL_SCL</sub> | Pulse width low, SCL               | f <sub>SCL</sub> = 100 kHz                                                                | 4.7 |     |     | μS   |

Copyright © 2017–2019, Texas Instruments Incorporated

STRUMENTS

EXAS

# Timing Requirements, I<sup>2</sup>C-Compatible Serial Interface (SDA/GPIO2, SCL/GPIO3) (continued)

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and  $T_A$  = –40°C to 85°C

| PARAMETER            |                      | TEST CONDITIONS             | MIN | TYP | MAX | UNIT |

|----------------------|----------------------|-----------------------------|-----|-----|-----|------|

| t <sub>PWL_SCL</sub> | Pulse width low, SCL | f <sub>SCL</sub> = 400 kHz  | 1.3 |     |     | μS   |

| t <sub>OF</sub>      | Output fall time     | C <sub>OUT</sub> = 10400 pF |     |     | 250 | ns   |

# 6.24 Power Supply Characteristics

VDDVCO, VDDO12, VDDO34, VDDREF = 1.8 V ±5%, 2.5 V ±5%, 3.3 V ±5% and T\_A = -40^{\circ}C to 85°C

|                     | PARAMETER                                   | TEST CONDITIONS                                                                                                                                          | MIN TYP | MAX | UNIT |

|---------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| I <sub>DD_REF</sub> | Reference input current                     | DBL = on                                                                                                                                                 | 4       |     | mA   |

| I <sub>DD_XIN</sub> | Crystal input current                       | Crystal with $P_{max} = 200 \ \mu W$                                                                                                                     | 2       |     | mA   |

| I <sub>DD_VCO</sub> | VCO and PLL current                         | $f_{VCO}$ = 2500 MHz, PSFB = PSA = 4<br>and PSB = off                                                                                                    | 13      |     | mA   |

| I <sub>DD_OUT</sub> | Output channel current                      | Activated output channel, 1x LVDS<br>156.25 MHz                                                                                                          | 10      |     | mA   |

| I <sub>DD_IOD</sub> | Output integer divider current              |                                                                                                                                                          | 2       |     | mA   |

| I <sub>DD_FOD</sub> | Output fractional divider current           |                                                                                                                                                          | 20      |     | mA   |

| I <sub>DD_PDN</sub> | Power-down current                          | Using reset pin / bits                                                                                                                                   | 3       |     | mA   |

| I <sub>DD_TYP</sub> | Typical current                             | 4x 156.25-MHz LVDS case using crystal input and doubler                                                                                                  | 83      |     | mA   |

| I <sub>DD_TYP</sub> | Typical current                             | 2x IODs LVDS/LVCMOS, 1x FOD<br>LVDS                                                                                                                      | 72      |     | mA   |

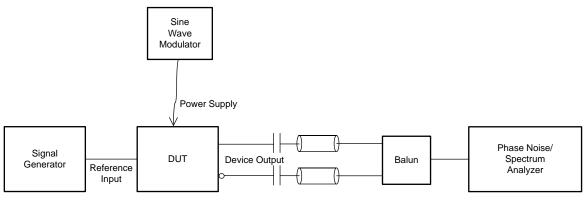

| L <sub>PSNR</sub>   | Power supply noise rejection <sup>(1)</sup> | $ \begin{array}{l} Yx = 100 \; \text{MHz LVDS, on one of} \\ \text{VDDx injected sine wave 50 mV at} \\ f_{\text{INJ}} = 10 \; \text{kHz}, \end{array} $ | -56     |     | dBc  |

| L <sub>PSNR</sub>   | Power supply noise rejection <sup>(1)</sup> | $\begin{array}{l} Yx = 100 MHz \ LVDS, \ on \ one \ of \\ VDDx \ injected \ sine \ wave \ 50 \ mV \ at \\ f_{INJ} = 100 \ \text{kHz} \end{array}$        | -46     |     | dBc  |

| L <sub>PSNR</sub>   | Power supply noise rejection <sup>(1)</sup> | $\begin{array}{l} Yx = 100 MHz \ LVDS, \ on \ one \ of \\ VDDx \ injected \ sine \ wave \ 50 \ mV \ at \\ f_{INJ} = 1 \ MHz \end{array}$                 | -49     |     | dBc  |

| L <sub>PSNR</sub>   | Power supply noise rejection <sup>(1)</sup> | $Yx = 100MHz$ LVDS, on one of VDDx injected sine wave 50 mV at $f_{INJ} = 10$ MHz                                                                        | -69     |     | dBc  |

| L <sub>PSNR</sub>   | Power supply noise rejection <sup>(1)</sup> | Yx = 100MHz LVDS, on one of<br>VDDx injected sine wave 50 mV at<br>$f_{INJ}$ = 20 MHz                                                                    | -74     |     | dBc  |

| L <sub>PSNR</sub>   | Power supply noise rejection <sup>(1)</sup> | Yx = 100MHz LVDS, on one of VDDx injected sine wave 50 mV at $f_{INJ}$ = 40 MHz                                                                          | -73     |     | dBc  |

(1) dBc with respect to output carrier frequency.

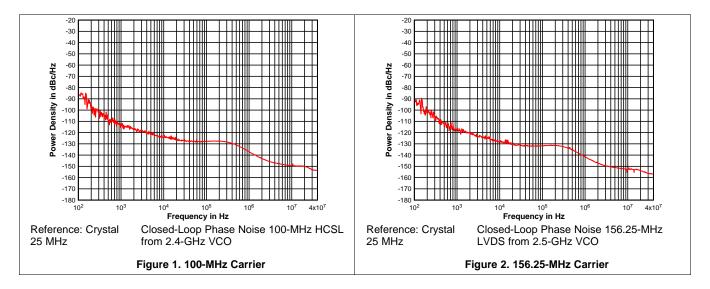

# 6.25 Typical Characteristics

VDDx = 1.8 V at room temperature

# 7 Parameter Measurement Information

#### 7.1 Parameters

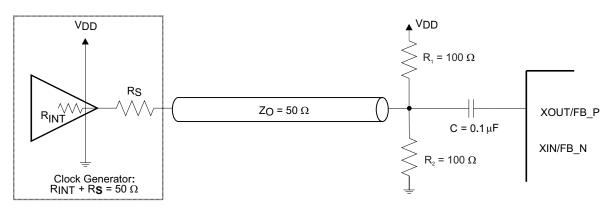

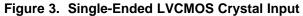

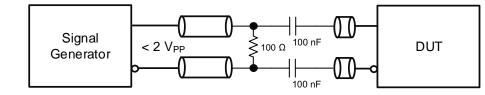

#### 7.1.1 Reference Inputs

(1) Applied signal has to stay within  $V_{\text{IN}\_\text{DIFF}}$  limits.

Figure 4. Differential AC-Coupled Input

### 7.1.2 GPIOs

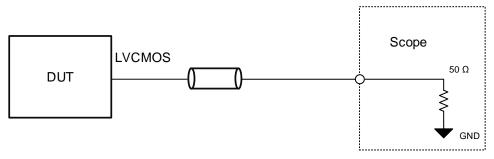

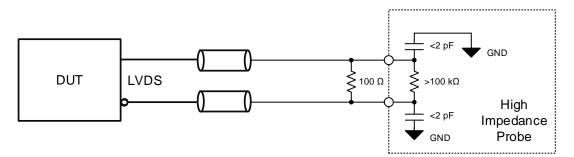

#### 7.1.3 Outputs

# **Parameters (continued)**

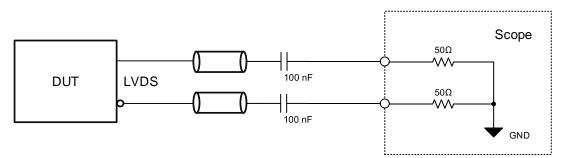

Figure 6. LVDS Output, DC-Coupled

Figure 7. LVDS Output AC-Coupled

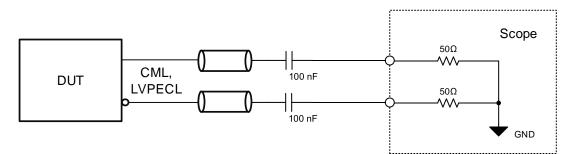

Figure 8. Differential AC-Coupled (CML, LVPECL)

# **Parameters (continued)**

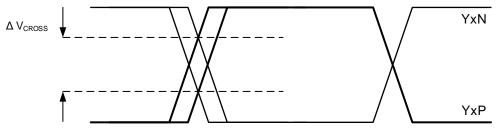

Differential Waveform HCSL

- Differential waveform created using math function in scope subtracting positive from negative output pin waveform: YxP - YxN.

- (2) Slew rate measured using absolute ± 150 mV on the differential waveform. This correlates to the cross-point of the single ended positive and negative waveform.

(1) Measurement conducted using the single ended waveforms. Total variation of the crossing point of rising YxP and falling YxN edges.

Figure 12. HCSL, Delta Crossing Voltage

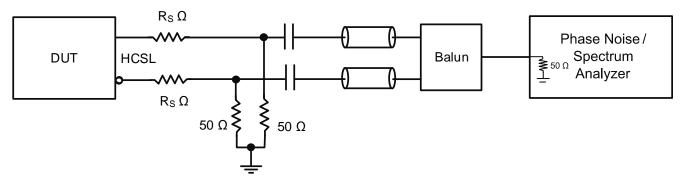

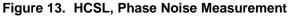

# **Parameters (continued)**

(1) Measured using Tektronix DPO75902SX oscilloscope. Recommended to use an oscilloscope bandwidth setting of 4/8 GHz and vertical setting of 50mV/division. Data processed using Clock Jitter Tool: Ver:1.6.7.2.

Figure 14. HCSL PCIe Test Load Setup

#### 7.1.4 Serial Interface

Figure 15. I<sup>2</sup>C Timing

# 8 Detailed Description

### 8.1 Overview

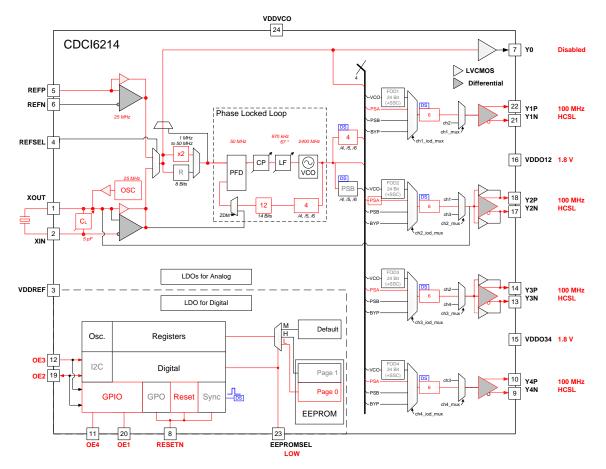

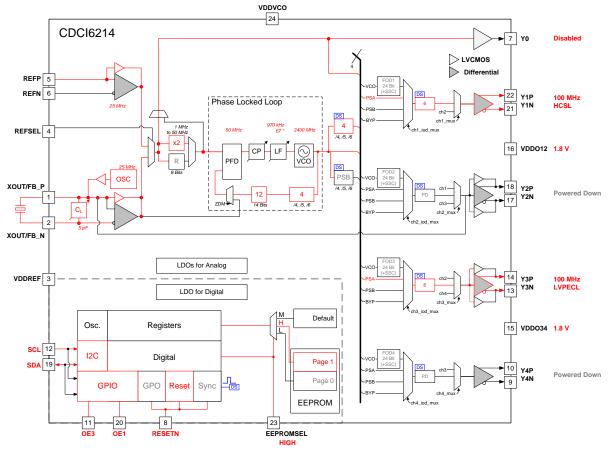

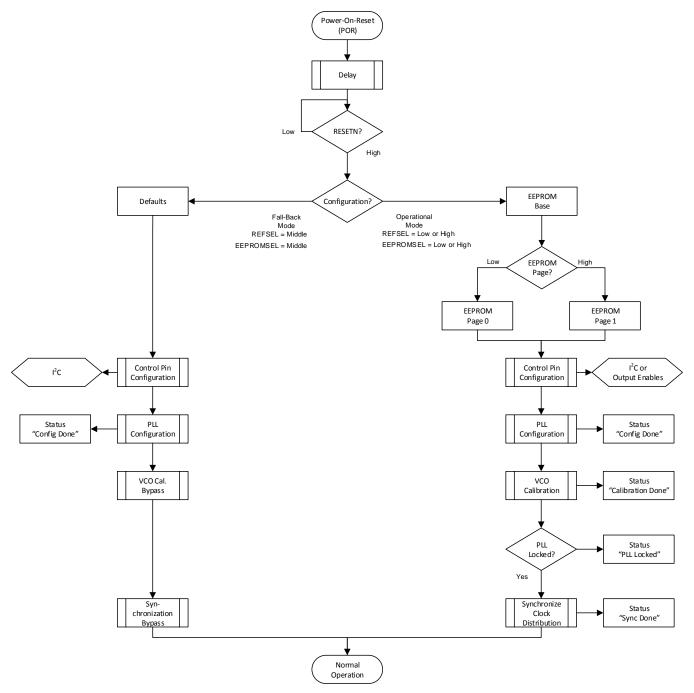

The CDCI6214 clock generator is a phase-locked loop with integrated loop filter and selectable input reference. The output of the integrated voltage-controlled oscillator (VCO) is connected to a clock distribution network, which includes multiple frequency dividers and feeds four output channels with configurable differential and single-ended output buffers.

# 8.2 Functional Block Diagram

Figure 17. CDCI6214 Clock Generator With Four Outputs

#### 8.3 Feature Description

The following sections describe the individual blocks of the CDCI6214 ultra-low power clock generator.

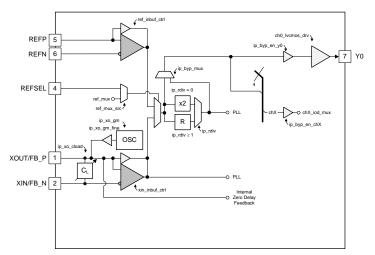

#### 8.3.1 Reference Block

A reference clock to the PLL is fed to pins 1 (XOUT/FB\_P) and 2 (XIN/FB\_N) or to pins 5 (REFP) and 6 (REFN). There are multiple input stages available to adapt to many clock references. The bit-fields that control the reference input type selection are xin\_inbuf\_ctrl and ref\_inbuf\_ctrl.

The reference mux selects the reference for the PLL and the PLL-bypass path. For debug purposes ip\_byp\_mux allows to connect the reference divider or doubler output to the clock distribution.

The buffers for the PLL-bypass path can be individually enabled and disabled using ip\_byp\_en\_ch[4:1] and ip\_byp\_en\_y0.

Figure 18. Reference Block

#### 8.3.1.1 Input Stages

#### 8.3.1.1.1 Crystal Oscillator

The XIN and XOUT pins provide a crystal oscillator stage to drive a fundamental mode crystal in the range of 8 MHz to 50 MHz. The crystal input stage integrates a tunable load capacitor array up to 9 pF using ip\_xo\_cload. The drive capability of the oscillator is adjusted using ip\_xo\_gm.

#### 8.3.1.1.2 LVCMOS

The LVCMOS input buffer threshold voltage follows VDDREF. This helps to use the device as a level shifter as the outputs have separate supplies.

#### 8.3.1.1.3 Differential AC-Coupled

The differential input stage has an internal bias generator and should only be used with AC-coupled reference inputs.

#### 8.3.1.2 Reference Mux

Either XIN or REF can be selected as reference to the PLL and clock distribution path. The reference mux is controlled using the REFSEL pin with ref\_mux\_src = 0 or the ref\_mux bit-field with ref\_mux\_src = 1.

#### 8.3.1.3 Reference Divider

A reference divider can be used to divide higher input frequencies to the permitted PFD range. It supports division values of 1 to 255 using ip\_rdiv.

**CDCI6214**

SNAS734D - JULY 2017 - REVISED JUNE 2019

#### Feature Description (continued)

#### 8.3.1.3.1 Doubler

The reference path contains a doubler circuit. It is used to double the input frequency and can be used to achieve the highest PFD update frequency of 100 MHz using a 50-MHz crystal. The doubler activates using  $ip_rdiv = 0$ .

#### 8.3.1.4 Bypass-Mux

The input reference or the input to the PFD can be routed to the bypass path using ip\_byp\_mux.

#### 8.3.1.5 Zero Delay, Internal and External Path

In zero delay mode the REF input clock is used as reference clock at the PFD. The FB\_P clock (LVCMOS) or FB\_P/N clock (differential) can be used to feed an external source as feedback clock to the PFD. The external feedback path is recommended for zero delay operation. Moreover there is an additional internal feedback path which is sourced by output channel 2.

| Operation                        |        | Reference |                 |         |                    | Feedback           |              |                  |              |          |         |          |                                |

|----------------------------------|--------|-----------|-----------------|---------|--------------------|--------------------|--------------|------------------|--------------|----------|---------|----------|--------------------------------|

|                                  | REFSEL | ref_mux   | ref_mux_<br>src | ip_rdiv | ref_inbuf<br>_ctrl | xin_inbuf<br>_ctrl | zdm_mo<br>de | zdm_cloc<br>ksel | zdm_aut<br>o | pll_psfb | pll_psa | pll_ndiv | ch2_iod_<br>div <sup>(2)</sup> |

| Normal PLL, XIN<br>Reference     | L      | x         | 0               | 1       | x                  | 0                  | 0            | x                | x            | x        | x       | x        | x                              |

| Normal PLL, REF<br>Reference     | L      | x         | 0               | 1       | x                  | x                  | 0            | x                | x            | x        | x       | x        | x                              |

| Normal PLL, REF<br>Reference     | x      | 1         | 1               | 1       | x                  | x                  | 0            | x                | x            | x        | x       | x        | x                              |

| Zero Delay, Internal<br>Feedback | x      | 1         | 1               | 1       | А                  | А                  | 1            | 0                | 1            | В        | В       | С        | С                              |

| Zero Delay, External<br>Feedback | x      | 1         | 1               | 1       | А                  | А                  | 1            | 1                | 1            | В        | В       | С        | С                              |

| Table 1. Zero | Delav O | peration <sup>(1)</sup> |

|---------------|---------|-------------------------|

|---------------|---------|-------------------------|

(1) 'x' allows any possible bit-field value. An entry of 'A', 'B' or 'C' indicates the same bit-field value.

(2) For internal feedback channel 2 is required. For external feedback the output clock connected to FB\_P/N is recommended to have same settings as default PLL feedback path.

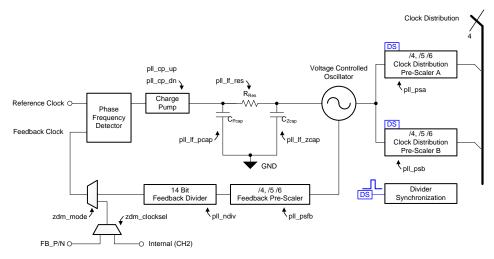

#### 8.3.2 Phase-Locked Loop

The CDCI6214 contains a fully integrated phase-locked loop circuit. The error between a reference phase and an internal feedback phase is compared at the phase-frequency-detector. The comparison result is fed to a charge pump that is connected to an integrated loop filter. The control voltage resulting from the loop filter tunes an internal voltage-controlled oscillator (VCO). The frequency of the VCO is fed through a pre-scaler feedback divider (PSFB) and another feedback divider back to the PFD.

The PLL closed-loop bandwidth is configurable using registers PLL0, PLL1, and PLL2.

- Integer PLL

- PFD operates 1 MHz to 100 MHz

- Live Lock-Detector provides PLL lock status on status pin and bit lock\_det (there is an additional sticky bit unlock\_s)

- Integrated selectable loop filter components

- For 25-MHz PFD bandwidths between 100 kHz and 3000 kHz can be achieved to optimize PLL to input reference

- Voltage-Controlled Oscillator (VCO) tuning range of 2400 to 2800 MHz

- VCO is compatible to 0.5% spread spectrum (SSC) references at 100 MHz.

Figure 19. Phase-Locked Loop Circuit

| f in MH-                | f <sub>PED</sub> in MHz | BW in MHz | Phase       | Damping | I <sub>CP</sub> in mA    | C <sub>Pcap</sub> IN pF | $R_{Res}$ IN k $\Omega$ | C <sub>Zcap</sub> IN pF |

|-------------------------|-------------------------|-----------|-------------|---------|--------------------------|-------------------------|-------------------------|-------------------------|

| f <sub>VCO</sub> in MHz |                         |           | Margin in ° | Factor  | pll_cp_up <sup>(2)</sup> | pll_lf_pcap             | pll_lf_res              | pll_lf_zcap             |

| 2400                    | 25                      | 0.51      | 67          | 0.9     | 2.0                      | 17.5                    | 2.5                     | 450                     |

| 2400                    | 50                      | 0.97      | 67          | 1.3     | 2.0                      | 17.5                    | 2.5                     | 450                     |

| 2400                    | 100                     | 1.41      | 68          | 1.2     | 2.4                      | 17.5                    | 1.5                     | 450                     |

| 2457.6                  | 61.44                   | 1.04      | 67          | 1.4     | 1.8                      | 17.5                    | 2.5                     | 450                     |

| 2500                    | 25                      | 0.49      | 67          | 0.9     | 2.0                      | 17.5                    | 2.5                     | 450                     |

| 2500                    | 50                      | 0.93      | 68          | 1.3     | 2.0                      | 17.5                    | 2.5                     | 450                     |

| 2680                    | 67                      | 0.38      | 67          | 1.3     | 0.2                      | 19.5                    | 5.5                     | 480                     |

| 2688                    | 48                      | 0.93      | 68          | 1.3     | 1.5                      | 17.5                    | 2.5                     | 480                     |

| 2688                    | 96                      | 0.36      | 67          | 1.0     | 0.2                      | 19.5                    | 3.5                     | 480                     |

| 2800                    | 50                      | 1.00      | 68          | 1.0     | 2.6                      | 17.5                    | 1.5                     | 450                     |

| 2800                    | 100                     | 1.00      | 68          | 1.0     | 1.3                      | 17.5                    | 1.5                     | 450                     |

| Table 2. Common | Clock | Generator | Loop | Filter | Settings <sup>(1)</sup> |

|-----------------|-------|-----------|------|--------|-------------------------|

|-----------------|-------|-----------|------|--------|-------------------------|

(1) All values typical design targets.

(2) Program same value to pll\_cp\_dn.

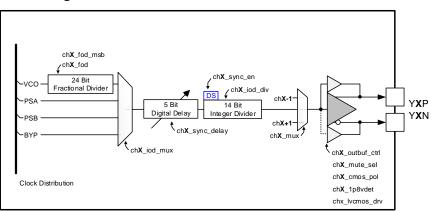

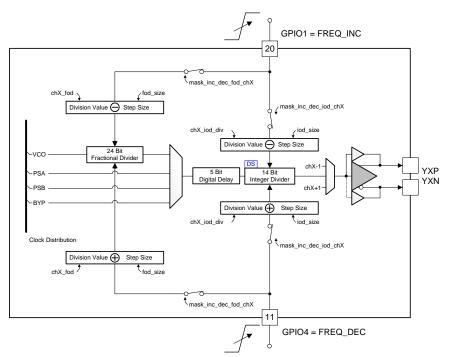

#### 8.3.3 Clock Distribution

The VCO connects to two individually configurable pre-scaler dividers sourcing the on-chip clock distribution.

The clock distribution consists of four output channels. Each output channel contains a divider with integer and fractional division as well as spread-spectrum and synchronization capabilities.

A mux after each divider allows to feed the generated frequency to the adjacent output buffers. Thus for single frequency clock generation only a single output divider needs to be active.

The output buffers are compatible to various signaling standards: LVDS, CML-like, LVPECL-like, LVCMOS and HCSL using ch1\_outbuf\_ctrl.

- HCSL must be directly connected to a load termination to ground. A series resistance can be used to adapt to the trace impedance.

- LVDS requires a differential termination connected between the positive and negative output buffer pins. The termination can be connected directly or using AC-coupling. When using the LVDS output type, set ch1\_1p8vdet, ch2\_1p8vdet, ch3\_1p8vdet, andch4\_1p8vdet to match the VDDO12 and VDDO34.

- CML and LVPECL are only supported in an AC-coupled configuration. The receiver and the termination may

only be connected through AC-coupling capacitors to the device pins.

- LVCMOS outputs are designed for capacitive loads only. A series resistance should be used to adapt the

**STRUMENTS**

XAS

driver impedance to the trace impedance. For a typical 50- $\Omega$  trace, a resistor between 22  $\Omega$  to 33  $\Omega$  should be used. The polarity of the positive and negative pins can be adjusted separately.

The output buffers support a wide frequency range of up to 350 MHz. Higher output frequencies up to 700 MHz are functional, but are not covered by electrical specifications.

#### 8.3.3.1 Output Channel

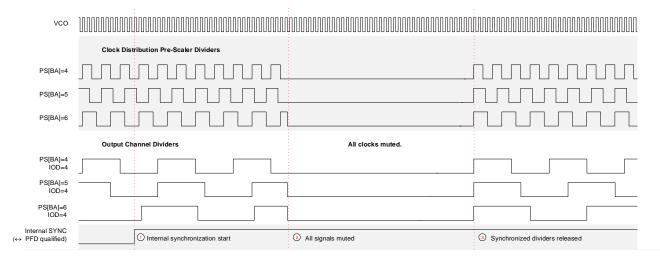

Figure 20. Clock Distribution Pre-Scaler Dividers<sup>(1)</sup>

#### Figure 21. Clock Distribution, Output Channel

| INSTANCES | DIVISION VALUES |

|-----------|-----------------|

| PSA       | 4, 5, 6         |

| PSB       | 4, 5, 6         |

(1) A known phase relationship for divider synchronization with mixed division values is ensured by architecture.

#### Table 3. Output Buffer Signal Standards

|        |        | -                   | -    |                       |                          |

|--------|--------|---------------------|------|-----------------------|--------------------------|

| OUTPUT | LVCMOS | HCSL <sup>(1)</sup> | LVDS | AC-CML <sup>(2)</sup> | AC-LVPECL <sup>(2)</sup> |

| Y0     | X      |                     |      |                       |                          |