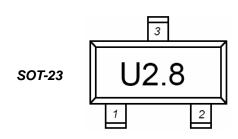

## SLVU2.8

## Low Voltae EPD TVS Diode For ESD and Latch-Up Protection Revision:B

## **General Description**

The Ultraslow Capacitance Transient Voltage Suppressors are designed to low voltage, integrated circuits from transients caused by electrostatic discharge (ESD), electrical fast transients (EFT), tertiary lightning and other induced voltages.

### **Applications**

- Ethernet 10/100/1000 Base T

- WAN/LAN Equipment

- Desktops, Servers, Notebooks & Handhelds

- Laser Diode Protection

### **Features**

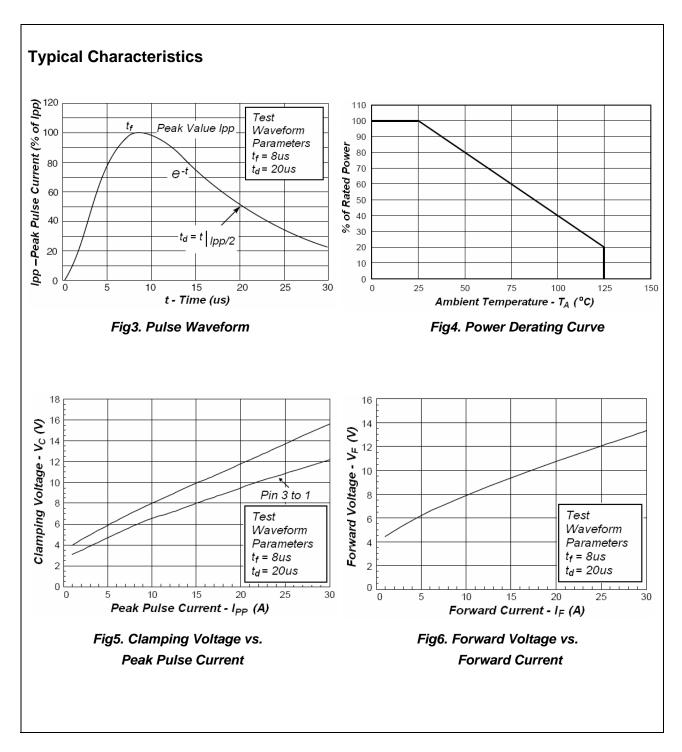

- 400 W Peak Pulse Power per Line (tp=8/20μs)

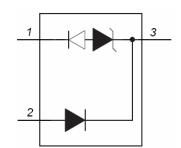

- One Device protects one Unidirectional Line.

- Low Capacitance.

- Low Leakage Current.

- Low Operating and Clamping Voltages.

- Transient Protection for High Speed Data Lines to

IEC61000-4-2(ESD)±15kV(air),±8kV(Contact)

IEC61000-4-4(EFT) 40A(5/50ns)

IEC61000-4-5(lightning) 24A(8/20us)

#### **Absolute Maximum Ratings**

| Parameter                                  | Symbol          | Value      | Units |

|--------------------------------------------|-----------------|------------|-------|

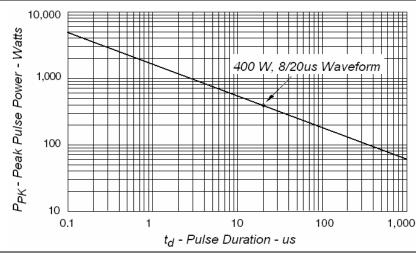

| Peak Pulse Power (tp = 8/20µs) - See Fig1. | P <sub>PK</sub> | 400        | W     |

| Peak Pulse Current (tp = 8/20µs)           | I <sub>PP</sub> | 24         | Α     |

| Storage Temperature Range                  |                 | -55 to 150 | °C    |

| Operating Junction Temperature Range       | TJ              | -55 to 150 | °C    |

Fig1. Peak Pulse Power

VS Pulse Time

# **Electrical Parameter**

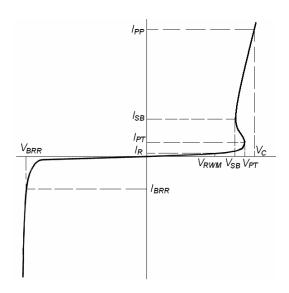

| Symbol           | Parameter                                    |  |  |  |

|------------------|----------------------------------------------|--|--|--|

| I <sub>PP</sub>  | Peak Pulse Current                           |  |  |  |

| V <sub>C</sub>   | Clamping Voltage @ I <sub>PP</sub>           |  |  |  |

| $V_{RWM}$        | Reverse Stand-Off Voltage                    |  |  |  |

| I <sub>R</sub>   | Reverse Leakage Current @ V <sub>RWM</sub>   |  |  |  |

| $V_{SB}$         | Snap-Back Voltage @ I <sub>SB</sub>          |  |  |  |

| I <sub>SB</sub>  | Snap-Back Current                            |  |  |  |

| $V_{PT}$         | Punch-Through Voltage                        |  |  |  |

| I <sub>PT</sub>  | Punch-Through Current                        |  |  |  |

| $V_{BRR}$        | Reverse Breakdown Voltage @ I <sub>BRR</sub> |  |  |  |

| I <sub>BRR</sub> | Reverse Breakdown Current                    |  |  |  |

Fig 2. SLVU2.8 IV Characteristic Curve

# **Electrical Characteristics**

| Parameter                 | Symbol          | Conditions                            | Minimum | Typical | Maximum | Units |

|---------------------------|-----------------|---------------------------------------|---------|---------|---------|-------|

| Reverse Stand-Off Voltage | $V_{RWM}$       | Pin 3 to 1 or Pin 2 to 1              | 1       |         | 2.8     | V     |

| Punch-Through Voltage     | $V_{PT}$        | I <sub>PT</sub> = 2uA, Pin 3 to 1 3.0 |         |         |         | V     |

| Snap-Back Voltage         | V <sub>SB</sub> | I <sub>SB</sub> = 50mA, Pin 3 to 1    | 1 2.8   |         |         | V     |

| Reverse Leakage Current   | I <sub>R</sub>  | V <sub>RWM</sub> =2.8V, T=25℃         |         | 1       |         | uA    |

|                           |                 | Pin 3 to 1 or Pin 2 to 1              |         |         | '       |       |

| Clamping Voltage          | V <sub>C</sub>  | $I_{PP}$ =2A, $t_{P}$ =8/20us         |         |         | 3.9     | V     |

|                           |                 | Pin 3 to 1                            |         |         | 5.9     |       |

| Clamping Voltage          | V <sub>C</sub>  | $I_{PP}$ =5A, $t_{P}$ =8/20us         |         |         | 7       | V     |

|                           |                 | Pin 3 to 1                            |         |         | ,       | ٧     |

| Clamping Voltage          | V <sub>C</sub>  | $I_{PP}$ =24A, $t_{P}$ =8/20us        |         | 12.5    |         | V     |

|                           |                 | Pin 3 to 1                            |         |         | 12.5    | V     |

| Clamping Voltage          | V <sub>C</sub>  | $I_{PP}$ =5A, $t_{P}$ =8/20us         |         |         | 8.5     | V     |

|                           |                 | Pin 2 to 1                            |         |         |         |       |

| Clamping Voltage          | V <sub>C</sub>  | $I_{PP}$ =24A, $t_{P}$ =8/20us        |         |         | 15      | V     |

|                           |                 | Pin 2 to 1                            |         |         | 15      | V     |

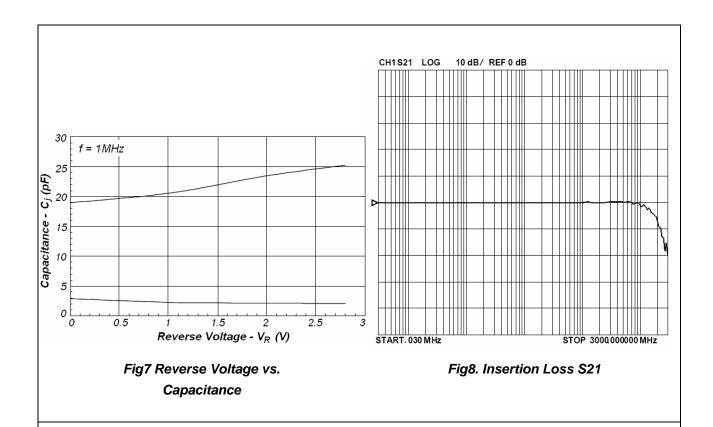

| Junction Capacitance      | C <sub>j</sub>  | Pin 3 to 1 and 2                      |         |         | 100     | pF    |

|                           |                 | (Pin 1 and 2 tied together)           |         | 70      |         |       |

|                           |                 | VR =0V, f =1MHz                       |         |         |         |       |

| lunction Canacitance      |                 | Pin 2 to 1 (Pin 3 N.C.)               | 2.5     |         | 5       | nE    |

| Junction Capacitance      | C <sub>j</sub>  | VR =0V, f =1MHz                       |         | 3.5     | υ       | pF    |

| Steering Diode Characteristics |                  |                                  |         |         |         |       |

|--------------------------------|------------------|----------------------------------|---------|---------|---------|-------|

| Parameter                      | Symbol           | Conditions                       | Minimum | Typical | Maximum | Units |

| Reverse Breakdown Voltage      | $V_{BRR}$        | I <sub>T</sub> =10uA, Pin 3 to 2 | 40      |         |         | V     |

| Reverse Leakage Current        | I <sub>BRR</sub> | V <sub>RWM</sub> =2.8V, T =25°C  |         |         | 1       | UA    |

| Reverse Leakage Current        |                  | Pin 3 to 2                       |         |         |         |       |

| Forward Voltage                | $V_{F}$          | I <sub>F</sub> =1A, Pin 2 to 3   |         |         | 2       | V     |

## **Application Note**

The SLVU2.8 is ideal for providing protection for electronic equipment that is susceptible to damage caused by Electrostatic Discharge (ESD), Electrical Fast Transients (EFT) and tertiary lightning effects. This product is offered in a unidirectional configuration and provides both commonmode and differential-mode protection.

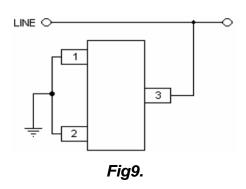

### Unidirectional Common-Mode Protection (Figure 9)

The SLVU2.8 provides one line of unidirectional protection in a common-mode configuration as depicted in figure 9.

Circuit connectivity is as follows:

- Line 1 is connected to Pin 3

- Pins 1 and 2 are connected to ground

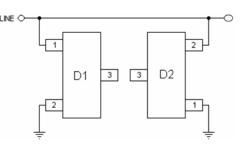

#### Bidirectional Common-Mode Protection (Figure 10)

Two SLVU2.8 devices provide one line of bidirectional protection in a common-mode configuration as depicted in figure 10.

Circuit connectivity is as follows:

- Line 1 is connected to Pin1 of Device 1 & Pin 2 of Device 2

- Pin 2 of Device 1 and Pin 1 of Device 2 are connected to ground

- Pin 3 of both devices is not connected

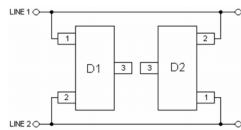

Fig10.

### Bidirectional Differential-Mode Protection (Figure 11)

Two SLVU2.8 devices provide up to two lines of bidirectional protection in a differential mode configuration as depicted in figure 11.

Circuit connectivity is as follows:

- Line 1 is connected to Pin1 of Device 1 & Pin 2 of Device 2

- Line 2 is connected to Pin 2 of Device 1 & Pin 1 of Device 2

Fig11.

#### Circuit Board Layout Protection

Circuit board layout is critical for Electromagnetic Compatibility (EMC) protection. The following guidelines are recommended:

- The protection device should be placed near the input terminals or connectors, the device will divert the transient current immediately before it can be coupled into the nearby traces.

- The path length between the TVS device and the protected line should be minimized.

- All conductive loops including power and ground loops should be minimized.

- The transient current return path to ground should be kept as short as possible to reduce parasitic inductance.

- Ground planes should be used whenever possible. For multilayer PCBs, use ground vias.

#### **Typical Applications** RJ45 TPIN 50 Ω 50Ω To Twisted -- Pair Network 10/100 75Ω 50Ω 50Ω Ethernet Repeater 50Ω 50Ω TPIP 50Ω ∕∕∕√√ Ē 75Ω .01uF TPON \$200Ω .001uF SLVU2.8 **≨**200Ω HTPOP .01uF VCCT .01uF SLVU2.8 GNDT

Fig12. 10/100 Ethernet Protection Circuit

Fig13. 10/100 Ethernet "Enhanced" Lightning Protection Circuit

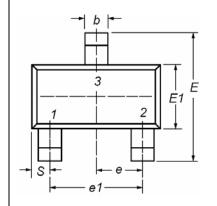

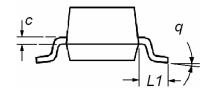

### **SOT-23 Mechanical Data**

| Dim        | Millimeters |      |      |  |  |  |

|------------|-------------|------|------|--|--|--|

|            | Min         | TYP  | Max  |  |  |  |

| Α          | 1.00        |      | 1.40 |  |  |  |

| <b>A</b> 1 | 0           |      | 0.10 |  |  |  |

| A2         | 1.00        |      | 1.30 |  |  |  |

| b          | 0.35        |      | 0.50 |  |  |  |

| С          | 0.10        |      | 0.20 |  |  |  |

| D          | 2.70        | 2.90 | 3.10 |  |  |  |

| E          | 2.40        |      | 2.80 |  |  |  |

| E1         | 1.40        |      | 1.60 |  |  |  |

| е          | 0.85        |      | 1.15 |  |  |  |

| e1         |             | 1.90 |      |  |  |  |

| L1         | 0.40        |      |      |  |  |  |

| q          | 0°          |      | 10°  |  |  |  |

| S          | 0.45        |      | 0.55 |  |  |  |

The SINO-IC logo is a registered trademark of ShangHai Sino-IC Microelectronics Co., Ltd.

© 2005 SINO-IC – Printed in China – All rights reserved.

### SHANGHAI SINO-IC MICROELECTRONICS CO., LTD

Add: Building 3, Room 3401-03, No.200 Zhangheng Road, ZhangJiang Hi-Tech Park, Pudong,

Shanghai 201203, China

**Phone:** +86-21-33932402 33932403 33932405 33933508 33933608

Fax: +86-21-33932401

Email: webmaster@sino-ic.com

Website: http://www.sino-ic.com