# SSD2828

## Advance Informatiom

### **MIPI Master Bridge**

This document contains information on a new product. Specifications and information herein are subject to change without notice.

http://www.solomon-systech.com

SSD2828

Rev 1.3

P 1/182

Dec 2012

| Version | Change Items                                                                                                                                                                                                                                                                                                                                                                     | <b>Effective Date</b> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 0.10    | 1 <sup>st</sup> Release                                                                                                                                                                                                                                                                                                                                                          | 24-Apr-12             |

| 1.0     | Initial release of Advance Information                                                                                                                                                                                                                                                                                                                                           | 08-Aug-12             |

| 1.1     | <ul> <li>Remove DFR register and interface format select (IFS) description (Section 10.1)</li> <li>Modify PLL calculation (Section 8.1.12)</li> <li>Include example for 1 frame RAM size in command mode setting (Packet size control register (8.1.14))</li> <li>Modify flow for MIPI read (Section 10.5.1, 10.6.1)</li> <li>Modify PS[1:0] = 11 setting (Section 7)</li> </ul> | 19-Sept-12            |

| 1.2     | 1.2       - Modify TX_CLK pin description (Section 7)       13-Dec-12         - Modify the description of END and CO (Section 8.1.38)       13-Dec-12         - Modify the timing for data latch in RGB timing (Section 14.6)       13-Dec-12                                                                                                                                    |                       |

| 1.3     | - Specify the prefix T in RGB timing (Section14.6)                                                                                                                                                                                                                                                                                                                               | 09-Jan-13             |

### Appendix 1: IC Revision history of SSD2828 Specification

### CONTENTS

| 1 | GE             | NERAL DESCRIPTION                                                                    |    |

|---|----------------|--------------------------------------------------------------------------------------|----|

| 2 | FE.            | ATURES                                                                               |    |

|   | 2.1            | References                                                                           |    |

|   | 2.2            | DEFINITIONS                                                                          | 11 |

| 3 | OR             | DERING INFORMATION                                                                   |    |

| 4 | BL             | OCK DIAGRAM                                                                          |    |

| 5 | FU             | NCTIONAL DESCRIPTION                                                                 |    |

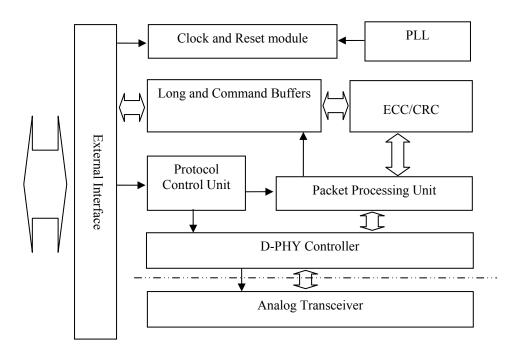

|   | 5.1            | FUNCTIONAL BLOCKS                                                                    |    |

|   | 5.2            | CLOCK AND RESET MODULE                                                               |    |

|   | 5.3            | EXTERNAL INTERFACE                                                                   |    |

|   | 5.4            | PROTOCOL CONTROL UNIT (PCU)                                                          |    |

|   | 5.5            | PACKET PROCESSING UNIT (PPU)                                                         |    |

|   | 5.6            | ERROR CORRECTION CODE/ CYCLIC REDUNDANCY CHECK (ECC/CRC)<br>LONG AND COMMAND BUFFERS |    |

|   | 5.7<br>5.8     | LONG AND COMMAND BUFFERS<br>INTERRUPT SIGNAL                                         |    |

|   | 5.8<br>5.9     | D-PHY CONTROLLER                                                                     |    |

|   | 5.10           | ANALOG TRANSCEIVER                                                                   |    |

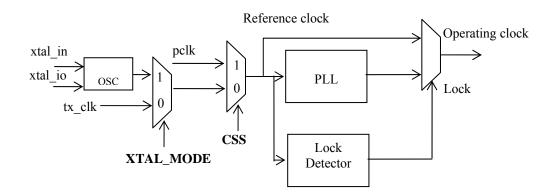

|   | 5.11           | INTERNAL PLL                                                                         |    |

|   | aai            |                                                                                      | 10 |

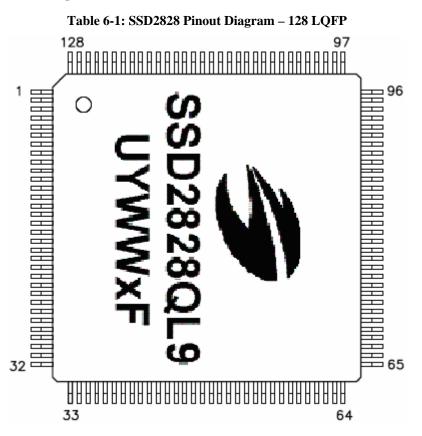

| 6 | 221            | D2828QL9 PIN ASSIGNMENT                                                              | 19 |

| _ | DD             |                                                                                      | 22 |

| 7 | PIP            | N DESCRIPTION                                                                        |    |

| 0 | CO             | OMMAND TABLE                                                                         | 27 |

| 8 | CO             |                                                                                      |    |

|   | 8.1            | REGISTER DESCRIPTION REGISTER DESCRIPTION                                            |    |

|   | 8.1.           | J                                                                                    |    |

|   | 8.1.2          | J 0                                                                                  |    |

|   | 8.1.           | 5 8                                                                                  |    |

|   | 8.1.4          |                                                                                      |    |

|   | 8.1.:<br>8.1.0 | 5 0                                                                                  |    |

|   | 8.1.0          |                                                                                      |    |

|   | 8.1.8          |                                                                                      |    |

|   | 8.1.9          |                                                                                      |    |

|   | 8.1.           |                                                                                      |    |

|   | 8.1.           | •                                                                                    |    |

|   | 8.1.           | 12 Clock Control Register                                                            |    |

|   | 8.1.           |                                                                                      |    |

|   | 8.1.           |                                                                                      |    |

|   | 8.1.           |                                                                                      |    |

|   | 8.1.           |                                                                                      |    |

|   | 8.1.<br>8.1.   | - <i>I</i> - 3                                                                       |    |

|   | 8.1.           |                                                                                      |    |

|   | 8.1.2          | •                                                                                    |    |

|   | 8.1.2          | 1 3                                                                                  |    |

|   | 8.1.2          |                                                                                      |    |

|   | 8.1.2          | 1 0                                                                                  |    |

|   | 8.1.2          |                                                                                      |    |

|   | 8.1.2          | 25 Delay Adjustment Register 1                                                       |    |

|   | 8.1.2          | 26 Delay Adjustment Register 2                                                       |    |

|   |                |                                                                                      |    |

| 8.1.27           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.1.28           | Delay Adjustment Register 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

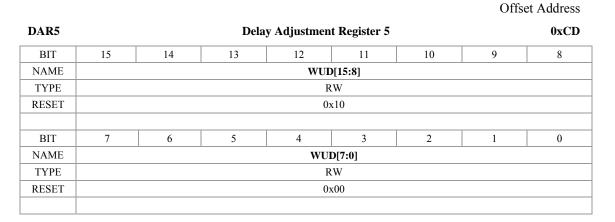

| 8.1.29           | Delay Adjustment Register 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 8.1.30           | Delay Adjustment Register 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

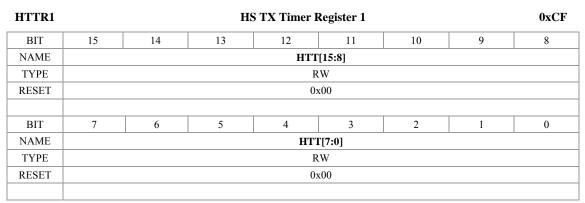

| 8.1.31           | HS TX Timer Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

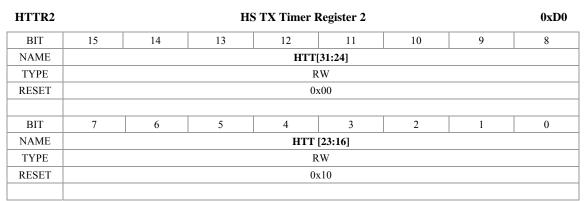

| 8.1.32           | HS TX Timer Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

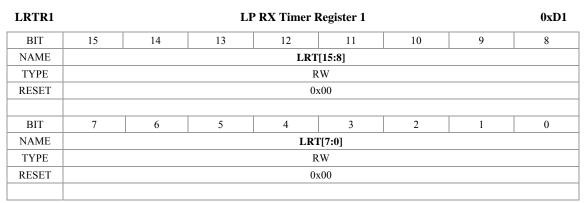

| 8.1.33           | LP RX Timer Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 8.1.34           | LP RX Timer Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 8.1.35           | TE Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 8.1.36           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.1.37           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.1.38           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.1.39           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.1.40           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.1.41           | Analog Control Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 8.1.42           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.1.43           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.1.44           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.1.45           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.1.46           | 5 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 8.1.47           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.1.48           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.1.40<br>8.1.49 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.1.49           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.1.51           | CABC Brightness Control Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 8.1.52           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.1.53           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.1.54           | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.1.55           | 5 5 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 8.1.56           | 8 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 8.1.57           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.1.58           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.1.59           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.1.60           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.1.61           | DLYB01 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.1.62           | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.1.63           | - 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 8.1.64           | - 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 8.1.65           | 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

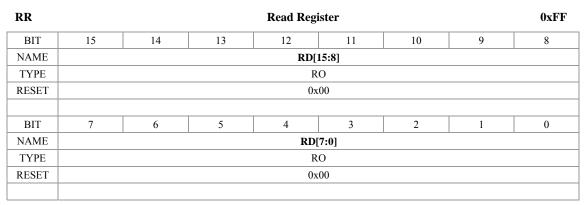

| 8.1.66           | Read Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 9 CON            | FIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 106 |

| <i>y</i> con     | FIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 9.1 L            | ANE MANAGEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 9.2 U            | SE CASES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

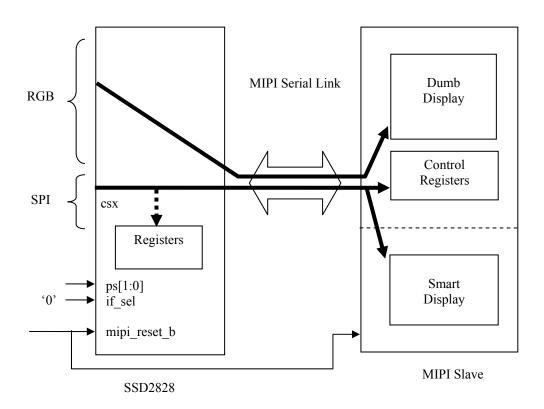

| 9.2.1            | RGB + SPI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

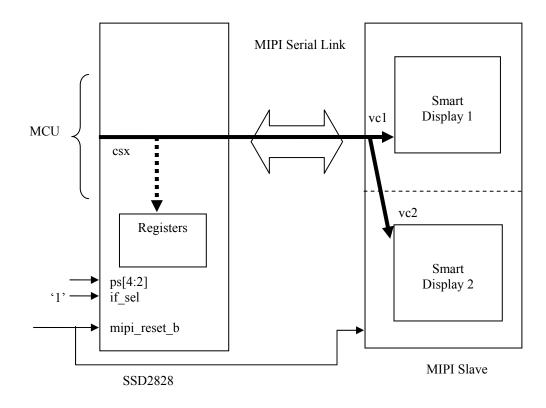

| 9.2.2            | MCU Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 9.2.3            | MIPI DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

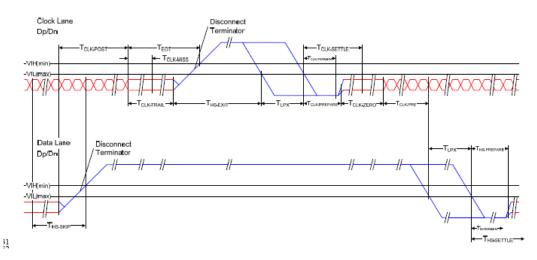

| 9.2.4            | High Speed Clock Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 9.2.5            | Data Lane State Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

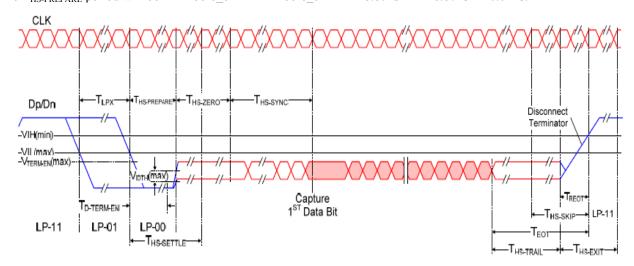

| 9.2.6            | High Speed Data Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 9.2.7            | Bi-Directional Data Lane Turnaround                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

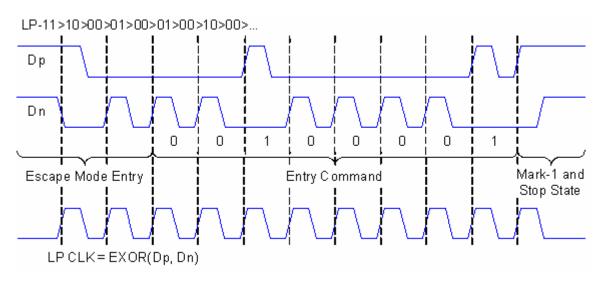

| 9.2.8            | Escape Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 9.2.9            | Low Power Data Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 9.2.10           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 9.2.11           | Tearing Effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 9.2.12           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 9.2.12           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

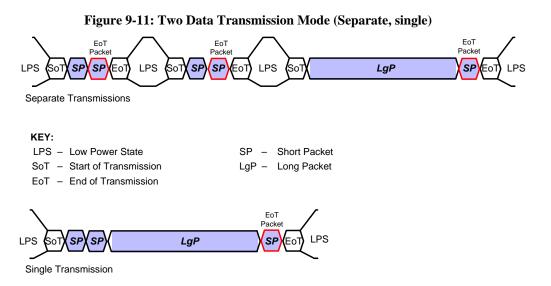

| 9.2.13           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

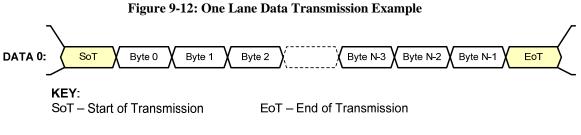

| 9.2.14           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 9.2.15           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 7.2.10           | Long I acher I official contractions and the second s |     |

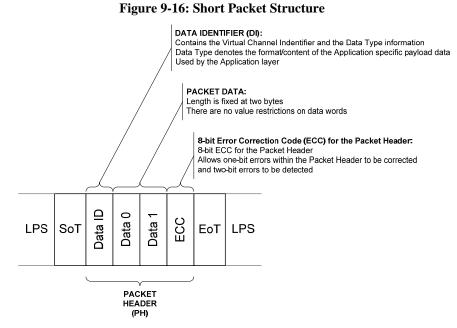

| 9.2  | 2.17 Short Packet Structure                                                                          |     |

|------|------------------------------------------------------------------------------------------------------|-----|

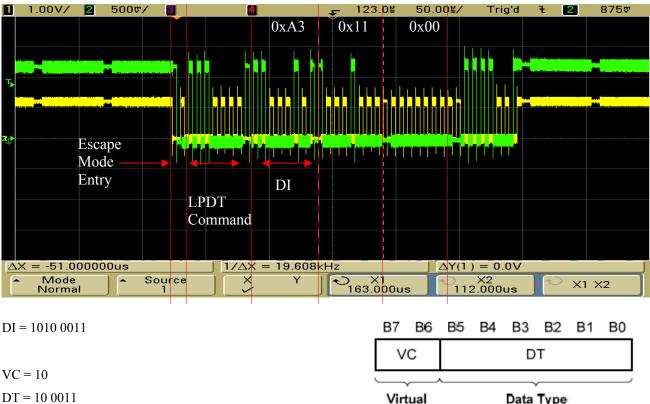

| 9.2  | 2.18 Data Identifier (DI)                                                                            |     |

|      | 2.19 Victual Channel Identifier (VC)                                                                 |     |

|      | 2.20 Data Type (DT)                                                                                  |     |

| 9.3  | OPERATING MODES                                                                                      |     |

|      | 3.2 State machine operation                                                                          |     |

|      | 3.3 D-PHY operation                                                                                  |     |

|      | 3.4 Analog Transceiver                                                                               |     |

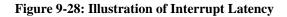

|      | 3.5         PLL           3.6         Clock Source Example                                           |     |

|      | EXTERNAL INTERFACE                                                                                   |     |

| 10   |                                                                                                      | 145 |

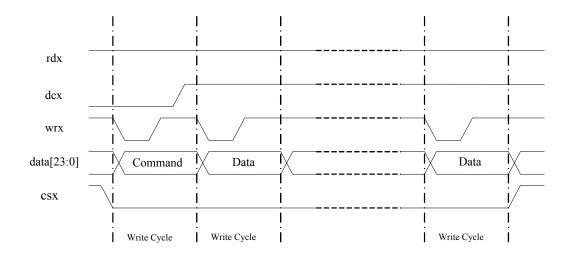

| 10.1 | MCU INTERFACE TYPE A, FIXED E MODE                                                                   |     |

| 10.2 | MCU INTERFACE TYPE A, CLOCKED E MODE                                                                 |     |

| 10.3 | MCU INTERFACE TYPE B                                                                                 |     |

| 10.4 | SPI INTERFACE 8 BIT 4 WIRE                                                                           |     |

| 10.5 | SPI INTERFACE 8 BIT 3 WIRE                                                                           |     |

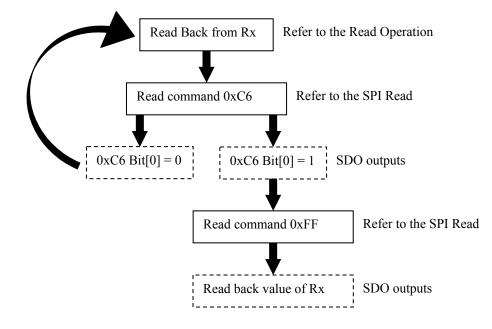

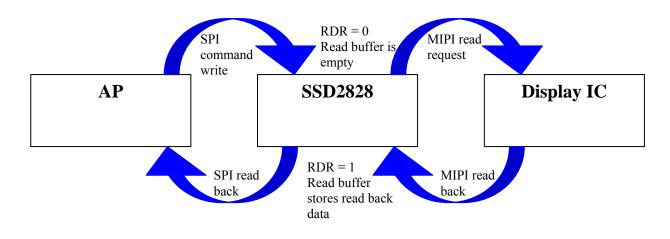

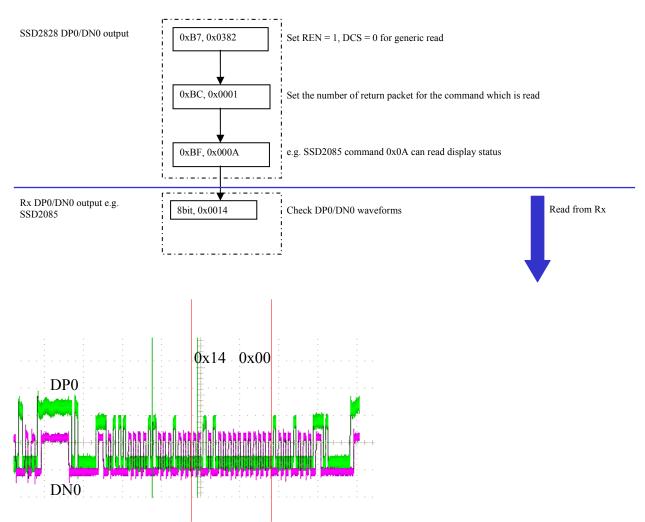

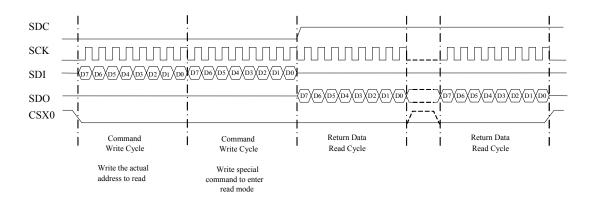

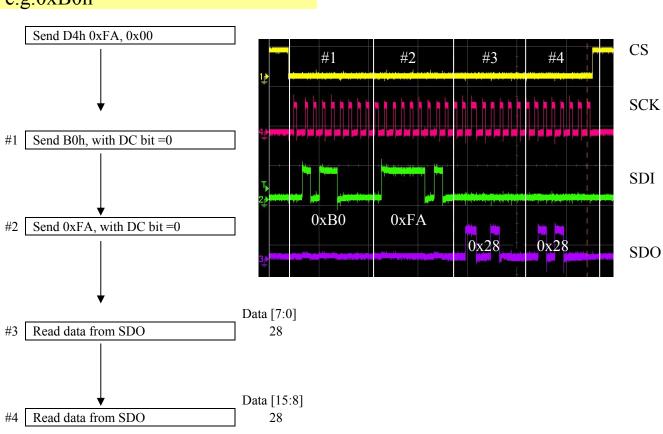

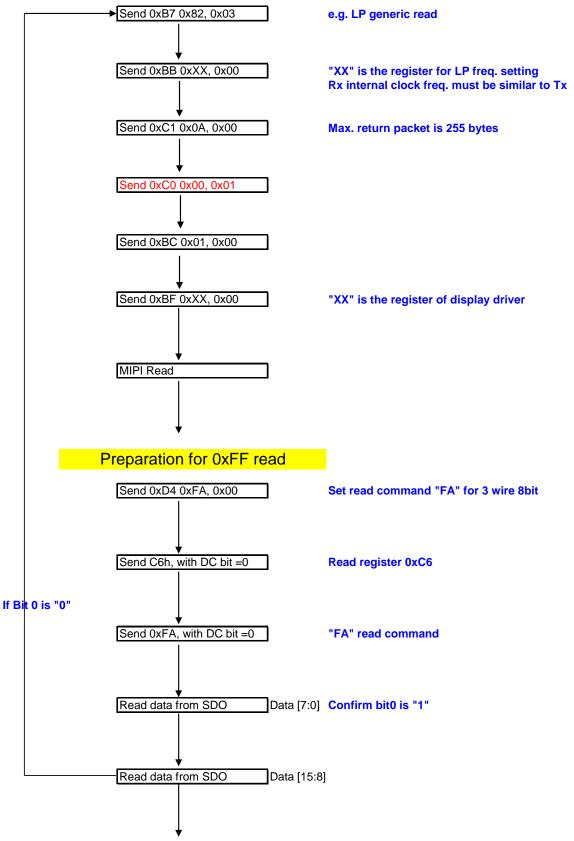

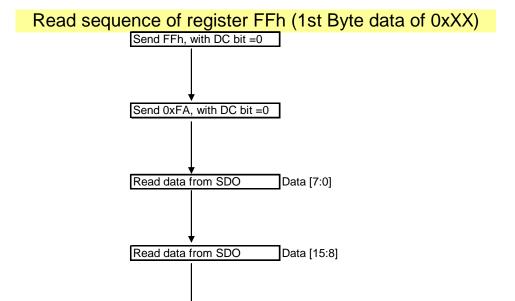

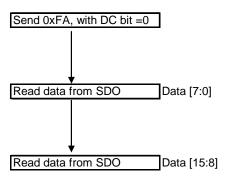

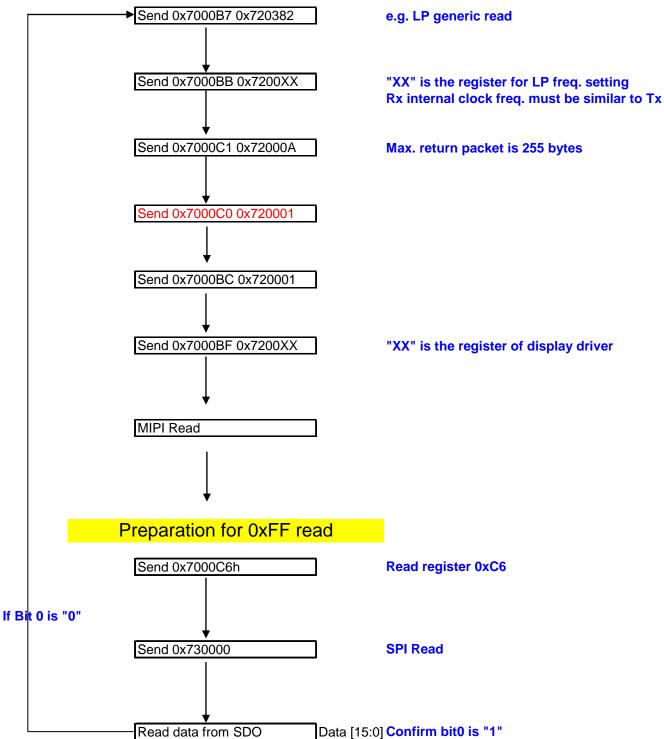

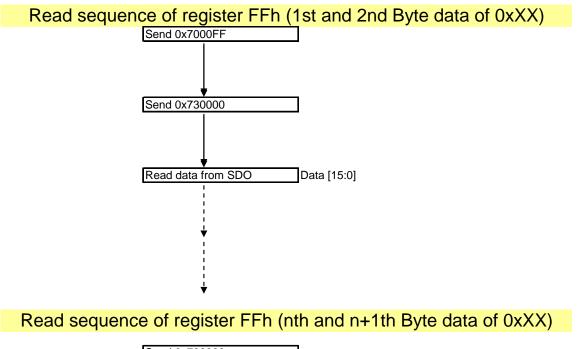

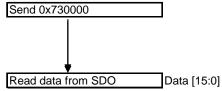

|      | 0.5.1 3 or 4 wires 8bit SPI read back sequence for 0xFF register which is stored MIPI read back data |     |

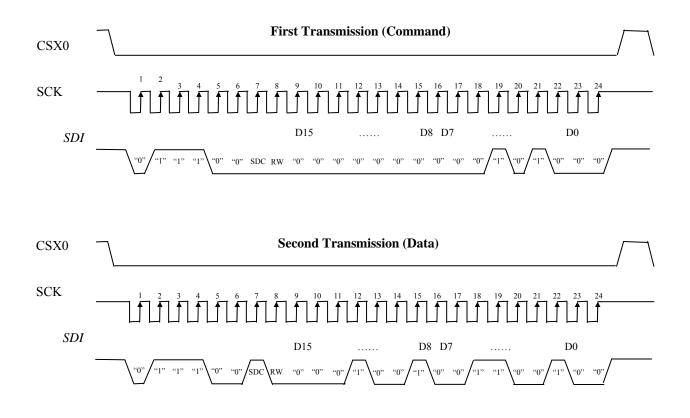

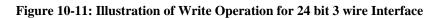

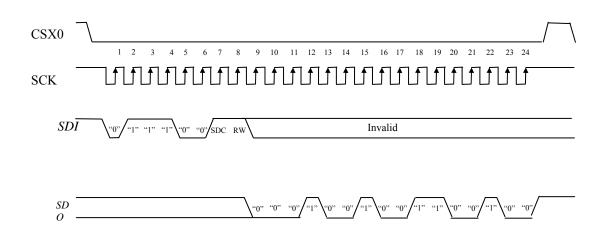

| 10.6 | SPI INTERFACE 24 BIT 3 WIRE                                                                          |     |

|      |                                                                                                      |     |

| 11   | MAXIMUM RATINGS                                                                                      | 160 |

| 12   | RECOMMENDED OPERATING CONDITIONS                                                                     | 161 |

| 14   |                                                                                                      | 101 |

| 13   | DC CHARACTERISTICS                                                                                   | 162 |

| 10   |                                                                                                      |     |

| 14   | AC CHARACTERISTICS                                                                                   | 164 |

| 14.1 | MCU INTERFACE (TYPE A) TIMING                                                                        | 165 |

| 14.2 | MCU INTERFACE (TYPE B) TIMING                                                                        |     |

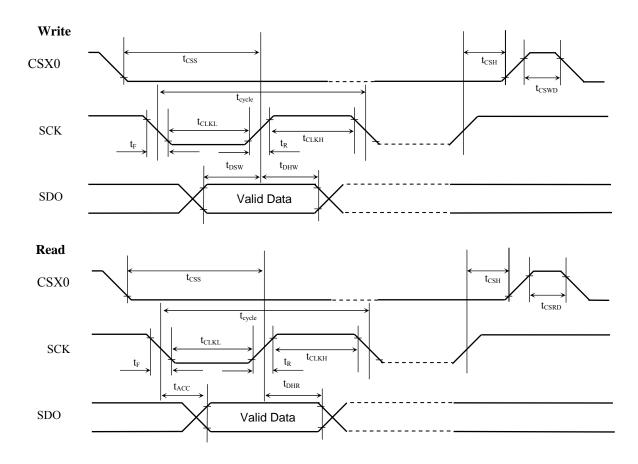

| 14.3 | 8 BIT 4 WIRE SPI INTERFACE TIMING                                                                    |     |

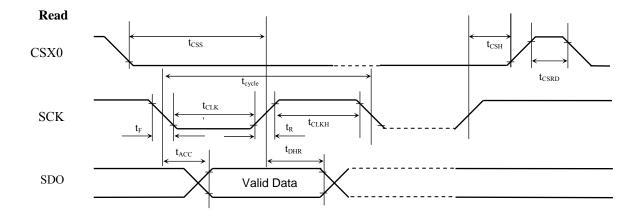

| 14.4 | 8 BIT 3 WIRE SPI INTERFACE TIMING                                                                    | 169 |

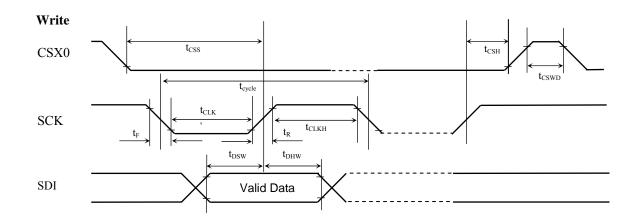

| 14.5 | 24 Bit 3 Wire SPI Interface Timing                                                                   |     |

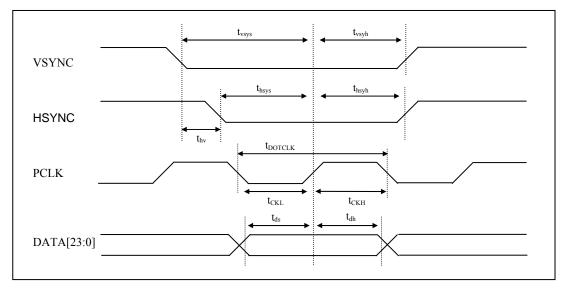

| 14.6 | RGB INTERFACE TIMING                                                                                 |     |

| 14.7 | RESET TIMING                                                                                         |     |

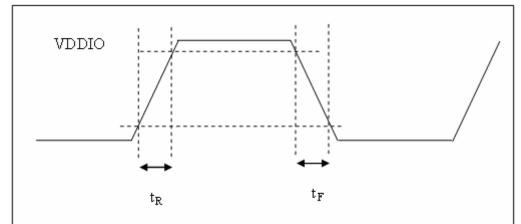

| 14.8 | TX_CLK TIMING                                                                                        | 172 |

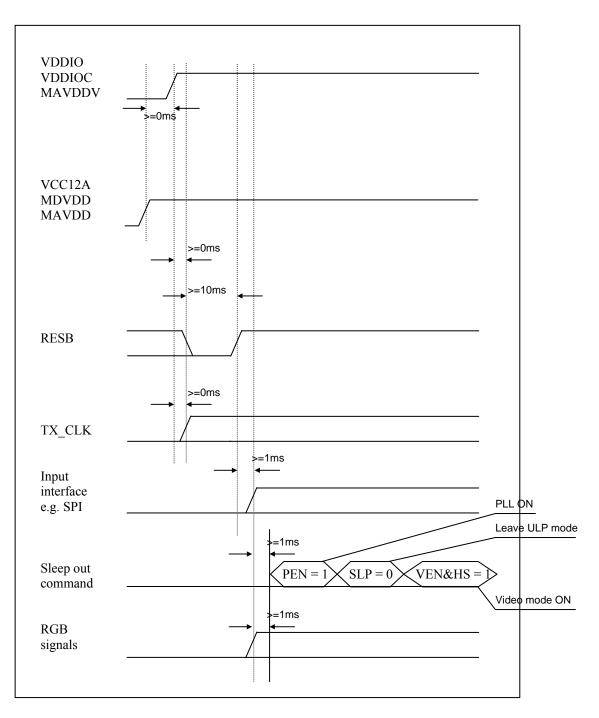

| 15   | POWER UP SEQUENCE                                                                                    | 173 |

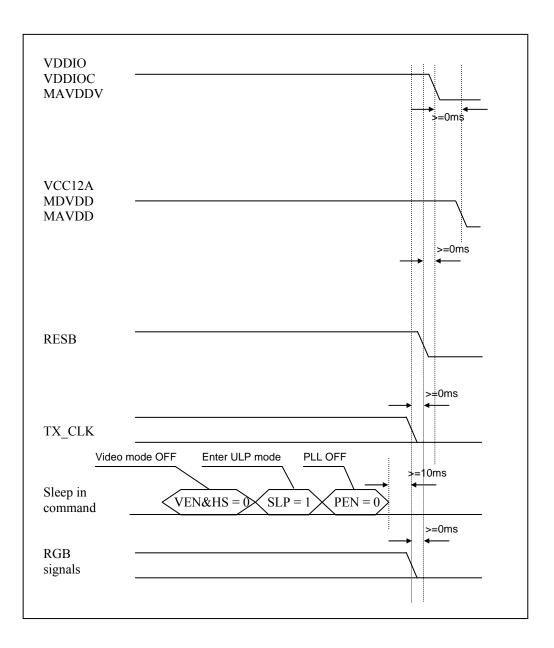

| 16   | POWER OFF SEQUENCE                                                                                   | 174 |

|      |                                                                                                      |     |

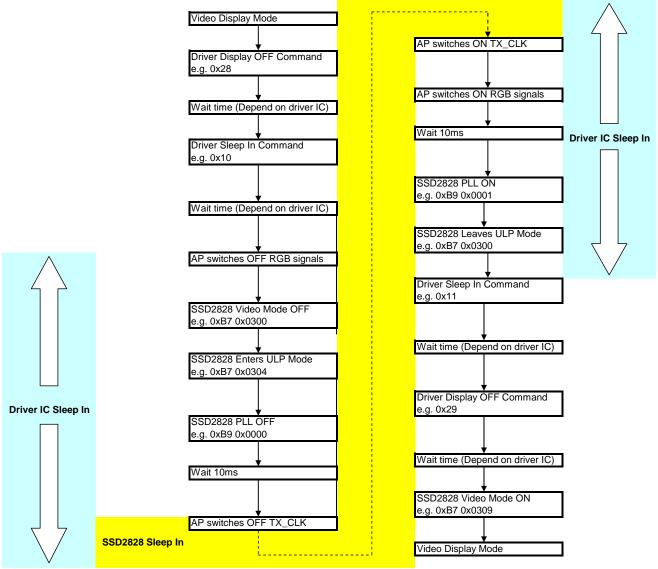

| 17   | EXAMPLE FOR SYSTEM SLEEP IN AND OUT                                                                  | 175 |

| 18   | SERIAL LINK DATA ORDER                                                                               | 176 |

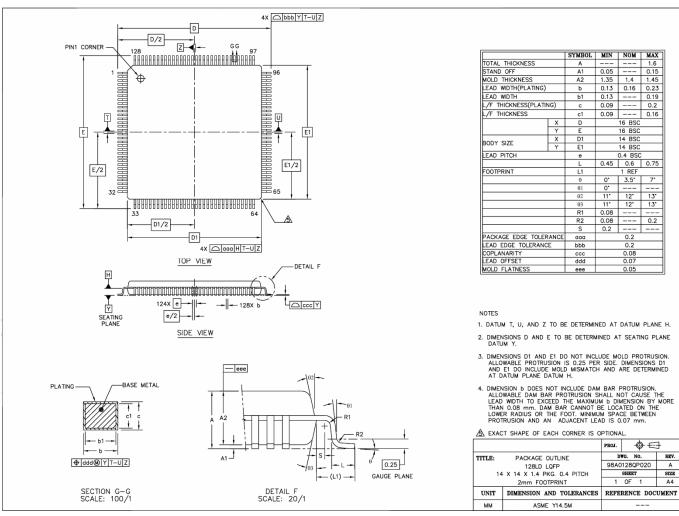

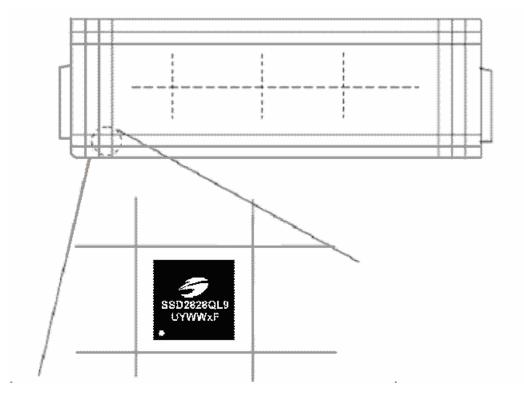

| 19   | PACKAGE INFORMATION                                                                                  | 179 |

| 19.1 | DIMENSION FOR SSD2828                                                                                | 179 |

| 19.1 | MARKING FOR SSD2828                                                                                  |     |

| 19.3 | CHIP TRAY FOR SSD2828                                                                                |     |

|      |                                                                                                      |     |

### TABLES

| TABLE 3-1: ORDERING INFORMATION                                                                                               |    |

|-------------------------------------------------------------------------------------------------------------------------------|----|

| TABLE 6-1: SSD2828 PINOUT DIAGRAM – 128 LQFP                                                                                  | 19 |

| TABLE 6-2: SSD2828 PIN ASSIGNMENT                                                                                             |    |

| TABLE 7-1: MULTIPLEXING SCHEME FOR RGB AND MCU INTERFACE                                                                      |    |

| TABLE 8-1: SSD2828 REGISTER SUMMARY                                                                                           |    |

| TABLE 8-2: DEVICE IDENTIFICATION REGISTER DESCRIPTION                                                                         |    |

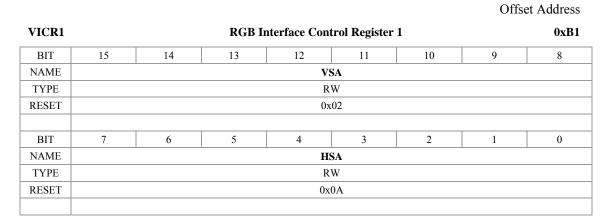

| TABLE 8-3: RGB INTERFACE CONTROL REGISTER 1 DESCRIPTION                                                                       |    |

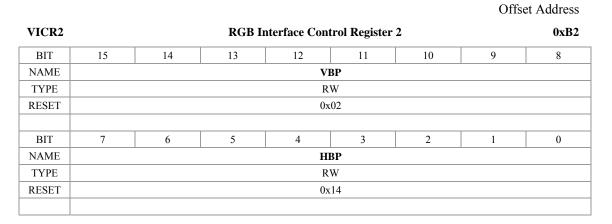

| TABLE 8-4: RGB INTERFACE CONTROL REGISTER 2 DESCRIPTION                                                                       |    |

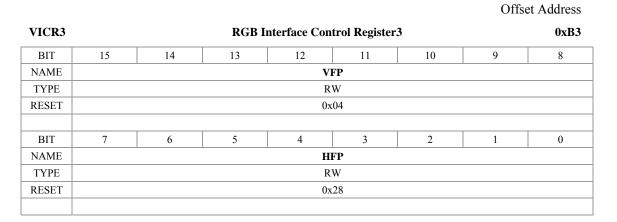

| TABLE 8-5: RGB INTERFACE CONTROL REGISTER 3 DESCRIPTION                                                                       |    |

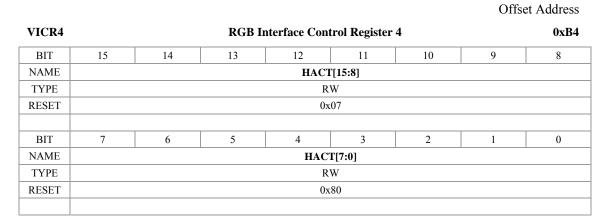

| TABLE 8-6: RGB INTERFACE CONTROL REGISTER 4 DESCRIPTION                                                                       |    |

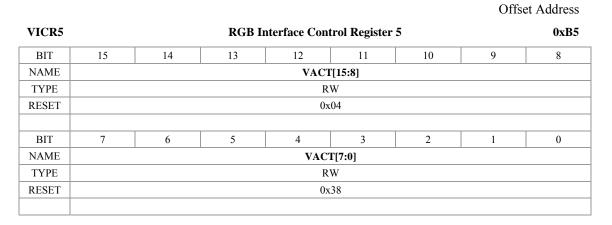

| TABLE 8-7: RGB INTERFACE CONTROL REGISTER 5 DESCRIPTION                                                                       |    |

| TABLE 8-8: RGB INTERFACE CONTROL REGISTER 6 DESCRIPTION                                                                       |    |

| TABLE 8-9: CONFIGURATION REGISTER DESCRIPTION                                                                                 |    |

| TABLE 8-10: VC CONTROL REGISTER DESCRIPTION                                                                                   |    |

| TABLE 8-11: PLL CONTROL REGISTER DESCRIPTION.                                                                                 |    |

| TABLE 8-12: PLL CONFIGURATION REGISTER DESCRIPTION                                                                            |    |

| TABLE 8-13: CLOCK CONTROL REGISTER DESCRIPTION                                                                                |    |

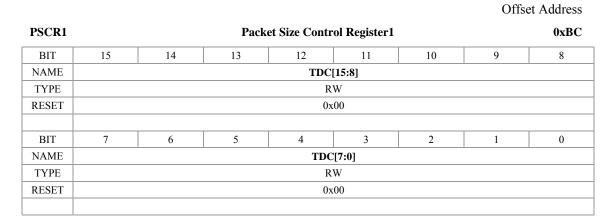

| TABLE 8-14: PACKET SIZE CONTROL REGISTER 1 DESCRIPTION                                                                        |    |

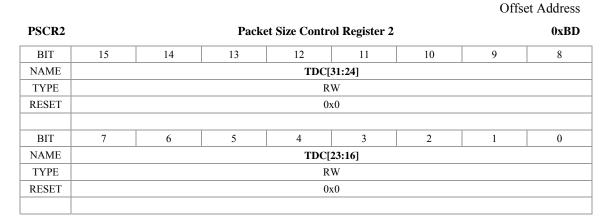

| TABLE 8-15: PACKET SIZE CONTROL REGISTER 2 DESCRIPTION                                                                        |    |

| TABLE 8-16: PACKET SIZE CONTROL REGISTER 3 DESCRIPTION                                                                        |    |

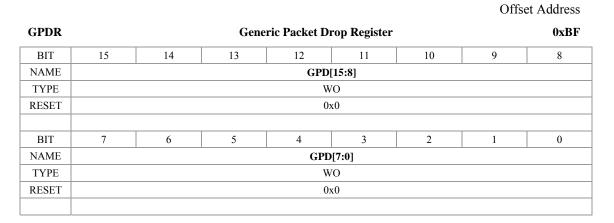

| TABLE 8-17: GENERIC PACKET DROP REGISTER DESCRIPTION                                                                          |    |

| TABLE 8-18: OPERATION CONTROL REGISTER DESCRIPTION       TABLE 8-10. MANUAL OF CONTROL REGISTER DESCRIPTION                   |    |

| TABLE 8-19: MAXIMUM RETURN SIZE REGISTER DESCRIPTION         TABLE 8-20: RETURN DATA COUNT REGISTER DESCRIPTION               |    |

| TABLE 8-20. RETURN DATA COUNT REGISTER DESCRIPTION         TABLE 8-21: ACK RESPONSE STATUS REGISTER DESCRIPTION               |    |

| TABLE 8-21: ACK RESPONSE STATUS REGISTER DESCRIPTION                                                                          |    |

| TABLE 8-22: LINE CONTROL REGISTER DESCRIPTION         TABLE 8-23: INTERRUPT CONTROL REGISTER DESCRIPTION                      |    |

| TABLE 8-23: INTERRUPT CONTROL REGISTER DESCRIPTION         TABLE 8-24: INTERRUPT STATUS REGISTER DESCRIPTION                  |    |

| TABLE 8-24. INTERROPT STATUS REGISTER DESCRIPTION                                                                             |    |

| TABLE 8-26: DELAY ADJUSTMENT REGISTER 1 DESCRIPTION                                                                           |    |

| TABLE 8-200 DELAT ADJUSTMENT REGISTER T DESCRIPTION         TABLE 8-27: DELAY ADJUSTMENT REGISTER 2 DESCRIPTION               |    |

| TABLE 8-28: DELAY ADJUSTMENT REGISTER 2 DESCRIPTION                                                                           |    |

| TABLE 0-20: DELAY ADJUSTMENT REGISTER 0-DESCRIPTION                                                                           |    |

| TABLE 0 2010 DELAY ADJUSTMENT REGISTER 5 DESCRIPTION                                                                          |    |

| TABLE 0-5012 DELAY ADJUSTMENT REGISTER 6 DESCRIPTION                                                                          |    |

| TABLE 8-32: HS TX TIMER REGISTER 1 DESCRIPTION                                                                                |    |

| TABLE 8-33: HS RX TIMER REGISTER 2 DESCRIPTION                                                                                |    |

| TABLE 8-34: LP TX TIMER REGISTER 1 DESCRIPTION                                                                                | 66 |

| TABLE 8-35: LP TX TIMER REGISTER 2 DESCRIPTION                                                                                | 67 |

| TABLE 8-36: TE STATUS REGISTER DESCRIPTION                                                                                    | 68 |

| TABLE 8-37: SPI READ REGISTER DESCRIPTION                                                                                     | 69 |

| TABLE 8-38: PLL LOCK REGISTER DESCRIPTION                                                                                     | 70 |

| TABLE 8-39: TEST REGISTER DESCRIPTION                                                                                         | 71 |

| TABLE 8-40: TE COUNT REGISTER DESCRIPTION                                                                                     |    |

| TABLE 8-41: ANALOG CONTROL 1 REGISTER DESCRIPTION                                                                             |    |

| TABLE 8-42: ANALOG CONTROL REGISTER 2 DESCRIPTION                                                                             |    |

| TABLE 8-43: ANALOG CONTROL REGISTER 3 DESCRIPTION                                                                             |    |

| TABLE 8-44: ANALOG CONTROL REGISTER 4 DESCRIPTION                                                                             |    |

| TABLE 8-45: INTERRUPT OUTPUT CONTROL REGISTER DESCRIPTION                                                                     |    |

| TABLE 8-46: RGB INTERFACE CONTROL REGISTER 7 DESCRIPTION                                                                      |    |

| TABLE 8-47: LANE CONFIGURATION REGISTER DESCRIPTION.                                                                          |    |

| TABLE 8-48: DELAY ADJUSTMENT REGISTER 7 DESCRIPTION.                                                                          |    |

| TABLE 8-49: PULL CONTROL REGISTER 1 DESCRIPTION                                                                               |    |

| TABLE 8-50: PULL CONTROL REGISTER 2 DESCRIPTION       TABLE 8-51: PULL CONTROL REGISTER 2 DESCRIPTION                         |    |

| TABLE 8-51: PULL CONTROL REGISTER 3 DESCRIPTION         TABLE 8-52: CABC BRIGHTNESS CONTROL REGISTER 1 DESCRIPTION            |    |

| TABLE 8-52: CABC BRIGHTNESS CONTROL REGISTER 1 DESCRIPTION         TABLE 8-53: CABC BRIGHTNESS CONTROL REGISTER 2 DESCRIPTION |    |

| TABLE 8-53: CABC BRIGHTNESS CONTROL REGISTER 2 DESCRIPTION         TABLE 8-54: CABC BRIGHTNESS STATUS REGISTER DESCRIPTION    |    |

| TADLE 0-34. CADC DRIGHTNESS STATUS REGISTER DESCRIPTION                                                                       |    |

| TABLE 8-55: ENCODER CONTROL REGISTER DESCRIPTION                        |     |

|-------------------------------------------------------------------------|-----|

| TABLE 8-56: VIDEO SYNC DELAY REGISTER DESCRIPTION                       | 90  |

| TABLE 8-57: TRIMMING REGISTER DESCRIPTION                               | 91  |

| TABLE 8-58: GPIO1 REGISTER DESCRIPTION                                  | 93  |

| TABLE 8-59: GPIO1 REGISTER DESCRIPTION                                  |     |

| TABLE 8-60: DLYA01 REGISTER DESCRIPTION                                 |     |

| TABLE 8-61: DLYA23 REGISTER DESCRIPTION                                 |     |

| TABLE 8-62: DLYB01 REGISTER DESCRIPTION                                 |     |

| TABLE 8-63: DLYB23 REGISTER DESCRIPTION                                 |     |

| TABLE 8-64: DLYC01 REGISTER DESCRIPTION                                 |     |

| TABLE 8-65: DLYC23 REGISTER DESCRIPTION                                 |     |

| TABLE 8-66: ACR5 REGISTER DESCRIPTION                                   | 103 |

| TABLE 8-67: READ REGISTER DESCRIPTION                                   | 105 |

| TABLE 9-1: SSD2828 LANE MANAGEMENT                                      |     |

| TABLE 9-2: OPERATION DURING VIDEO MODE BLLP PERIOD                      | 108 |

| TABLE 9-3: DSI STATE CODE AND DC CHARACTERISTICS                        | 110 |

| TABLE 9-4: DATA LANE MODE ENTERING/EXITING SEQUENCES                    | 111 |

| TABLE 9-5: START-OF-TRANSMISSION SEQUENCE                               | 112 |

| TABLE 9-6: End-of-Transmission Sequence                                 | 112 |

| TABLE 9-7: MIPI ESCAPE MODE ENTRY CODE                                  |     |

| TABLE 9-8: DATA TYPES FOR PROCESSOR-SOURCED PACKETS                     | 123 |

| TABLE 9-9: DATA TYPES FOR PERIPHERAL-SOURCED PACKETS                    | 124 |

| TABLE 9-10: PLL SETTING FOR NON-BURST MODE (PLL REFERENCE USING PCLK)   | 128 |

| TABLE 9-11: PLL SETTING FOR NON-BURST MODE (PLL REFERENCE USING TX_CLK) | 128 |

| TABLE 9-12: PLL SETTING FOR BURST MODE                                  | 129 |

| TABLE 9-13: MIPI ERROR REPORT                                           |     |

| TABLE 10-1: MCU INTERFACE DATA PIN MAPPING FOR PARAMETER CYCLE          |     |

| TABLE 11-1: MAXIMUM RATINGS (VOLTAGE REFERENCED TO V <sub>SS</sub> )    | 160 |

| TABLE 12-1: RECOMMENDED OPERATING CONDITIONS                            | 161 |

| TABLE 13-1: DC CHARACTERISTICS                                          |     |

| TABLE 13-2: HS TRANSMITTER DC CHARACTERISTICS                           | 163 |

| TABLE 13-3: LP TRANSMITTER DC CHARACTERISTICS                           | 163 |

| TABLE 13-4: LP RECEIVER DC CHARACTERISTICS                              |     |

| TABLE 14-1: MCU INTERFACE (TYPE A) TIMING CHARACTERISTICS               | 165 |

| TABLE 14-2: MCU INTERFACE (TYPE B) TIMING CHARACTERISTICS               | 166 |

| TABLE 14-3: 8 BIT 4 WIRE SPI INTERFACE TIMING CHARACTERISTICS.          | 167 |

| TABLE 14-4: 8 BIT 3 WIRE SPI INTERFACE TIMING CHARACTERISTICS           | 169 |

| TABLE 14-5: 24 BIT 3 WIRE SPI INTERFACE TIMING CHARACTERISTICS.         |     |

| TABLE 14-6: RGB INTERFACE TIMING CHARACTERISTICS                        | 171 |

| TABLE 14-7: RESET TIMING                                                |     |

| TABLE 14-8: TX_CLK TIMING CHARACTERISTICS                               |     |

### FIGURES

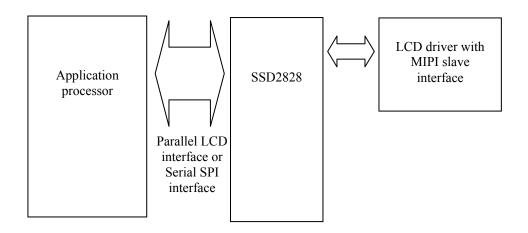

| FIGURE 4-1: OVERVIEW OF DISPLAY SYSTEM USING SSD2828                                            | 12  |

|-------------------------------------------------------------------------------------------------|-----|

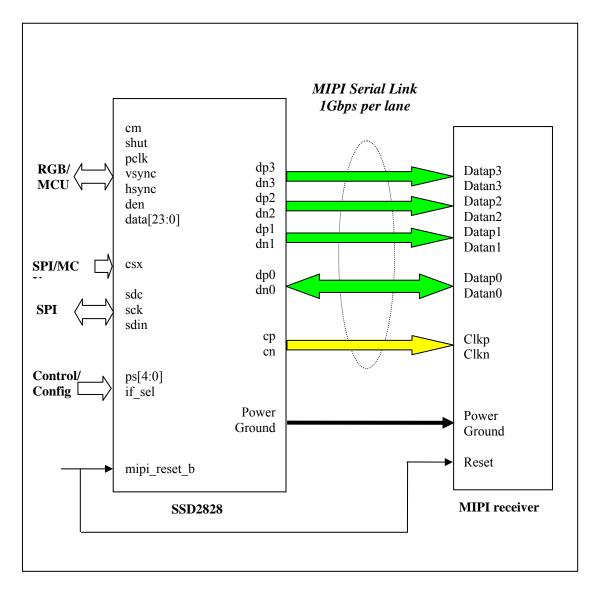

| FIGURE 4-2: SSD2828 INTERFACE DIAGRAM                                                           |     |

| FIGURE 4-3: BLOCK DIAGRAM                                                                       |     |

| FIGURE 5-1: THE CLOCKING SCHEME OF SSD2828                                                      |     |

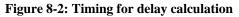

| FIGURE 8-1: TIMING FOR DELAY CALCULATION                                                        |     |

| FIGURE 8-2: TIMING FOR DELAY CALCULATION                                                        |     |

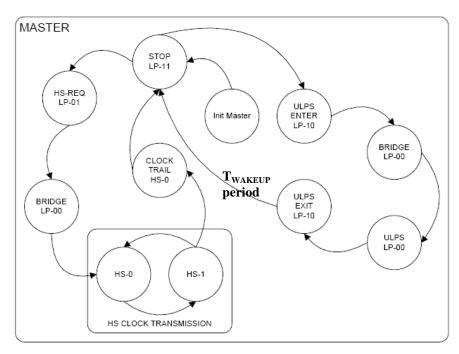

| FIGURE 8-3: T <sub>WAKEUP</sub> PERIOD DELAY CALCULATION                                        |     |

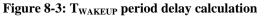

| FIGURE 8-4: TIMING FOR DELAY CALCULATION                                                        |     |

| FIGURE 9-1: SSD2828 WITH RGB AND SPI INTERFACE                                                  |     |

| FIGURE 9-2: SSD2828 WITH MCU INTERFACE                                                          |     |

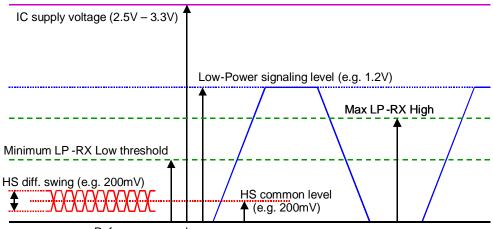

| FIGURE 9-3: MIPI LINE LEVELS                                                                    |     |

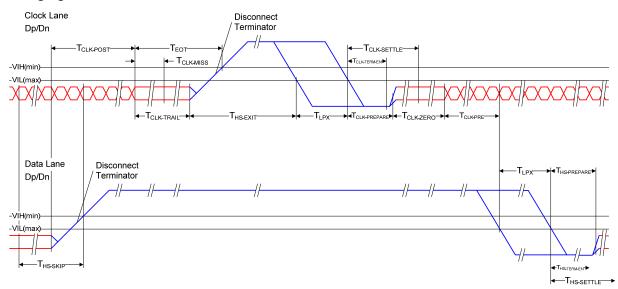

| FIGURE 9-4: SWITCHING THE CLOCK LANE BETWEEN HIGH SPEED MODE AND LOW-POWER MODE                 |     |

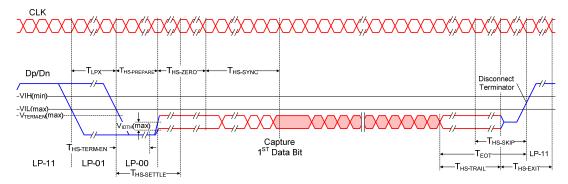

| FIGURE 9-5: HIGH-SPEED DATA TRANSMISSION IN BURSTS                                              |     |

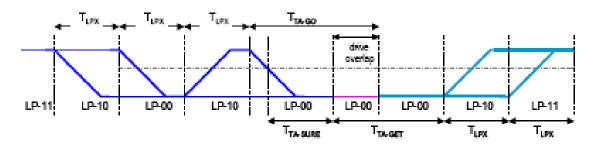

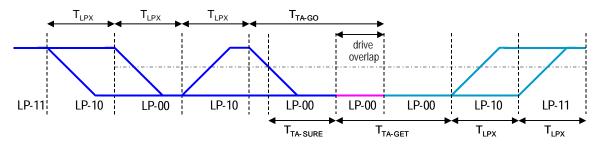

| FIGURE 9-6: TURNAROUND PROCEDURE                                                                |     |

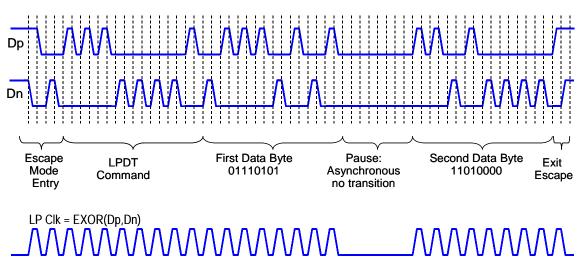

| FIGURE 9-7: LOW POWER DATA TRANSMISSION                                                         |     |

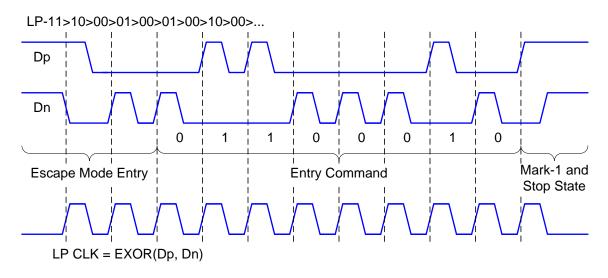

| FIGURE 9-8: TRIGGER – RESET COMMAND IN ESCAPE MODE                                              |     |

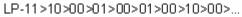

| FIGURE 9-9: TEARING EFFECT COMMAND IN ESCAPE MODE                                               |     |

| FIGURE 9-10: ACKNOWLEDGE COMMAND IN ESCAPE MODE                                                 |     |

| FIGURE 9-11: TWO DATA TRANSMISSION MODE (SEPARATE, SINGLE)                                      |     |

| FIGURE 9-12: ONE LANE DATA TRANSMISSION EXAMPLE                                                 |     |

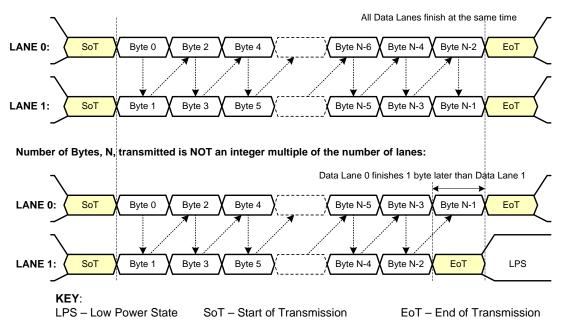

| Figure 9-13: Two Lane HS Transmission Example<br>Figure 9-14: Endian Example (Long Packet)      |     |

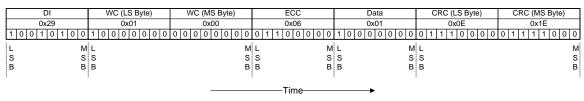

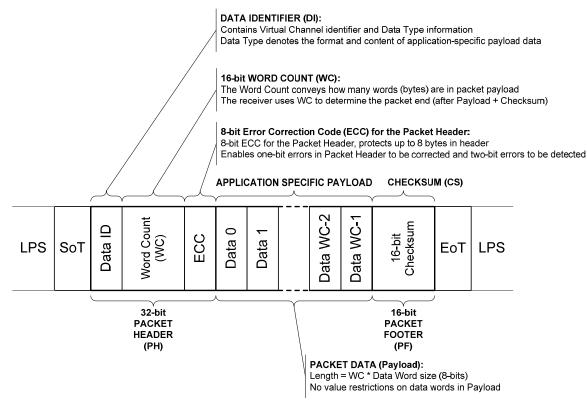

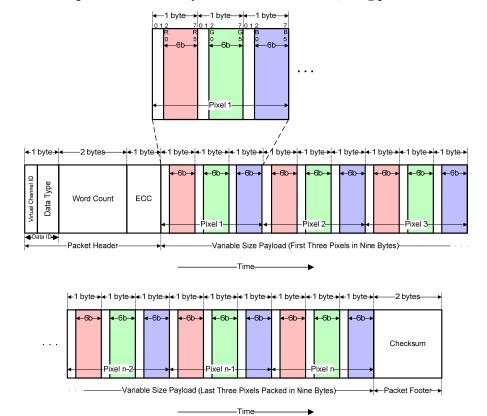

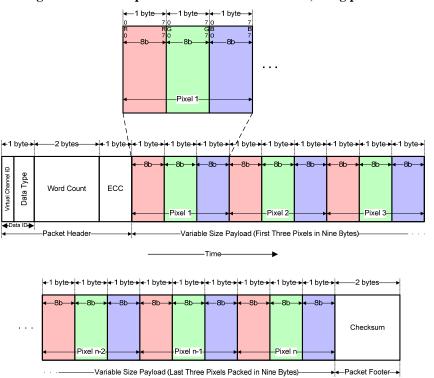

| FIGURE 9-14. ENDIAN EXAMPLE (LONG PACKET)<br>FIGURE 9-15: LONG PACKET STRUCTURE                 |     |

| FIGURE 9-15: LONG PACKET STRUCTURE                                                              |     |

| Figure 9-17: Data Indentifier Structure                                                         |     |

| FIGURE 9-17: DATA INDENTIFIER STRUCTORE                                                         |     |

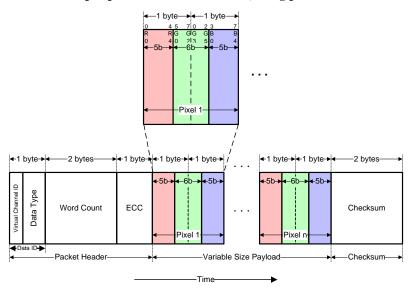

| Figure 9-19: 18-bit per Pixel – RGB Color Format, Long packet for MIPI Interface                |     |

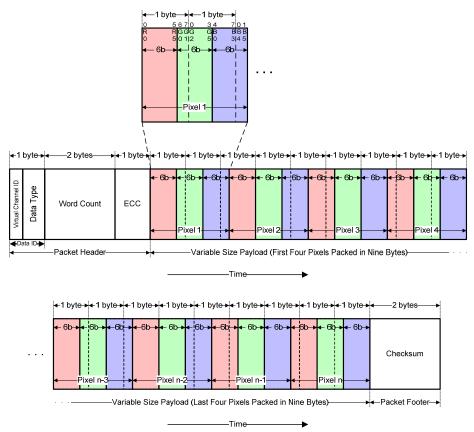

| FIGURE 9-20: 18-BIT PER PIXEL IN THREE BYTES – RGB COLOR FORMAT, LONG FACKET FOR MIT FINTER ACE |     |

| Figure 9-21: 24-bit per Pixel – RGB Color Format, Long packet for MIPI Interface                |     |

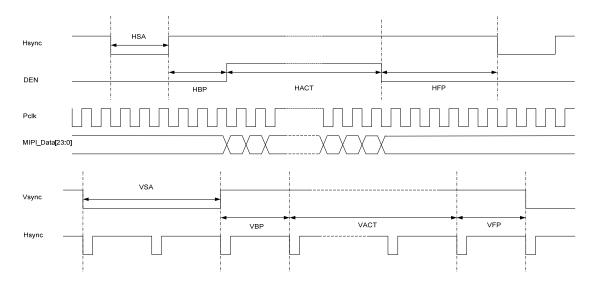

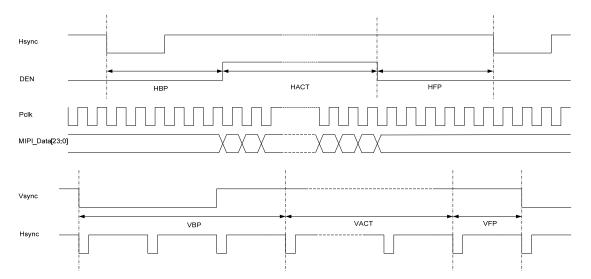

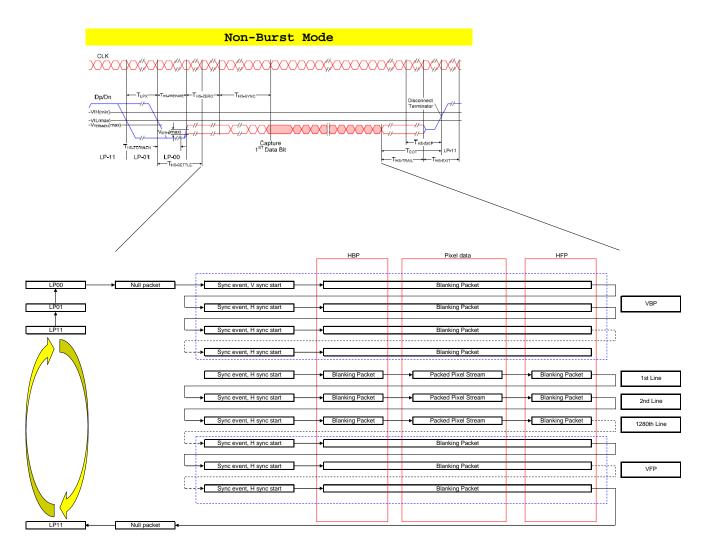

| Figure 9-22: Illustration of RGB Interface Parameters for Non-burst Mode with Sync Pulses       |     |

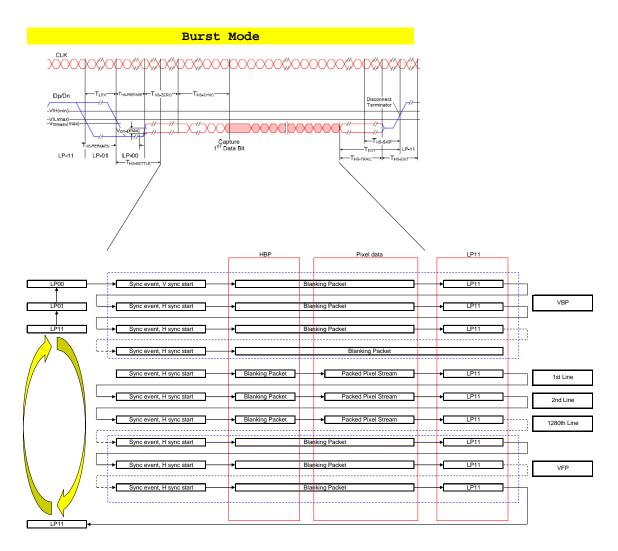

| Figure 9-23: Illustration of RGB Interface Parameters for Non-Burst Mode with Sync Events and B |     |

| Mode                                                                                            |     |

| FIGURE 9-24: NON-BURST MODE MIPI STRUCTURE                                                      |     |

| FIGURE 9-25: BURST MODE MIPI STRUCTURE                                                          |     |

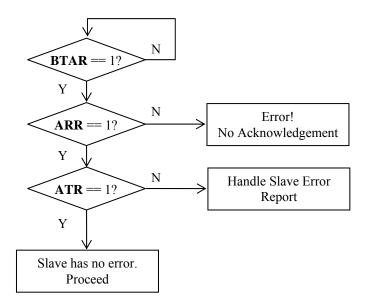

| FIGURE 9-26: ACKNOWLEDGEMENT HANDLING AFTER NON-READ COMMAND                                    |     |

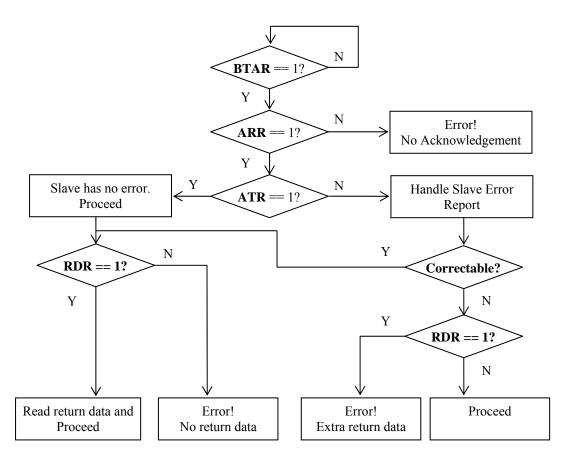

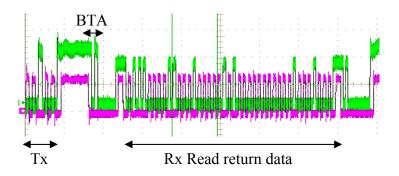

| FIGURE 9-27: ACKNOWLEDGEMENT HANDLING AFTER READ COMMAND                                        |     |

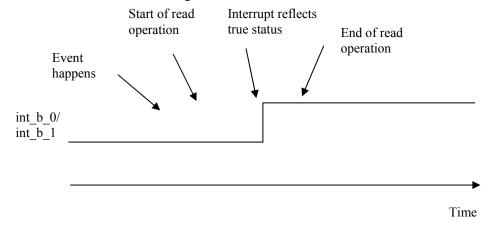

| FIGURE 9-28: ILLUSTRATION OF INTERRUPT LATENCY                                                  | 140 |

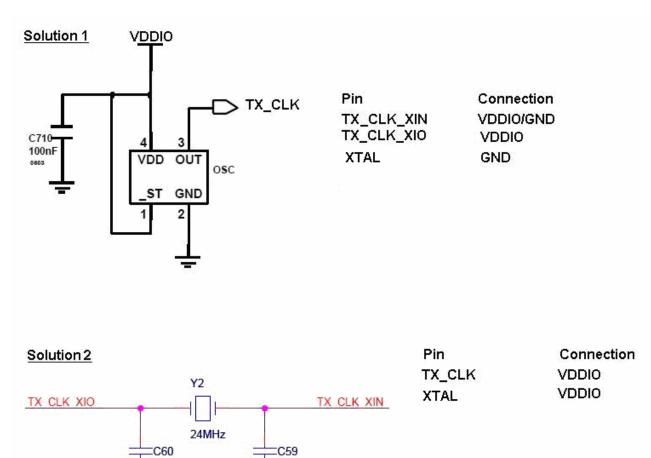

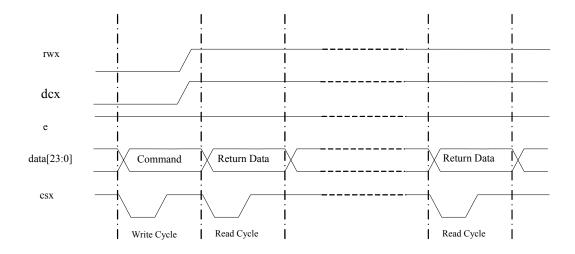

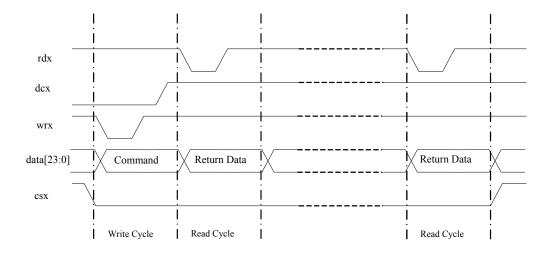

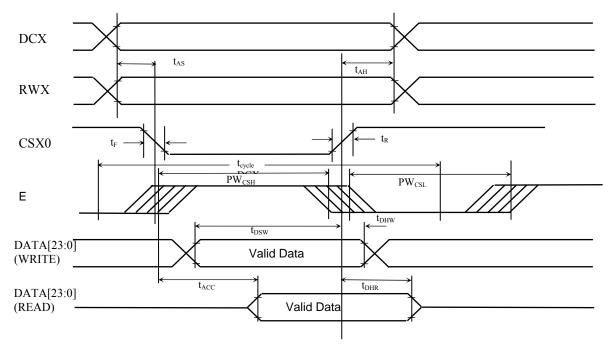

| FIGURE 10-1: ILLUSTRATION OF WRITE OPERATION FOR TYPE A, FIXED E MODE INTERFACE                 | 146 |

| FIGURE 10-2: ILLUSTRATION OF READ OPERATION FOR TYPE A, FIXED E MODE INTERFACE                  | 146 |

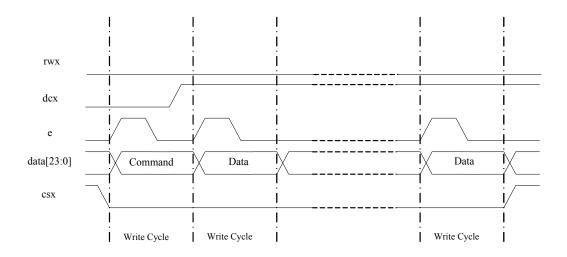

| FIGURE 10-3: ILLUSTRATION OF WRITE OPERATION FOR TYPE A, CLOCKED E MODE INTERFACE               | 147 |

| FIGURE 10-4: ILLUSTRATION OF READ OPERATION FOR TYPE A, CLOCKED E MODE INTERFACE                | 148 |

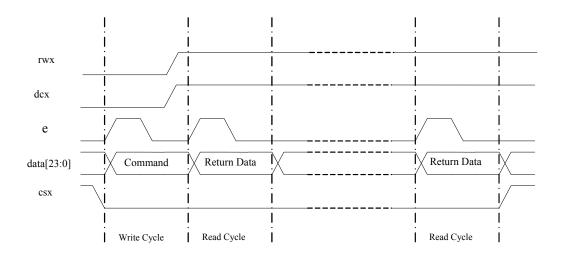

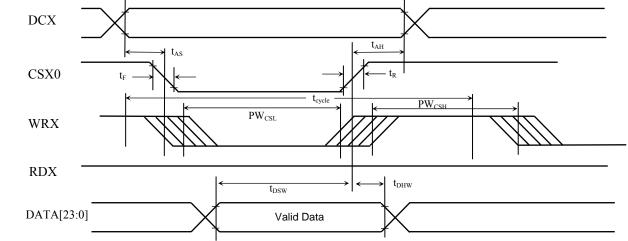

| FIGURE 10-5: ILLUSTRATION OF WRITE OPERATION FOR TYPE B INTERFACE                               | 149 |

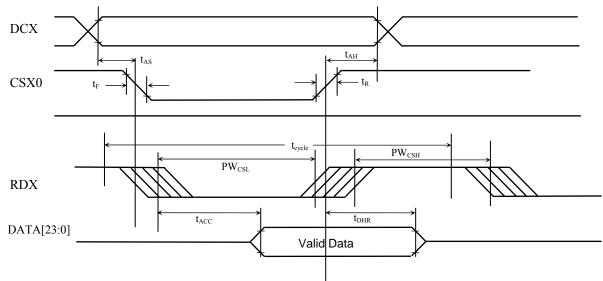

| FIGURE 10-6: ILLUSTRATION OF READ OPERATION FOR TYPE B INTERFACE                                | 149 |

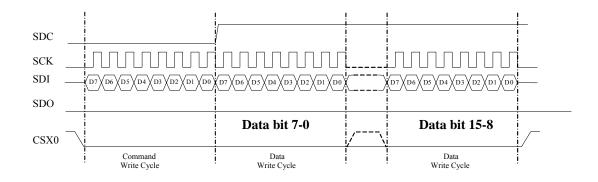

| FIGURE 10-7: ILLUSTRATION OF WRITE OPERATION FOR 8 BIT 4 WIRE INTERFACE                         |     |

| FIGURE 10-8: ILLUSTRATION OF READ OPERATION FOR 8 BIT 4 WIRE INTERFACE                          |     |

| FIGURE 10-9: ILLUSTRATION OF WRITE OPERATION FOR 8 BIT 3 WIRE INTERFACE                         |     |

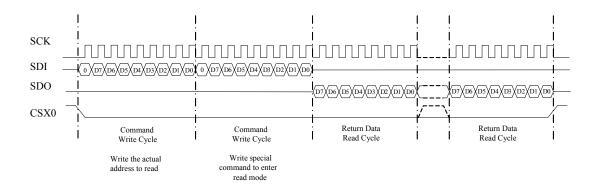

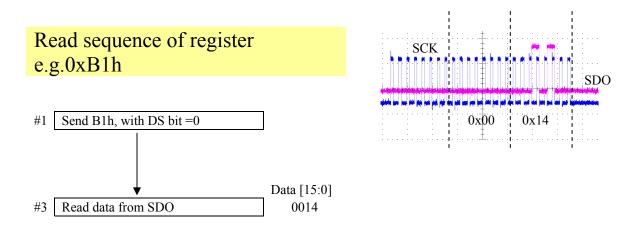

| FIGURE 10-10: ILLUSTRATION OF READ OPERATION FOR 8 BIT 3 WIRE INTERFACE                         |     |

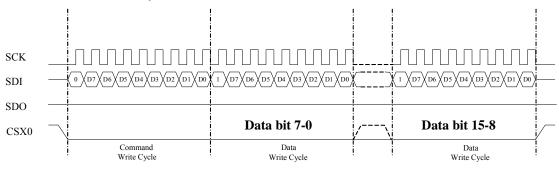

| FIGURE 10-11: ILLUSTRATION OF WRITE OPERATION FOR 24 BIT 3 WIRE INTERFACE                       |     |

| FIGURE 10-12: ILLUSTRATION OF READ OPERATION FOR 24 BIT 3 WIRE INTERFACE                        |     |

| FIGURE 14-1: MCU INTERFACE (TYPE A) TIMING DIAGRAM                                              |     |

| FIGURE 14-2: MCU INTERFACE (TYPE B) TIMING DIAGRAM                                              |     |

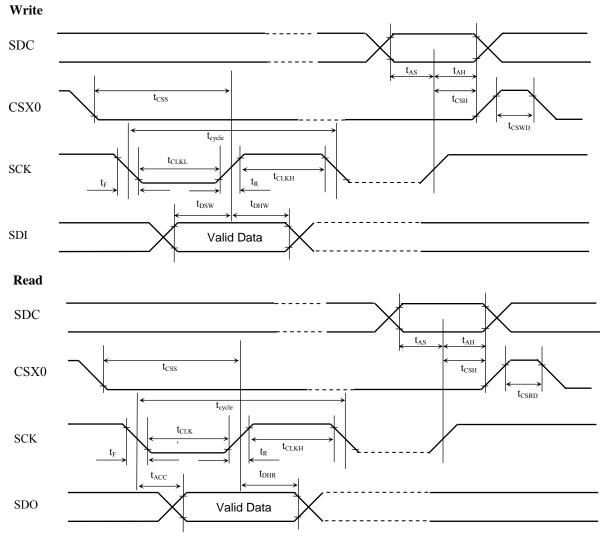

| FIGURE 14-3: 8 BIT 4 WIRE SPI INTERFACE TIMING DIAGRAM                                          |     |

| FIGURE 14-4: 8 BIT 3 WIRE SPI INTERFACE TIMING DIAGRAM                                          |     |

| FIGURE 14-5: 24 BIT 3 WIRE SPI INTERFACE TIMING DIAGRAM                                         |     |

| FIGURE 14-6: RGB INTERFACE TIMING DIAGRAM                                                       |     |

| FIGURE 14-7: TX_CLK TIMING DIAGRAM                                                              |     |

| Figure 19-1- Package Information<br>Figure 19-2- Marking Information                            |     |

|                                                                                                 |     |

| FIGURE 19-3- TRAY INFORMATION |

|-------------------------------|

|                               |

### **1 GENERAL DESCRIPTION**

The SSD2828 IC is an MIPI master bridge chip that connects an application processor with traditional parallel LCD interface and an LCD driver with MIPI slave interface. The 2828 supports up to 1Gbps per lane speed with maximum 4 lanes using both parallel RGB interface and serial SPI interface.

### 2 FEATURES

- Support up to total of 4Gbps over the serial link

- Support up to 4 data lanes

- Number of signals is significantly reduced when compare to traditional RGB/MCU transfer

- Support up to 1920 pixels per display row in Video mode, up to 60hz refresh rate

- Support up to 2560 pixels per display row in Video mode, up to 30hz refresh rate

- Reduce power consumption and decrease EMI by using low amplitude signal over differential pair for serial data.

- Support parallel MCU interface (DBI 2.0) up to 24-bits

- Support parallel RGB interface (DPI 2.0) up to 24-bits

- Support serial SPI interface (DBI 2.0) up to 16-bits

- Support both command mode and video mode in MIPI DSI standard

- Support 16, 18 and 24-bit per pixel in Raw or Pixel mode for command mode transfer

- Support independent bi-directional data transfer (forward link in High Speed and Low Power mode and reverse link in Low Power mode) for each DSI

- Support Ultra low power mode in idle state for each DSI

- Support CABC function for Video mode

- On-chip PLL with variable output frequency

- Power supply: ( $V_{DDD}$  and  $V_{DDA}$ ) 1.2V +/-10%

- IO Power supply: 1.8V to 3.3V +/-10%

- Support of MIPI standard DSI(v1.01.00), DCS(v1.02.00), D-PHY (v1.00.00)

### 2.1 References

- MIPI Alliance Standard for Display Serial Interface, version 1.01

- MIPI Alliance Standard for Display Command Set, version 1.02

- MIPI Alliance Standard for D-PHY, version 1.00

- MIPI Alliance Standard for Display Bus Interface, version 2.0

- MIPI Alliance Standard for Display Pixel Interface, version 2.0

### 2.2 Definitions

- HS High Speed

- SPI Type C interface option 1 of MIPI Alliance Standard for Display Bus Interface v2.0 (DBI-2)

- LP Low Power

- MCU Type B interface of MIPI Alliance Standard for Display Bus Interface v2.0 (DBI-2)

- ULPS Ultra Low Power State

- RGB MIPI Alliance Standard for Display Pixel Interface v2.0 (DPI-2)

- VC Virtual Channel

### **3 ORDERING INFORMATION**

| Table 3-1: | Ordering | Information |