October 2013 Revision 1.15

# NPCA110P Audio Enhancing Engine and CODEC

### **General Description**

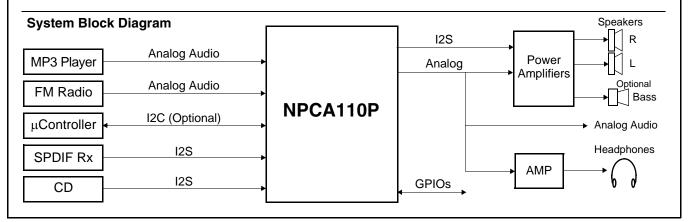

The Nuvoton NPCA110P device is a member of Nuvoton's Sound Enhancing family optimized for portable devices such as docking stations for MP3-players and mobile phones, Multi-Media speakers, PC monitor speakers and Boom boxes.

The NPCA110P integrates Waves<sup>®</sup> MaxxAudio 3 sound enhancement algorithms. These are proprietary, patented, psychoacoustic algorithms that compensate for the acoustic limitations of small CE devices.

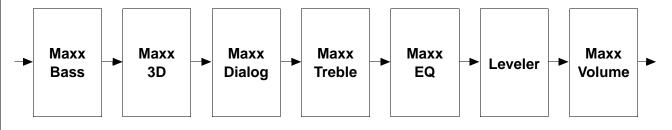

The MaxxAudio 3 algorithms enable reproduction of rich content, with a wide dynamic range and a full frequency range, on a limited audio system. For low-frequency reproduction, MaxxBass® uses a patented psychoacoustic technique to create a perceived low bass, which can be extended up to 1.5 octaves lower than the original. This technique reproduces full and rich sounding bass tones. Power handling is done by MaxxVolume®, which utilizes the power amplifiers and speakers to their full extent yet avoids clipping and distortions.

The MaxxAudio 3 software suite provides additional algorithms that enhance the overall sound quality, such as Maxx3D, which widens the stereo image, and MaxxTreble, for reproducing crystal clear high frequencies. To design a resonance-free audio system, MaxxEQ provides a flexible equalizer with 10 bands.

The NPCA110P enables digital control over the Volume and Bass, replacing traditional analog potentiometers. Additional digital controls for selecting a specific music style (Jazz, Vocal, Rap, Classical, etc.) can also be added.

The Maxx family of devices includes:

- High-performance, 24-bit audio enhancing engine preprogrammed with Waves MaxxAudio 3 algorithms

- Optional Audio ADC

- Optional Audio DAC

- Digital I/O and other features for high-performance audio systems

The MaxxAudio Graphical User Interface (GUI) enables sound engineers to easily tune the device and customize presettings for different audio products.

### **Outstanding Features**

- Improves audio quality for low-performance speakers

- System-level BOM savings

- Stereo operation

- I2C controlled

- 24-bit accuracy

- Audio algorithms

- WMAXXBASS®

- ─ MAXXTREBLE

- MAXXEQ

- MAXXLEVELER

- WMAXXDIALOG

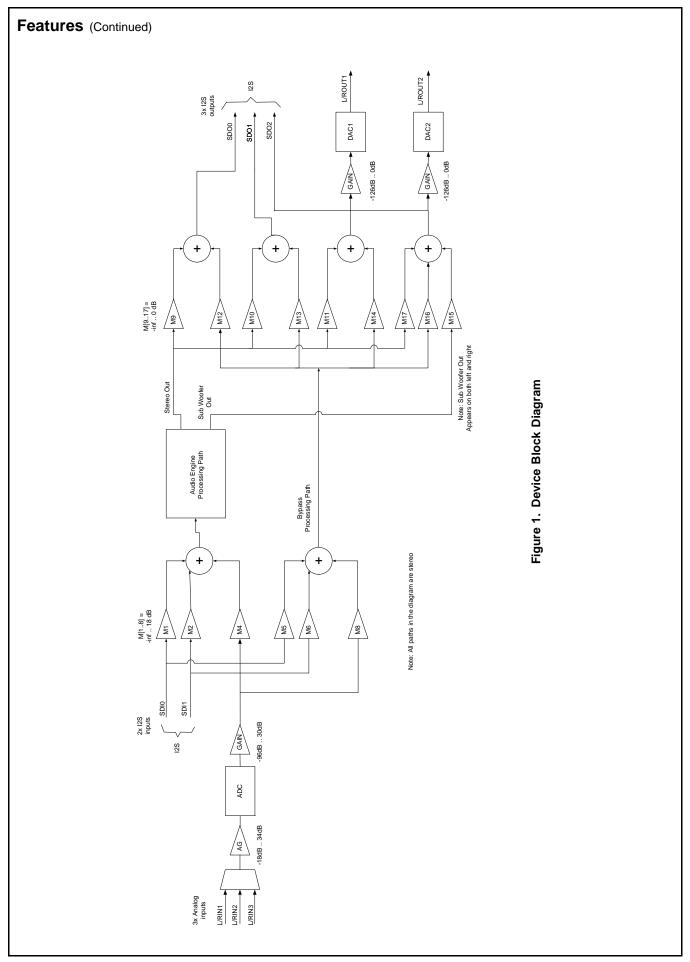

- Audio input

- Up to three I2S or Synchronous Serial Interface (SSI) inputs

- Up to three stereo analog inputs: typical SNR of 90 dB; typical THD of –75 dB

- Audio output

- Optional generation of bass channel for sub-woofer

- Up to three I2S or SSI outputs

- Up to four analog outputs: typical SNR of 96 dB; typical THD of –86 dB

- Several General-Purpose digital signals available to the application (GPIOs)

- Typical operational power target of less than 0.2W

- Power-down target of less than 1 mW

- 3.3V operation

#### **Features**

#### **Bus Interfaces**

- Synchronous Serial Interface (SSI)

- Compatible with I2S

- Master and slave timing support

- I2C Interface

- Compliant with I2C-BUS Specification Revision 1.0, 1992

- Master or slave interface

- Supports 7-bit address mode

#### **Audio Enhancing Engine**

- Processing Unit

- 24-bit

- 125 MIPs

#### **Audio Algorithms**

- Sample frequency of 44.1 KHz or 48 KHz

- MaxxBass®

- Patented Waves MaxxBass psycho-acoustic bass extension delivers a more natural sound than traditional bass boost technologies, which use EQ and can overpower your system. MaxxBass analyzes low frequencies to create harmonics that are perceived as lower, deeper tones.

- Maxx3D

- Maxx3D extends the span of stereo-side content while maintaining the integrity of unprocessed center content.

- Maxx3D for Speakers improves the stereo separation of speakers, widening the stereo field for optimal imaging.

- Maxx3D for Headphones improves stereo perception, restoring the original listening balance to provide more natural sound.

#### ■ MaxxTreble

MaxxTreble delivers crystal clear high-frequency enhancement for increased RMS without exceeding the system ceiling. Its proprietary algorithm restores luster to over-compressed formats to provide the perfect listening experience.

#### ■ MayyEC

MaxxEQ provides the ability to design EQ curves and shape sound with surgical precision, using up to 10 programmable filters with bell, shelf, low pass, and high pass, plus adjustable frequency, gain, and Q parameters. MaxxEQ's intuitive Graphic User Interface makes click-and-drag filter design fast and easy.

#### ■ MaxxVolume<sup>®</sup>

MaxxVolume is an all-in-one volume control, with High-Level Compression to increase RMS levels, Low-Level Compression to increase the clarity of soft sounds, Noise Gating to eliminate signal and system noise, and Leveling to smooth out volume levels.

#### MaxxLeveler

MaxxLeveler regulates the perceived volume of the audio, keeping all audio content at the same level.

#### MaxxDialog

MaxxDialog is a revolutionary new technology that enables users to adjust center channel dialog levels without affecting the rest of the audio mix. Based on the Waves Center pro audio plug-in, MaxxDialog delivers clear, crisp dialog that does not disappear behind loud music and sound effects.

#### Sub-Woofer

- Enables separating low-frequency content and directing it into a third audio channel, for driving a subwoofer.

- Filtering to eliminate noise induced by cellular phone transmission

#### Straps, Clocks, Supply and Package Information

- Strap Input Controlled Operating Modes

- PLL reference clock select (REF strap)

- Test mode select (nTEST strap)

- I2C master or slave select (I2CMS strap)

- Boot options

- □ ROM code operation

- Loadable algorithms for new functions or ROM code patching

- Input Clocks

- SSI / I2S clock: 64x of sample frequency

- Optional Crystal oscillator or input clock

- Power Supply

- 3.3V supply operation

- Power-Save Modes

- Clock switch to a lower frequency

- WAIT instruction (clock stopped)

- PLL power-down

#### ■ Package

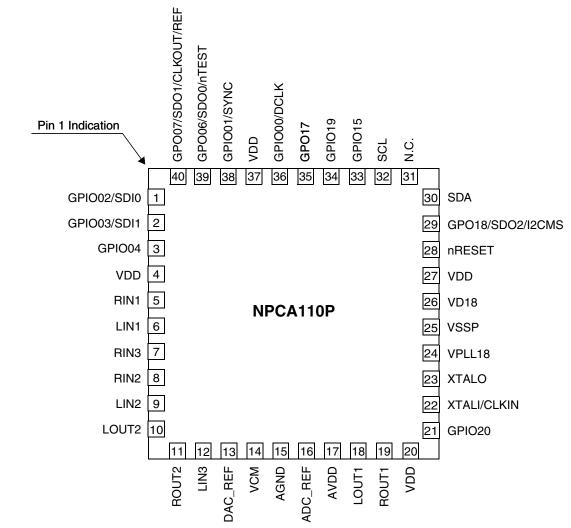

6 x 6 mm, 40-pin Quad Flat No-Lead (QFN) package

### **Algorithm Processing Chain**

## **Revision Record**

| Date          | Status        | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2011 | Revision 0.10 | Datasheet first revision.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| June 2011     | Revision 0.75 | <ul> <li>Added algorithm processing Chain diagram</li> <li>Added block diagram</li> <li>Added Clocks section in Chapter 2</li> <li>Added current consumption in Electrical Specification</li> <li>Various small changes</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| August 2011   | Revision 0.80 | <ul> <li>Pins: Corrected that SDA and SCL are OD6 pins</li> <li>Power and Reset:  — Removed TBD from crystal circuit  — Added Clocks section</li> <li>Electrical Specifications:  — Changed input type ST V<sub>IH</sub> level to minimum 2.0 V, V<sub>H</sub> to 280 mV  — Section 4.2.5: Changed maximum leakage of all pins from &lt;30 μA to &lt;10 μA  — Changed pull-up resistor minimum value to 34 KΩ  — Removed DAC current consumption in Analog section  — In DAC Characteristics, for LRCT, changed values to -67 (typical) and -64 (max)  — Added that CLKOUT duty cycle is characterized only  — Changed I2C timing AC levels to 0.8 and 2.0V  — I2C Slave: removed t<sub>HD:DS</sub> from spec; changed t<sub>HD:DAT</sub> minimum to 18 ns  — SSI slave: Changed t<sub>HR</sub> minimum to 2 ns</li> </ul> |

| November 2011 | Revision 1.0  | Changes:  Changed device description  Changed package marking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| February 2012 | Revision 1.1  | Changes: • Fixed typo: "I2CMS" signal is "I2C Master/Slave Strap" (not I2S).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| October 2013  | Revision 1.15 | Changes:  • In "Physical Dimensions", corrected topside package marking.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### **Table of Contents** Features 2 Signal/Pin Description CONNECTION DIAGRAM ......7 1.2 1.3 1.3.1 1.3.2 1.3.3 I2S / GPIO / STRAPS .......9 1.3.4 1.3.5 1.3.6 Power 11 1.3.7 Not Connected 11 2.0 **Power, Clocks and Reset** 2.1.1 2.1.2 2.1.3 Power Connection 13 2.2 2.3 2.3.1 2.3.2 3.0 **Device Specifications** 3.1.1 3.1.2 3.1.3 Power Supply Current Consumption under Recommended Operating Conditions ....... 19 3.1.4 DC CHARACTERISTICS OF PINS BY I/O BUFFER TYPES ......19 3.2 3.2.1 3.2.2 3.2.3 3.2.4 3.2.5 3.2.6 INTERNAL RESISTORS ......21 3.3 3.3.1

#### Table of Contents (Continued) 3.4.1 DAC Characteristics 22 3.4.2 AC ELECTRICAL CHARACTERISTICS ......23 3.5 3.5.1 AC Test Conditions 23 3.5.2 3.5.3 3.5.4 3.5.5 3.5.6 3.5.7 PACKAGE THERMAL INFORMATION ......29 3.6

### 1.0 Signal/Pin Description

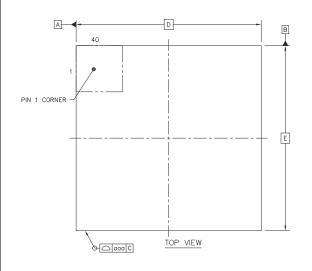

#### 1.1 CONNECTION DIAGRAM

Note: Bottom Pad is VSS.

40-Pin Quad Flat No-Lead (QFN) Package Order Number: NPCA110PA0YX

### 1.2 PIN TYPES

Table 2. Abbreviations

| Abbreviations | Description                                                                                                                                                                                                                                                                          |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO          | General-Purpose I/O                                                                                                                                                                                                                                                                  |

| GPO           | General-Purpose Output                                                                                                                                                                                                                                                               |

| Ox/y          | Output, Source x mA, Sink y mA                                                                                                                                                                                                                                                       |

| ODy           | Output, Open-Drain, Sink y mA                                                                                                                                                                                                                                                        |

| 5V            | Input tolerant to 5 volts                                                                                                                                                                                                                                                            |

| PU            | Input buffer with a pull-up resistor. This pull-up resistor is intended to maintain unconnected input pins at high logic level. The voltage measured externally on an unconnected input pin is in the range of 1.5 to 2.5V, although the input itself is near V <sub>DD</sub> level. |

| Т             | Input buffer with CMOS / LVTTL levels                                                                                                                                                                                                                                                |

| ST            | Schmitt trigger input buffer with CMOS / LVTTL levels                                                                                                                                                                                                                                |

| A             | Analog input or output                                                                                                                                                                                                                                                               |

| хо            | Crystal Oscillator                                                                                                                                                                                                                                                                   |

### 1.3 PIN DESCRIPTION

### 1.3.1 Clocks and Reset

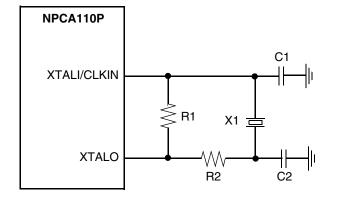

Note: Crystal oscillator connections are found in Figure 3 on page 14.

| Signal      | 1/0 | Description                                                                                                                                                                                                                 | Pull-<br>Up /<br>Down | Power<br>Well | Buffer<br>Type | Comments |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------|----------------|----------|

| XTALI/CLKIN | I   | Crystal Clock Input. Used for a crystal connection circuit or as a clock input (clock input at LVTTL levels). The crystal should have a frequency of 12.288 MHz (48 KHz sample rate) or 11.2896 MHz (44.1 KHz sample rate). |                       | VDD           | ХО             |          |

| XTALO       | 0   | Crystal Clock Output. Used for a crystal connection circuit.                                                                                                                                                                |                       |               |                |          |

| nRESET      | I   | Power-Up Reset Input. If driven low, forces reset.                                                                                                                                                                          | PU                    | VDD           | 5V, ST         |          |

### 1.3.2 GPIO

| Signal | I/O | Description                       | Pull-<br>Up /<br>Down | Power<br>Well | Buffer<br>Type | Comments |

|--------|-----|-----------------------------------|-----------------------|---------------|----------------|----------|

| GPIO19 | I/O | General-Purpose I/O Signal 19.    | PU                    | VDD           | T, 5V, O2/2    |          |

| GPIO15 | I/O | General-Purpose I/O Signal 15.    | PU                    | VDD           | T, 5V, O2/2    |          |

| GPO17  | 0   | General-Purpose Output Signal 17. | PU                    | VDD           | T, 5V, O8/8    |          |

| GPIO20 | I/O | General-Purpose I/O Signal 20.    | PU                    | VDD           | T, 5V, O2/2    |          |

### 1.3.3 I2S / GPIO / STRAPS

| Signal                        | I/O      | Description                                                                                                                                                                                                                                                                                                                   | Pull-<br>Up /<br>Down | Power<br>Well | Buffer<br>Type | Comments |

|-------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------|----------------|----------|

| GPIO00 /<br>DCLK              |          | General-Purpose I/O Signal 00. / I2S Clock. Input for an I2S slave and output for an I2S master. The frequency must be either 32 or 64 times the sample frequency. When used as output, a $33\Omega$ to $100\Omega$ series resistor is required.                                                                              | PU                    | VDD           | T,5V,O2/2      |          |

| GPIO01 /<br>SYNC              |          | General-Purpose I/O Signal 01. / I2S SYNC. Input for an I2S slave and output for an I2S master. Indicates the sample frequency. When used as output, a $33\Omega$ to $100\Omega$ series resistor is required.                                                                                                                 | PU                    | VDD           | T,5V,O2/2      |          |

| GPIO02 /<br>SDI0              | I/O<br>I | General-Purpose I/O Signal 02. / I2S Serial Data In 0. Carries input stereo data stream 0.                                                                                                                                                                                                                                    | PU                    | VDD           | T,5V,O2/2      |          |

| GPIO03 /<br>SDI1              | I/O<br>I | General-Purpose I/O Signal 03. / I2S Serial Data In 1. Carries input stereo data stream 1.                                                                                                                                                                                                                                    | PU                    | VDD           | T,5V,O2/2      |          |

| GPIO04                        | I/O      | General-Purpose I/O Signal 04.                                                                                                                                                                                                                                                                                                | PU                    | VDD           | T,5V,O2/2      |          |

| GPO06 /<br>SDO0 /<br>nTEST    |          | General-Purpose Output Signal 06. / I2S Serial Data Out 0. Carries output stereo data stream 0. A $33\Omega$ to $100\Omega$ series resistor is required. / Test Strap. Sampled during Power-Up reset. The pin is pulled up by an internal resistor for normal operation or set to 0 by an external 8.2 KΩ pull-down resistor. | PU                    | VDD           | T,5V,O2/2      |          |

| GPO07 /<br>SDO1 /<br>CLKOUT / |          | General-Purpose Output Signal 07. / I2S Serial Data Out 1. Carries output stereo data stream 0. / General-Purpose Clock Output. A $33\Omega$ to                                                                                                                                                                               | PU                    | VDD           | T,5V,O2/2      |          |

| REF                           | ı        | 100 $\Omega$ series resistor is required. / Reference Strap. Sampled during Power-Up. The pin is pulled up by an internal resistor (selects DCLK in) or set to 0 by an external 8.2 K $\Omega$ pull-down resistor (selects crystal oscillator).                                                                               |                       |               |                |          |

| SDO2 /<br>GPO18 /<br>I2CMS    |          | I2S Serial Data Out 2. Carries output stereo data stream 0. A 33 to 100 $\Omega$ series resistor is required. / General-Purpose Output Signal 18. / I2C Master/Slave Strap. Sampled during                                                                                                                                    | PU                    | VDD           | T,5V,O2/2      |          |

|                               |          | Power-Up reset. The pin is pulled up by an internal resistor (selects slave) or set to 0 by an external 8.2 K $\Omega$ pull-down resistor (selects master).                                                                                                                                                                   |                       |               |                |          |

## 1.3.4 I2C / GPIO

| Signal | I/O | Description                                                                                                                                                                                | Pull-<br>Up /<br>Down | Power<br>Well | Buffer<br>Type | Comments |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------|----------------|----------|

| SDA    | I/O | Master/Slave I2C Data Line.                                                                                                                                                                |                       | VDD           | ST,5V,OD6      |          |

| SCL    |     | Master/Slave I2C Clock Line. When used as an input, ignores short pulses of a length of less than 5 ns and rejects more signal changes within 20 ns (reducing signal reflections hazards). |                       | VDD           | ST,5V,OD6      |          |

### 1.3.5 CODEC

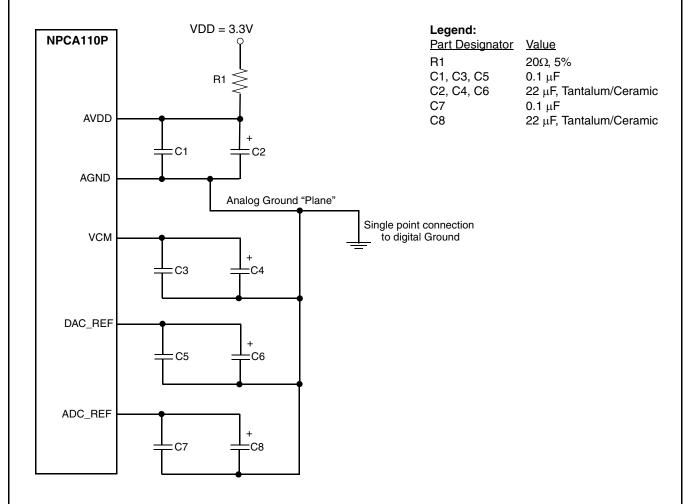

Note: Codec power connections are found in Figure 4 on page 15

| Signal     | I/O | Description                                                                                                                                                                                                            | Power<br>Well | Buffer<br>Type |

|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|

| LIN1, RIN1 | А   | Analog-to-Digital Converter Input Pair 1. Left Input and Right Input are analog inputs and require AC coupling with a 1 $\mu$ F capacitor (0.33 $\mu$ F capacitor if 30 K $\Omega$ input impedance is selected).       | AVDD          | analog         |

| LIN2, RIN2 | А   | Analog-to-Digital Converter Input Pair 2. Left Input and Right Input are analog inputs and require AC coupling with a 1 $\mu$ F capacitor (0.33 $\mu$ F capacitor if 30 K $\Omega$ input impedance is selected).       | AVDD          | analog         |

| LIN3, RIN3 | А   | Analog-to-Digital Converter Input Pair 3. Left Input and Right Input are analog inputs and require AC coupling with a 1 $\mu$ F capacitor (0.33 $\mu$ F capacitor if 30 K $\Omega$ input impedance is selected).       | AVDD          | analog         |

| LOUT1      | Α   | Digital-to-Analog Converter Left Output 1. Left Output 1 is an analog output. This is the main Left Output.                                                                                                            | AVDD          | analog         |

| ROUT1      | Α   | Digital-to-Analog Converter Right Output 1. Right Output 1 is an analog output. This is the main Right Output.                                                                                                         | AVDD          | analog         |

| LOUT22     | А   | <b>Digital-to-Analog Converter Left Output 2.</b> Left Output 2 is an analog output of DAC2. In the case of 2.1 outputs (i.e., stereo pair and a bass channel), LOUT2 is the analog channel used for bass output.      | AVDD          | analog         |

| ROUT22     | Α   | Digital-to-Analog Converter Right Output 2. Right Output 2 is an analog output of DAC2.                                                                                                                                | AVDD          | analog         |

| VCM        | Р   | CODEC Internally Generated Common-Mode Voltage. Should be connected via a 0.1 μF ceramic capacitor, parallel with a tantalum/Ceramic 22 μF capacitor, to AVSS.                                                         | AVDD          | analog         |

| ADC_REF    | Р   | CODEC Internally Generated ADC Reference Voltage. Should be connected via a 0.1 $\mu$ F ceramic capacitor, parallel with a tantalum/Ceramic 22 $\mu$ F capacitor to AVSS.                                              | AVDD          | analog         |

| DAC_REF    | Р   | CODEC Internally Generated DAC Reference Voltage. Should be connected via a 0.1 $\mu$ F ceramic capacitor, parallel with a tantalum/Ceramic 22 $\mu$ F capacitor, to AVSS.                                             | AVDD          | analog         |

| AVDD       | Р   | <b>CODEC Analog 3.3V Supply.</b> Should be connected to a filtered supply. Bypass capacitors of 0.1 μF (ceramic) and 22 μF should be connected to AVSS. A $20\Omega$ series resistor to VDD may be used as the filter. |               |                |

| AVSS       | G   | CODEC Analog Ground. Should be connected to ground. The user may use a separate analog ground plane, connected to the digital (main) ground plane at one point near the NPCA110P.                                      |               |                |

### 1.3.6 **Power**

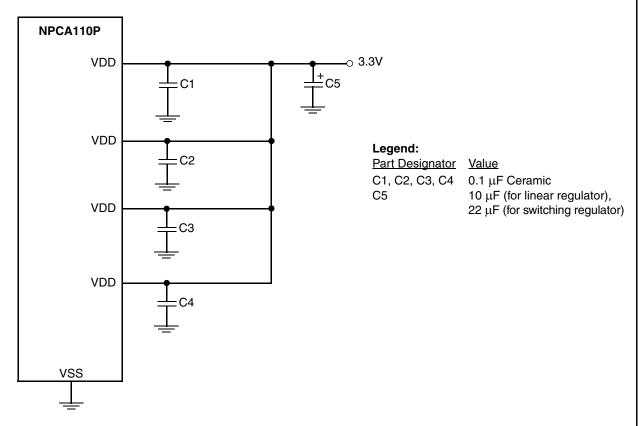

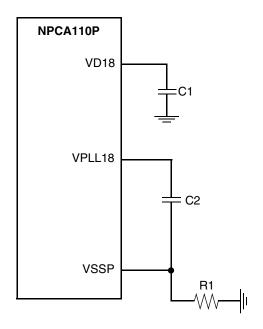

Note: Power connections are found in Figure 1 on page 13 and Figure 2 on page 14.

| Signal | I/O | Description                                                                                                                               |

|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| VSSP   | G   | <b>PLL Ground.</b> Should be connected to a digital ground plane via a $0\Omega$ resistor.                                                |

| VPLL18 | Р   | PLL 1.8V Supply. Internally generated for PLL. Should be connected via a 4.7 $\mu\text{F}$ ceramic capacitor to VSSP.                     |

| VD18   | Р   | Internal 1.8V Supply. Internally generated for internal logic. Should be connected via a 4.7 $\mu$ F ceramic capacitor to digital ground. |

| VSS    |     | <b>Digital Ground.</b> Should be connected to a digital ground plane. The QFN40 package bottom pad must be connected to digital ground.   |

| VDD    | Р   | 3.3V Digital Supply.                                                                                                                      |

### 1.3.7 Not Connected

| Signal | I/C | Description                                                            |

|--------|-----|------------------------------------------------------------------------|

| NC     |     | Not Connected. Should be left open and not be connected to any signal. |

Revision 1.15 11 www.nuvoton.com

### 2.0 Power, Clocks and Reset

#### 2.1 POWER

#### 2.1.1 Power Planes

The NPCA110P has three power plane groups (wells), as shown in Table 3.

Table 3. NPCA110P Power Planes

| Power Plane<br>Group | Description                                                                                                 | Power Plane<br>Notation | Power Pins | Ground Pins |

|----------------------|-------------------------------------------------------------------------------------------------------------|-------------------------|------------|-------------|

| Internal group       | Powers the internal PLL. Supply is generated internally, but requires filtering.                            | V <sub>D18</sub>        | VPLL18     | VSSP        |

|                      | Powers the internal logic of all the device modules. Supply is generated internally but requires filtering. | V <sub>D18</sub>        | VD18       | vss         |

| Active group         | 3.3V power to the I/O interface and internal regulators.                                                    | $V_{DD}$                | VDD        | VSS         |

| Analog Active        | Powers the CODEC; requires filtering                                                                        | $AV_DD$                 | AVDD       | AGND        |

For correct NPCA110P operation,  $AV_{DD}$  must be applied at the same time that  $V_{DD}$  is applied. Protection is provided only against rise-time differences between the different power planes.

#### 2.1.2 Power States

The NPCA110P has the following main power states:

Power Fail

All power planes are powered off; (i.e., V<sub>DD</sub>, AV<sub>DD</sub> are inactive).

Power Active

All power planes are powered on (i.e., V<sub>DD</sub>, AV<sub>DD</sub> are active).

#### Illegal Power States

The following power states are illegal (i.e., NPCA110P operation is not guaranteed):

- · Active power plane on and analog power plane off.

- · Active power plane off and analog power plane on.

#### 2.1.3 Power Connection and Layout Guidelines

The NPCA110P requires a power supply voltage of 3.13V-3.47V for the digital supplies ( $V_{DD}$ ) and 3.00V-3.47V for the analog power supply ( $AV_{DD}$ ).

$V_{DD}$  uses a common ground return named Digital Ground and marked  $V_{SS}$ . The analog circuits use a separate ground return. This ensures effective isolation of the analog modules from noise caused by the digital modules.

The following directives are recommended for the NPCA110P power and ground connections.

#### **Ground Connection**

Use two ground planes, one for digital signals (VSS) and one or more for analog signals (AVSS). Make the following ground connections:

- Connect a specific analog ground plane (AVSS) to the digital ground plane (VSS) at one point only. This point should be physically located near the relevant NPCA110P analog supply pin, AVDD.

- Connect the analog ground return pin (AGND) of the NPCA110P to the analog ground plane.

- Connect the decoupling capacitors of the analog supply (AVDD) to the analog ground plane, as close as possible to the AGND pin.

- Connect all VSS pins and the bottom pad of the NPCA110P to the GND plane.

- Locate the decoupling capacitors of the Active power plane's digital supply (VDD) pins close to a VDD pin; connect one terminal of each capacitor to the ground plane.

- If there is insufficient room for decoupling capacitors, place smaller capacitors close to the power-ground pins and larger capacitors further away.

Note that low-impedance ground layers improve noise isolation and reduce ground bounce problems.

#### **Power Connection**

All NPCA110P supply pins must be connected to the appropriate power plane. Decoupling capacitors must be used as recommended as follows:

- Connect the digital supply pins (VDD) to a 3.3V power supply. A 10 μF (or larger) capacitor should be connected between VDD and the digital ground plane. A 0.1μF capacitor should be connected to ground near each VDD pin of the device.

- Connect the analog supply pins (AVDD) to a low-noise, 3.3V power supply. If the AVDD pin is connected to the same power supply as the VDD pins, it is recommended to use an external L-C or R-C filter for the AVDD pin.

The recommend power connections are shown below:

Figure 1. 3.3V Digital Power Connection Diagram

#### Legend:

Part Designator Value R1 0Ω

C1, C2 4.7  $\mu$ F Ceramic

Figure 2. 1.8V Power Connection Diagram

#### Legend:

$\begin{array}{ll} \mbox{Part Designator} & \mbox{Final Values} \\ \mbox{R1} & 2 \mbox{ M}\Omega \mbox{ 5\%,} \end{array}$

C1 20 pF Ceramic 5%, C2 20 pF Ceramic 5%

Option 1:

R2  $2000\Omega 1\%$ ,

X1 12.288 or 11.2896 MHz,  $\label{eq:classical} C_L \!=\! 12 \text{ pF, ESR} < 75\Omega,$

Drive level up to 500 μW

Option 2:

R2 4990 $\Omega$  1%,

X1 12.288 or 11.2896 MHz,  $C_L {=} 12 \text{ pF, ESR} < 75 \Omega, \label{eq:classical}$

Drive level up to 100  $\mu$ W

Figure 3. Typical Crystal Oscillator Connection Diagram

Figure 4. Recommended CODEC Power Connection Diagram

#### 2.2 CLOCKS

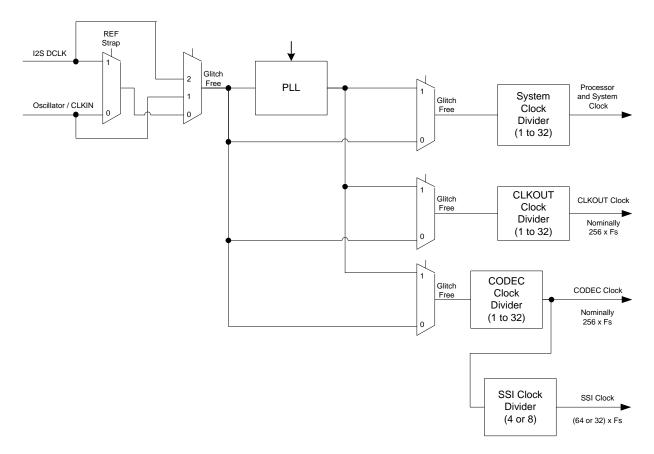

The NPCA110P clock structure is shown below. The clock generation parameters are supplied to the device at initialization.

Figure 5. Clocks in the NPCA110P

#### **Clock Source**

The clock source is either DCLK (I2S serial clock, in slave mode) or the crystal oscillator, and is used as the reference clock of the PLL. The clock is selected initially by the REF strap and may be changed later.

When DCLK is a stable clock, the oscillator may be omitted. The oscillator may be replaced by a clock input.

The best selection for a crystal frequency is 256 times the sample clock used.

#### PLL

The PLL is used to generate the Processor and the CODEC clock (if the oscillator is omitted) and can be used to generate the SSI (I2S) clock as well (if the device is in I2S master mode).

The PLL reference clock may be as low as 44 KHz; however, for low jitter, a higher frequency reference clock is recommended.

#### 2.3 RESET SOURCES AND TYPES

The NPCA110P has one reset domain.

#### **Reset Types**

- Power-Up reset Activated when nReset signal is asserted (when the V<sub>DD</sub> and V<sub>D18</sub> supplies are powered up).

- Watchdog reset Activated when a watchdog condition is detected.

The following sections describe the sources and effects of the various resets on the NPCA110P, per reset type.

#### 2.3.1 Power-Up Reset

$V_{DD}$  Power-Up reset is generated when nRESET signal is asserted.

On Power-Up reset, the NPCA110P performs the following:

- Puts pins with strap options into TRI-STATE® mode and enables the internal pull-up/down resistors on the strap pins.

- Samples the values of the strap pins (after nRESET deassertion).

- Performs all actions done by a Watchdog reset.

Note: The internal reset signal is active for at least 3 ms.

### 2.3.2 Watchdog Reset

Watchdog reset is generated by the Watchdog module on detection of a watchdog event.

The NPCA110P loads default values to all registers.

### 3.0 Device Specifications

### 3.1 GENERAL DC ELECTRICAL CHARACTERISTICS

### 3.1.1 Recommended Operating Conditions

| Symbol           | Parameter <sup>1</sup>                                 | Min  | Тур | Max  | Unit |

|------------------|--------------------------------------------------------|------|-----|------|------|

| $V_{DD}$         | 3.3V Supply Voltage (VDD pins)                         | 3.13 | 3.3 | 3.47 | V    |

| $AV_{DD}$        | 3.3V Analog Supply Voltage (AVDD pin)                  | 3.00 | 3.3 | 3.47 | V    |

| V <sub>OFF</sub> | V <sub>DD</sub> and AV <sub>DD</sub> Power Off Voltage | -0.3 | 0   | +0.5 | V    |

| T <sub>A</sub>   | Operating Ambient Temperature                          | 0    |     | +70  | °C   |

<sup>1.</sup> Unless otherwise specified, all voltages are relative to ground.

### 3.1.2 Absolute Maximum Ratings

Absolute maximum ratings are values beyond which damage to the device may occur. Unless otherwise specified, all voltages are relative to ground. These parameters are characterized and not fully tested.

| Symbol            | Parameter                                                    | Conditions                                                  | Min  | Max                   | Unit |

|-------------------|--------------------------------------------------------------|-------------------------------------------------------------|------|-----------------------|------|

| $V_{DD}$          | 3.3V Supply Voltage, including AV <sub>DD</sub> <sup>1</sup> |                                                             | -0.5 | 3.6                   | V    |

|                   |                                                              | All buffer types (except analog)                            | -0.5 | V <sub>DD</sub> + 0.5 | ٧    |

| $V_{I}$           | Input Voltage <sup>1</sup>                                   | 5V buffer types                                             | -0.5 | 5.5                   | V    |

|                   |                                                              | V <sub>DD</sub> < 0.5V, all digital signals                 | -0.5 | 3.47                  | V    |

| V <sub>O</sub>    | Output Voltage <sup>1</sup>                                  | All buffer types (except analog)                            | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| I <sub>SINK</sub> | Total NPCA110P Sink or Source<br>Current                     | Total of all output pins                                    |      | 50                    | mA   |

|                   | ESD Tolerance                                                | $C_{ZAP} = 100 \text{ pF, R}_{ZAP} = 1.5 \text{ K}\Omega^2$ | 2000 |                       | V    |

| T <sub>STG</sub>  | Storage Temperature                                          |                                                             | -65  | +150                  | °C   |

| T <sub>BIAS</sub> | Ambient Temperature Under Bias                               |                                                             | 0    | +70                   | °C   |

| $P_D$             | Power Dissipation                                            | For correct operation                                       |      | 0.5                   | W    |

<sup>1.</sup> All voltages are relative to ground.

### 3.1.3 Capacitance

| Symbol          | Parameter           | Conditions | Min <sup>1</sup> | Typ <sup>2</sup> | Max <sup>1</sup> | <b>Unit</b> pF |

|-----------------|---------------------|------------|------------------|------------------|------------------|----------------|

| C <sub>IO</sub> | I/O Pin Capacitance | All pins   |                  | 8                | 12               | pF             |

<sup>1.</sup> Not fully tested; characterized only.

<sup>2.</sup> Value based on test complying with RAI-5-048-RA human body model ESD testing.

<sup>2.</sup>  $T_A = 25^{\circ}C$ ; f = 1 MHz.

#### 3.1.4 Power Supply Current Consumption under Recommended Operating Conditions

These table values are preliminary:

|                  | tore raided are premimary.                                                |               |                                                                                     |                  | ı                | 1    |

|------------------|---------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------|------------------|------------------|------|

| Symbol           | Parameter                                                                 | Power<br>Mode | Conditions <sup>1</sup>                                                             | Typ <sup>2</sup> | Max <sup>2</sup> | Unit |

| 11 )1 )          | V <sub>DD</sub> Average <sup>3</sup> Supply Current (including ADC, DACs) | Active        | $V_{IL}=0.5$ V, $V_{IH}=2.4$ V, DAC load = 10 K $\Omega$ Processor clock is 125 MHz | 55               | 70 <sup>4</sup>  | mA   |

| I <sub>DD</sub>  | V <sub>DD</sub> Stop <sup>5</sup> Supply Current                          | Idle          |                                                                                     | 0.7              |                  | mA   |

| I <sub>ADC</sub> | ADC Average current                                                       | Active        |                                                                                     | 4                | 6                | mA   |

| I <sub>DAC</sub> | Each DAC Average current ( $R_L = 10 \text{ K}\Omega$ )                   | Active        |                                                                                     | 2.5              | 5                | mA   |

- 1. Unless stated otherwise, all parameters are specified for  $0^{\circ}C \le T_A \le 70^{\circ}C$ ,  $V_{33} = 3.13V$  3.47V and no resistive load on outputs.

- 2. Not fully tested; characterized only.

- 3. Average current is used for power calculation.

- 4. Resistive loads (such as I2C) on outputs may increase this current, especially if the LEDs are driven directly from the device.

- 5. Stop is defined as: Processor and system clock is halted, PLL is in power-down (Reference clock selected as clock, PLLPD bit set, crystal oscillator disabled).

#### 3.2 DC CHARACTERISTICS OF PINS BY I/O BUFFER TYPES

The tables in this section summarize the DC characteristics of all device pins described in (Section 1.3 on page 8). The characteristics describe the I/O buffer types defined in Section 1.2 on page 8. For exceptions, see Section 3.2.5 on page 20.

#### 3.2.1 Input, TTL Compatible

Symbol: T

| Symbol                        | Parameter                          | Conditions                                         | Min  | Max                  | Unit |

|-------------------------------|------------------------------------|----------------------------------------------------|------|----------------------|------|

| V                             | V <sub>IH</sub> Input High Voltage | Non-5V types                                       | 2.0  | V <sub>DD</sub> +0.5 | V    |

| VIH                           | input nigri voltage                | 5V types                                           | 2.0  | 5.5                  | V    |

| V <sub>IL</sub>               | Input Low Voltage                  |                                                    | -0.5 | 0.8                  | V    |

| I <sub>ILK</sub> <sup>1</sup> | Input Leakage Current              | $V_{DD} = 3.13V - 3.47V$ and $0 < V_{IN} < V_{DD}$ |      | ±2                   | μА   |

<sup>1.</sup> For additional conditions, see Section 3.2.5 on page 20.

#### 3.2.2 Input, TTL Compatible, with Schmitt Trigger

Symbol: ST

| Symbol                             | Parameter             | Conditions                                         | Min              | Max                  | Unit |

|------------------------------------|-----------------------|----------------------------------------------------|------------------|----------------------|------|

| V                                  | Innut High Voltage    | Non-5V types                                       | 2.0              | V <sub>DD</sub> +0.5 | ٧    |

| V <sub>IH</sub> Input High Voltage | input nigri voltage   | 5V types                                           | 2.0              | 5.5                  | ٧    |

| V <sub>IL</sub>                    | Input Low Voltage     |                                                    | -0.5             | 0.8                  | ٧    |

| V <sub>H</sub>                     | Input Hysteresis      |                                                    | 280 <sup>1</sup> |                      | mV   |

| I <sub>ILK</sub> <sup>2</sup>      | Input Leakage Current | $V_{DD} = 3.13V - 3.47V$ and $0 < V_{IN} < V_{DD}$ |                  | ±2                   | μА   |

- 1. Not tested; guaranteed by characterization guardband.

- 2. For additional conditions, see Section 3.2.5 on page 20.

#### 3.2.3 Output, TTL/CMOS-Compatible, Push-Pull Buffer

Symbol:  $O_{p/n}$

Output, TTL/CMOS-compatible, rail-to-rail push-pull buffer that is capable of sourcing p mA and sinking n mA.

| Symbol                        | Parameter              | Conditions                                         | Min                   | Max | Unit |

|-------------------------------|------------------------|----------------------------------------------------|-----------------------|-----|------|

| V                             | Output Lligh Voltage   | $I_{OH} = -p \text{ mA}$                           | 2.4                   |     | V    |

| V <sub>OH</sub>               | Output High Voltage    | I <sub>OH</sub> = -50 μA                           | V <sub>DD</sub> - 0.2 |     | V    |

| V                             | Outrout Law Valtage    | $I_{OL} = n \text{ mA}$                            |                       | 0.4 | V    |

| V <sub>OL</sub>               | Output Low Voltage     | I <sub>OL</sub> = 50 μA                            |                       | 0.2 | V    |

| I <sub>OLK</sub> <sup>1</sup> | Output Leakage Current | $V_{DD} = 3.13V - 3.47V$ and $0 < V_{IN} < V_{DD}$ |                       | ±2  | μА   |

<sup>1.</sup> For additional conditions, see Section 3.2.5 on page 20.

#### 3.2.4 Output, TTL/CMOS-Compatible, Open-Drain Buffer

Symbol:  $OD_n$

Output, TTL/CMOS-compatible open-drain output buffer capable of sinking n mA. Output from these signals is open-drain and is never forced high.

| Symbol                        | Parameter              | Conditions                                         | Min | Max | Unit |

|-------------------------------|------------------------|----------------------------------------------------|-----|-----|------|

| \/                            | Output Low Voltage     | $I_{OL} = n \text{ mA}$                            |     | 0.4 | V    |

| V <sub>OL</sub>               | Output Low Voltage     | I <sub>OL</sub> = 50 μA                            |     | 0.2 | V    |

| I <sub>OLK</sub> <sup>1</sup> | Output Leakage Current | $V_{DD} = 3.13V - 3.47V$ and $0 < V_{IN} < V_{DD}$ |     | ±2  | μА   |

<sup>1.</sup> For additional conditions, see Section 3.2.5 on page 20.

#### 3.2.5 Notes and Exceptions

- 1. I<sub>ILK</sub> and I<sub>OLK</sub> are measured in the following cases (where applicable):

- Internal pull-up or pull-down resistor is disabled

- Push-pull output buffer is disabled (TRI-STATE mode)

- Open-drain output buffer is at high level

- 2. Pins marked with '5V' in the Buffer Type column in Section 1.3 on page 8 are 5V tolerant.

The analog type pins, are not 5V tolerant. This applies if these buffer types are stand-alone or if they are multiplexed with 5V tolerant buffer types.

- 3. Maximum leakage of all the NPCA110P pins together is <10 μA when input voltage is within the supply rails voltage and when PU resistors are disabled in Hi-Z (not fully tested; characterized only).

- 4. A pin (nRESET) that has an internal static pull-up resistor therefore has leakage current from  $V_{DD}$  (when  $V_{IN} = 0$ ).

- Strap pins have an internal pull-up resistor enabled during Power-Up reset and therefore may have leakage current from V<sub>DD</sub> (when V<sub>IN</sub> = 0).

- 6. I<sub>OH</sub> is valid for a GPIO pin only when it is not configured as open-drain.

- 7. All digital pins of output type  $O_{p/n}$  have a back-drive protection capability of up to 3.6V.

#### 3.2.6 Terminology

**Back-Drive Protection.** Back-drive protected pins sustain any voltage within the specified voltage limits when the device power supply is off.

**5-Volt Tolerance.** 5V tolerant pins sustain 5V even if the applied voltage is above the device power supply voltage. A pin is 5V tolerant in the following conditions (where applicable):

- Internal pull-down resistor is disabled. If it is enabled, leakage current is high.

- Push-pull output buffer is disabled (TRI-STATE mode)

#### **INTERNAL RESISTORS** 3.3

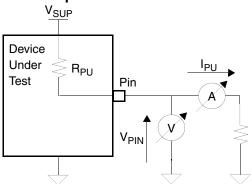

#### **DC Test Conditions**

### **Pull-Up Resistor Test Circuit**

Figure 6. Internal Resistor Test Conditions,  $T_A = 0$ °C to 70°C

#### **Internal Pull-Up Strap** $V_{SUP}$ $\begin{array}{c} \text{Strap Sampled "High"} \\ (\text{V}_{\text{PIN}} > \text{V}_{\text{IH}}) \end{array}$ Strap Sampled "Low" $(V_{PIN} < V_{IL})$ Device Device 10 μA Under Under R<sub>PU</sub> $R_{PU}$ Test Test Pin Pin 10 KΩ

Figure 7. Internal Resistor Design Requirements,  $T_A = 0$ °C to 70°C

- 1. The equivalent resistance of the pull-up resistor is calculated by  $R_{PU} = (V_{SUP} V_{PIN}) / I_{PU}$ .

- 2. The equivalent resistance of the pull-down resistor is calculated by  $R_{PD}$  =  $V_{PIN}$  /  $I_{PD}$ .

#### **Pull-Up Resistors** 3.3.1

#### Symbol: PU

| Symbo           | Parameter                                    | Conditions <sup>1</sup> | Min <sup>2</sup> | Typical | Max <sup>2</sup> | Unit |

|-----------------|----------------------------------------------|-------------------------|------------------|---------|------------------|------|

| R <sub>PU</sub> | Pull-Up Equivalent Resistance for other pins | V <sub>PIN</sub> = 0V   | 34               | 60      | 95               | ΚΩ   |

- 1. TA = 0°C to 70°C,  $V_{SUP}$  = 3.3V  $\pm 5\%$ . 2. Not fully tested; characterized only.

### 3.4 ANALOG CHARACTERISTICS

#### 3.4.1 ADC Characteristics

| Parameter                        | Symbol           | Conditions <sup>1</sup>                                           | Min | Тур                   | Max  | Unit             |

|----------------------------------|------------------|-------------------------------------------------------------------|-----|-----------------------|------|------------------|

| Resolution                       | RES              |                                                                   |     | 24                    |      | Bit              |

|                                  | 7                | Selecting 10 KΩ, AC coupled                                       | 10  | 25                    |      | ΚΩ               |

| Input Impedance <sup>2</sup>     | Z <sub>IN</sub>  | Selecting 30 KΩ, AC coupled                                       | 30  | 75                    |      | ΚΩ               |

| Input Capacitance <sup>3</sup>   | C <sub>AIN</sub> |                                                                   |     |                       | 20   | pF               |

| Dynamic Range                    | DR               |                                                                   | 80  | 90                    |      | dB               |

| Signal-to-Noise Ratio            | SNR              |                                                                   | 80  | 90                    |      | dB               |

| Total Harmonic Distortion        | THD              | At -9 dB of Full-Scale @1 KHz,<br>AV <sub>DD</sub> = 3.13 - 3.47V |     | -75 <sup>4</sup>      | -70  | dB               |

| Total Harmonic Distortion        | THD              | At -9 dB of Full-Scale @1 KHz <sup>3</sup>                        |     | -75                   |      | dB               |

| Full Scale Voltage               | V <sub>FS</sub>  |                                                                   |     | AV <sub>DD</sub> /3.3 |      | V <sub>RMS</sub> |

| Left and Right Channel Mismatch  | LRMM             |                                                                   |     | ±0.1                  | ±0.3 | dB               |

| Analog Multiplexer DC Offset     | MOFS             |                                                                   |     |                       | ±15  | mV               |

| Analog Multiplexer Gain Mismatch | MGM              |                                                                   |     |                       | ±0.5 | dB               |

| Overall Passband Ripple          | OPR              |                                                                   |     |                       | ±0.5 | dB               |

- 1. All parameters specified for  $0^{\circ}C \le T_{A} \le 70^{\circ}C$  and  $AV_{DD} = 3.00V 3.47V$  and using the calibration data, unless otherwise specified.

- 2. Defined when ADC Programmable Gain Amplifier (PGA) Volume control is set to 0 dB. When set to 10 K $\Omega$ : Minimum Z $_{IN}$  at highest PGA gain is 1 K $\Omega$ . When set to 30 K $\Omega$ : Minimum Z $_{IN}$  at highest PGA gain is 2 K $\Omega$ .

- 3. Not fully tested; characterized only.

- 4. Typical value is specified for  $T_A$  = 25°C and AV<sub>33</sub>= 3.30V.

#### 3.4.2 DAC Characteristics

| Parameter                        | Symbol            | Conditions <sup>1</sup>                | Min | Тур                   | Max  | Unit             |

|----------------------------------|-------------------|----------------------------------------|-----|-----------------------|------|------------------|

| Resolution                       | RES               |                                        |     | 24                    |      | Bit              |

| Output Load Resistance           | Z <sub>L</sub>    | AC coupled                             | 0.6 | 10                    |      | ΚΩ               |

| Output Capacitance <sup>2</sup>  | C <sub>AOUT</sub> | AC coupled                             |     | 30                    | 1000 | pF               |

| Dynamic Range                    | DR                |                                        | 90  | 96                    |      | dB               |

| Signal-to-Noise Ratio            | SNR               |                                        | 90  | 96                    |      | dB               |

| Total Harmonic Distortion        | THD               | At -1 dB of Full-Scale<br>@1 KHz input |     | -86                   | -76  | dB               |

| Full-Scale Voltage               | V <sub>FS</sub>   |                                        |     | AV <sub>DD</sub> /3.3 |      | V <sub>RMS</sub> |

| Left and Right Channel Mismatch  | LRMMO             |                                        |     | ±0.1                  | ±0.3 | dB               |

| Left and Right Channel Crosstalk | LRCT              |                                        |     | -67                   | -64  | dB               |

- 1. All parameters specified for  $0^{\circ}C \leq T_A \leq 70^{\circ}C$  and  $AV_{33}$ = 3.00V 3.47V and using the calibration data, unless otherwise specified.

- 2. Not fully tested; characterized only.

#### 3.5 **AC ELECTRICAL CHARACTERISTICS**

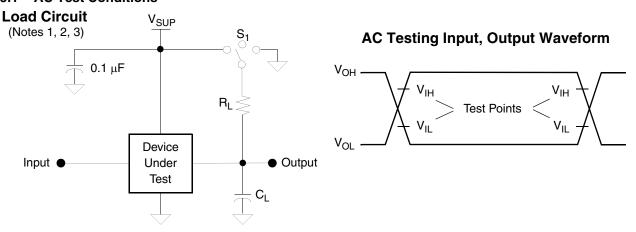

#### **AC Test Conditions** 3.5.1

Figure 8. AC Test Conditions,  $T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{SUP} = 3.13V - 3.47V$

#### Notes:

- 1.  $V_{SUP}$  is  $V_{33}$  according to the power well of the pin, relevant for all signals at LVTTL levels.

- 2. C<sub>I</sub> = 50 pF for all output pins except the following pin groups (values include both jig and oscilloscope capacitance)

$C_L = 100 \text{ pF for I2C}$

$C_L$  = as otherwise defined

- 3.  $S_1 = Open$  for push-pull output pins

- $S_1 = V_{SUP}$

- for high-impedance to active low and active low to high-impedance transition measurements

for high-impedance to active high and active high to high-impedance transition measurements  $S_1 = GND$

$R_L = 1.0 \text{ K}\Omega$  – for all pins

4. The following abbreviations are used in Section 3.5: RE = Rising Edge; FE = Falling Edge.

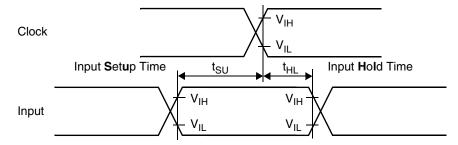

#### **Definitions**

The timing specifications in this section are relative to V<sub>IL</sub> or V<sub>IH</sub> (according to the specific buffer type) on the rising or falling edges of all the signals, as shown in the following figures (unless specifically stated otherwise).

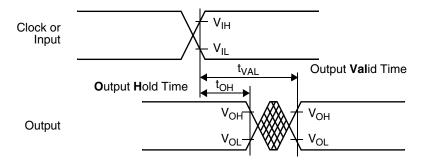

Figure 9. Input Setup and Hold Time

Figure 10. Clock-to-Output and Propagation Delay

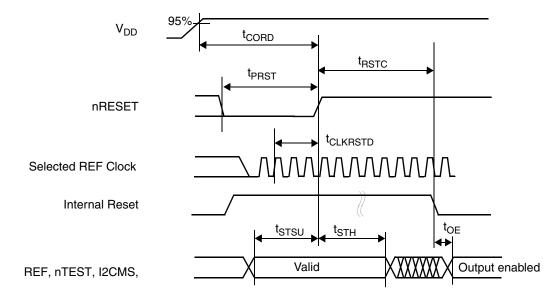

### 3.5.2 Reset Timing

| Symbol               | Figure    | Description                                                                                  | Conditions        | Min   | Max   | Units               |

|----------------------|-----------|----------------------------------------------------------------------------------------------|-------------------|-------|-------|---------------------|

| t <sub>CORD</sub>    | 11        | Power-Up Requirement: all power supplies at valid level until nRESET deasserted <sup>1</sup> | After reset delay | 5     |       | ms                  |

| t <sub>PRST</sub>    | <u>11</u> | nRESET Pulse Width                                                                           | To assure reset   | 1     |       | ms                  |

| t 1:                 | 44 .      |                                                                                              | REF latched high  | 11000 | 12500 | t <sub>REFCLK</sub> |

| <sup>t</sup> RSTC    | <u>11</u> | Internal reset delay after nRESET deasserted                                                 | REF latched low   | 48000 | 52000 | t <sub>REFCLK</sub> |

| t <sub>CLKRSTD</sub> | <u>11</u> | Stable reference clock to reset end                                                          |                   | 100   |       | μS                  |

| t <sub>STSU</sub>    | <u>11</u> | Valid straps signals level setup time to nRESET rising                                       |                   | 100   |       | μS                  |

| t <sub>STH</sub>     | <u>11</u> | Valid straps signals level hold after nRESET rising                                          |                   | 10    |       | t <sub>REFCLK</sub> |

| t <sub>OE</sub>      | 11        | Internal reset end to outputs enabled on strap pins                                          |                   | -100  |       | t <sub>REFCLK</sub> |

### 1. Requirement for system.

Figure 11. Device Reset

### 3.5.3 Clock Timing

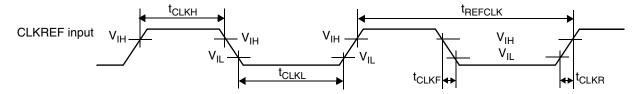

### **CLKREF (DCLK or Oscillator) Clock Timing**

| Symbol              | Figure    | Description                    | Conditions              | Min | Тур | Max  | Units |

|---------------------|-----------|--------------------------------|-------------------------|-----|-----|------|-------|

| t <sub>REFCLK</sub> | 12        | CLKREF Average Clock<br>Period | From RE to RE of CLKREF | 50  |     | 1000 | ns    |

| A <sub>CLK</sub>    |           | CLKREF Accuracy                | For a specific system   |     | 50  | 100  | ppm   |

| t <sub>CLKH</sub>   | <u>12</u> | CLKREF High Time               | From RE to FE of CLKREF | 35  |     |      | ns    |

| t <sub>CLKL</sub>   | <u>12</u> | CLKREF Low Time                | From FE to RE of CLKREF | 35  |     |      | ns    |

| t <sub>CLKR</sub>   | <u>12</u> | CLKREF Rise Time               | From 0.8V to 2.0V       |     |     | 5    | ns    |

| t <sub>CLKF</sub>   | <u>12</u> | CLKREF Fall Time               | From 2.0V to 0.8V       |     |     | 5    | ns    |

| Duty<br>Cycle       |           | CLKREF Duty Cycle              | At 1.4V                 | 40  |     | 60   | %     |

| J <sub>PERIOD</sub> |           | Period Jitter <sup>1</sup>     | At 1.4V                 |     |     | 1.5  | ns    |

1. Measured over a 20  $\mu s$  window.

Figure 12. CLKREF Clock Waveforms

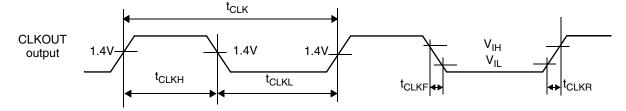

### **CLKOUT Timing**

| Symbol            | Figure    | Description                    | Conditions                                         | Min | Max | Units |

|-------------------|-----------|--------------------------------|----------------------------------------------------|-----|-----|-------|

| t <sub>CLK</sub>  | <u>13</u> | CLKOUT Clock Period            | From RE to RE of CLKOUT, $C_L = 20 \text{ pF}$     | 50  |     | ns    |

| t <sub>CLKH</sub> | <u>13</u> | CLKOUT High Time <sup>1</sup>  | From RE to FE of CLKOUT, $C_L = 20 \text{ pF}$     | 15  |     | ns    |

| t <sub>CLKL</sub> | <u>13</u> | CLKOUT Low Time <sup>1</sup>   | From FE to RE of CLKOUT, C <sub>L</sub> = 20 pF    | 15  |     | ns    |

| t <sub>CLKR</sub> | <u>13</u> | CLKOUT Rise Time <sup>1</sup>  | From $V_{IL}$ to $V_{IH}$ of CLKOUT, $C_L = 20 pF$ |     | 5   | ns    |

| t <sub>CLKF</sub> | <u>13</u> | CLKOUT Fall Time <sup>1</sup>  | From $V_{IH}$ to $V_{IL}$ of CLKOUT, $C_L = 20 pF$ |     | 5   | ns    |

| D <sub>CLK</sub>  |           | CLKOUT Duty Cycle <sup>1</sup> | C <sub>L</sub> = 20 pF                             | 28  |     | %     |

1. Not fully tested; characterized only.

Figure 13. CLKOUT Clock Waveforms

### 3.5.4 Input Signals Detection Timing

| Symbol            | Figure | Description                                                  | Conditions | Min | Max | Units |

|-------------------|--------|--------------------------------------------------------------|------------|-----|-----|-------|

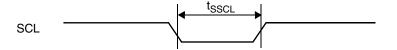

| t <sub>SSCL</sub> | 14     | Debounced SCL input pulse width (which guarantees detection) |            | 15  |     | ns    |

Figure 14. Input Signal Detection Timing

### 3.5.5 I2C Slave Timing

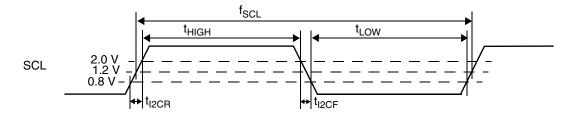

| Symbol              | Figure       | Description                    | Conditions                        | Min  | Max               | Units |

|---------------------|--------------|--------------------------------|-----------------------------------|------|-------------------|-------|

| f <sub>SCL</sub>    | 15           | SCL Frequency                  | At 1.2V SCL RE to RE              |      | 400 <sup>1</sup>  | KHz   |

| t <sub>LOW</sub>    | SCL Low Time |                                | At 0.8V (both edges)              | 0.5  |                   | μS    |

| t <sub>HIGH</sub>   | <u>15</u>    | SCL High Time                  | At 2.0V (both edges)              | 0.26 |                   | μS    |

| t <sub>I2CR</sub>   | <u>15</u>    | SCL, SDA Rise Time             | From 0.8V to 2.0V <sup>1</sup>    |      | 0.25 <sup>2</sup> | μS    |

| t <sub>I2CF</sub>   | <u>15</u>    | SCL, SDA Fall Time             | From 2.0V to 0.8V <sup>1</sup>    |      | 100               | ns    |

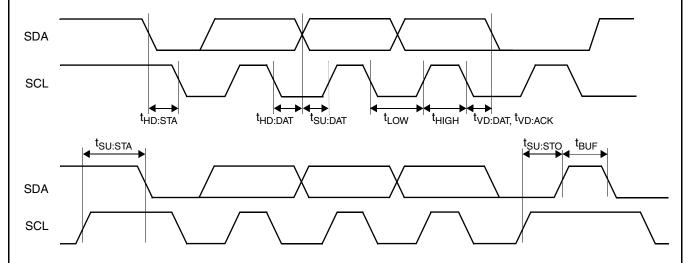

| t <sub>SU:DAT</sub> | <u>15</u>    | SDA Setup Time                 | Before SCL RE                     | 50   |                   | ns    |

| t <sub>HD:DAT</sub> | <u>16</u>    | SDA Hold Time                  | After SCL FE                      | 18   |                   | ns    |

| t <sub>SU:STA</sub> | <u>16</u>    | SCL Setup Time                 | Before Restart condition          | 0.26 |                   | μS    |

| t <sub>HD:STA</sub> | <u>16</u>    | SCL Hold Time                  | After Start/Restart condition     | 0.26 |                   | μS    |

| t <sub>SU:STO</sub> | <u>16</u>    | SCL Setup Time                 | Before Stop condition             | 0.26 |                   | μS    |

| t <sub>BUF</sub>    | <u>16</u>    | Bus Free Time                  | Between Stop and Start conditions | 0.5  |                   | μЅ    |

| t <sub>VD:DAT</sub> | <u>16</u>    | Data Valid Time                | After SCL FE                      |      | 0.45              | μS    |

| t <sub>VD:ACK</sub> | <u>16</u>    | Data Valid<br>Acknowledge Time | After SCL FE                      |      | 0.45              | μs    |

- 1. Test conditions: R<sub>L</sub> = 1 K $\Omega$  to V<sub>DD</sub> = 3.3V, C<sub>L</sub> = 100 pF to GND 2. Not tested; based on design simulation.

Figure 15. I2C SCL Signal Timing

Figure 16. I2C Timing

### 3.5.6 I2C Master Timing

| Symbol                     | Figure    | Description                                 | Conditions                        | Min                               | Тур                                 | Max                  | Units |

|----------------------------|-----------|---------------------------------------------|-----------------------------------|-----------------------------------|-------------------------------------|----------------------|-------|

| f                          | 45        | SCL Frequency <sup>4</sup>                  | Programming capability            | f <sub>AEE</sub> / 16384          |                                     | f <sub>AEE</sub> / 8 |       |

| f <sub>SCL</sub> <u>15</u> |           | SCL Frequency <sup>4</sup>                  | At 1.2V SCL RE to RE              | 0                                 |                                     | 400 <sup>1</sup>     | KHz   |

| t <sub>LOW</sub>           | <u>15</u> | SCL Low Time <sup>4</sup>                   | At 0.8V (both edges)              | 8 x T <sub>AEE</sub> <sup>2</sup> | 0.5 x T <sub>SCL</sub> <sup>3</sup> |                      |       |

| t <sub>HIGH</sub>          | <u>15</u> | SCL High Time <sup>4</sup>                  | At 2.0V (both edges)              | 8 x T <sub>AEE</sub>              | 0.5 x T <sub>SCL</sub>              |                      |       |

| t <sub>I2CR</sub>          | <u>15</u> | SCL, SDA Rise Time                          | From 0.8V to 2.0V <sup>1</sup>    |                                   |                                     | 0.25 <sup>4</sup>    | μS    |

| t <sub>I2CF</sub>          | <u>15</u> | SCL, SDA Fall Time <sup>4</sup>             | From 2.0V to 0.8V <sup>1</sup>    |                                   |                                     | 100                  | ns    |

| t <sub>SU:DAT</sub>        | <u>16</u> | SDA Setup Time <sup>4</sup>                 | Before SCL RE                     | 4 x T <sub>AEE</sub>              | 0.25 x T <sub>SCL</sub>             |                      |       |

| t <sub>HD:DAT</sub>        | <u>16</u> | SDA Hold Time <sup>4</sup>                  | After SCL FE                      | 4 x T <sub>AEE</sub>              | 0.25 x T <sub>SCL</sub>             |                      |       |

| t <sub>SU:STA</sub>        | <u>16</u> | SCL Setup Time <sup>4</sup>                 | Before Restart condition          | 12 x T <sub>AEE</sub>             | 0.5 x T <sub>SCL</sub>              |                      |       |

| t <sub>HD:STA</sub>        | <u>16</u> | SCL Hold Time <sup>4</sup>                  | After Start/Restart condition     | 4 x T <sub>AEE</sub>              | 0.5 x T <sub>SCL</sub>              |                      |       |

| t <sub>SU:STO</sub>        | <u>16</u> | SCL Setup Time <sup>4</sup>                 | Before Stop condition             | 4 x T <sub>AEE</sub>              | 0.5 x T <sub>SCL</sub>              |                      |       |

| t <sub>BUF</sub>           | <u>16</u> | Bus Free Time <sup>4</sup>                  | Between Stop and Start conditions | 16 x T <sub>AEE</sub>             | 0.5 x T <sub>SCL</sub>              |                      |       |

| t <sub>VD:DAT</sub>        | <u>16</u> | Data Valid Time <sup>4</sup>                | After SCL FE                      | 4 x T <sub>AEE</sub>              | 0.5 x T <sub>SCL</sub>              |                      |       |

| t <sub>VD:ACK</sub>        |           | Data Valid<br>Acknowledge Time <sup>4</sup> | After SCL FE                      | 4 x T <sub>AEE</sub>              | 0.5 x T <sub>SCL</sub>              |                      |       |

- 1. Test conditions:  $R_L = 1 \text{ K}\Omega$  to  $V_{DD} = 3.3\text{V}$ ,  $C_L = 100 \text{ pF}$  to GND. 2.  $T_{AEE}$  is the Processor core clock period. 3.  $T_{SCL}$  is the SCL clock period (1/ $f_{SCL}$ ). 4. Not tested; based on design simulation.

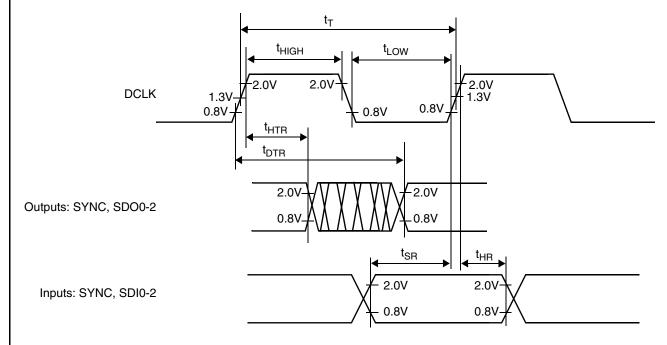

### 3.5.7 SSI Timing

| Symbol            | Figure    | Description       | Conditions            | Min   | Тур                  | Max  | Units                         |

|-------------------|-----------|-------------------|-----------------------|-------|----------------------|------|-------------------------------|

| t <sub>T</sub>    | <u>17</u> | DCLK Cycle Time   | At 1.3V DCLK RE to RE | 1/64  | 1/64                 | 1/32 | 1/F <sub>S</sub> <sup>1</sup> |

| f <sub>DCLK</sub> |           | DCLK Frequency    |                       | 32    | 64                   | 64   | F <sub>S</sub> <sup>1</sup>   |

| t <sub>LOW</sub>  | <u>17</u> | DCLK Low Time     | At 0.8V (both edges)  | 0.35  | 0.5                  |      | t <sub>T</sub>                |

| t <sub>HIGH</sub> | <u>17</u> | DCLK High Time    | At 2.0V (both edges)  | 0.35  | 0.5                  |      | t <sub>T</sub>                |

| t <sub>HTR</sub>  | <u>17</u> | Output Hold Time  | After DCLK RE         | 15 ns | 0.5 * t <sub>T</sub> |      |                               |

| t <sub>DTR</sub>  | <u>17</u> | Output Valid Time | After DCLK RE         |       | 0.5                  | 0.75 | t <sub>T</sub>                |

| t <sub>HR</sub>   | <u>17</u> | Input Hold Time   | After DCLK RE         | 2     |                      |      | t <sub>T</sub>                |

| t <sub>SR</sub>   | <u>17</u> | Input Setup Time  | Before DCLK RE        | 0.2   |                      |      | t <sub>T</sub>                |

1.  $\boldsymbol{F}_{\boldsymbol{S}}$  is the audio sampling frequency

Figure 17. SSI Signal Timing

### 3.6 PACKAGE THERMAL INFORMATION

Thermal resistance (degrees <sup>o</sup>C/W) Theta<sub>JA</sub> values for the NPCA110P packages are as follows:

Table 4. Theta  $(\Theta)$  J-A Values

|              | Θ <sub>JA</sub> (Degrees Kelvin/Watt) |       |       |  |  |

|--------------|---------------------------------------|-------|-------|--|--|

| Package      | 0 m/s                                 | 1 m/s | 2 m/s |  |  |

| 40-Pin QFN40 | 57                                    | 49    | 47    |  |  |

Note: All values apply to a device soldered to a 4-layer PCB.

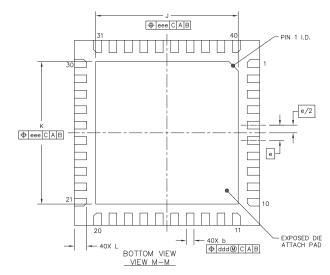

### **Physical Dimensions**

Control dimensions are in millimeters.

|                           |     | SYMBOL | MIN       | NOM  | MAX  |

|---------------------------|-----|--------|-----------|------|------|

| TOTAL THICKNESS           | Α   | 0.8    | 0.85      | 0.90 |      |

| STAND OFF                 | A1  | 0      | 0.035     | 0.05 |      |

| MOLD THICKNESS            |     | A2     | 0.65 C    |      | 0.67 |

| L/F THICKNESS             |     | A3     | 0.203 REF |      |      |

| LEAD WIDTH                |     | b      | 0.18      | 0.25 | 0.30 |

| BODY SIZE                 | Χ   | D      | 5.90      | 6.00 | 6.10 |

| BODY SIZE                 | Υ   | Е      | 5.90      | 6.00 | 6.10 |

| LEAD PITCH                |     | е      | 0.50 BSC  |      |      |

| EP SIZE                   | Χ   | J      | 4.40      | 4.62 | 4.72 |

| LF SIZE                   | Υ   | K      | 4.40      | 4.62 | 4.72 |

| LEAD LENGTH               |     | L      | 0.30      | 0.40 | 0.50 |

| PACKAGE EDGE<br>TOLERANCE |     | aaa    | 0.10      |      |      |

| MOLD FLATNESS             |     | bbb    | 0.10      |      |      |

| COPLANARITY               |     | ССС    | 0.08      |      |      |

| LEAD OFFSET               |     | ddd    | 0.10      |      |      |

| EXPOSED PAD OFF           | SET | eee    | 0.10      |      |      |

NOTE

1.0 COPLANARITY APPLIES TO LEADS, CORNER LEADS AND DIE ATTACH PAD.

### 40-Pin Quad Flat No-Lead (QFN) Package Order Number: NPCA110PA0YX

### Device topside mark specification:

1st Line: **Nuvoton company logo** 2nd Line: Part number (NPCA110PA)

Part number continuation (0YX, where 'Y' is the QFN package number 3rd Line:

and 'X' is the green package finish indicator);

Date code (YWW, where 'Y' is the year and 'WW' is the week); Assembly lot number (XXX)

4th Line: Assembly lot number continuation (XXXXXX-XX)

Date code: YWW, where Y is the year and WW is the week. For example, 035

indicates that device assembly was done on week 35, year 2010.

#### nuvoTon

NPCA110PA 0YXYWWXXX XXXXXX-XX

#### **Important Notice**

Nuvoton products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Furthermore, Nuvoton products are not intended for applications wherein failure of Nuvoton products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.

Nuvoton customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nuvoton for any damages resulting from such improper use or sales.

Headquarters

No. 4, Creation Rd. 3, Science-Based Industrial Park, Hsinchu, Taiwan, R.O.C TEL: 886-3-5770066 FAX: 886-3-5665577 http://www.nuvoton.com.tw (Chinese)

http://www.nuvoton.com (English)

Taipei Office 9F, No.480, Rueiguang Rd.,

Neihu District, Taipei, 114, Taiwan, R.O.C. TEL: 886-2-2658-8066 FAX: 886-2-8751-3579

**Nuvoton Technology Corporation America**

2727 North First Street, San Jose, CA 95134, U.S.A. TEL: 1-408-544-1718 FAX: 1-408-544-1787

Wilhold Electronics Colporatio NO. 2 Ueno-Bidg., 7-18, 3-chome Shinyokohama Kohoku-ku, Yokohama, 222-0033 TEL: 81-45-4781881

Winbond Electronics Corporation Japan

FAX: 81-45-4781800

Nuvoton Technology (H.K.) Ltd.

Nuvoton Technology (Shanghai) Ltd. 27F, 2299 Yan An W. Rd. Shanghai, 200336 China

Unit 9-15, 22F, Millennium City 2, 378 Kwun Tong Rd., Kowloon, Hong Kong TEL: 852-27513100 FAX: 852-27552064

TEL: 86-21-62365999 FAX: 86-21-62365998

For Advanced PC Product Line information contact: APC.Support@nuvoton.com

Please note that all data and specifications are subject to change without notice.