# MXD85A0F

SP10T TRX Switch with MIPI

This document contains information that is confidential and proprietary to Maxscend Microelectronics Company Limited (Maxscend) and may not be reproduced in any form without express written consent of Maxscend. No transfer or licensing of technology is implied by this document.

#### **General Description**

The MXD85A0F is a low loss, high isolation SP10T switch for antenna TRX application.

The MXD85A0F is compatible with MIPI control, which is a key requirement for many cellular transceivers. This part is packaged in a compact 2.4mm x 2.4mm, 20-pin, QFN package which allows for a small solution size with no need for external DC blocking capacitors (when no external DC is applied to the device ports).

## **Applications**

- 2G/3G/4G antenna diversity

- Cellular modems and USB Devices

#### **Features**

- Excellent insertion loss

- 0.75 dB Insertion Loss at 2.7GHz

- P0.1dB @ 35dBm

- Multi-Band operation 400MHz to 3000MHz

- RFFE serial control interface

- Compact 2.4mm x 2.4mm in QFN-20 package

- No DC blocking capacitors required (unless external DC is applied to the RF ports)

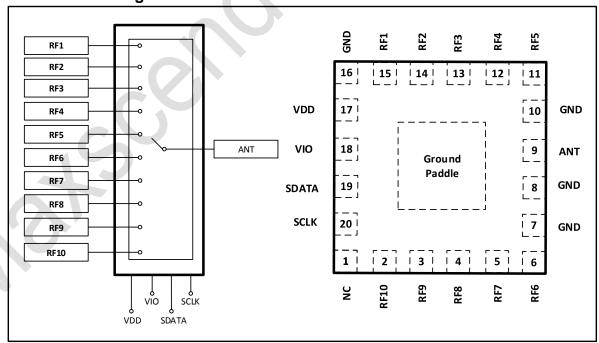

## **Functional Block Diagram and Pin Function**

Figure 1 Functional Block Diagram and Pinout (Top View)

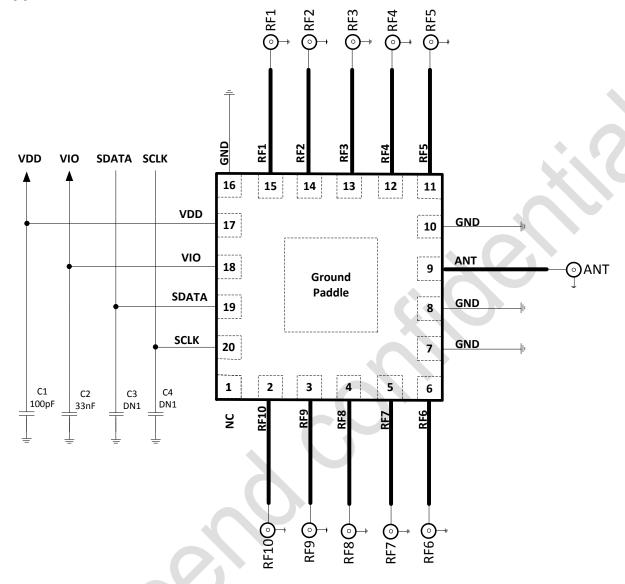

## **Application Circuit**

Figure 2 Evaluation Board Schematic

**Table 1. Pin Description**

| Pin No.          | Name | Description  | Pin No. | Name  | Description             |

|------------------|------|--------------|---------|-------|-------------------------|

| 1                | NC   | Not Connect  | 11      | RF5   | RF port5                |

| 2                | RF10 | RF port10    | 12      | RF4   | RF port4                |

| 3                | RF9  | RF port9     | 13      | RF3   | RF port3                |

| 4                | RF8  | RF port8     | 14      | RF2   | RF port2                |

| 5                | RF7  | RF port7     | 15      | RF1   | RF port1                |

| 6                | RF6  | RF port6     | 16      | GND   | Ground                  |

| 7                | GND  | Ground       | 17      | VDD   | Power supply            |

| 8                | GND  | Ground       | 18      | VIO   | Supply voltage for MIPI |

| 9                | ANT  | Antenna port | 19      | SDATA | MIPI data input/output  |

| 10               | GND  | Ground       | 20      | SCLK  | MIPI clock              |

| Ground<br>Paddle | GND  | Ground       |         |       |                         |

Note: Bottom ground paddles must be connected to ground.

#### **Truth Table**

#### Table 2.

| State | Mode    | Register_0 |    |    |    |    |    |    |    |  |

|-------|---------|------------|----|----|----|----|----|----|----|--|

| State | Wiode   | D7         | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

| 1     | ISO     | Х          | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| 2     | RF1 on  | Х          | 0  | 0  | 0  | 0  | 0  | 1  | 0  |  |

| 3     | RF2 on  | Х          | 0  | 0  | 0  | 1  | 0  | 1  | 0  |  |

| 4     | RF3 on  | Х          | 0  | 0  | 0  | 1  | 1  | 1  | 0  |  |

| 5     | RF4 on  | Х          | 0  | 0  | 0  | 1  | 0  | 1  | 1  |  |

| 6     | RF5 on  | Х          | 0  | 0  | 0  | 0  | 0  | 0  | 1  |  |

| 7     | RF6 on  | Х          | 0  | 0  | 0  | 1  | 0  | 0  | 1  |  |

| 8     | RF7 on  | Х          | 0  | 0  | 0  | 0  | 1  | 1  | 0  |  |

| 9     | RF8 on  | Х          | 0  | 0  | 0  | 0  | 1  | 0  | 0  |  |

| 10    | RF9 on  | Х          | 0  | 0  | 0  | 1  | 1  | 0  | 0  |  |

| 11    | RF10 on | Х          | 0  | 0  | 0  | 1  | 0  | 0  | 0  |  |

# **Recommended Operation Range**

### **Table 3. Recommended Operation Condition**

| Parameters                | Symbol   | Min     | Тур | Max  | Units |

|---------------------------|----------|---------|-----|------|-------|

| Operation Frequency       | f1       | 0.7     | -   | 3.0  | GHz   |

| Power supply              | $V_{DD}$ | 2.5     | 2.8 | 3.0  | V     |

| Power supply for MIPI     | Vio      | 1.65    | 1.8 | 1.95 | V     |

| MIPI Control Voltage High | Vн       | 0.8*VIO | 1.8 | 1.95 | V     |

| MIPI Control Voltage Low  | VL       | 0       | 0   | 0.3  | V     |

# **Specifications**

### **Table 4. Electrical Specifications**

| Parameter                                                         | Symbol           | Test Condition                                     | Min                       | Typical              | Max         | Units          |

|-------------------------------------------------------------------|------------------|----------------------------------------------------|---------------------------|----------------------|-------------|----------------|

| DC Specifications                                                 |                  |                                                    |                           |                      |             |                |

| Supply voltage                                                    | V <sub>DD</sub>  |                                                    | 2.5                       | 2.8                  | 3.0         | V              |

| Supply current                                                    | ldd              |                                                    |                           | 55                   | 80          | uA             |

| V <sub>IO</sub> supply voltage                                    | Vio              |                                                    | 1.65                      | 1.8                  | 1.95        | ٧              |

| V <sub>IO</sub> Supply current                                    | lio              |                                                    |                           | 4                    | 10          | uA             |

| SDATA, SCLK control voltage: High Low                             | Vctl_h<br>Vctl_l |                                                    | 0.8* V <sub>IO</sub><br>0 | V <sub>IO</sub><br>0 | 1.95<br>0.3 | V              |

| Switching Speed, one RF to another                                |                  | 10% to 90% RF                                      |                           | 1                    | 2           | uS             |

| RF Specifications                                                 |                  |                                                    |                           |                      |             |                |

| Insertion loss (ANT pin to RF1/2/3/4/5/6/7/8/9/10 pins)           | IL               | 0.1 to 1.0 GHz<br>1.0 to 2.0 GHz<br>2.0 to 2.7 GHz |                           | 0.50<br>0.65<br>0.75 |             | dB<br>dB<br>dB |

| Isolation (ANT pin to<br>RF1/2/3/4/5/6/7/8/9/10 pins)             | Iso              | 0.1 to 1.0 GHz<br>1.0 to 2.0 GHz<br>2.0 to 2.7 GHz | 35<br>25<br>18            | 40<br>30<br>20       |             | dB<br>dB<br>dB |

| Input return loss (ANT pin to RF1/2/3/4/5/6/7/8/9/10 pins)        | RL               | 0.1 to 1.0 GHz<br>1.0 to 2.0 GHz<br>2.0 to 2.7 GHz | 20<br>15<br>12            | 25<br>20<br>15       |             | dB<br>dB<br>dB |

| 0.1 dB Compression Point (ANT pin to RF1/2/3/4/5/6/7/8/9/10 pins) | P0.1dB           | 0.7 GHz to 3.0 GHz                                 |                           | +35                  |             | dBm            |

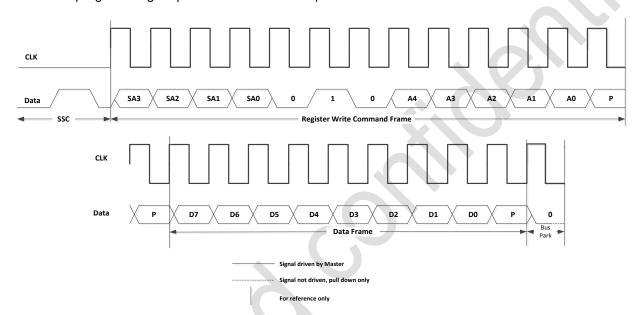

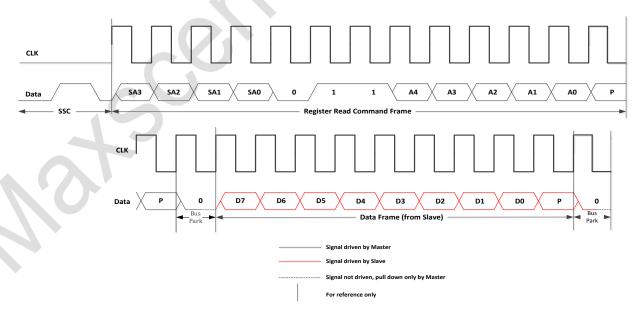

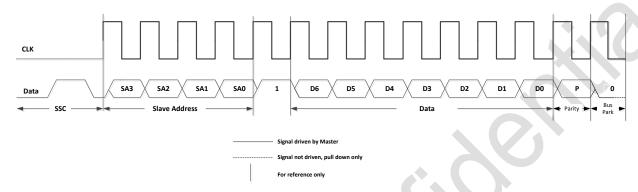

#### **MIPI Read and Write Timing**

MIPI supports the following Command Sequences:

- Register Write

- Register\_0 Write

- Register Read

Figures 3 and 4 provide the timing diagrams for register write commands and read commands, respectively. Figure 5 shows the Register 0 Write Command Sequence. Refer to the MIPI Alliance Specification for RF Front-End Control Interface (RFFE), v1.10 (26 July 2011) for additional information on MIPI USID programming sequences and MIPI bus specifications.

Figure 3 Register Write Command Sequence

Figure 4 Register Read Command Sequence

In the timing figures, SA[3:0] is slave address. A[4:0] is register address. D[7:0] is data. "P" is odd parity bit.

#### **Register 0 Write Command Sequence**

Figure shows the Register 0 Write Command Sequence. The Command Sequence starts with an SSC, followed by the Register 0 Write Command Frame containing the Slave address, a logic one, and a seven bit word to be written to Register 0. The Command Sequence ends with a Bus Park Cycle.

Figure 5 Register 0 Write Command Sequence

## **Register definition**

### Table 5. Register definition table

| Register<br>Address | Register<br>Name    | Data<br>Bits | R/W      | Function                                                                                                                                                                                                              | Description                                                                                                                                                                                                   | Default | BROADC<br>AST_ID<br>support | Trigger support |

|---------------------|---------------------|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------|-----------------|

| 0x00                | REGISTER_0          | 7:0          | R/W      | RF Control                                                                                                                                                                                                            | Register_0 truth Table: Table 2                                                                                                                                                                               | 0x00    | No                          | Yes             |

| 0x001B              | GROUP_SID           | 7:4          | R        | RESERVED                                                                                                                                                                                                              |                                                                                                                                                                                                               | 0x0     | No                          | No              |

| UXUUTB              | GROUP_SID           | 3:0          | R/W      | GSID                                                                                                                                                                                                                  | Group Slave ID                                                                                                                                                                                                | 0x0     | No                          | No              |

|                     | 7:6                 | R/W          | PWR_MODE | 00: Normal Operation (ACTIVE) 01: Reset all registers to default settings (STARTUP) 10: Low power (LOW POWER) 11: Reserved Note: Write PWR_MODE=2'h1 will reset all register, and puts the device into STARTUP state. | 0b10                                                                                                                                                                                                          | Yes     | No                          |                 |

|                     |                     | 5            | R/W      | Trigger_Mask_2                                                                                                                                                                                                        | If this bit is set, trigger 2 is disabled                                                                                                                                                                     | 0       | No                          | No              |

|                     |                     | 4            | R/W      | Trigger_Mask_1                                                                                                                                                                                                        | If this bit is set, trigger 1 is disabled                                                                                                                                                                     | 0       | No                          | No              |

| 0x001C PM_          | PM_TRIG             | 3            | R/W      | Trigger_Mask_0                                                                                                                                                                                                        | If this bit is set, trigger 0 is disabled Note: When all triggers are disabled, writing to a register that is associated with trigger 0, 1, or 2, causes the data to go directly to the destination register. | 0       | No                          | No              |

|                     |                     | 2            | W        | Trigger_2                                                                                                                                                                                                             | A write of a one to this bit loads trigger 2's registers                                                                                                                                                      | 0       | Yes                         | No              |

|                     |                     | 1            | W        | Trigger_1                                                                                                                                                                                                             | A write of a one to this bit loads trigger 1's registers                                                                                                                                                      | 0       | Yes                         | No              |

|                     |                     | 0            | W        | Trigger_0                                                                                                                                                                                                             | A write of a one to this bit loads trigger 0's registers Note: Trigger processed immediately then cleared. Trigger 0, 1, and 2 will always read as 0.                                                         | 0       | Yes                         | No              |

| 0x001D              | PRODUCT_ID          | 7:0          | R        | PRODUCT_ID                                                                                                                                                                                                            | Product Number                                                                                                                                                                                                | 0x01    | No                          | No              |

| 0x001E              | MANUFACTU<br>RER_ID | 7:0          | R        | MANUFACTUR<br>ER_ID[7:0]                                                                                                                                                                                              | Lower eight bits of MIPI registered<br>Manufacturer ID                                                                                                                                                        | 0x81    | No                          | No              |

|                     |                     | 7:6          | R        | RESERVED                                                                                                                                                                                                              |                                                                                                                                                                                                               | 0b00    | No                          | No              |

| 0x001F              | MAN_USID            | 5:4          | R        | MANUFACTUR<br>ER_ID[9:8]                                                                                                                                                                                              | Upper two bits of MIPI registered<br>Manufacturer ID                                                                                                                                                          | 0b11    | No                          | No              |

|                     |                     | 3:0          | R/W      | USID                                                                                                                                                                                                                  | USID of the device.                                                                                                                                                                                           | 0xa     | No                          | No              |

#### **Absolute Maximum Ratings**

#### Table 6. Maximum ratings

| Parameters                                                     | Symbol           | Minimum | Maximum | Units                |

|----------------------------------------------------------------|------------------|---------|---------|----------------------|

| Supply voltage                                                 | $V_{DD}$         | +2.0    | +3.3    | V                    |

| Supply voltage for MIPI                                        | $V_{1O}$         | +1.0    | +2.0    | V                    |

| MIPI Control voltage<br>(SDATA, SCLK)                          | V <sub>CTL</sub> | 0       | +2.0    | V                    |

| RF input power<br>(RF1/2/3/4/5/6/7/8/9/10)                     | Pin              |         | +36     | dBm                  |

| Operating temperature                                          | $T_OP$           | -20     | +85     | $^{\circ}\mathbb{C}$ |

| Storage temperature                                            | T <sub>STG</sub> | -40     | +125    | C                    |

| Electrostatic Discharge<br>Human body model<br>(HBM), Class 1C | ESD_HBM          |         | 1000    |                      |

| Machine Model (MM),<br>Class A                                 | ESD_MM           |         | 100     | V                    |

| Charged device model (CDM), Class III                          | ESD_CDM          |         | 500     |                      |

Note: Exposure to maximum rating conditions for extended periods may reduce device reliability. There is no damage to device with only one parameter set at the limit and all other parameters set at or below their nominal value. Exceeding any of the limits listed here may result in permanent damage to the device

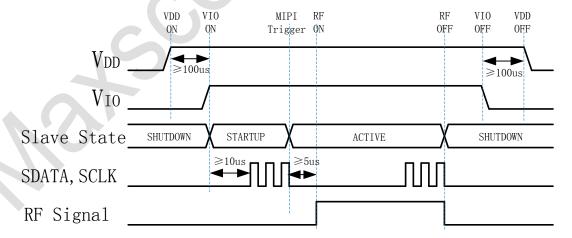

#### **Power ON and OFF sequence**

Here is the recommendation about power-on/off sequence in order to avoid damaging the device.

#### **Power ON**

- 1) Apply voltage supply VDD

- 2) Apply logic supply Vio

- 3) Wait 10µs or greater and then apply MIPI bus signals SCLK and SDATA

- 4) Wait 5µs or greater after MIPI bus goes idle and then apply the RF Signal

#### **Power OFF**

- 1) Remove the RF Signal

- 2) Remove MIPI bus SCLK and SDATA

- 3) Remove logic supply Vio

- 4) Remove voltage supply VDD

Note: VIO can be applied to the device before VDD or removed after VDD.

It is important to wait 10µs after VIO & VDD are applied before sending SDATA to ensure correction data transmission.

The minimum time between a power up and power down sequence (and vice versa) is ≥ 100us.

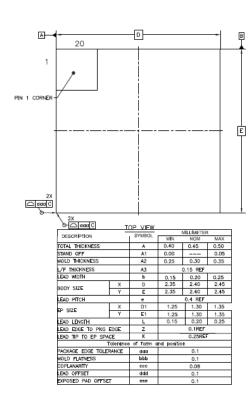

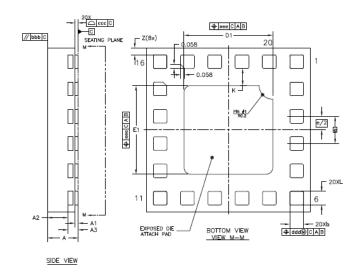

## **Package Outline Dimension**

Figure 6 package outline dimension

#### **Reflow Chart**

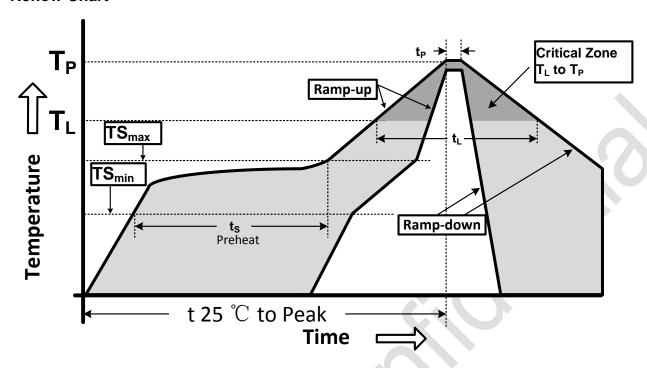

Figure 7 Recommended Lead-Free Reflow Profile

**Table 7. Reflow condition**

| Profile Parameter                                                 | Lead-Free Assembly, Convection, IR/Convection |

|-------------------------------------------------------------------|-----------------------------------------------|

| Ramp-up rate $(TS_{max} \text{ to } T_p)$                         | 3℃/second max.                                |

| Preheat temperature (TS <sub>min</sub> to TS <sub>max</sub> )     | 150℃ to 200℃                                  |

| Preheat time (t <sub>s</sub> )                                    | 60 - 180 seconds                              |

| Time above TL , 217 $^{\circ}$ C (t <sub>L</sub> )                | 60 - 150 seconds                              |

| Peak temperature (T <sub>p</sub> )                                | 260℃                                          |

| Time within 5 <sup>°</sup> C of peak temperature(t <sub>p</sub> ) | 20 - 40 seconds                               |

| Ramp-down rate                                                    | 6°C/second max.                               |

| Time 25°C to peak temperature                                     | 8 minutes max.                                |

#### **ESD Sensitivity**

Integrated circuits are ESD sensitive and can be damaged by static electric charge. Proper ESD protection techniques should be used when handling these devices.

#### **RoHS Compliant**

This product does not contain lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB) and polybrominated diphenyl ethers (PBDE), and are considered RoHS compliant.